Способ кодирования данных на основе ldpc кода - RU2743784C1

Код документа: RU2743784C1

Описание

Изобретение относится к устройствам кодирования информации с использованием кодов с низкой плотностью проверок на четность (LDPC) и предназначено для обеспечения работы немеханических запоминающих устройств на основе микросхем памяти (SSD, USB Flash Drive, Flash Card и т.д.), применяется в аппаратуре контроллера немеханических запоминающих устройств на основе микросхем памяти.

В контроллерах твердотельных дисков LDPC коды стали применятся относительно недавно, заменив доминирующие много лет в этой области БЧХ (Боуза-Чоудхури-Хоквингема) коды. Одной из основных причин замены кодов на LDPC стал массовый переход производителей твердотельных дисков от моделей флеш-памяти, где в одной ячейке памяти хранится один бит, к более экономичным видам памяти, где плотность информации значительно выше (два, три и более бит). С ростом числа исправляемых ошибок сложность LDPC декодеров растет линейно, что делает их более эффективными по площади и энергоэффективности, чем БЧХ декодеры. Дополнительным фактором в пользу выбора LDPC является высокая корректирующая способность: стандартный LDPC декодер (в отличие от БЧХ декодера), наряду с жёсткими решениями (‘0’ или ‘1’), получаемыми при чтении с носителя памяти, может использовать мягкие решения, представляющие собой вероятностные оценки (Log-Likelihood Ratio, LLR) для каждого бита хранимой информации, и получаемые путем чтения ячейки памяти с несколькими порогами чтения.

Недостатком применения LDPC кодов является большая аппаратная сложность для кодирования данных.

Техническим результатом заявленного изобретения является упрощение алгоритма вычисления кодового слова, обеспечивающего использование малого количества аппаратной логики.

Результат обеспечивается тем, что предлагается способ кодирования данных на основе LDPC кода, в котором для генерирования кодового слова используется проверочная матрица, которая содержит первую часть матрицы, относящуюся к исходным данным, и вторую часть матрицы, относящуюся к проверочным данным, при этом на главной диагонали второй части матрицы в нижней части располагаются циркулянты со сдвигом, равным нулю, а значения ячеек под главной диагональю второй части матрицы в этой же в нижней части равны нулю.

Применение такой проверочной матрицы позволит упростить процедуру кодирования.

Далее будет описано подробное осуществление изобретения.

Заявленный способ подразумевает использование LDPC кодера.

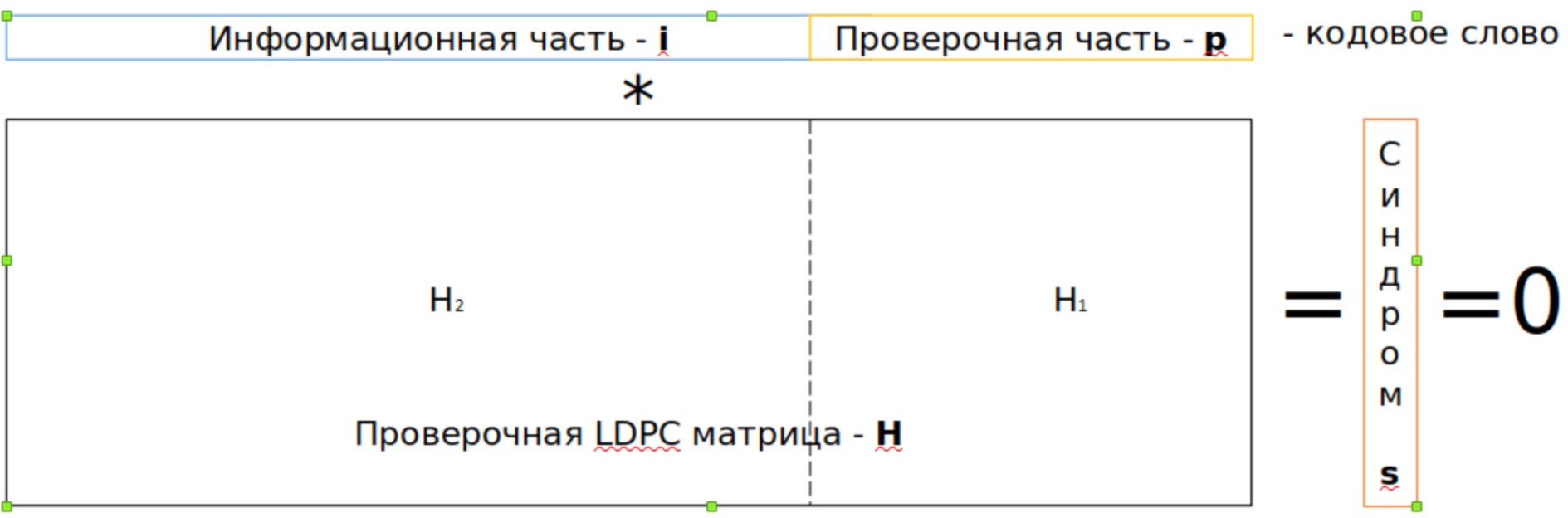

LDPC кодер кодирует поступающие данные блоками, также называемыми “кодовые слова”. Процесс кодирования заключается в добавлении к исходным данным некоторого количества дополнительных данных – проверочных данных, которые впоследствии используются декодером для проверки исправления ошибок. Таким образом, кодовое слово состоит из исходных данных — i и проверочных данных — p.

Конкретный LDPC код может быть задан несколькими способами, один из них — это проверочная матрица Н. Проверочная матрица двумерная, её длина равна длине кодового слова, если умножить эту матрицу на кодовое слово без ошибок, то получится нулевой вектор. Если же в кодовом слове есть ошибки, то получится ненулевой вектор s, называемый синдромом.

Исходя из того, что вектор синдромов должен быть равен нулю для кодового слова без ошибок, задача LDPC кодера состоит в построении проверочной части p на основе информационной части i и проверочной матрицы H.

Запишем условие равенства синдрома нулю в виде формулы:

H * (i, p) = s = 0

Разложим данное выражение в виде суммы:

H2* i + H1* p = 0

где H1 - часть проверочной матрицы, относящаяся к проверочным данным р, т.е. та часть матрицы Н, которая умножается на проверочные данные кодового слова для вычисления вектора матрицы;

а H2 – часть проверочной матрицы, относящаяся к исходным данным i, т.е. та часть матрицы Н, которая умножается на исходные данные кодового слова для вычисления вектора матрицы.

Перенесём одно слагаемое в правую часть и домножим обе части на H1-1, получим:

P = -H1-1 * H2 * i

Таким образом, вычисление проверочной части кодового слова сводится к двум умножениям вектора на матрицу.

Матрица H2 является низкоплотной, аппаратная реализация такого умножения достаточно проста, имеет низкую сложность и высокую скорость. Кроме того, обычно матрица H строится из ячеек (например, 128х128 или 512х512), каждая из которых либо содержит все нули, либо является единичной матрицей сдвинутой вправо на определённое количество позиций. Например, ячейка размера 4х4 сдвинутая на 1, будет выглядеть так:

Такие ячейки называют циркулянтами, а матрицы, состоящие из таких ячеек — квазициклическими. Умножение вектора на такую ячейку сводится к циклическому сдвигу всех элементов и имеет простую аппаратную реализацию.

Матрица H1-1, в свою очередь, является плотной матрицей, и умножение такой матрицы на вектор будет либо иметь большую аппаратную сложность, либо занимать длительное время. Для устранения этого недостатка матрица H1 строится таким образом, что в нижней части под главной диагональю расположены нули, а на диагонали расположены циркулянты со сдвигом, равным нулю.

Тогда для нижней строки (под строкой здесь будем понимать часть матрицы высотой равной размеру циркулянта) можно записать следующее условие равенства синдрома нулю:

где I — циркулянт с нулевым сдвигом, то есть единичная матрица, pn — блок проверочных бит с длиной, равной размеру циркулянта.

Таким образом, можно получить последний блок проверочных бит длины размера циркулянта без сложных вычислений: pn = – (H2 * i)n. Далее pn умножается на Cn и прибавляется к (H2 * i), тогда аналогично можно вычислить предпоследний блок проверочных бит:

pn–1 = – (H2 * i + Cn * pn)n–1

и так далее до:

pk = – (H2 * i + Ck+1..n * pk+1..n)k

Оставшаяся часть проверочных бит вычисляется умножением на обратную матрицу D–1, которая существенно меньше по размеру, чем H1–1:

p1..k–1 = – D–1 * (H2 * I + Ck..n * pk..n)1..k–1

Пример реализация способа

LDPC кодер содержит два основных модуля, которые реализуют упрощенный алгоритм вычисления проверочных бит.

Первый модуль вычисляет вектор синдромов, умножая проверочную матрицу H на входные данные i, а затем на проверочные данные pn..pk по мере их вычисления. Результат помещается в блок памяти Memory.

Второй модуль умножает вектор синдромов из блока памяти Memory на обратную матрицу H–1.

Для повышения эффективности обработки входных данных первый модуль представлен в двух экземплярах. Так второй экземпляр первого модуля может начать обработку следующего кодового слова, не дожидаясь завершения обработки pn..pk первым экземпляром первого модуля. Затем эти экземпляры меняются ролями. Для реализации данного функционала память, хранящая ячейки проверочной матрицы, разделена на 2 части – memH2 и memCT.

Второй модуль имеет параметр rwidth позволяющий умножать параллельно по несколько строк матрицы, что дает возможность увеличить скорость работы за счёт увеличения аппаратной сложности. Оптимальным вариантом является подбор этого параметра таким образом, чтобы время работы второго модуля было чуть меньше времени обработки первым модуле информационной части кодового слова, тогда все модули будут работать параллельно с минимальным простоем.

В режиме чтения информационных данных первый модуль осуществляет умножение части LDPC-матрицы H2 на вектор входных данных i. Результатом умножения является вектор синдромов s, записанный в промежуточную память Memory.

Алгоритм работы модуля в данном режиме следующий:

a) на вход модуля поступает очередной блок входных данных размером с ячейку матрицы;

b) считывается конфигурация очередной ячейки матрицы H2 из памяти, извлекается информация о номере строки ячейки, сдвиге циркулянта и о том, является ли ячейка последней в столбце;

c) считывается текущее значение синдрома из промежуточной памяти Memory с адресом, равным номеру строки ячейки;

d) считанное значение синдрома суммируется с блоком входных данных, домноженным на сдвинутый циркулянт и записывается обратно в память Memory по тому же адресу;

e) если ячейка не последняя в столбце, то происходит переход к пункту b);

f) если блоки входных данных не кончились, то происходит переход к пункту a);

g) когда блоки входных данных кончились, модуль переходит в режим поочередного вычисления проверочных ячеек.

В режиме вычисления проверочных ячеек первый модуль осуществляет умножение части LDPC-матрицы Ck..n на блоки проверочных бит pn..pk по мере их вычисления. Алгоритм работы отличается от режима работы при чтении исходных данных только тем, что первый модуль выдает текущее значение одной из ячеек синдрома по запросу LDPC-кодера, которое затем направляется на вход первого модуля, т.к. оно и является очередным вычисленным блоком проверочных бит.

Второй модуль осуществляет умножение вектора синдромов, посчитанного первым, на плотную матрицу Н-1 и работает по следующему алгоритму:

a) считывается очередной блок синдромов размера cell_size из промежуточной памяти Memory;

b) считывается часть столбца матрицы Н-1 из памяти, хранящая ячейки проверочной матрицы;

c) производится умножение считанной части столбца на rwidth бит блока синдромов, результат добавляется к соответствующей ячейке промежуточной памяти Memory;

d) если биты синдромов не закончились, то происходит переход к пункту b);

e) если столбцы не закончились, происходит переход к пункту a);

f) когда все столбцы обработаны, результаты из промежуточной памяти Memory подаются на выход;

Памяти, хранящие ячейки проверочной матрицы, имеют внешний интерфейс для загрузки ячеек проверочной матрицы, что позволяет при необходимости менять матрицу во время работы LDPC-кодера.

Реферат

Изобретение относится к области кодирования информации с использованием кодов с низкой плотностью проверок на четность (LDPC) и предназначено для обеспечения работы немеханических запоминающих устройств на основе микросхем памяти. Технический результат - упрощение алгоритма вычисления кодового слова, обеспечивающего использование малого количества аппаратной логики. Способ кодирования данных на основе LDPC кода, в котором для генерирования кодового слова, состоящего из исходных данных и проверочных данных, используется проверочная матрица, которая содержит первую часть матрицы, относящуюся к исходным данным, и вторую часть матрицы, относящуюся к проверочным данным, при этом на главной диагонали второй части матрицы в нижней части располагаются циркулянты со сдвигом, равным нулю, а значения ячеек под главной диагональю второй части матрицы в этой же нижней части равны нулю.

Формула

Документы, цитированные в отчёте о поиске

Устройство и способ кодирования-декодирования блочного кода проверки на четность с низкой плотностью с переменной длиной блока

Устройство кодирования, способ конфигурирования кода с исправлением ошибок и программа для них

Способ кодирования кода разреженного контроля четности

Способ для выполнения кодирования на основе матрицы контроля по четности ldpc-кода в системе беспроводной связи и терминал с его использованием

Устройство и способ для генерирования матрицы проверки четности в системе связи с использованием линейных блочных кодов и устройство передачи/приема и способ для использования этого

Устройство и способ для кодирования и декодирования блочных кодов с низкой плотностью контроля по четности с переменной скоростью кодирования

Комментарии