Устройство и способ для кодирования и декодирования блочных кодов с низкой плотностью контроля по четности с переменной скоростью кодирования - RU2354045C2

Код документа: RU2354045C2

Чертежи

Описание

Область техники, к которой относится изобретение

Настоящее изобретение относится, в общем, к системе мобильной связи и, в частности, к устройству и способу для кодирования и декодирования блочных кодов с низкой плотностью контроля по четности (LDPC-кодов), обладающих переменной скоростью кодирования.

Уровень техники

В условиях быстрого развития мобильных систем связи необходимо разрабатывать технологию, способную к передаче больших массивов данных с приближением к пропускной способности проводной сети даже в беспроводной среде. Для удовлетворения растущей потребности в высокоскоростной высокопроизводительной системе связи, способной обрабатывать и передавать разнообразные данные, например, изображения и радиоданные, помимо службы речевой связи важно повысить эффективность передачи системы путем применения соответствующей схемы канального кодирования для повышения тем самым общей производительности системы. Однако мобильная система связи вследствие ее характеристик неизбежно порождает ошибки во время передачи данных в результате шумов, помех и затухания в зависимости от состояния канала. Порождение ошибок вызывает потерю большого количества информационных данных.

Для предотвращения потери информационных данных из-за порождения ошибок в настоящее время применяют разнообразные схемы защиты от ошибок, частично основанные на характеристиках канала, для повышения, тем самым, надежности мобильной системы связи. Наиболее характерная схема защиты от ошибок использует коды с коррекцией ошибок.

На фиг.1 представлена схема, иллюстрирующая структуру передатчика/приемника в традиционной системе мобильной связи. Как видно из фиг.1, передатчик 100 содержит кодер 111, модулятор 113 и радиочастотный (RF) процессор 115, и приемник 150 содержит RF-процессор 151, демодулятор 153 и декодер 155.

В передатчике 100 передаваемые информационные данные «u» после их генерации подаются в кодер 111. Кодер 111 формирует кодированный символ «c» кодированием информационных данных «u» по заданной схеме кодирования и выдает кодированный символ «c» в модулятор 113. Модулятор 113 формирует модулированный символ «s» модулированием кодированного символа «c» по заданной схеме модуляции и выдает модулированный символ «s» в RF-процессор 115. RF-процессор 115 выполняет радиочастотную (RF) обработку модулированного символа «s», выданного модулятором 113, и передает RF-обработанный сигнал в эфир через антенну ANT.

Сигнал, передаваемый в эфир передатчиком 100 описанным способом, принимается в приемник 150 посредством его антенны ANT, и сигнал, принятый антенной, подается в RF-процессор 151. RF-процессор 151 выполняет RF-обработку принятого сигнала и выдает RF-обработанный сигнал «r» в демодулятор 153. Демодулятор 153 демодулирует RF-обработанный сигнал «r», выданный из RF-процессора 151, с применением схемы демодуляции, соответствующей схеме модуляции, применяемой в модуляторе 113, и выдает демодулированный сигнал «x» в декодер 155. Декодер 155 декодирует демодулированный сигнал «x», выданный из демодулятора 153, с применением схемы декодирования, соответствующей схеме кодирования, применяемой в кодере 111, и выдает декодированный сигнал «

Чтобы приемник 150 безошибочно декодировал информационные данные «u», переданные передатчиком 100, требуются высокопроизводительные кодер и декодер. В частности, так как необходимо учитывать среду радиоканала из-за характеристик мобильной системы связи, следует более внимательно учитывать ошибки, которые могут порождаться воздействием среды радиоканала.

К наиболее характерным кодам с коррекцией ошибок относятся турбокоды и коды с низкой плотностью контроля по четности (LDPC-коды).

Общеизвестно, что турбокод превосходит по выигрышу в производительности сверточный код, который обычно применяют для коррекции ошибок во время высокоскоростной передачи данных. Турбокод обладает таким преимуществом, что может эффективно исправить ошибку, вызванную шумом, создаваемым в канале передачи и, тем самым, повысить надежность передачи данных. LDPC-код можно декодировать с применением итеративного декодирующего алгоритма суммы-произведения в фактор-графе. Так как декодер для LDPC-кода использует итеративный декодирующий алгоритм на основе алгоритма суммы-произведения, то он менее сложен, чем декодер для турбо-кода. Кроме того, декодер для LDPC-кода легче реализуем декодером параллельной обработки по сравнению с декодером турбо-кода.

Теорема Шеннона о канальном кодировании показывает, что надежная связь возможна только со скоростью передачи данных, не превышающей пропускную способность канала связи. Однако теорема Шеннона о канальном кодировании не предлагает детализированного способа канального кодирования/декодирования для поддержки скорости передачи данных на уровне вплоть до максимального предела пропускной способности канала связи. Как правило, хотя случайный код с очень большой длиной блоков характеризуется производительностью, приближающейся к предельной пропускной способности канала связи по теореме Шеннона о канальном кодировании, когда применяют способ декодирования MAP (по максимальной апостериорной вероятности) или ML (по максимальной вероятности), реализовать способ декодирования фактически невозможно ввиду большого объема связанных с ним вычислений.

Турбокод предложен авторами Берроу (Berrou), Главе (Glavieux) и Титимадзима в 1993 г. и показывает высокую производительность, которая приближается к предельной пропускной способности канала связи по теореме Шеннона о канальном кодировании. Предложение турбокода явилось толчком к активным исследованиям итеративного декодирования и графического выражения кодов, и в центре внимания исследований вновь оказались LDPC-коды, предложенные Галагером (Gallager) в 1962 г. В фактор-графе турбокода и LDPC-кода присутствуют циклы, и общеизвестно, что итеративное декодирование в фактор-графе LDPC-кода, в котором существуют циклы, является близким к оптимальному. Кроме того, экспериментально доказано, что LDPC-код обладает высокой производительностью при итеративном декодировании. Известно, что LDPC-код, обладающий максимальной производительностью, всегда показывает характеристики с разностью, приблизительно, 0,04 [дБ] на предельной пропускной способности канала по теореме Шеннона о канальном кодировании, при частоте появления ошибочных битов (BER) 10-5, с использованием блоков с размером 107. Кроме того, хотя LDPC-код, определенный в поле Галуа (GF) с q>2, т.е. GF(q), усложняется с точки зрения процесса его декодирования, он намного превосходит двоичный код по производительности. Однако удовлетворительного теоретического описания успешного декодирования по итеративному декодирующему алгоритму для LDPC-кода, определенного в GF(q), не существует.

LDPC-код, предложенный Галлагером, определен при посредстве матрицы контроля по четности, в которой основные элементы имеют значение 0, и неосновные элементы, кроме элементов, имеющих значение 0, имеют ненулевое значение, например, значение 1. В последующем описании будет принято, что ненулевое значение равно значению 1.

Например, LDPC-код (N, j, k) является линейным блочным кодом с длиной N блока и определен разреженной матрицей контроля по четности, в которой каждый столбец содержит j элементов со значением 1, каждая строка содержит k элементов со значением 1, и все элементы, кроме элементов со значением 1, имеют значение 0.

LDPC-код, в котором вес каждого столбца в матрице контроля по четности имеет фиксированное значение «j», и вес каждой строки в матрице контроля по четности имеет фиксированное значение «k», как описано выше, называется «регулярным LDPC-кодом». В данном случае, термин «вес» относится к числу элементов с ненулевым значением среди элементов, составляющих матрицу контроля по четности. В отличие от регулярного LDPC-кода LDPC-код, в котором вес каждого столбца в матрице контроля по четности и вес каждой строки в матрице контроля по четности не фиксированы, называется «иррегулярным LDPC-кодом». Общеизвестно, что иррегулярный LDPC-код превосходит регулярный LDPC-код по производительности. Однако в случае иррегулярного LDPC-кода, поскольку вес каждого столбца и вес каждой строки в матрице контроля по четности не фиксированы, т.е. являются иррегулярными, вес каждого столбца в матрице контроля по четности и вес каждой строки в матрице контроля по четности должны подвергаться надлежащей коррекции, чтобы гарантировать превосходящую производительность.

На фиг.2 представлена схема, иллюстрирующая матрицу контроля по четности обычного LDPC-кода (8, 2, 4). Как видно из фиг.2, матрица H контроля по четности LDPC-кода (8, 2, 4) состоит из 8 столбцов и 4 строк, в которой вес каждого столбца имеет фиксированное значение 2, и вес каждой строки имеет фиксированное значение 4. Поскольку вес каждого столбца и вес каждой строки в матрице контроля по четности являются регулярными, как указано выше, LDPC-код (8, 2, 4), показанный на фиг.2, становится регулярным LDPC-кодом.

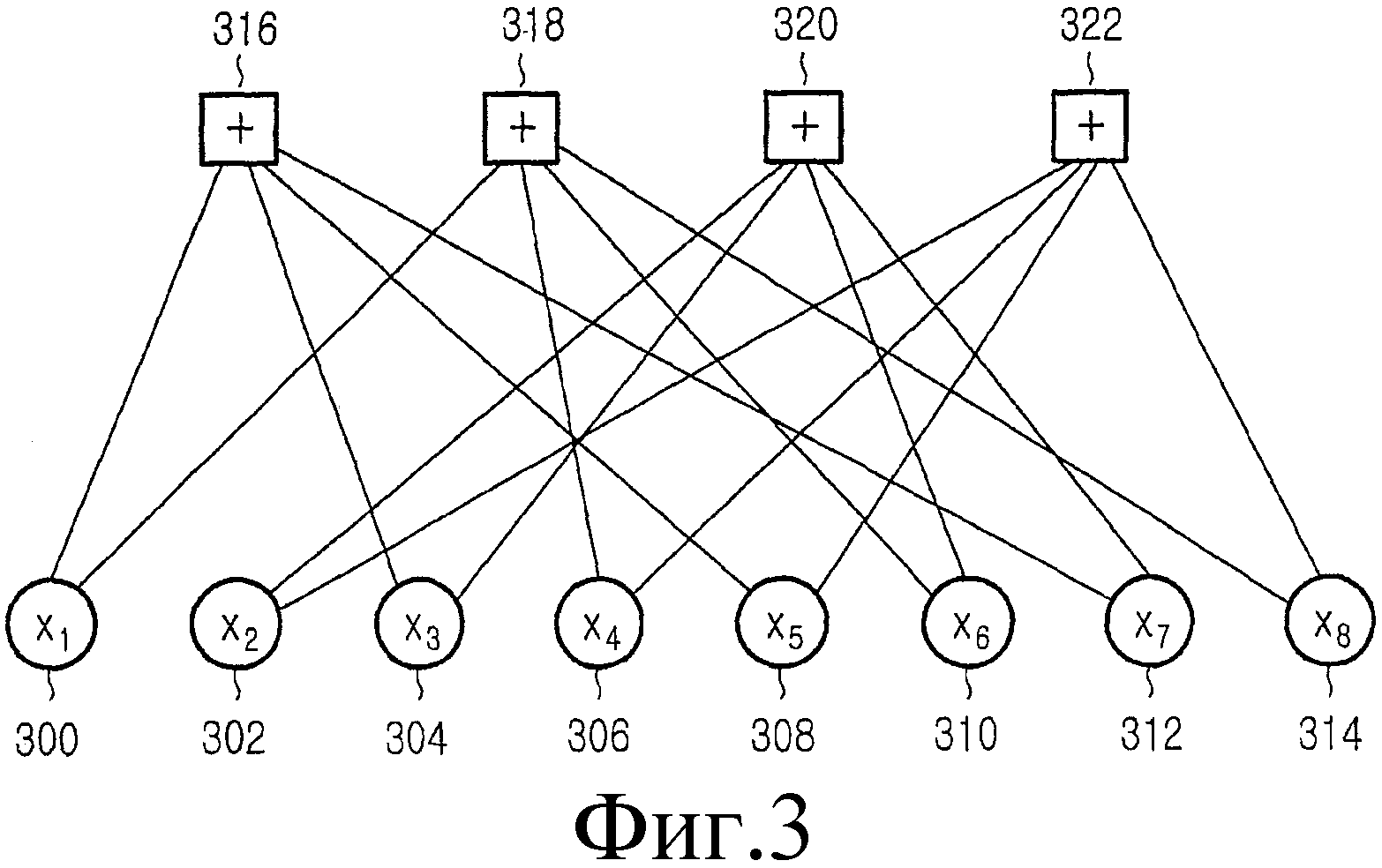

На фиг.3 представлена схема, иллюстрирующая фактор-граф LDPC-кода (8, 2, 4), показанного на фиг.2. Как видно из фиг.3, фактор-граф LDPC-кода (8, 2, 4), состоит из 8 переменных вершин x1 300, x2 302, x3 304, x4 306, x5 308, x6 310, x7 312 и x8 314 и 4 проверочных вершин 316, 318, 320 и 322. Когда элемент со значением 1, т.е. ненулевым значением, присутствует в точке, где пересекаются i-тая строка и j-тый столбец матрицы контроля по четности LDPC-кода (8, 2, 4), создается ветвь между переменной вершиной xj и j-й проверочной вершиной.

Поскольку матрица контроля по четности LDPC-кода имеет очень малый вес, как описано выше, то декодирование можно выполнить итеративным декодированием даже в блочном коде, имеющим относительно большую длину, который имеет производительность, приближающуюся к предельной пропускной способности канала связи по теореме Шеннона о канальном кодировании, например, в турбокоде, при непрерывном увеличении длины блока блочного кода. Мак-Кей (MacKay) и Нил (Neal) показали, что итеративный процесс декодирования LDPC-кода с использованием схемы передачи потока приближается по производительности к итеративному декодированию турбокода.

Для генерации высокоэффективного LDPC-кода необходимо выполнить следующие условия.

(1) Следует рассмотреть циклы на фактор-графе LDPC-кода.

Термин «цикл» относится к петле, образованной ребрами, соединяющими переменные вершины с проверочными вершинами в фактор-графе LDPC-кода, и длина цикла определяется как число ребер, составляющих петлю. Длинный цикл означает большое число ребер, соединяющих переменные вершины с проверочными вершинами и составляющих петлю в фактор-графе LDPC-кода. Напротив, короткий цикл означает небольшое число ребер, соединяющих переменные вершины с проверочными вершинами и составляющих петлю в фактор-графе LDPC-кода.

Когда циклы в фактор-графе LDPC-кода становятся длиннее, эффективность действия LDPC-кода возрастает по следующим причинам. То есть, когда в фактор-графе LDPC-кода формируются длинные циклы, можно предотвратить снижение производительности, например, появление минимального уровня ошибок, когда на фактор-графе LDPC-кода присутствует слишком много циклов небольшой длины.

(2) Следует рассмотреть эффективное кодирование LDPC-кода.

LDPC-код с большим трудом поддается кодированию в реальном времени в сравнении со сверточным кодом или турбокодом ввиду высокой сложности его кодирования. Чтобы снизить сложность кодирования LDPC-кода, предложен код с повторением и накоплением (RA-код). Однако RA-код ограничен по снижению сложности кодирования LDPC-кода. Поэтому следует принять во внимание эффективное кодирование LDPC-кода.

(3) Следует рассмотреть распределение степеней в фактор-графе LDPC-кода.

Иррегулярный LDPC-код, как правило, превосходит по производительности регулярный LDPC-код, поскольку фактор-граф LDPC-кода обладает различными степенями. Термин «степень» относится к числу ребер, соединенных с переменными вершинами и проверочными вершинами в фактор-графе LDPC-кода. Кроме того, формулировка «распределение степеней» на фактор-графе LDPC-кода относится к отношению числа вершин с конкретной степенью к общему числу вершин. Как показано Ричардсоном (Richardson), LDPC-код с особым распределением степеней обладает особенно высокой производительностью.

На фиг.4 представлена схема, иллюстрирующая матрицу контроля по четности традиционного блочного LDPC-кода. До описания фиг.4 следует отметить, что блочный LDPC-код является новым LDPC-кодом, для которого рассмотрены вопросы не только эффективного кодирования, но также эффективного хранения и повышения производительности матрицы контроля по четности, и блочный LDPC-код является LDPC-кодом, расширенным обобщением структуры регулярного LDPC-кода. Как видно из фиг.4, матрица контроля по четности блочного LDPC-кода разбита на множество частичных блоков, и перестановочная матрица отображается в каждый из частичных блоков. На фиг.4 «P» представляет перестановочную матрицу с размерностью Ns×Ns, и верхний индекс (или порядок) apq перестановочной матрицы P составляет либо 0 ≤ apq ≤ Ns-1, либо apq=∞.

Кроме того, «p» указывает, что соответствующая перестановочная матрица расположена в p-той строке частичных блоков матрицы контроля по четности, и «q» указывает, что соответствующая перестановочная матрица расположена в q-ом столбце частичных блоков матрицы контроля по четности. То есть,

На фиг.5 представлена схема, иллюстрирующая перестановочную матрицу P, показанную на фиг.4. Как показано на фиг.5, перестановочная матрица P является квадратной матрицей с размерностью Ns×Ns, и каждый из Ns столбцов, составляющих перестановочную матрицу P, имеет вес 1, и каждая из Ns строк, составляющих перестановочную матрицу P, также имеет вес 1. В настоящем описании, хотя размерность перестановочной матрицы P выражена в виде Ns×Ns, она будет также выражаться в виде Ns, поскольку перестановочная матрица P является квадратной матрицей.

На фиг.4 перестановочная матрица P с верхним индексом apq=0, т.е. перестановочная матрица P0, представляет собой единичную матрицу

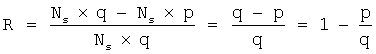

В полной матрице контроля по четности блочного LDPC-кода, показанной на фиг. 4, поскольку общее число строк равно Ns×p, и общее число столбцов равно Ns×q (при p ≤ q), когда полная матрица контроля по четности блочного LDPC-кода имеет полный ранг, скорость кодирования можно выразить уравнением (1), независимо от размера частичных блоков.

Если apq≠∞ для всех p и q, перестановочные матрицы, соответствующие частичным блокам, не равны нулевым матрицам, и частичные блоки составляют регулярный LDPC-код, в котором весовое значение каждого столбца и весовое значение каждой строки в каждой из перестановочных матриц, соответствующих частичным блокам равны, соответственно, p и q. В настоящем описании, каждая из перестановочных матриц, соответствующих частичным блокам, будет упоминаться как «частичная матрица».

Так как в полной матрице контроля по четности существует (p-1) зависимых строк, скорость кодирования выше, чем скорость кодирования, вычисленная по уравнению (1). В случае блочного LDPC-кода, если определена весовая позиция первой строки каждой из частичных матриц, составляющих полную матрицу контроля по четности, то можно определить весовые позиции остальных (Ns-1) строк. Поэтому потребный размер памяти уменьшается до 1/Ns по сравнению со случаями, когда веса выбираются нерегулярно для хранения информации о полной матрице контроля по четности.

Как упоминалось выше, термин «цикл» относится к петле, сформированной ребрами, соединяющими переменные вершины с проверочными вершинами в фактор-графе LDPC-кода, и длина цикла определяется как число ребер, составляющих петлю. Длинный цикл предполагает большое число ребер, соединяющих переменные вершины с проверочными вершинами и составляющих петлю в фактор-графе LDPC-кода. Когда циклы в фактор-графе LDPC-кода становятся длиннее, эффективность действия LDPC-кода возрастает.

Напротив, когда циклы в фактор-графе LDPC-кода становятся короче, способность LDPC-кода к коррекции ошибок уменьшается из-за снижения производительности, например, появления минимального уровня ошибок. То есть, когда существует много циклов с короткой длиной в фактор-графе LDPC-кода, информация о конкретной вершине, принадлежащей циклу с короткой длиной, начиная с нее, возвращается после небольшого числа итераций. Когда число итераций возрастает, информация возвращается к соответствующей вершине более часто, так что информацию невозможно правильно корректировать, что вызывает снижение способности LDPC-кода к коррекции ошибок.

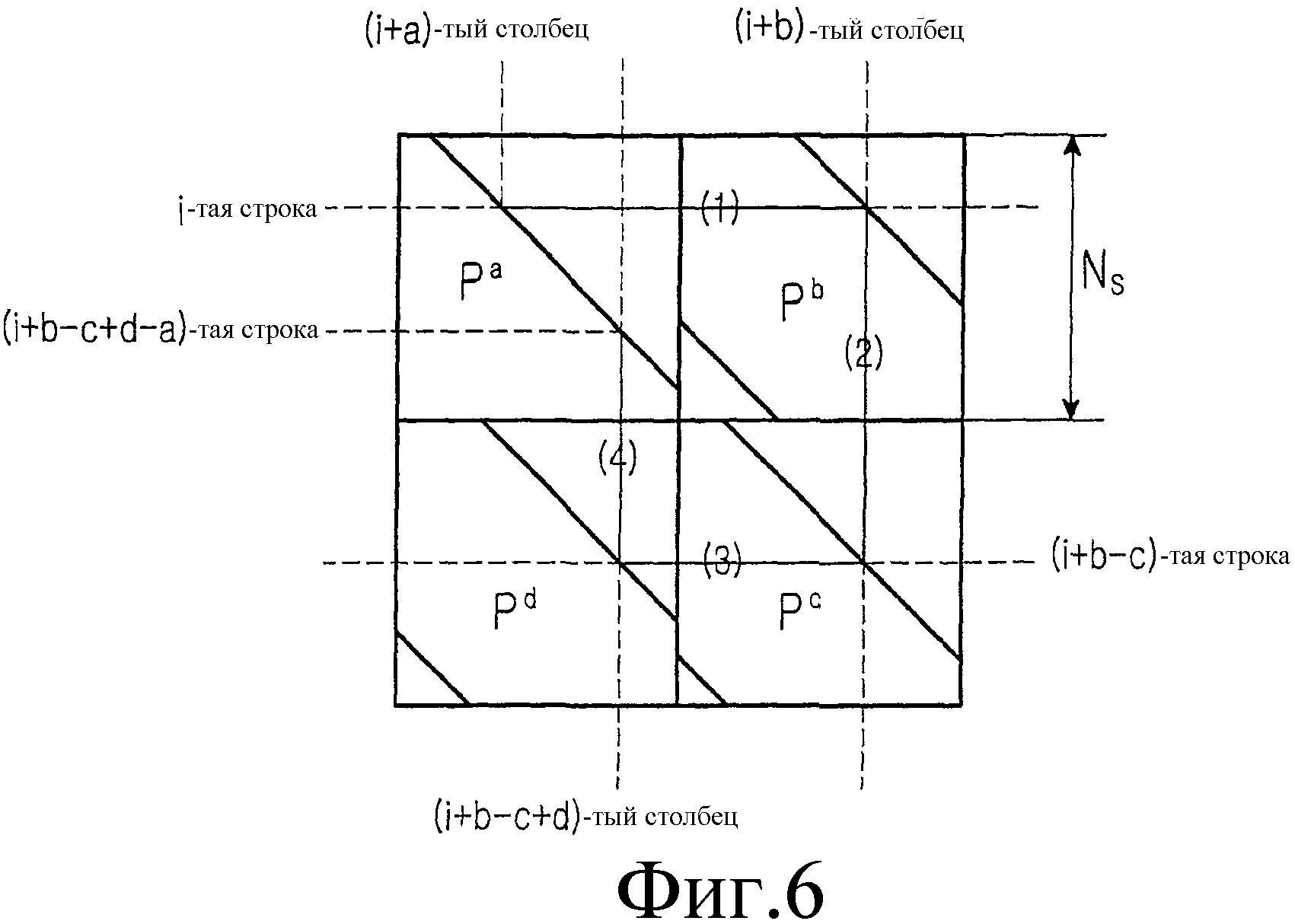

На фиг.6 представлена схема, иллюстрирующая циклическую структуру блочного LDPC-кода, матрица контроля по четности которого состоит из 4 частичных матриц. Перед описанием фиг.6 следует отметить, что блочный LDPC-код является новым LDPC-кодом, для которого рассмотрены вопросы не только эффективного кодирования, но также эффективного хранения и повышения производительности матрицы контроля по четности. Блочный LDPC-код является также LDPC-кодом, расширенным обобщением структуры регулярного LDPC-кода. Матрица контроля по четности блочного LDPC-кода, показанная на фиг.6, состоит из 4 частичных блоков, при этом диагональная линия представляет позицию, в которой расположены элементы со значением 1, и участки, отличающиеся от диагонально линованных участков, представляют позиции, в которых расположены элементы со значение 0. Кроме того, «P» представляет такую же перестановочную матрицу, что и перестановочная матрица, описанная в связи с фиг.5.

Для анализа циклической структуры блочного LDPC-кода, показанной на фиг.6, элемент со значением 1, расположенный в I-той строке частичной матрицы Pa, определяется как опорный элемент, и элемент со значением 1, расположенный в i-той строке, будет именоваться «точкой-0». В настоящем описании «частичной матрицей» будет именоваться матрица, соответствующая частичному блоку. Точка-0 расположена в (i+a)-ом столбце частичной матрицы Pa.

Элемент со значением 1 в частичной матрице Pb, расположенный в той же строке, что и точка-0, будет именоваться «точкой-1». По той же причине, что и точка-0, точка-1 расположена в (i+b)-ом столбце частичной матрицы Pb.

Затем элемент со значением 1 в частичной матрице Pc, расположенный в том же столбце, что и точка-1, будет именоваться «точкой-2». Так как частичная матрица Pc является матрицей, получаемой сдвигом соответствующих столбцов единичной матрицы I вправо по модулю Ns на c, точка-2 расположена в (i+b-c)-той строке частичной матрицы Pc.

Кроме того, элемент со значением 1 в частичной матрице Pd, расположенный в той же строке, что и точка-2, будет именоваться «точкой-3». Точка-3 расположена в (i+b-c+d)-ом столбце частичной матрицы Pd.

И, наконец, элемент со значением 1 в частичной матрице Pa, расположенный в том же столбце, что и точка-3, будет именоваться «точкой-4». Точка-4 расположена в (i+b-c+d-a)-той строке частичной матрицы Pa.

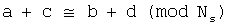

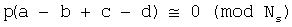

В циклической структуре блочного LDPC-кода, показанной на фиг.6, если существует цикл длиной 4, точка-0 и точка-4 расположены в одной позиции. То есть, зависимость между точкой-0 и точкой-4 определяется уравнением (2)

Уравнение (2) можно переписать в форме уравнения (3)

В результате, когда выполняется соотношение, заданное уравнением (3), формируется цикл длиной 4. Как правило, когда точка-0 и точка-4p становятся в первый раз идентичными друг другу, получается соотношение

Другими словами, если положительное целое число, имеющее минимальное значение из положительных целых чисел, удовлетворяющих уравнению (4) для данных a, b, c и d, определить как «p», то цикл с длиной 4p становится циклом с минимальной длиной в циклической структуре блочного LDPC-кода, показанной на фиг.6.

В заключение, как описано выше, для (a-b+c-d)≠0, если выполняется условие gcd(Ns, a-b+c-d)=1, то p = Ns. В настоящем описании, gcd(Ns, a-b+c-d) является функцией для вычисления «наибольшего общего делителя» (gcd) целых чисел Ns и a-b+c-d. Поэтому цикл с длиной 4Ns становится циклом с минимальной длиной.

В качестве способа кодирования для блочного LDPC-кода будет применяться способ Ричардсона - Урбанке (Richardson-Urbanke). Поскольку в качестве способа кодирования применяется способ Ричардсона - Урбанке, сложность кодирования можно минимизировать, когда форма матрицы контроля по четности становится аналогичной форме полной нижнетреугольной матрицы.

На фиг.7 приведена схема, иллюстрирующая матрицу контроля по четности, имеющую форму, схожую с формой полной нижнетреугольной матрицы. Матрица контроля по четности, показанная на фиг.7, отличается от матрицы контроля по четности, имеющей форму полной нижнетреугольной матрицы в форме части контроля по четности. На фиг.7 верхний индекс (или порядок) apq перестановочной матрицы P информационной части составляет либо 0 ≤ apq ≤ Ns-1, либо apq=∞, как описано выше. Перестановочная матрица P с верхним индексом apq=1, т.е. перестановочная матрица P0 информационной части, представляет собой единичную матрицу

Самая серьезная проблема для LDPC-кода, обладающего матрицей контроля по четности, показанной на фиг.7, состоит в том, что, если длина частичного блока определена как Ns, то формируется Ns проверочных вершин, степени которых всегда равны 1 в фактор-графе блочного LDPC-кода. Проверочные вершины со степенью 1 не могут влиять на совершенствование производительности на основе итеративного декодирования. Поэтому стандартный иррегулярный LDPC-код на базе способа Ричардсона - Урбанке не содержит проверочной вершины со степенью 1. Поэтому матрица контроля по четности, показанная на фиг.7, будет принята в качестве базовой матрицы контроля по четности для создания такой матрицы контроля по четности, что она обеспечивает возможность эффективного кодирования, несмотря на отсутствие проверочной вершины со степенью 1. В матрице контроля по четности, показанной на фиг.7, состоящей из частичных матриц, выбор частичной матрицы является очень важным фактором для совершенствования производительности блочного LDPC-кода, так что очень важным фактором становится также определение подходящего критерия выбора частичной матрицы.

Для облегчения способа создания матрицы контроля по четности блочного LDPC-кода и способа кодирования блочного LDPC-кода предполагается, что матрица контроля по четности, показанная на фиг.7, выполнена с 6 частичными матрицами, как показано на фиг.8.

На фиг.8 представлена схема, иллюстрирующая матрицу контроля по четности, показанную на фиг.7, которая разбита на 6 частичных блоков. Как видно из фиг.8, матрица контроля по четности блочного LDPC-кода, показанная на фиг.7, разбита на информационную часть «s», первую часть p1 контроля по четности и вторую часть p2 контроля по четности. Информационная часть «s» представляет собой часть матрицы контроля по четности, отображаемую в фактическое информационное слово в процессе кодирования блочного LDPC-кода, подобно информационной части, описанной в связи с фиг.7, но, для удобства объяснения, информационная часть «s» представлена отличающимися условными обозначениями. Первая часть p1 контроля по четности и вторая часть p2 контроля по четности представляют собой часть матрицы контроля по четности, отображаемую в фактическое контрольное слово в процессе кодирования блочного LDPC-кода, подобно части контроля по четности, описанной в связи с фиг.7, и часть контроля по четности разбита на две части.

Частичные матрицы A и C соответствуют частичным блокам A (802) и C (804) информационной части «s», частичные матрицы B и D соответствуют частичным блокам B (806) и D (808) первой части p1 контроля по четности, и частичные матрицы T и E соответствуют частичным блокам T (810) и E (812) второй части p2 контроля по четности. Хотя, на фиг. 8 матрица контроля по четности разбита на 7 частичных блоков, следует отметить, что «0» не является отдельным частичным блоком, и, поскольку частичная матрица T, соответствующая частичному блоку T (810), имеет полную нижне-треугольную форму, участок, где нулевые матрицы расположены на основе диагонали, обозначен «0». Процесс упрощения способа кодирования с использованием частичных матриц информационной части «s», первой части p1 контроля по четности и второй части p2 контроля по четности описан ниже со ссылкой на фиг.10.

На фиг.9 представлена схема, иллюстрирующая транспонированную матрицу частичной матрицы B, показанной на фиг.8, частичную матрицу E, частичную матрицу T и обратную матрицу частичной матрицы T из матрицы контроля по четности, показанной на фиг.7. Как видно из фиг.9, частичная матрица BT представляет собой транспонированную матрицу частичной матрицы B, и частичная матрица T-1 представляет собой обратную матрицу частичной матрицы T.

Перестановочные матрицы, показанные на фиг. 9, например,

На фиг.10 представлена блок-схема процедуры создания матрицы контроля по четности традиционного блочного LDPC-кода. До описания фиг.10 следует отметить, что для генерации блочного LDPC-кода необходимо определить длину кодового слова и скорость кодирования блочного LDPC-кода, подлежащего генерации, и необходимо определить размерность матрицы контроля по четности в зависимости от установленных длины кодового слова и скорости кодирования. Если длину кодового слова блочного LDPC-кода обозначить N и скорость кодирования обозначить R, то размерность матрицы контроля по четности становится N(1-R)×N. Фактически, процедура создания матрицы контроля по четности блочного LDPC-кода, показанная на фиг.10, выполняется только один раз, так как матрица контроля по четности с самого начала создается, чтобы соответствовать ситуации системы связи, и созданная матрица контроля по четности применяется впоследствии.

Как видно из фиг.10, на этапе 1011 контроллер разбивает матрицу контроля по четности с размерностью N(1-R)×N всего на p×q блоков с p блоками по горизонтальной оси и q блоками по вертикальной оси и затем переходит к этапу 1013. Поскольку каждый из блоков имеет размерность Ns×Ns, матрица контроля по четности состоит из Ns×p столбцов и Ns×q строк. На этапе 1013 контроллер классифицирует p×q блоков, получаемых разбиением матрицы контроля по четности, на информационную часть «s», первую часть p1 контроля по четности и вторую часть p2 контроля по четности и затем переходит к этапам 1015 и 1021.

На этапе 1015 контроллер разбивает информационную часть «s» на ненулевые блоки или ненулевые матрицы и нулевые блоки или нулевые матрицы в зависимости от степени распределения для гарантированной высокой производительности блочного LDPC-кода и затем переходит к этапу 1017. Поскольку степень распределения для гарантированной высокой производительности блочного LDPC-кода описана выше, здесь не дается подробного описания распределения. На этапе 1017 контроллер определяет перестановочные матрицы

На этапе 1019 контроллер случайным образом определяет перестановочные матрицы

На этапе 1021 контроллер разбивает первую часть p1 контроля по четности и вторую часть p2 контроля по четности на 4 частичных матрицы B, T, D и E и затем переходит к этапу 1023. На этапе 1023 контроллер вводит ненулевые перестановочные матрицы Py и

На этапе 1025 контроллер вводит единичные матрицы I в диагональные частичные блоки частичной матрицы T, вводит отдельные перестановочные матрицы

На этапе 1027 контроллер вводит частичную матрицу Px в частичную матрицу D и затем переходит к этапу 1029. На этапе 1029 контроллер вводит перестановочную матрицу

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Как изложено выше, известно, что LDPC-код вместе с турбокодом дает большой выигрыш в производительности во время высокоскоростной передачи данных и эффективно корректирует ошибку, вызываемую шумами, порожденными в канале передачи, чем способствует повышению надежности передачи данных. Однако LDPC-код характеризуется недостатком с точки зрения скорости кодирования. То есть, так как LDPC-код характеризуется относительно высокой скоростью кодирования, он имеет ограничение по скорости кодирования. Среди существующих в настоящее время LDPC-кодов основные LDPC-коды имеют скорость кодирования 1/2, и только второстепенные LDPC-коды имеют скорость кодирования 1/3. Ограничение по скорости кодирования катастрофически сказывается на высокоскоростной высокопроизводительной передаче данных. Хотя, с использованием схемы с изменением плотности можно вычислить распределение степеней, представляющее наивысшую производительность, для реализации сравнительно низкой скорости кодирования LDPC-кода, реализация LDPC-кода с распределением степеней, представляющим наивысшую производительность, является сложной задачей ввиду различных ограничений, например, циклической конструкции в фактор-графе и исполнения аппаратных средств.

При разработке мобильной системы связи используют разнообразные схемы, например комбинированный автоматический запрос на повторную передачу (HARQ) и адаптивную модуляцию и кодирование (AMC), для повышения эффективности ресурса. Для применения схем HARQ и AMC, LDPC-коды должны обладать способностью к поддержке различных скоростей кодирования. Однако, так как LDPC-коды ограничены с точки зрения скорости кодирования, как упоминалось выше, LDPC-кодам сложно поддерживать различные скорости кодирования.

Кроме того, для применения схемы HARQ необходимо создать LDPC-коды, обладающие различными скоростями кодирования и использующие один кодер. Соответственно, существует потребность в схеме, допускающей создание LDPC-кодов, обладающих различными скоростями кодирования и использующих один кодер.

Поэтому целью настоящего изобретения является создание устройства и способа для кодирования и декодирования LDPC-кода, обладающего переменной скоростью кодирования в мобильной системе связи.

Другой целью настоящего изобретения является создание устройства и способа для кодирования и декодирования LDPC-кода, обладающего переменной скоростью кодирования, сложность кодирования которого сведена к минимуму, в мобильной системе связи.

В соответствии с одним аспектом настоящего изобретения предлагается способ кодирования блочного кода с низкой плотностью контроля по четности (LDPC-кода), обладающего переменной скоростью кодирования. Способ содержит этапы, состоящие в том, что принимается информационное слово; и информационное слово кодируется в блочный LDPC-код на базе одной из первой матрицы контроля по четности и второй матрицы контроля по четности, в зависимости от скорости кодирования, подлежащей применению при формировании информационного слова в блочный LDPC-код.

В соответствии с другим аспектом настоящего изобретения предлагается устройство для кодирования блочного кода с низкой плотностью контроля по четности (LDPC-кода), обладающего переменной скоростью кодирования. Устройство содержит кодер для кодирования информационного слова в блочный LDPC-код на базе одной из первой матрицы контроля по четности и второй матрицы контроля по четности, в зависимости от скорости кодирования, подлежащей применению при формировании информационного слова в блочный LDPC-код; модулятор для модуляции блочного LDPC-кода в модулированный символ с использованием схемы модуляции; и передатчик для передачи модулированного символа.

В соответствии с дополнительным другим аспектом настоящего изобретения предлагается способ декодирования блочного кода с низкой плотностью контроля по четности (LDPC-кода), обладающего переменной скоростью кодирования. Способ содержит этапы, состоящие в том, что принимается сигнал; определяется одна из первой матрицы контроля по четности и второй матрицы контроля по четности в зависимости от скорости кодирования блочного LDPC-кода, подлежащего декодированию; и принятый сигнал декодируется в зависимости от вышеопределенной матрицы контроля по четности для детектирования блочного LDPC-кода.

В соответствии с еще одним аспектом настоящего изобретения предлагается устройство для декодирования блочного кода с низкой плотностью контроля по четности (LDPC-кода), обладающего переменной скоростью кодирования. Устройство содержит приемник для приема сигнала и декодер для определения одной из первой матрицы контроля по четности и второй матрицы контроля по четности в зависимости от скорости кодирования блочного LDPC-кода, подлежащего декодированию, и для декодирования принятого сигнала в зависимости от вышеопределенной матрицы контроля по четности для детектирования блочного LDPC-кода.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Вышеперечисленные и другие цели, признаки и преимущества настоящего изобретения станут очевидны из рассмотрения нижеприведенного подробного описания совместно с прилагаемыми чертежами, на которых:

Фиг.1 - схема, иллюстрирующая передатчик/приемник в традиционной системе мобильной связи;

Фиг.2 - схема, иллюстрирующая матрицу контроля по четности обычного LDPC-кода (8, 2, 4);

Фиг.3 - схема, иллюстрирующая фактор-граф LDPC-кода (8, 2, 4), показанного на фиг.2;

Фиг.4 - схема, иллюстрирующая матрицу контроля по четности обычного блочного LDPC-кода;

Фиг.5 - схема, иллюстрирующая перестановочную матрицу P с фиг.4;

Фиг.6 - схема, иллюстрирующая циклическую структуру блочного LDPC-кода, у которого матрица контроля по четности состоит из 4 частичных матриц;

Фиг.7 - схема, иллюстрирующая матрицу контроля по четности, имеющую форму, аналогичную форме полной нижнетреугольной матрицы;

Фиг.8 - схема, иллюстрирующая матрицу контроля по четности с фиг.7, которая разбита на 6 частичных блоков;

Фиг.9 - схема, иллюстрирующая транспонированную матрицу частичной матрицы B, показанной на фиг.8, частичную матрицу E, частичную матрицу T и обратную матрицу частичной матрицы T;

Фиг.10 - блок-схема последовательности операций, иллюстрирующая процедуры создания матрицы контроля по четности традиционного блочного LDPC-кода;

Фиг.11 - схема, иллюстрирующая процесс создания матрицы контроля по четности с использованием схемы с сокращением в соответствии с вариантом осуществления настоящего изобретения;

Фиг.12 - схема, иллюстрирующая процесс создания матрицы контроля по четности с использованием схемы с исключением в соответствии с вариантом осуществления настоящего изобретения;

Фиг.13 - схема, иллюстрирующая процесс создания матрицы контроля по четности с использованием схемы с, так называемым, «перфорированием» в соответствии с вариантом осуществления настоящего изобретения;

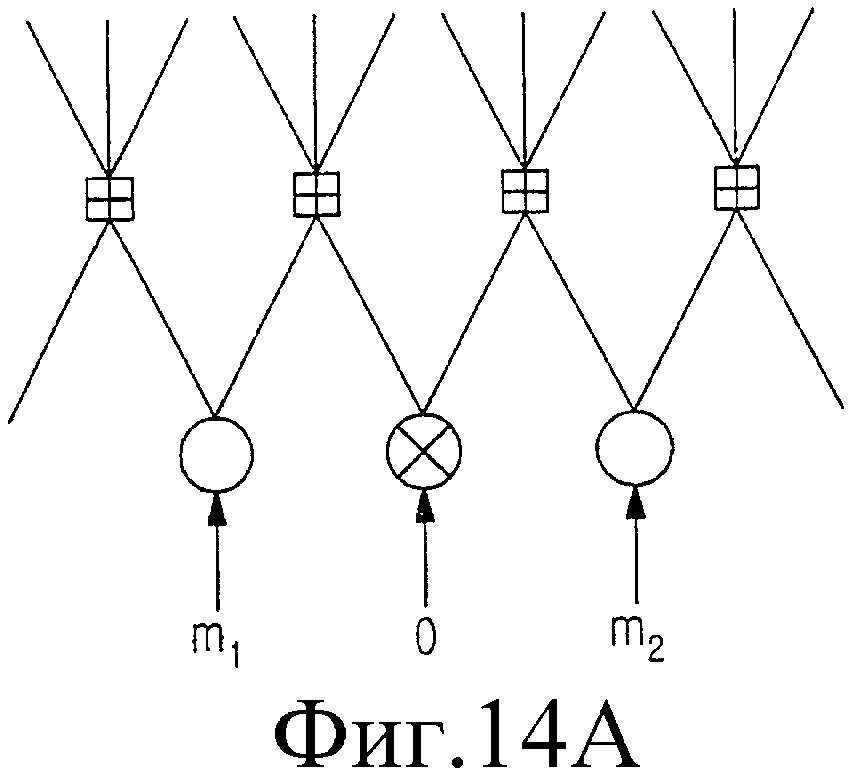

Фиг.14A - 14D - схемы для описания роли вершины контроля по четности, перфорируемой в процессе декодирования для кодового слова блочного LDPC-кода, сгенерированного с использованием схемы с перфорированием в соответствии с вариантом осуществления настоящего изобретения;

Фиг.15 - схема, иллюстрирующая процесс создания матрицы контроля по четности с использованием схемы с сокращением в соответствии с вариантом осуществления настоящего изобретения;

Фиг.16 - схема, иллюстрирующая матрицу контроля по четности для блочного LDPC-кода с переменной скоростью кодирования в соответствии с вариантом осуществления настоящего изобретения;

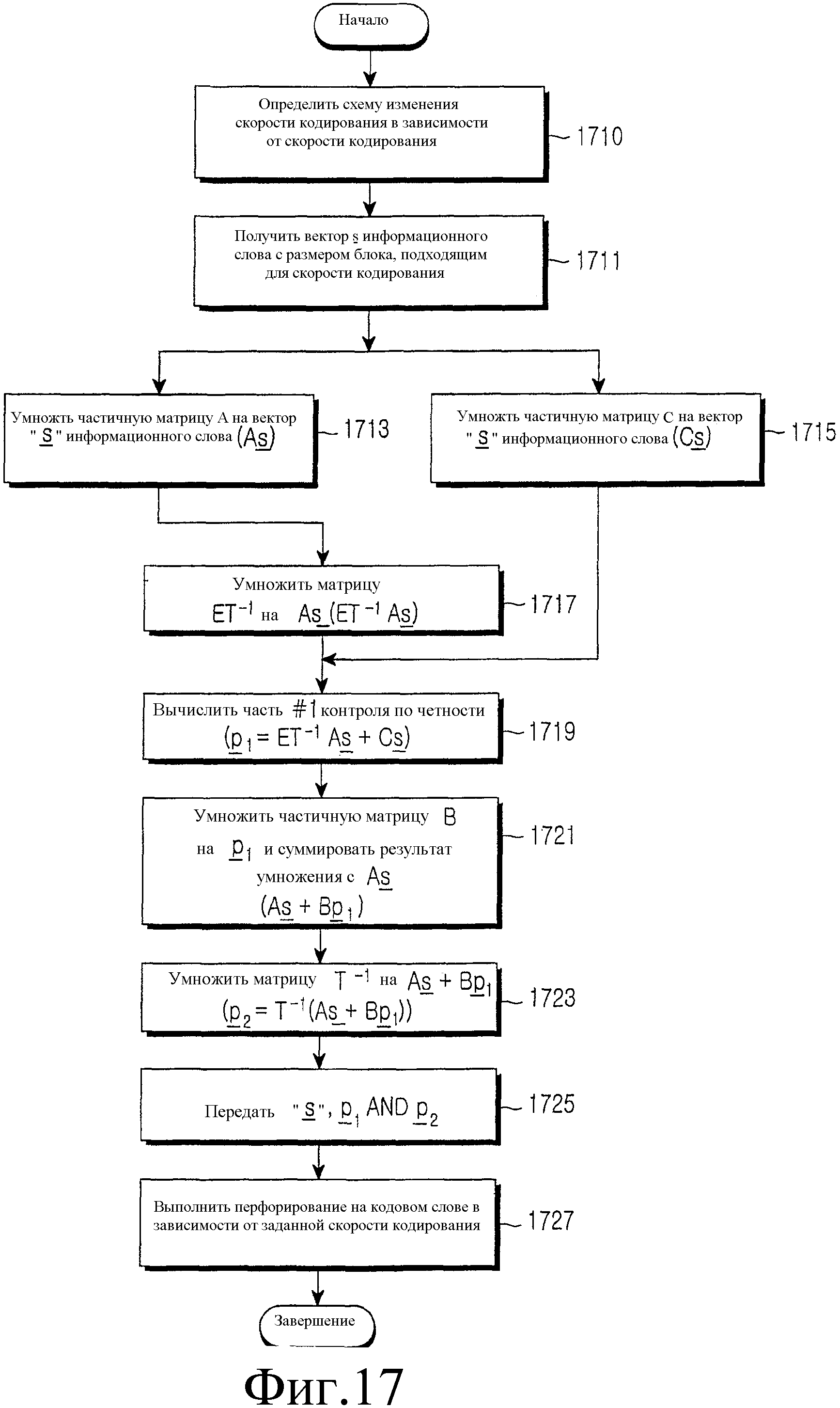

Фиг.17 - блок-схема последовательности операций, иллюстрирующая процесс кодирования блочного LDPC-кода с переменной скоростью кодирования в соответствии с вариантом осуществления настоящего изобретения;

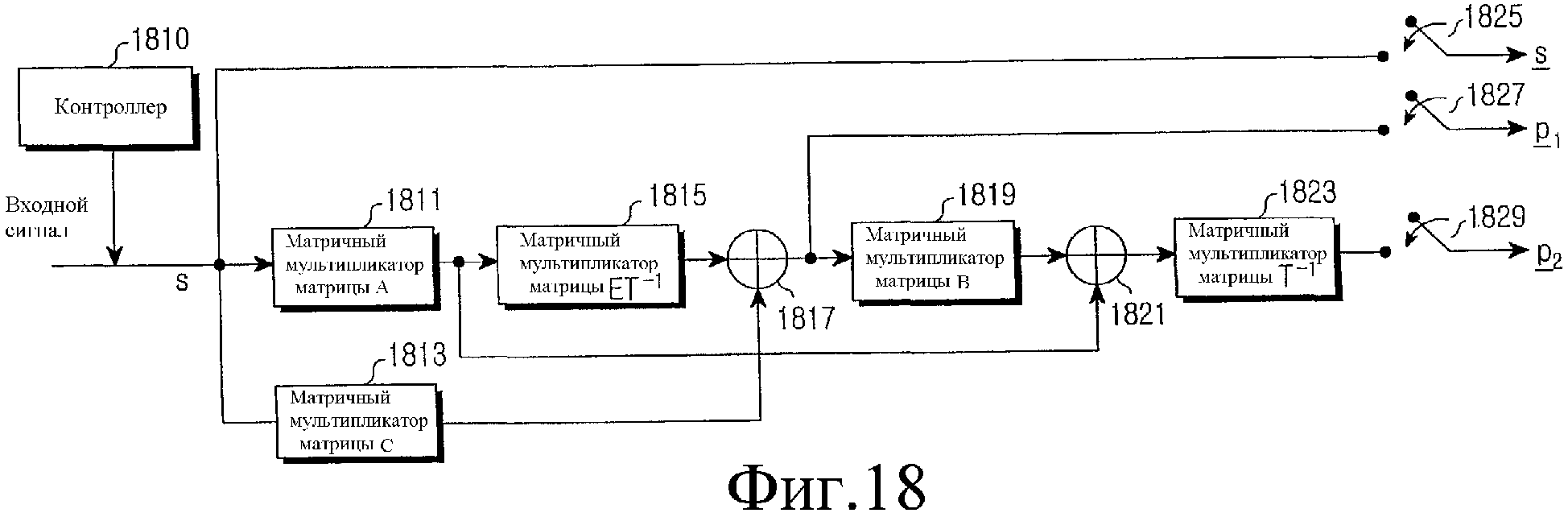

Фиг.18 - блок-схема, иллюстрирующая внутреннюю конструкцию устройства для кодирования блочного LDPC-кода с переменной скоростью кодирования в соответствии с вариантом осуществления настоящего изобретения;

Фиг.19 - блок-схема, иллюстрирующая внутреннюю конструкцию устройства для декодирования блочного LDPC-кода с переменной скоростью кодирования в соответствии с вариантами осуществления настоящего изобретения;

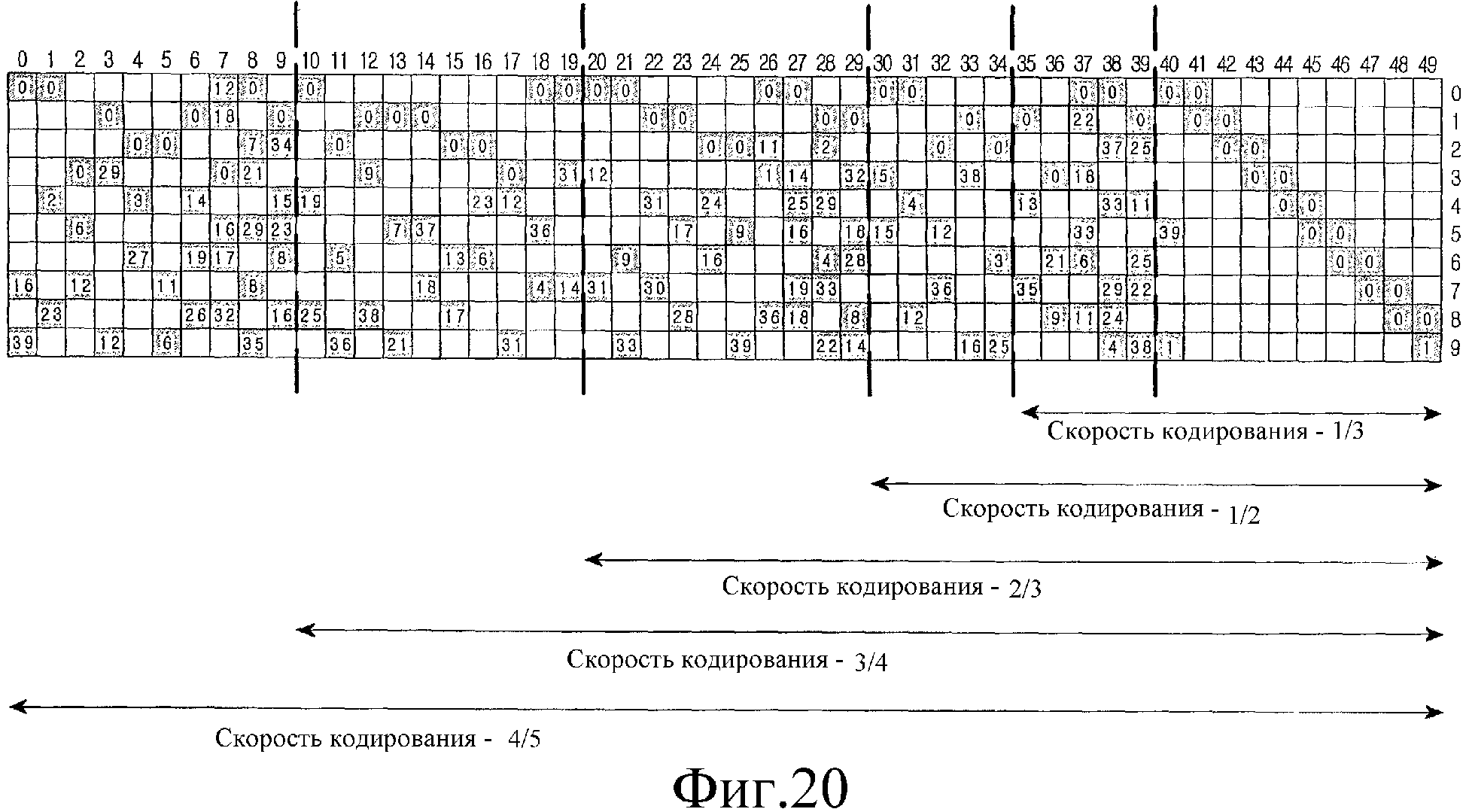

Фиг.20 - схема, иллюстрирующая матрицу контроля по четности для блочного LDPC-кода с переменной скоростью кодирования в соответствии с вариантом осуществления настоящего изобретения;

Фиг.21 - схема, иллюстрирующая внутреннюю конструкцию кодирующего устройства для блочного LDPC-кода с переменной скоростью кодирования в соответствии с другим вариантом осуществления настоящего изобретения;

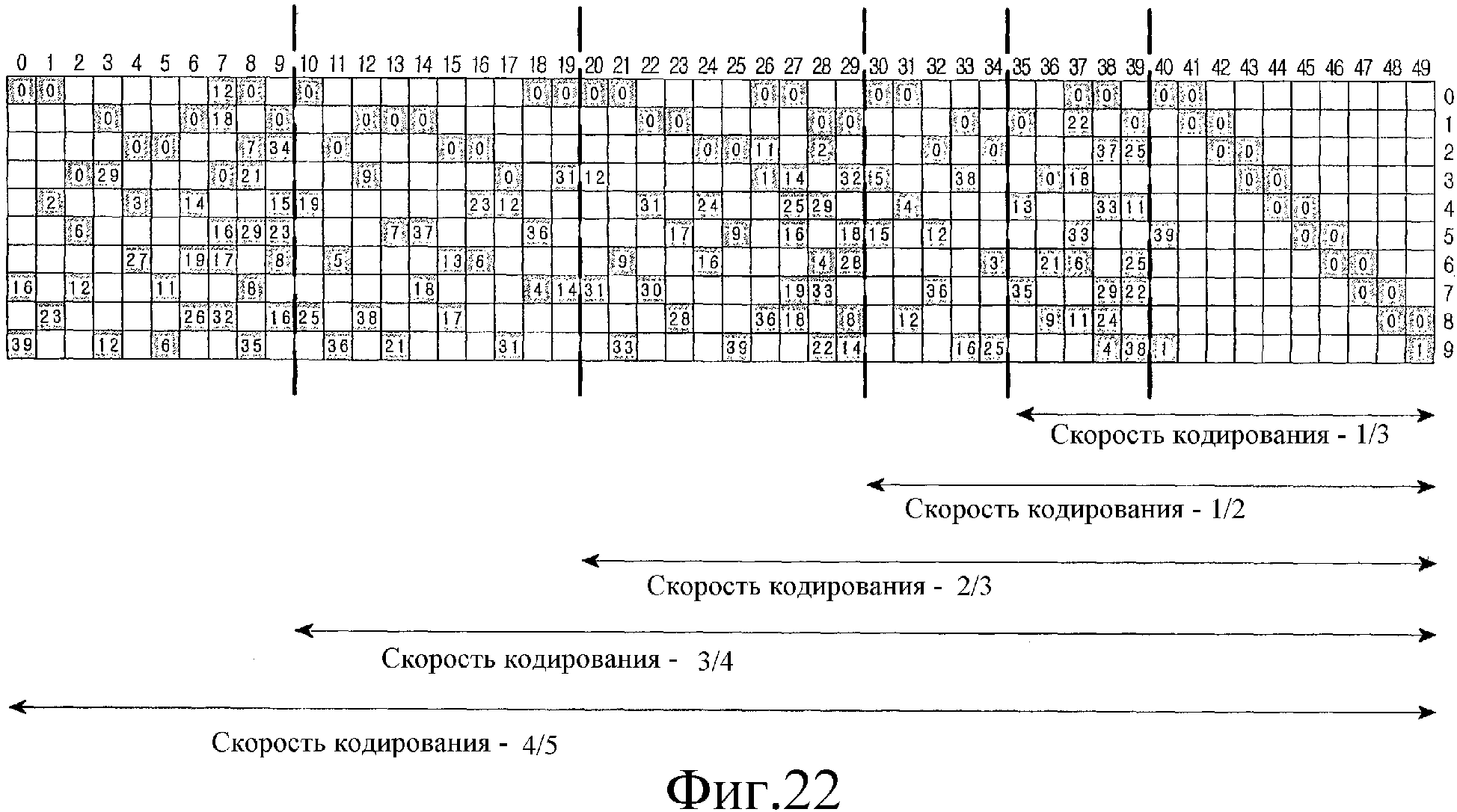

Фиг.22 - схема, иллюстрирующая матрицу контроля по четности для блочного LDPC-кода с переменной скоростью кодирования в соответствии с вариантом осуществления настоящего изобретения;

Фиг.23 - схема, иллюстрирующая матрицу контроля по четности для блочного LDPC-кода с переменной скоростью кодирования в соответствии с вариантом осуществления настоящего изобретения;

Фиг.24 - схема, иллюстрирующая матрицу контроля по четности для блочного LDPC-кода с переменной скоростью кодирования в соответствии с вариантом осуществления настоящего изобретения; и

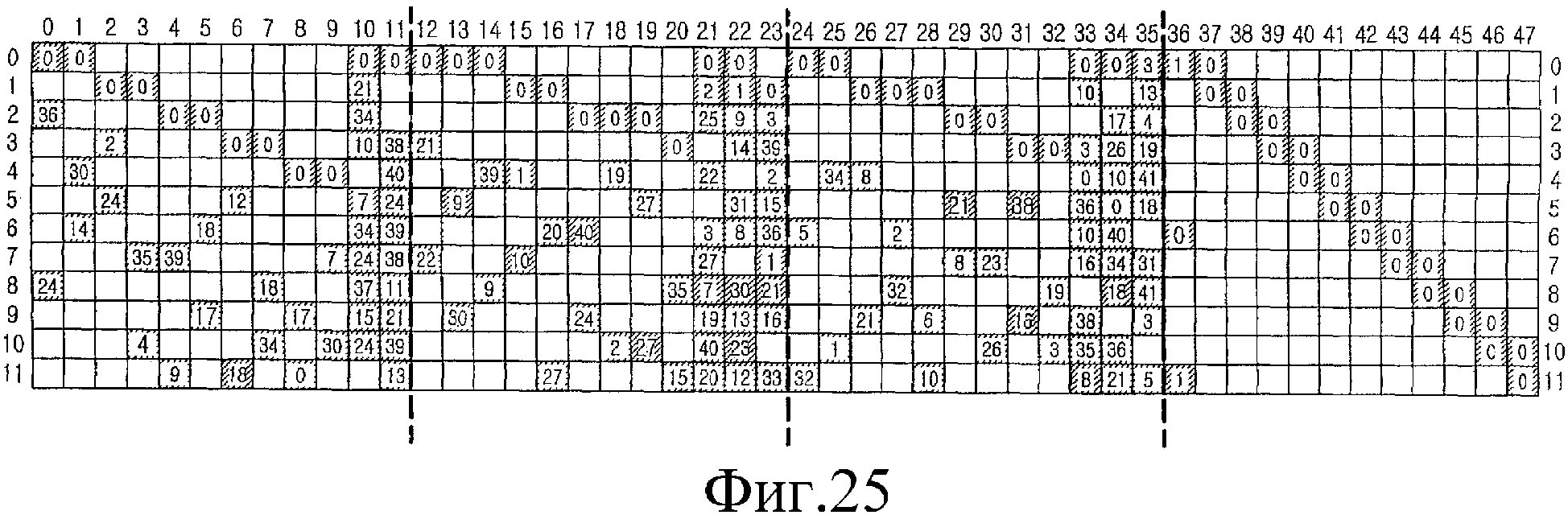

Фиг.25 - схема, иллюстрирующая матрицу контроля по четности для блочного LDPC-кода с переменной скоростью кодирования в соответствии с вариантом осуществления настоящего изобретения.

ПОДРОБНОЕ ОПИСАНИЕ ПРЕДПОЧТИТЕЛЬНОГО ВАРИАНТА ОСУЩЕСТВЛЕНИЯ

Ниже приведено описание нескольких предпочтительных вариантов осуществления настоящего изобретения со ссылками на прилагаемые чертежи. В нижеследующем описании для краткости отсутствует подробное описание известных функций и конструкций, включенных в настоящий документ.

В соответствии с настоящим изобретением предлагаются устройство и способ для кодирования и декодирования блочного кода с низкой плотностью контроля по четности (LDPC-кода), обладающего переменной скоростью кодирования (далее по тексту именуемого «блочный LDPC-код с переменной скоростью кодирования»). То есть, в соответствии с настоящим изобретением предлагаются устройство и способ для кодирования и декодирования блочного LDPC-кода с переменной скоростью кодирования, в котором длина минимального цикла в фактор-графе блочного LDPC-кода максимально увеличена, сложность кодирования блочного LDPC-кода сведена к минимуму, распределение степеней в фактор-графе блочного LDPC-кода имеет оптимальное значение 1, и поддерживается переменная скорость кодирования. Кодирующее и декодирующее устройства для блочного LDPC-кода по настоящему изобретению можно применять к передатчику/приемнику, описанным со ссылкой на фиг.1, хотя это не показано отдельно в описании.

Мобильная система связи следующего поколения развилась в пакетную систему связи, и пакетная система связи, которая представляет собой систему для передачи пакетированных данных множеству мобильных станций, разработана с возможностью высокопроизводительной передачи данных. Для повышения пропускной способности данных предложены схемы с автоматическим запросом на повторную передачу (HARQ) и адаптивной модуляции и кодированием (AMC). Посокольку схема HARQ и схема AMC поддерживают переменную скорость кодирования, существует потребность в блочных LDPC-кодах, поддерживающих различные скорости кодирования.

Разработка блочного LDPC-кода с переменной скоростью кодирования, как разработка обычного LDPC-кода, осуществляется путем разработки матрицы контроля по четности. Однако в системе мобильной связи, чтобы обеспечить блочный LDPC-код с переменной скоростью кодирования с одним КОДЕКом, т.е. чтобы обеспечить блочные LDPC-коды, обладающие различными скоростями кодирования, матрица контроля по четности должна содержать матрицы контроля по четности, способные представлять блочные LDPC-коды, обладающие разными скоростями кодирования. То есть, необходимо поддерживать, по меньшей мере, две скорости кодирования с использованием одной матрицы контроля по четности.

Согласно настоящему изобретению схемы для поддержки, по меньшей мере, двух скоростей кодирования с использованием одной матрицы контроля по четности включают в себя схему с сокращением, схему с исключением и схему с перфорированием. Ниже приведено описание схемы с сокращением, схемы с исключением и схемы с перфорированием.

Схема с сокращением снижает скорость кодирования фиксированием числа строк в матрице контроля по четности и уменьшением числа столбцов, отображаемых в информационное слово. Схема с сокращением пригодна для получения различных скоростей кодирования для разных длин кодовых слов.

На фиг.11 представлена схема, иллюстрирующая процесс создания матрицы контроля по четности с использованием схемы с сокращением в соответствии с вариантом осуществления настоящего изобретения. Как видно из фиг.11, Hi(Ri,Ni,Ki) представляет матрицу контроля по четности блочного LDPC-кода, обладающего скоростью Ri кодирования, длину Ni кодового слова и длину Ki информационного слова, где при i

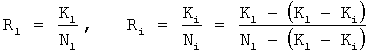

Поэтому, в процессе создания матрицы контроля по четности с использованием схемы с сокращением, как описано в связи с фиг.11, скорость кодирования соответствующего блочного LDPC-кода можно выразить как показано в уравнении (5).

При i

>0

Как можно видеть из уравнения (6), скорость кодирования, получаемая при создании матрицы контроля по четности с использованием схемы с сокращением, снижается.

Если предположить, что на фиг.11 матрица контроля по четности вида H1(R1,N1,K1) имеет полный ранг, то, даже несмотря на создание матриц контроля по четности с использованием схем с сокращением, число строк в матрицах контроля по четности, созданных с использованием схем с сокращением, остается постоянным. Поэтому длина информационного слова сокращается, тогда как длина контрольного слова остается постоянной, что снижает скорость кодирования. Как правило, если столбцы, отображаемые в часть контроля по четности, исключаются из заданной матрицы контроля по четности, генерируемый набор кодовых слов полностью отличается от набора кодовых слов, генерируемого, когда столбцы, отображаемые в часть контроля по четности, не исключаются. Поэтому схема с сокращением характеризуется базовым принципом исключения столбцов, отображаемых в информационное слово.

Схема с исключением снижает скорость кодирования фиксированием числа столбцов и увеличением числа строк в матрице контроля по четности. В настоящем изобретении увеличение числа строк в матрице контроля по четности означает увеличение числа контрольных уравнений, которым должны удовлетворять кодовые слова. Увеличение числа контрольных уравнений уменьшает количество кодовых слов, которые должны удовлетворять контрольным уравнениям. Соответственно, «схема с исключением» получила свое название потому, что она исключает кодовые слова, которые не могут удовлетворять кодовым уравнениям, добавленным по причине увеличения числа строк в матрице контроля по четности, из базового набора кодовых слов.

На фиг.12 представлена схема, иллюстрирующая процесс создания матрицы контроля по четности с использованием схемы с исключением в соответствии с вариантом осуществления настоящего изобретения. Как видно из фиг.12, Hi(Ri,N) представляет матрицу контроля по четности блочного LDPC-кода со скоростью Ri кодирования и длиной N кодового слова. В предположении, что на фиг. 12 каждая из матриц контроля по четности имеет полный ранг Mi, скорость кодирования кода, генерируемого для каждой из матриц контроля по четности, может быть выражена, как показано уравнением (7).

Как показано в уравнении (7), полный ранг Mi обычно возрастает по «i» и вызывает снижение Ri. В качестве альтернативы, можно также создать матрицу контроля по четности с высокой скоростью кодирования с использованием схемы исключения строк на основе матрицы контроля по четности с очень низкой скоростью кодирования, например, H4(R4,N), показанную на фиг.12, в отличие от схемы с исключением.

Схема с перфорированием повышает скорость кодирования передачей только части генерируемых контрольных слов вместо передачи всех контрольных слов, генерируемых в кодере, как в случае турбокода. Схема с перфорированием, хотя и не передает все генерируемые контрольные слова, может считать, что в матрице контроля по четности отсутствуют изменения. Поэтому схема с перфорированием отличается от схем удаления или добавления столбцов и строк матрицы контроля по четности, как в случае схемы с сокращением или схемы с исключением.

На фиг.13 представлена схема, иллюстрирующая процесс создания матрицы контроля по четности с использованием схемы с перфорированием в соответствии с вариантом осуществления настоящего изобретения. Как видно из фиг.13, матрица контроля по четности для блочного LDPC-кода (N,K)=(1720,860) со скоростью кодирования 1/2 содержит 20×40 частичных блоков. Частичная матрица, соответствующая каждому из частичных блоков, является квадратной матрицей, размерность которой равна Ns×Ns=43×43.

Когда кодовое слово блочного LDPC-кода разделено на информационное слово и контрольное слово, информационное слово и контрольное слово также можно разделить по каждому частичному блоку. Поэтому кодовое слово блочного LDPC-кода можно выразить, как показано в уравнении (8).

В уравнении (8)

Если из части контроля по четности в матрице контроля по четности, показанной на фиг. 13, перфорируются четные блоки, кодовое слово блочного LDPC-кода, полученного перфорированием, можно выразить, как показано в уравнении (9).

В уравнении (9), cpunc, обозначает кодовое слово блочного LDPC-кода, полученного перфорированием. Как показано в уравнении (9), кодовое слово становится равным кодовому слову блочного LDPC-кода со скоростью кодирования 2/3. То есть, использование схемы с перфорированием изменяет скорость кодирования, но сохраняет длину информационного слова.

В процессе декодирования кодового слова блочного LDPC-кода, генерируемого с использованием схемы с перфорированием, применяется порождающая матрица контроля по четности с отношением к перфорированным битам четности, как к стертым битам. То есть, если значение логарифмического отношения правдоподобия (LLR), введенное из канала, по которому передаются перфорированные биты контроля четности, всегда считать равным «0», то порождающую матрицу контроля по четности можно применять в неизменном виде во время декодирования. Поэтому перфорированная вершина, соответствующая контрольному слову, никогда не сказывается на повышении производительности или снижении производительности благодаря итеративному декодированию в процессе декодирования и просто служит как путь, по которому проходят сообщения, передаваемые из других вершин.

На фиг.14A - 14D представлены схемы, иллюстрирующие роль вершины, соответствующей контрольному слову, перфорированной в процессе декодирования, для кодового слова блочного LDPC-кода, генерируемого с использованием схемы с перфорированием в соответствии с вариантом осуществления настоящего изобретения. Однако, до описания фиг.14A - 14D, следует отметить, что знак

Как видно из фиг.14A, значение «0» LLR вводится в перфорированную вершину контроля по четности. После этого сообщение, выданное из канала, показанного на фиг.14A, подается в проверочные вершины в ходе первого процесса декодирования, как показано на фиг.14B. На фиг.14B переменные вершины, соответствующие контрольному слову, подведены к проверочным вершинам, подсоединенным к входному сообщению, т.е. значению вероятности символа. Переменная вершина, соответствующая контрольному слову, подает значение «0» LLR в подсоединенные проверочные вершины.

Проверочные вершины вычисляют значения вероятности, которые должны подаваться в каждую из переменных вершин, выполнением заданной операции с использованием значений вероятности, выданных из переменных вершин, соединенных с проверочными вершинами, и подают вычисленные значения вероятности в соответствующие переменные вершины. Сообщение, подаваемое во все вершины, соединенные с переменной вершиной, соответствующей контрольному слову, перфорированному из проверочной вершины, становится «0», как показано на фиг.14C. Кроме того, сообщение, подаваемое в перфорированную переменную вершину, соответствующую контрольному слову, не равно «0», и сообщения, подаваемые в перфорированные переменные вершины, соответствующие контрольному слову, независимо подаются по собственным путям, без взаимного влияния, как показано на фиг.14D. Нижеследующий процесс декодирования эквивалентен обычному процессу декодирования для LDPC-кода, и перфорированная переменная вершина, соответствующая контрольному слову, не оказывает непрерывного влияния на повышение производительности вследствие декодирования и служит просто как путь передачи сообщений.

Как описано выше, в схеме с перфорированием исходные кодер и декодер можно использовать для кодирования и декодирования. То есть, в схеме с перфорированием сложность кодирования и сложность декодирования являются почти постоянными, независимо от скорости кодирования и длины блока (кодового слова), длина информационного слова является фиксированной, и скорость кодирования изменяется изменением только длины контрольного слова. Поэтому схема с перфорированием характеризуется высокой надежностью. Так как производительность блочного LDPC-кода, генерируемого с использованием схемы с перфорированием, изменяется в зависимости от схемы его перфорирования, то схемное решение перфорирования является важным фактором.

Далее приведено подробное описание способа для реальной генерации блочного LDPC-кода с использованием схемы с сокращением и схемы с перфорированием. Аналогично известным блочным кодам блочный LDPC-код может также изменять свою скорость кодирования с использованием схемы с сокращением. Поэтому в варианте осуществления настоящего изобретения скорость кодирования блочного LDPC-кода изменяется с использованием схемы с сокращением.

На фиг.15 представлена схема, иллюстрирующая процесс создания матрицы контроля по четности с использованием схемы с сокращением в соответствии с вариантом осуществления настоящего изобретения. Как видно из фиг. 15, показанная матрица контроля по четности создается, если все

Как правило, в случае конечной длины блочный LDPC-код с высокой скоростью кодирования, показывающий высокую производительность, характеризуется более высокой средней степенью проверочной вершины, чем блочный LDPC-код с низкой скоростью кодирования, показывающий высокую производительность. Поэтому, для генерации блочного LDPC-кода с низкой скоростью кодирования с использованием схемы с сокращением необходимо снизить среднюю степень проверочной вершины после использования схемы с сокращением.

Кроме того, поскольку использование схемы с сокращением изменяет распределение степеней, то, чтобы разработать блочный LDPC-код с переменной скоростью кодирования, обладающий высоким шумовым порогом, с использованием схемы анализа изменения плотности, необходимо учитывать как распределение степеней порождающей матрицы контроля по четности, так и распределение степеней дочерней матрицы контроля по четности, создаваемой с использованием схемы с сокращением. Однако схема с перфорированием считает, что перфорированная переменная вершина исключена, вместо фактического исключения перфорированной переменной вершины. Поэтому схема с перфорированием может генерировать блочный LDPC-код с высокой скоростью кодирования, без вызова изменений в степени распределения матрицы контроля по четности в целом.

Ниже будет приведено описание способа генерации блочного LDPC-кода, допускающего поддержку различных скоростей кодирования, т.е. с переменной скоростью кодирования, с использованием одной матрицы контроля по четности, т.е. одной порождающей матрицы контроля по четности. Далее будет приведено описание блочного LDPC-кода, который имеет фиксированную длину кодового слова и переменную скорость кодирования. Кроме того, будет приведено описание способа генерации блочного LDPC-кода, допускающего изменение его скорости кодирования от 1/3 до 1/2, с использованием схемы с сокращением и схемы с перфорированием, в качестве примера блочного LDPC-кода с переменной скоростью кодирования, в котором длина блока, т.е. длина кодового слова, является фиксированной, и позволяющего порождающей матрице контроля по четности и дочерней матрице контроля по четности, создаваемой из порождающей матрицы контроля по четности с использованием схемы с сокращением, обладать высоким шумовым порогом.

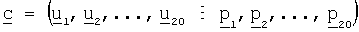

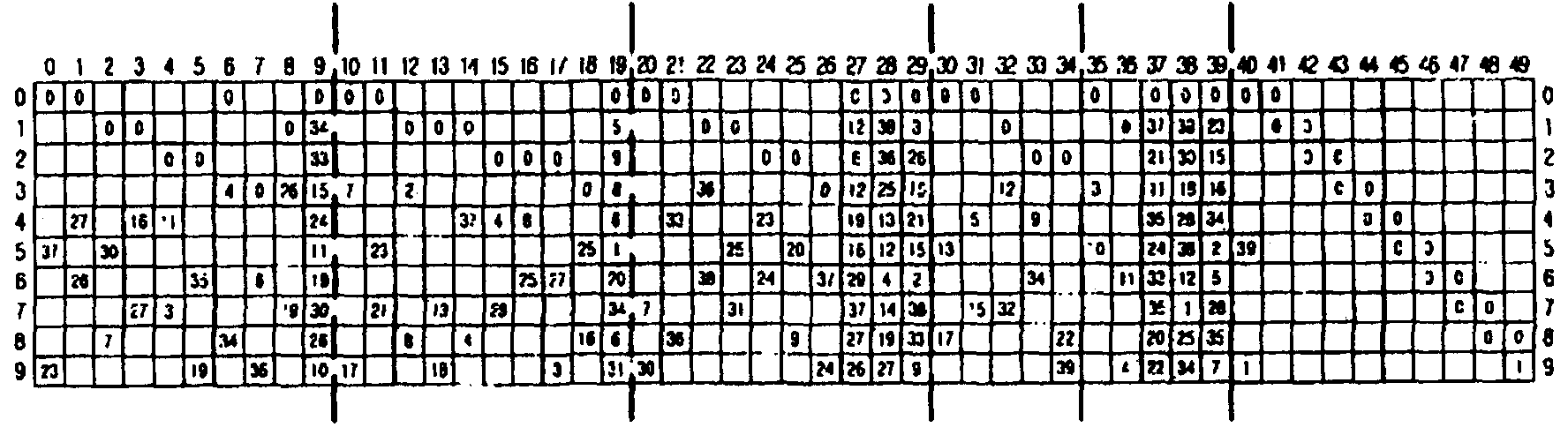

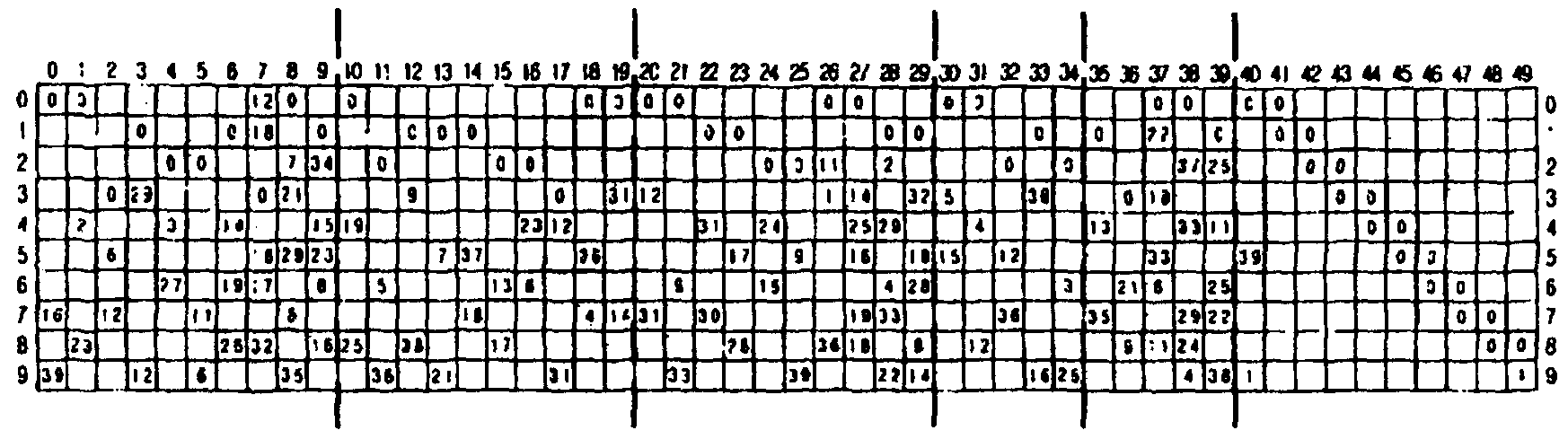

На фиг.16 представлена схема, иллюстрирующая матрицу контроля по четности для блочного LDPC-кода с переменной скоростью кодирования в соответствии с вариантом осуществления настоящего изобретения. Как видно из фиг.16, изображенная матрица контроля по четности содержит 49 столбцов частичных блоков и 28 строк частичных блоков, и Ns×Ns-размерная частичная матрица отображается в каждый из частичных блоков, составляющих матрицу контроля по четности. В настоящем описании термин «частичная матрица» означает перестановочную матрицу, отображаемую в каждый из частичных блоков, и размерность частичного блока, равная Ns, относится к квадратной матрице, в которой частичная матрица имеет размерность Ns×Ns. Здесь следует отметить, что размерность частичной матрицы выражается как Ns×Ns или Ns.

Скорость кодирования матрицы контроля по четности, показанной на фиг.16, можно выразить, как показано в уравнении (10).

То есть матрицу контроля по четности, показанную на фиг.16, можно использовать как блочный LDPC-код, который обладает скоростью кодирования 3/7 и длиной 49Ns кодового слова, или матрицу контроля по четности блочного LDPC-кода с переменной скоростью кодирования можно создать как одну матрицу контроля по четности с использованием схемы с сокращением или схемы с перфорированием. Например, блочный LDPC-код, который обладает скоростью кодирования 1/3 и длиной 42Ns кодового слова можно создать сокращением столбцов с 1-го столбца частичного блока по 7-й столбец частичного блока с использованием схемы с сокращением, отображением частичных матриц, соответствующих столбцам с 8-го столбца частичного блока по 21-й столбец частичного блока, в информационное слово и отображением частичных матриц, соответствующих столбцам с 22-го столбца частичного блока по 49-й столбец частичного блока в контрольное слово.

В другом примере, блочный LDPC-код, который обладает скоростью кодирования 1/2 и длиной 42Ns кодового слова, можно генерировать отображением частичных матриц, соответствующих столбцам с 1-го столбца частичного блока по 21-й столбец частичного блока, в информационное слово и перфорированием 7 столбцов частичных блоков из столбцов с 22-го столбца частичного блока по 49-й столбец частичного блока с использованием схемы с перфорированием. В вышеприведенных примерах показана возможность генерации блочных LDPC-кодов, которые эквивалентны между собой по фактической длине кодового слова, но отличаются один от другого по скорости кодирования, с использованием схемы с сокращением или схемы с перфорированием.

Важнейшим фактором, который следует учитывать при генерации блочного LDPC-кода, поддерживающего переменную скорость кодирования, является проектирование таким образом, чтобы не только порождающая матрица контроля по четности, но также дочерняя матрица контроля по четности обладали высокими характеристиками по шумовому порогу. Поэтому оптимизируют распределение степеней для матрицы контроля по четности блочного LDPC-кода с низкой скоростью кодирования и создают матрицу контроля по четности блочного LDPC-кода с высокой скоростью кодирования так, чтобы он содержал оптимизированную матрицу контроля по четности, и распределение степеней было оптимизировано.

То есть матрица контроля по четности, показанная на фиг.16, может быть создана оптимизацией степени распределения для матрицы контроля по четности блочного LDPC-кода со скоростью кодирования 1/3 и повторным выполнением оптимизации распределения степеней в матрице контроля по четности блочного LDPC-кода, который содержит оптимизированную матрицу контроля по четности и имеет скорость кодирования 3/7. На фиг.16, для удобства разработки матрицы контроля по четности, степени переменных вершин ограничены 4 типами, т.е. 2, 3, 5 и 16, и степени проверочных вершин ограничены 3 типами, т.е. 5, 6 и 7.

На фиг.16, шумовой порог равен σ*=1,256 (-0,219[дБ]) для укороченного блочного LDPC-кода со скоростью кодирования 1/3, шумовой порог равен σ*=1,066 (0,114[дБ]) для блочного LDPC-кода со скоростью кодирования 3/7, и имеют место нижеприведенные распределения степеней блочных LDPC-кодов (максимальные пропускные способности канала для LDPC-кодов равны -0,495[дБ] и -0,122[дБ]).

- распределение степеней укороченного блочного LDPC-кода со скоростью кодирования 1/3:

λ2=0,348, λ3=0,174, λ5=0,065, λ16=0,413;

ρ5=0,419, ρ6=0,581

- распределение степеней блочного LDPC-кода со скоростью кодирования 3/7:

λ2=0,280, λ3=0,202, λ5=0,104, λ16=0,414;

ρ6=0,093

Значение λi (i=2, 3, 5, 16) является распределением ребра, связанного с переменной вершиной, которая характеризуется i степенями, ρi (i=2, 3, 5, 16) является распределением ребра, связанного с проверочной вершиной, которая характеризуется i степенями.

То есть, для поддержки переменной скорости кодирования необходимо разработать блочные LDPC-коды со сниженной скоростью кодирования и блочные LDPC-коды с повышенной скоростью кодирования так, чтобы все данные коды обладали высоким шумовым порогом, посредством назначения результата, полученного выполнением первой оптимизации для блочного LDPC-кода с низкой скоростью кодирования, в качестве одного ограничивающего условия, и затем последовательным выполнением оптимизации для блочных LDPC-кодов с соседней высокой скоростью кодирования. Хотя на фиг.16 степени переменных вершин ограничены 4 типами для удобства, если число допустимых степеней переменных вершин возрастает, то можно получить шумовой порог с более высокой характеристикой.

Ниже приведено описание процесса разработки блочного LDPC-кода с переменной скоростью кодирования в предположении, что скорости кодирования связаны отношением R1 < R2 < …

Этап 1

Во-первых, для скорости Ri кодирования оптимизация распределения степеней выполняется с использованием схемы изменения плотности. Будет принято, что в степени распределения, полученной выполнением оптимизации распределения степеней, отношение переменных вершин со степенью j (1≤j≤dv,max) ко всем переменным вершинам равно fl,j. Отношение fl,j и степень λl,j распределения ребра являются взаимозаменяемыми согласно отношению, заданному уравнением (11), и λl,j представляет отношение энергии, подводимой к переменной вершине со степенью j, к суммарной энергии.

В уравнении (11), «k» имеет то же значение, что и значение степени «j», и проверочная вершина также учитывается таким же образом, как переменная вершина.

Оптимизация распределения степеней выполняется назначением дополнительного ограничительного условия, состоящего в том, что, при l (2≤l≤m), включаются fl-1,j×Nl-1 переменных вершин со степенью j из Nj (длина Ri кодового слова) переменных вершин с использованием распределения степеней, полученного на этапе 1. Проверочная вершина также выполняется таким же образом как переменная вершина.

Выполнение оптимизации распределения степеней таким образом, как описано на этапе 1 и этапе 2, дает возможность разработать матрицу контроля по четности блочного LDPC-кода с различными скоростями кодирования. Можно заметить, что разработанная матрица контроля по четности является матрицей контроля по четности, соответствующей блочному LDPC-коду, длина контрольного слова которого выдерживается равной M, и длина блока изменяется до Ni, с использованием схемы с сокращением в зависимости от требуемой скорости Ri кодирования. Кроме того, если совместно со схемой с сокращением применяется схема с перфорированием, то можно генерировать блочный LDPC-код с большим числом различных скоростей кодирования и длин блоков (кодовых слов).

В предположении, что для скорости Ri кодирования число перфорированных битов контроля четности обозначено как Pi (

Чтобы генерировать блочный LDPC-код с фиксированной длиной блока, число Pi перфорированных битов контроля четности соответственно определяют так, чтобы поддерживать Ni-Pi=Nl. В данном случае, скорость кодирования можно выразить, как показано в уравнении (13).

Как изложено выше, важнейшим фактором, который следует учитывать при разработка матрицы контроля по четности для блочного LDPC-кода с переменной скоростью кодирования, является оптимизация распределения степеней. Если для переменной скорости кодирования поддерживается слишком много скоростей кодирования, степень проверочной вершины возрастает со снижением характеристики цикла. Поэтому матрица контроля по четности должна разрабатываться с учетом всех поддерживаемых скоростей кодирования, подлежащего получению шумового порога и характеристики цикла.

На фиг.17 представлена блок-схема последовательности операций, иллюстрирующая процесс кодирования блочного LDPC-кода с переменной скоростью кодирования в соответствии с вариантом осуществления настоящего изобретения. Перед описанием фиг.17 будет принято, что матрица контроля по четности для блочного LDPC-кода с переменной скоростью кодирования состоит из 6 частичных матриц, как описано со ссылкой на фиг.8.

Как видно из фиг.17, на этапе 1710 контроллер определяет схему изменения скорости кодирования, подлежащей применению к порождающей матрице контроля по четности, в зависимости от заданной скорости кодирования, чтобы генерировать блочный LDPC-код с переменной скоростью кодирования. В настоящем описании термин «схема изменения скорости кодирования» охватывает схему с сокращением и схему с перфорированием, и, когда порождающая матрица контроля по четности применяется в неизменном виде, не применяется ни одна из схем изменения скорости кодирования. Скорость кодирования можно изменять с использованием либо одной, либо обеих из схемы с сокращением и схемы с перфорированием. Здесь будет принято, что скорость кодирования изменяется с использованием схемы с сокращением или схемы с перфорированием.

На этапе 1711 контроллер получает вектор «s» информационного слова, подлежащий кодированию в блочный LDPC-код с переменной скоростью кодирования. Длина вектора «s» информационного слова изменяется только, когда применяется схема с сокращением. В данном случае принято, что длина принимаемого вектора «s» информационного слова, подлежащего кодированию в блочный LDPC-код с переменной скоростью кодирования, равна «k». На этапе 1713 контроллер матрично умножает принимаемый вектор «s» информационного слова на частичную матрицу A матрицы (As) контроля по четности. В данном случае, так как число элементов, имеющих значение 1, расположенных в частичной матрице A, намного меньше, чем число элементов, имеющих значение 0, матричное перемножение (As) вектора «s» информационного слова и частичной матрицы A матрицы контроля по четности можно обеспечить относительно с помощью небольшого числа операций суммы - произведения.

Кроме того, так как в частичной матрице A позицию, в которой находятся элементы, имеющие значение 1, можно выразить в виде экспоненциального умножения позиции ненулевого блока и перестановочной матрицы блока, матричное умножение можно выполнить посредством очень простой операции по сравнению со случайной матрицей контроля по четности.

На этапе 1715 контроллер выполняет матричное умножение (Cs) на частичной матрице C матрицы контроля по четности и вектора «s» информационного слова. Что касается частичных матриц A и C, используемых на этапах 1713 и 1715, когда схема с сокращением применяется к порождающей матрице контроля по четности, не используется столько столбцов порождающей матрицы контроля по четности, сколько их находится в сокращенной части. Поэтому столбцы, соответствующие сокращенной части, исключаются из частичных матриц A и C порождающей матрицы контроля по четности.

На этапе 1717 контроллер выполняет матричное перемножение (ET-1As) на результате (As) матричного перемножения вектора «s» информационного слова и частичной матрицы A матрицы контроля по четности и матрицы ET-1. В данном случае, так как число элементов, имеющих значение 1, в матрице ET-1 является очень небольшим, как указано выше, если дан порядок перестановочной матрицы блока, то матричное перемножение может быть просто выполнимым.

На этапе 1719 контроллер вычисляет первый вектор P1 контроля по четности сложением ET-1As и Cs (P1=ET-1As+Cs). В данном случае, операция сложения является операцией исключающей ИЛИ (XOR), и ее результат становится равным 0 для операции между битами, имеющими одинаковое значение, и 1 для операции между битами, имеющими разные значения. То есть процесс до этапа 1719 является процессом для вычисления первого вектора P1 контроля по четности.

На этапе 1721, контроллер умножает частичную матрицу B матрицы контроля по четности на первый вектор P1 контроля по четности (BP1), прибавляет результат умножения (BP1) к As (As+BP1). Если даны вектор «s» информационного слова и первый вектор P1 контроля по четности, то их следует умножить на обратную матрицу T-1 частичной матрицы T матрицы контроля по четности для вычисления второго вектора P2 контроля по четности. Поэтому на этапе 1723 контроллер умножает результат вычисления (As + BP1) на этапе 1721 на обратную матрицу T-1 частичной матрицы T для вычисления второго вектора P2 контроля по четности, (P2=T-1(As+BP1)).

Как описано выше, если дан вектор «s» информационного слова подлежащего кодированию блочного LDPC-кода с переменной скоростью кодирования, то можно вычислить первый вектор P1 контроля по четности и второй вектор P2 контроля по четности, и, в результате, можно получить все кодовые слова. На этапе 1725, контроллер генерирует вектор «c» кодового слова с использованием вектора «s» информационного слова, первого вектора P1 контроля по четности и второго вектора P2 контроля по четности.

На этапе 1727 контроллер генерирует блочный LDPC-код, соответствующий скорости кодирования, перфорированием контрольного слова вектора «c» кодового слова в зависимости от заданной схемы перфорирования и затем завершает процедуру.

На фиг.18 представлена блок-схема, иллюстрирующая внутреннюю конструкцию устройства для кодирования блочного LDPC-кода с переменной скоростью кодирования в соответствии с вариантом осуществления настоящего изобретения. Как видно из фиг.18, устройство для кодирования блочного LDPC-кода с переменной скоростью кодирования содержит контроллер 1810, матричный мультипликатор 1811 матрицы A, матричный мультипликатор 1813 матрицы C, матричный мультипликатор 1815 матрицы ET-1, сумматор 1817, матричный мультипликатор 1819 матрицы B, сумматор 1821, матричный мультипликатор 1823 матрицы T-1 и переключатели 1825, 1827 и 1829.

Входной сигнал, т.е. вектор «s» информационного слова с длиной k, подлежащий кодированию в блочный LDPC-код с переменной скоростью кодирования, вводится в переключатель 1825, матричный мультипликатор 1811 матрицы A и матричный мультипликатор 1813 матрицы C. Когда устройство кодирования блочного LDPC-кода с переменной скоростью кодирования использует схему с сокращением, контроллер 1810 изменяет длину «k» вектора «s» информационного слова в зависимости от соответствующей скорости кодирования и определяет длину кодового слова и схему перфорирования блочного LDPC-кода с переменной скоростью кодирования в зависимости от соответствующей скорости кодирования.

Матричный мультипликатор 1811 матрицы A умножает вектора «s» информационного слова на частичную матрицу A порождающей матрицы контроля по четности и выводит результат умножения в матричный мультипликатор 1815 матрицы ET-1 и сумматор 1821. Когда к порождающей матрице контроля по четности применяется сокращающая схема, как описано со ссылкой на фиг.17, матрица A и матрица C имеют форму, в которой столбцы, соответствующие сокращенной части, исключены из матрицы A и матрицы C порождающей матрицы контроля по четности. Матричный мультипликатор 1815 матрицы ET-1 умножает сигнал, выдаваемый матричным мультипликатором 1811 матрицы A, на частичную матрицу ET- порождающей матрицы контроля по четности и выводит результат умножения в сумматор 1817.

Сумматор 1817 прибавляет сигнал, выдаваемый матричным мультипликатором 1815 матрицы ET-1, к сигналу, выдаваемому матричным мультипликатором 1813 матрицы C, и выдает результат сложения в матричный мультипликатор 1819 матрицы B и переключатель 1827. В данном случае, сумматор 1817 выполняет операцию XOR побитовым способом. Например, если вектор длиной 3 для x=(x1, x2, x3) и вектор длиной 3 для y=(y1, y2, y3) вводятся в сумматор 1817, сумматор 1817 выводит вектор длиной 3 для z=(x1⊕y1, x2⊕y2, x3⊕y3) посредством выполнения операции XOR на векторе длиной 3 для x=(x1, x2, x3) и векторе длиной 3 для y=(y1, y2, y3). В данном случае, операция ⊕ означает операцию XOR, результат которой становится равным 0 для операции между битами, имеющими одинаковое значение, и 1 для операции между битами, имеющими разное значение. Сигнал, выдаваемый сумматором 1817, становится первым вектором P1 контроля по четности.

Матричный мультипликатор 1819 матрицы B умножает сигнал, выдаваемый сумматором 1817, т.е. первый вектор P1 контроля по четности, на частичную матрицу B порождающей матрицы контроля по четности и выводит результат умножения в сумматор 1821. Сумматор 1821 прибавляет сигнал, выдаваемый матричным мультипликатором 1819 матрицы B, к сигналу, выдаваемому матричным мультипликатором 1811 матрицы A, и выводит результат сложения в матричный мультипликатор 1823 матрицы T-1. Сумматор 1821, аналогично сумматору 1817, выполняет операцию XOR на сигнале, выданном матричным мультипликатором 1819 матрицы B, и сигнале, выданном матричным мультипликатором 1811 матрицы A, и выдает результат операции XOR в матричный мультипликатор 1823 матрицы T-1.

Матричный мультипликатор 1823 матрицы T-1 умножает сигнал, выдаваемый сумматором 1821, на обратную матрицу T-1 частичной матрицы T порождающей матрицы контроля по четности и выдает результат умножения в переключатель 1829. Выходной сигнал матричного мультипликатора 1823 матрицы T-1 становится вторым вектором P2 контроля по четности. Каждый из переключателей 1825, 1827 и 1829 включается только в его время передачи для передачи относящегося к нему сигнала. Переключатель 1825 включается на время передачи вектора «s» информационного слова, переключатель 1827 включается на время передачи первого вектора P1 контроля по четности, и переключатель 1829 включается на время передачи второго вектора P2 контроля по четности. Когда к порождающей матрице контроля по четности применяется схема с перфорированием, контроллер 1810 управляет переключателем 1627 и переключателем 1629 для перфорирования контрольного слова в зависимости от соответствующей скорости кодирования.

Ниже в описании более подробно изложено что, так как варианты осуществления настоящего изобретения должны допускать генерацию блочного LDPC-кода с переменной скоростью кодирования, каждая из матриц, используемых в устройстве кодирования блочного LDPC-кода с переменной скоростью кодирования, показанном на фиг.18, изменяется всякий раз, когда изменяется матрица контроля по четности блочного LDPC-кода с переменной скоростью кодирования. Поэтому, хотя и на фиг. 18 не показано отдельно, контроллер 1810 изменяет матрицы, применяемые в кодирующем устройстве для блочного LDPC-кода с переменной скоростью кодирования, изменяется матрица контроля по четности блочного LDPC-кода с переменной скоростью кодирования.

Все коды семейства LDPC-кодов можно декодировать в фактор-графе с использованием алгоритма суммы-произведения. Схему декодирования LDPC-кода можно приближенно разделить на двунаправленную схему передачи данных и схему передачи потока. Когда операция декодирования выполняется с использованием двунаправленной схемы передачи данных, каждая проверочная вершина содержит процессор вершины, что повышает сложность декодирования пропорционально числу проверочных вершин. Однако, так как все проверочные вершины обновляются одновременно, скорость декодирования заметно повышается. И, наоборот, схема передачи потока содержит единственный процессор вершины, и процессор вершины обновляет информацию с проходом по всем вершинам в фактор-графе. Поэтому сложность декодирования в схеме передачи потока ниже, но увеличение размерности матрицы контроля по четности, т.е. увеличение числа вершин, снижает скорость декодирования.

Однако, если матрица контроля по четности создается на каждый блок наподобие блочного LDPC-кода с переменной скоростью кодирования, обладающего различными скоростями кодирования, предлагаемого в настоящем изобретении, то применяется столько процессоров вершин, сколько имеется блоков, составляющих матрицу контроля по четности. В данном случае можно реализовать декодер, который характеризуется меньшей сложностью декодирования, чем двунаправленная схема передачи данных, и более высокой скоростью декодирования, схема передачи потока.

На фиг.19 представлена блок-схема, иллюстрирующая внутреннюю конструкцию устройства для декодирования блочного LDPC-кода с переменной скоростью кодирования в соответствии с вариантами осуществления настоящего изобретения. Как видно из фиг.19, декодирующее устройство для декодирования блочного LDPC-кода с переменной скоростью кодирования содержит блочный контроллер 1910, секцию 1900 переменной вершины, сумматор 1915, обратный перемежитель 1917, перемежитель 1919, контроллер 1921, память 1923, сумматор 1925, секцию 1950 проверочной вершины и жесткий решающий модуль 1929. Секция 1900 переменной вершины содержит декодер 1911 переменной вершины и переключатели 1913 и 1914, и секция 1950 проверочной вершины содержит декодер 1927 проверочной вершины.

Сигнал, принятый по радиоканалу? вводится в блочный контроллер 1910. Блочный контроллер 1910 определяет размер блока принятого сигнала. Если имеется часть информационного слова, перфорированная в кодирующем устройстве, соответствующем декодирующему устройству, блочный контроллер 1910 вставляет «0» в перфорированную часть информационного слова для коррекции полного размера блока и выдает результирующий сигнал в декодер 1911 переменной вершины. Блочный контроллер 1910 содержит предварительно сохраненную информацию о способе применения схемы с сокращением и схемы с перфорированием к порождающей матрице контроля по четности в зависимости от соответствующей скорости кодирования, заданной между декодирующим устройством и соответствующим ему кодирующим устройством. В данном случае информация о способе применения схемы с сокращением и схемы с перфорированием к порождающей матрице контроля по четности в зависимости от соответствующей скорости кодирования содержит информацию о числе сокращенных или перфорированных частичных блоков и информацию о позициях сокращенных или перфорированных частичных блоков. Поэтому блочный контроллер 1910 исключает части, сокращаемые в зависимости от скорости кодирования, применяемой в кодирующем устройстве, из принимаемого сигнала, вставляет значение «0» LLR в перфорированные части и выдает полученные сигналы в декодер 1911 переменной вершины.

Декодер 1911 переменной вершины вычисляет значения вероятностей сигнала, выдаваемого блочным контроллером 1910, обновляет вычисленные значения вероятностей и выводит обновленные значения вероятностей в переключатели 1913 и 1914. Декодер 1911 переменной вершины связывает переменные вершины соответственно матрице контроля по четности, ранее установленной в декодирующем устройстве для блочных LDPC-кодов с переменной скоростью кодирования, и выполняет операцию обновления на таком количестве входных значений и выходных значений, которое равно количеству значений 1, связанных с переменными вершинами. Количество значений 1, связанных с переменными вершинами, равно весу каждого из столбцов, содержащихся в матрице контроля по четности. Внутреннее функционирование декодера 1911 переменной вершины изменяется в зависимости от веса каждого из столбцов, содержащихся в матрице контроля по четности. Однако, когда переключатель 1913 включен, переключатель 1914 включен на вывод выходного сигнала декодера 1911 переменной вершины в сумматор 1915.

Сумматор 1915 получает сигнал, выдаваемый декодером 1911 переменной вершины, и выходной сигнал перемежителя 1919 от предшествующего процесса итеративного декодирования, вычитает выходной сигнал перемежителя 1919 от предшествующего процесса итеративного декодирования из выходного сигнала декодера 1911 переменной вершины и выдает результат вычитания в обратный перемежитель 1917. Если процесс декодирования является процессом начального декодирования, то выходной сигнал перемежителя 1919 должен приниматься равным 0.

Обратный перемежитель 1917 выполняет обратное перемежение сигнала, выдаваемого сумматором 1915, в зависимости от заданной схемы перемежения, и выдает сигнал, обработанный обратным перемежением, в сумматор 1925 и декодер 1927 проверочной вершины. Обратный перемежитель 1917 имеет внутреннюю конструкцию, соответствующую матрице контроля по четности, так как выходное значение, используемое для формирования входного значения перемежителя 1919, соответствующего обратному перемежителю 1917, различается в зависимости от позиции элементов, имеющих значение 1 в матрице контроля по четности.

Сумматор 1925 получает сигнал, выданный декодером 1927 проверочной вершины, от предшествующего процесса итеративного декодирования и выходной сигнал обратного перемежителя 1917, вычитает выходной сигнал обратного перемежителя 1917 из выходного сигнала декодера 1927 проверочной вершины от предшествующего процесса итеративного декодирования и выдает результат вычитания в перемежитель 1919. Декодер 1927 проверочной вершины связывает проверочные вершины в зависимости от матрицы контроля по четности, предварительно установленной в декодирующем устройстве для блочного LDPC-кода, и выполняет операцию обновления на входных значениях и выходных значениях, количество которых равно количеству значений 1, связанных с проверочными вершинами. Количество значений 1, связанных с проверочными вершинами, равно весу каждой из строк, составляющих матрицу контроля по четности. Поэтому внутреннее функционирование декодера 1927 проверочных вершин изменяется в зависимости от веса каждой из строк, составляющих матрицу контроля по четности.

Перемежитель 1919 под управлением контроллера 1921, перемежает сигнал, выдаваемый сумматором 1925, соответственно заданной схеме перемежения и выдает перемеженный сигнал в сумматор 1915 и декодер 1911 переменной вершины. Контроллер 1921 считывает информацию, относящуюся к схеме перемежения, предварительно сохраненную в памяти 1923, и управляет схемой перемежения перемежителя 1919 и схемой обратного перемежения обратного перемежителя 1917 в зависимости от считанной информации о схеме перемежения. Аналогично, если процесс декодирования является процессом начального декодирования, то выходной сигнал обратного перемежителя 1917 должен приниматься равным 0.

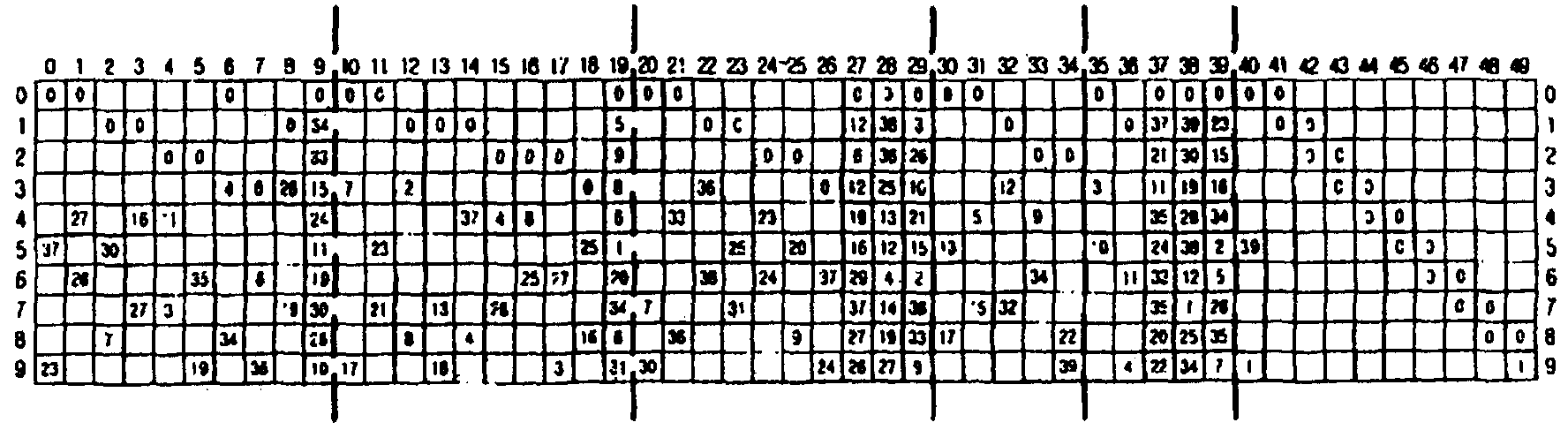

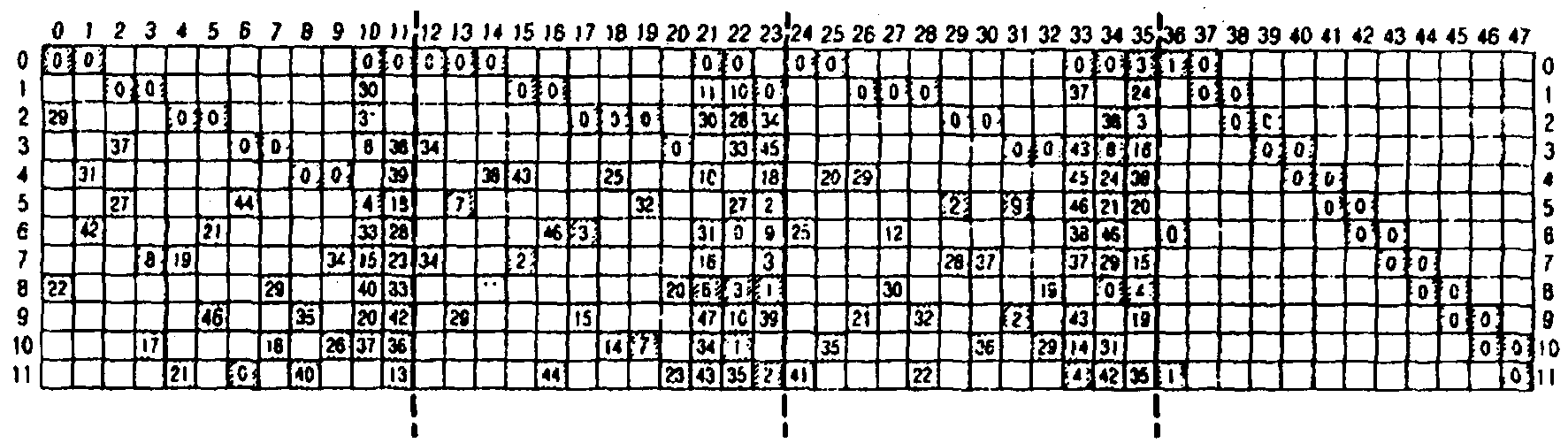

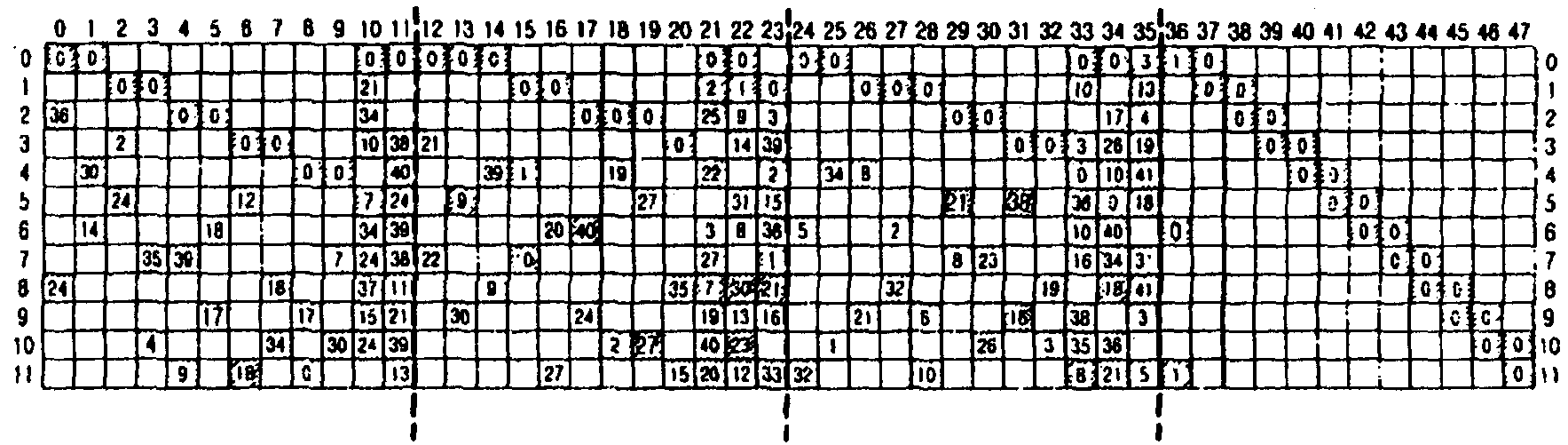

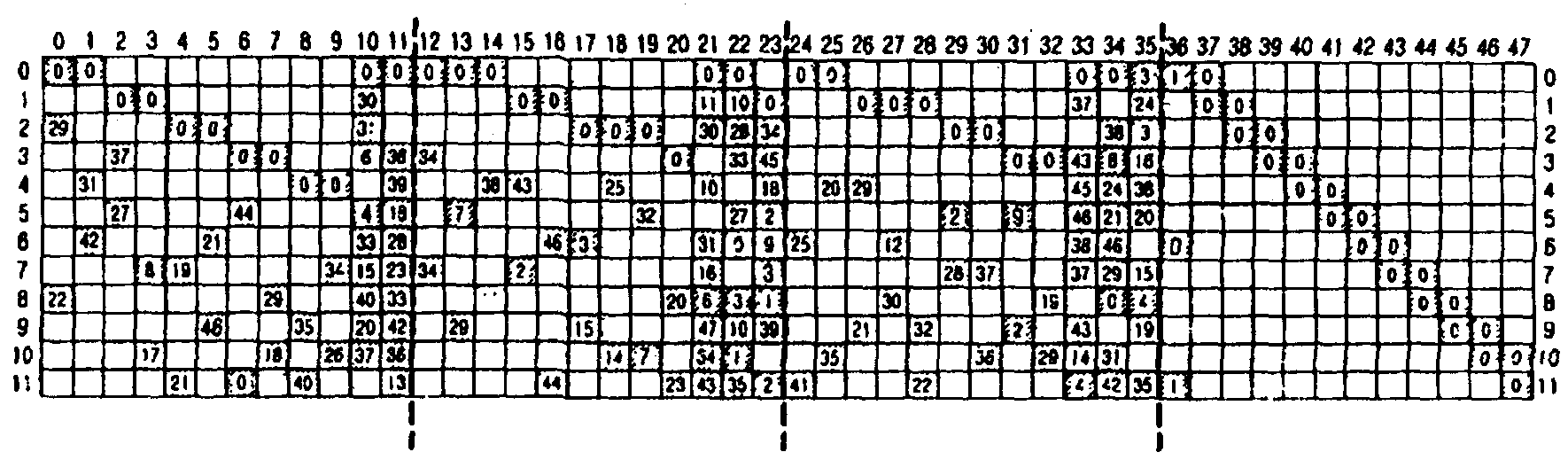

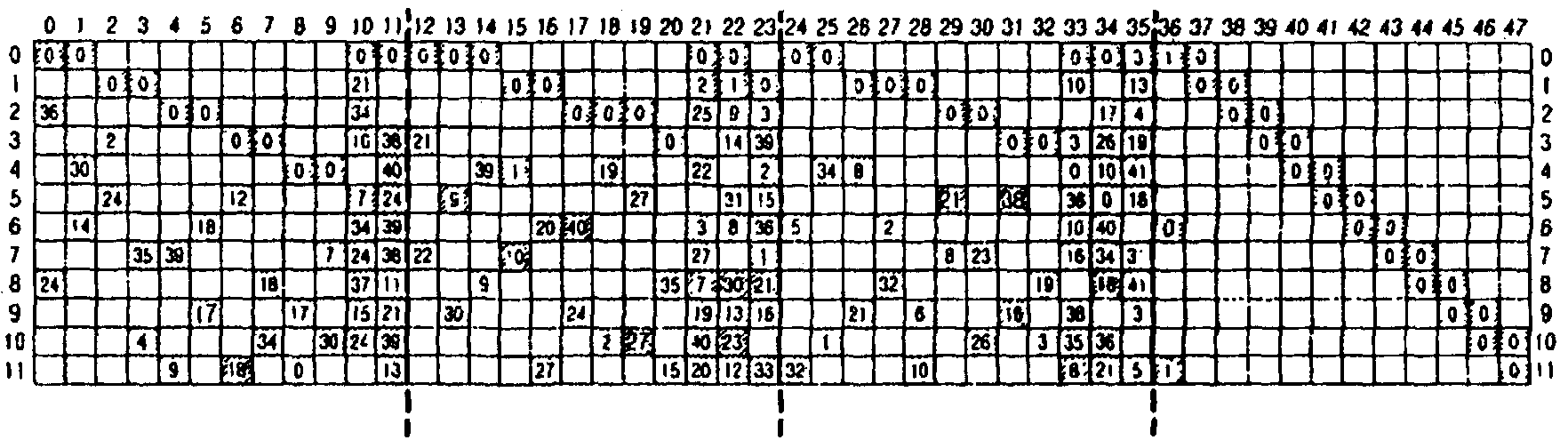

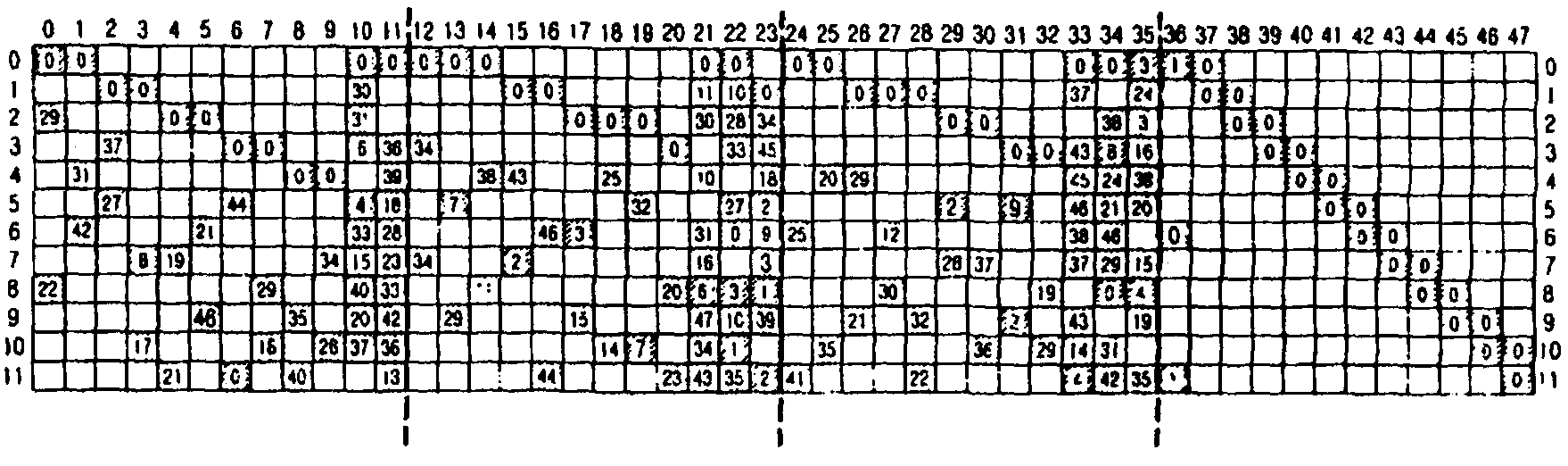

Посредством итеративного выполнения вышеописанных процессов декодирующее устройство выполняет надежное безошибочное декодирование. После того, как итеративное декодирование выполнено заданное число раз, переключатель 1914 отключает соединение между декодером 1911 переменной вершины и сумматором 1915, и переключатель 1913 включает соединение между декодером 1911 переменной вершины и жестким решающим модулем 1929 для обеспечения вывода сигнала из декодера 1911 переменной вершины в жесткий решающий модуль 1929. Жесткий решающий модуль 1929 выполняет жесткое решение относительно сигнала, выданного из декодера 1911 переменной вершины, и выдает результат жесткого решения, и выходное значение жесткого решающего модуля 1929 становится окончательно декодированным значением.