Устройство и способ кодирования-декодирования блочного кода проверки на четность с низкой плотностью с переменной длиной блока - RU2369008C2

Код документа: RU2369008C2

Чертежи

Описание

Область техники, к которой относится изобретение

Настоящее изобретение, в общем, относится к системе мобильной связи, и в частности к устройству и способу кодирования/декодирования блочных кодов проверки на четность с низкой плотностью (LDPC, ПЧНП).

Уровень техники

В результате быстрого развития систем мобильной связи возникла необходимость разработки технологии, позволяющей передавать большие массивы данных, приближаясь к пропускной способности кабельной сети в беспроводной среде связи. Для удовлетворения все увеличивающейся потребности в высокоскоростной системе связи, работающей с высокой пропускной способностью, которая позволяет обрабатывать и передавать различные данные, такие как данные изображения и радиоданные, помимо услуги, ориентированной на голосовую передачу, требуется повысить эффективность передачи системы, используя соответствующую схему кодирования канала, чтобы, таким образом, улучшить общие рабочие характеристики системы. Однако мобильная система связи, с учетом ее характеристик, неизбежно генерирует ошибки во время передачи данных из-за шумов, помех и затухания, в соответствии с условиями канала. Генерирование ошибок приводит к потере большого количества информационных данных.

Для предотвращения потери информационных данных в результате генерирования ошибок в настоящее время используют различные схемы управления ошибками, которые частично основаны на характеристиках канала, чтобы, таким образом, повысить надежность системы мобильной связи. В наиболее типичной схеме управления ошибками используют коды коррекции ошибок.

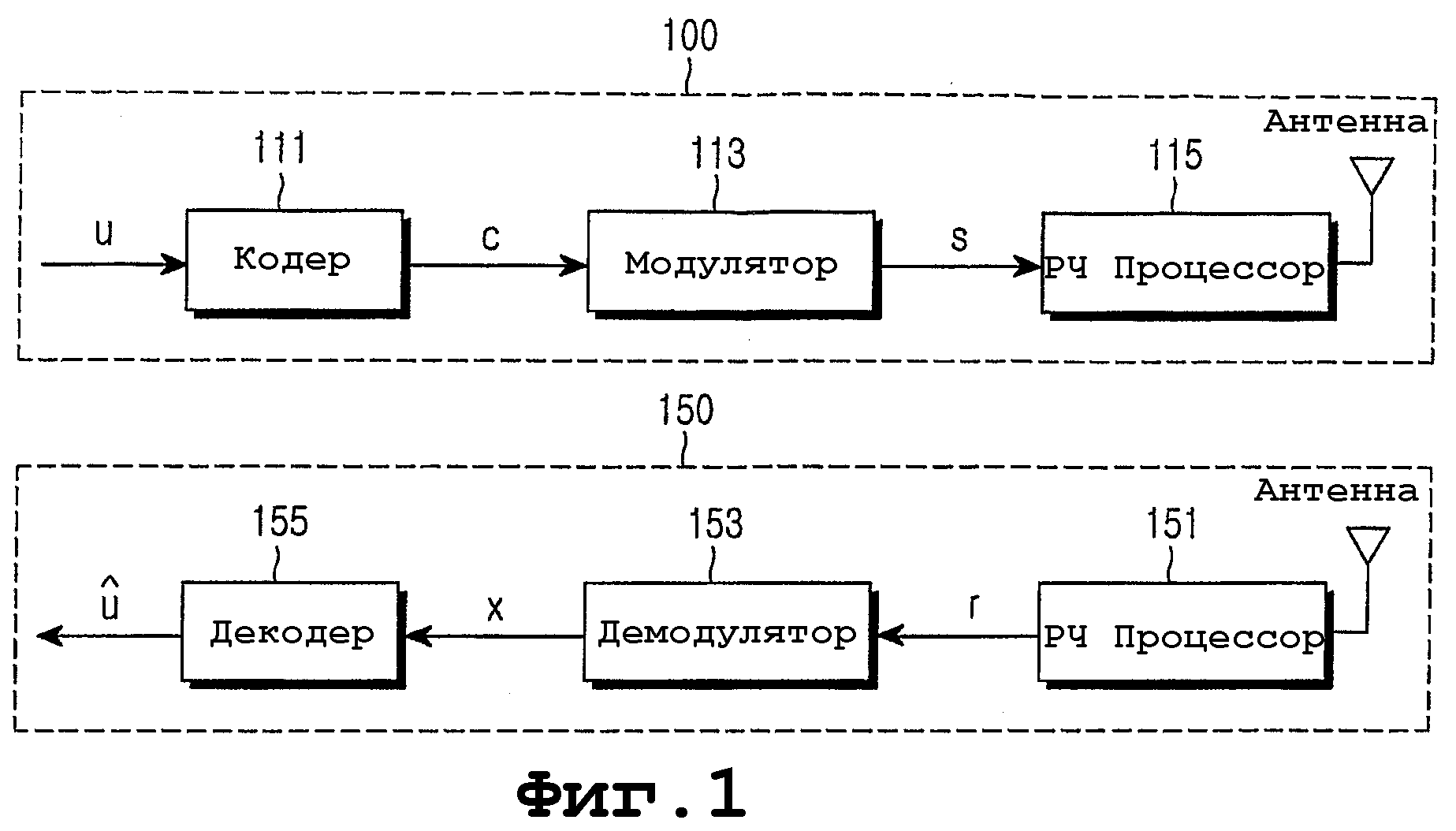

Ниже, со ссылкой на фиг. 1, приведено описание структуры передатчика/приемника в общей системе мобильной связи.

На фиг. 1 показана схема, иллюстрирующая структуру передатчика/приемника в общей системе мобильной связи. Как показано на фиг. 1, передатчик 100 включает в себя кодер 111, модулятор 113 и радиочастотный (RF, РЧ) процессор 115, и приемник 150 включает в себя РЧ процессор 151, демодулятор 153 и декодер 155.

В передатчике 100, если генерируют информационные данные "u", предназначенные для передачи, их передают в кодер 111. Кодер 111 генерирует кодированный символ "c" путем кодирования информационных данных "u", используя заданную схему кодирования, и выводит кодированный символ "c" в модулятор 113. Модулятор 113 генерирует символ "s" модуляции в результате модуляции кодированного символа "c" использованием заданной схемы модуляции и выводит символ "s" модуляции в РЧ процессор 115. РЧ процессор 115 выполняет РЧ обработку символа модуляции "s", поступающего с выхода модулятора 113, и передает сигнал после РЧ обработки по беспроводному каналу связи через антенну ANT (АНТ).

Сигнал, переданный по беспроводному каналу связи передатчиком 100, таким образом, принимают в приемнике 150 через его антенну АНТ, и сигнал, принятый через антенну, подают в РЧ процессор 151. РЧ процессор 151 выполняет РЧ обработку принятого сигнала и выводит сигнал "r" после РЧ обработки в демодулятор 153. Демодулятор 153 демодулирует сигнал "r" после РЧ обработки, поступающий с выхода РЧ процессора 151, используя схему демодуляции, соответствующую схеме модуляции, использованной в модуляторе 113, и выводит демодулированный сигнал "x" в декодер 155. Декодер 155 декодирует демодулированный сигнал "x", поступающий с выхода демодулятора 153, используя схему декодирования, соответствующую схеме кодирования, использованной в кодере 111, и выводит декодированный сигнал "u" в качестве окончательно декодированных информационных данных.

Для обеспечения возможности декодирования без ошибок в приемнике 150 информационных данных "u", переданных передатчиком 100, необходимо использовать высокоэффективный кодер и декодер. В частности, поскольку требуется учитывать среду радиоканала и характеристики мобильной системы связи, следует более серьезно учитывать ошибки, которые могут быть сгенерированы под влиянием среды радиоканала.

Наиболее типичные коды коррекции ошибки включают в себя турбокоды и коды проверки на четность с низкой плотностью (LDPC).

Известно, что турбокод обеспечивает лучшее повышение рабочих характеристик по сравнению со сверточным кодом, который обычно используют для коррекции ошибок во время передачи данных с высокой скоростью. Преимущество турбокода состоит в том, что он позволяет эффективно корректировать ошибку, вызванную шумами, генерируемыми в канале передачи данных, повышая, таким образом, надежность передачи данных. Код LDPC можно декодировать, используя итеративный алгоритм декодирования, основанный на алгоритме суммирования-умножения в фактор-графе. Поскольку в декодере для кода LDPC используют итеративный алгоритм декодирования на основе алгоритма суммирования-умножения, он является менее сложным, чем декодер для турбокода. Кроме того, декодер для кода LDPC легко воплотить на практике, используя декодер параллельной обработки, по сравнению с декодером для турбокода.

Теорема Шеннона кодирования канала показывает, что надежная связь возможна только при скорости передачи данных, не превышающей пропускную способность канала. Однако теорема Шеннона кодирования канала не предлагает подробный способ кодирования/декодирования канала для поддержания скорости передачи данных вплоть до максимальной предельной пропускной способности канала. Обычно, хотя случайный код, имеющий очень большой размер блока, проявляет рабочие характеристики, приближающиеся к предельному значению пропускной способности канала в соответствии с теоремой Шеннона кодирования канала, на практике, при использовании способа декодирования MAP (maximum a posteriori, МАВ (максимум апостериорной вероятности)) или ML (МП, максимального правдоподобия), невозможно выполнить этот способ декодирования из-за чрезвычайно большой вычислительной нагрузки.

Турбокод был предложен авторами Berrou, Glavieux и Thitimajshima в 1993 г., и он проявляет исключительные рабочие характеристики, которые приближаются к предельному значению пропускной способности канала в соответствии с теоремой Шеннона кодирования канала. Появление турбокода инициировало активное исследование в области итерационного декодирования и графического выражения кодов, в результате коды LDPC, предложенные автором Gallager в 1962 г., вышли на первый план в этих исследованиях. В фактор-графе турбокода и кода LDPC существуют циклы, и известно, что итерационное декодирование в фактор-графе кода LDPC, в котором существуют циклы, является субоптимальным. Кроме того, экспериментально было подтверждено, что код LDPC обладает исключительными характеристиками при использовании итеративного декодирования. Код LDPC, как известно, проявляет наилучшие характеристики, отличающиеся только приблизительно на 0,04 [дБ] от предельного значения пропускной способности канала, в соответствии с теоремой Шеннона кодирования канала, с частотой передачи ошибочных битов (BER, ЧБО) 10-5, при использовании размера блока 107. Кроме того, хотя сложность процесса декодирования кода LDPC, определенного в поле Галуа (GF, ПГ) при q > 2, то есть GF(q), увеличивается, его характеристики намного превышают двоичный код. При этом, однако, отсутствует удовлетворительное теоретическое описание успешного декодирования с использованием итеративного алгоритма декодирования для кода LDPC, определенного в GF(q).

Код LDPC, предложенный автором Gallager, определен по матрице проверки на четность, в которой большая часть элементов имеет значение 0 и меньшая часть элементов, за исключением элементов, имеющих значение 0, имеет ненулевое значение, например значение, равное 1. В следующем описании предполагается, что не равное нулю значение представляет собой значение, равное 1.

Например, код LDPC (N, j, k) представляет собой линейный блочный код, имеющий длину блока N, и определен как разреженная матрица проверки на четность, в которой каждый столбец имеет j элементов, имеющих значение 1, каждая строка имеет k элементов, имеющих значение 1, и все элементы, за исключением элементов, имеющих значение 1, имеют значение 0.

Код LDPC, в котором вес каждого столбца в матрице проверки на четность фиксирован значением "j" и вес каждой строки в матрице проверки на четность фиксирован значением "k", как описано выше, называется "регулярным кодом LDPC". Здесь "вес" относится к количеству элементов, имеющих ненулевое значение, среди элементов, составляющих матрицу проверки на четность. В отличие от регулярного кода LDPC, код LDPC, в котором не фиксированы вес каждого столбца и вес каждой строки в матрице проверки на четность, называется "нерегулярным кодом LDPC". Общеизвестно, что нерегулярный код LDPC обладает лучшими характеристиками по сравнению с регулярным кодом LDPC. Однако в случае нерегулярного кода LDPC, поскольку вес каждого столбца и вес каждой строки в матрице проверки на четность не фиксирован, то есть является нерегулярным, вес каждого столбца в матрице проверки на четность и вес каждой строки в матрице проверки на четность необходимо соответствующим образом регулировать для гарантирования лучших рабочих характеристик.

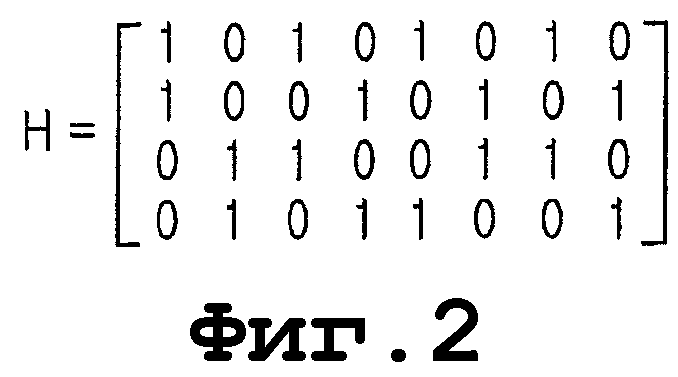

Ниже, со ссылкой на фиг. 2, приведено описание матрицы проверки на четность кода LDPC (8, 2, 4) в качестве примера кода LDPC (N, j, k).

На фиг. 2 показана схема, иллюстрирующая матрицу проверки на четность для общего кода LDPC (8, 2, 4). Как показано на фиг. 2, матрица H проверки на четность кода LDPC (8, 2, 4) состоит из 8 столбцов и 4 строк, в которой вес каждого столбца фиксирован и равен 2 и вес каждой строки фиксирован и равен 4. Поскольку вес каждого столбца и вес каждой строки в матрице проверки на четность является регулярным, как указано выше, код LDPC (8, 2, 4), представленный на фиг. 2, становится регулярным кодом LDPC.

Матрица проверки на четность кода LDPC (8, 2, 4) была описана выше со ссылкой на фиг. 2. Далее, со ссылкой на фиг. 3, будет описан фактор-граф кода LDPC (8, 2, 4), описанного со ссылкой на фиг. 2.

На фиг. 3 показана схема, иллюстрирующая фактор-граф кода LDPC (8, 2, 4) по фиг. 2. Как показано на фиг. 3, фактор-граф кода LDPC (8, 2, 4) состоит из 8 переменных узлов x1 300, x2 302, x3 304, x4 306, x5 308, x6310, x7 312 и x8 314 и 4 узлов 316, 318, 320 и 322 проверки. Когда элемент, имеющий значение 1, то есть имеющий значение, не равное нулю, существует в точке, в которой i-ая строка и j-ый столбец матрицы проверки на четность кода LDPC (8, 2, 4) пересекаются друг с другом, между переменным узлом xi и j-ым узлом проверки, формируется ответвление.

Поскольку матрица проверки на четность кода LDPC имеет очень небольшой вес, как описано выше, становится возможным выполнить декодирование, используя итеративное декодирование даже в блочном коде, имеющем относительно большую длину, который проявляет рабочую характеристику, приближающуюся к предельному значению пропускной способности канала для теоремы Шеннона кодирования канала, таком как турбокод, при постоянном увеличении длины блока блочного кода. Авторы MacKay и Neal доказали, что процесс итеративного декодирования кода LDPC с использованием схемы передачи потока приближается по своим рабочим характеристикам к процессу итеративного декодирования турбокода.

Для генерирования кода LDPC с высокими рабочими характеристиками следует удовлетворить следующие условия.

(1) Следует учитывать циклы фактор-графа кода LDPC.

Термин "цикл" относится к петле, формируемой ребрами, соединяющими переменные узлы с узлами проверки в фактор-графе кода LDPC, и длина цикла определена количеством ребер, составляющих петлю. Длинный цикл означает, что количество ребер, соединяющих переменные узлы с узлами проверки, составляющими петлю в фактор-графе кода LDPC, велико. В отличие от этого, короткий цикл означает, что количество ребер, соединяющих переменные узлы с узлами проверки, составляющими петлю в фактор-графе кода LDPC, невелико.

По мере того, как циклы в фактор-графе кода LDPC становятся более длинными, эффективность рабочих характеристик кода LDPC повышается по следующим причинам. Когда длинные циклы генерируют в фактор-графе кода LDPC, становится возможным предотвратить снижение такой характеристики, как минимальный уровень ошибок, возникающий, когда в фактор-графе кода LDPC существуют слишком много циклов с короткой длиной.

(2) Следует учитывать эффективное кодирование кода LDPC.

Для кода LDPC трудно выполнить кодирование в режиме реального времени по сравнению со сверточным кодом или турбокодом из-за высокой сложности кодирования. Для снижения сложности кодирования кода LDPC был предложен код повторного накопления (RA, ПН). Однако код RA также имеет ограничения в отношении снижения сложности кода LDPC. Поэтому следует учитывать эффективное кодирование кода LDPC.

(3) Следует учитывать степень распределения фактор-графа кода LDPC.

Обычно нерегулярный код LDPC обладает лучшими характеристиками по сравнению с регулярным кодом LDPC, поскольку фактор-граф нерегулярного кода LDPC имеет различные степени. Термин "степень" относится к количеству ребер, соединенных с переменными узлами, и узлами проверки в фактор-графе кода LDPC. Кроме того, фраза "распределение степени" фактор-графа кода LDPC относится к отношению количества узлов, имеющих определенную степень, к общему количеству узлов. Автор Richardson доказал, что код LDPC, имеющий определенную степень распределения, обладает лучшими характеристиками.

Далее, со ссылкой на фиг. 4, будет приведено описание матрицы проверки на четность блочного кода LDPC.

На фиг. 4 показана схема, иллюстрирующая матрицу проверки на четность общего блочного кода LDPC. Перед описанием фиг. 4, следует отметить, что блочный код LDPC представляет собой новый код LDPC, для которого не учитывается не только эффективное кодирование, но также и эффективное хранение и улучшение рабочих характеристик матрицы проверки на четность, и блочный код LDPC представляет собой код LDPC, продолженный путем обобщения структуры регулярного кода LDPC. Как показано на фиг. 4, матрица проверки на четность блочного кода LDPC разделена на множество частичных блоков, и матрицу перестановок отображают на каждом из частичных блоков. На фиг. 4 "P" представляет собой матрицу перестановок, имеющую размер Ns×Ns, и верхний индекс (или экспоненту) apq матрицы перестановок P равен либо 0 < apq < Ns-1 или apq= ∞.

Кроме того, "p" обозначает, что соответствующая матрица перестановок расположена в p-ой строке частичных блоков матрицы проверки на четность, и "q" обозначает, что соответствующая матрица перестановок расположена в q-ом столбце частичных блоков матрицы проверки на четность. Таким образом,

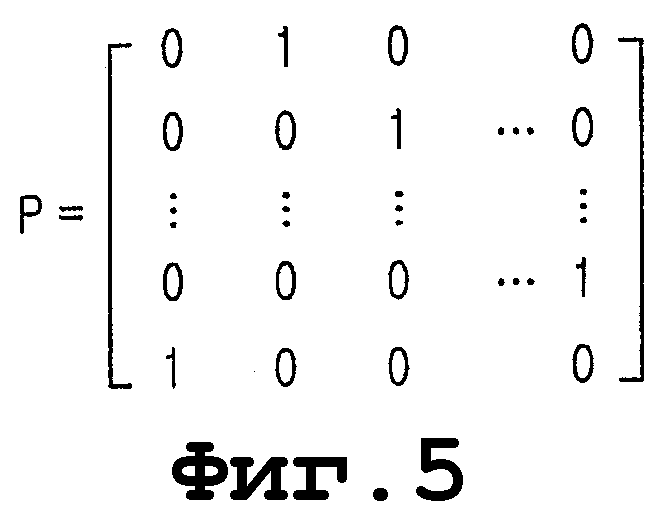

Матрица перестановок будет описана ниже со ссылкой на фиг. 5.

На Фиг. 5 показана схема, иллюстрирующая матрицу P перестановок по фиг. 4. Как показано на фиг. 5, матрица P перестановок представляет собой квадратную матрицу, имеющую размер Ns×Ns, и каждый из Nsстолбцов, составляющих матрицу P перестановок, имеет вес 1, и каждая из Nsстрок, составляющих матрицу P перестановок, также имеет вес 1. Здесь, хотя размер матрицы P перестановок выражен, как Ns×Ns, он также может быть выражен как Ns, поскольку матрица P перестановок представляет собой квадратную матрицу.

На фиг. 4 матрица P перестановок с верхним индексом apq=0, то есть матрица P° перестановок представляет собой единичную

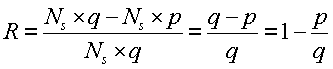

Во всей матрице проверки на четность блочного кода LDPC, представленного на фиг. 4, поскольку общее количество строк равно Ns×p и общее количество столбцов равно Ns×q (для p ≤ q), когда вся матрица проверки на четность кода LDPC имеет полный ранг, скорость кодирования может быть выражена как уравнение (1) независимо от размера частичных блоков.

Если apq≠∞ для всех p и q, матрицы перестановок, соответствующие частичным блокам, представляют собой не нулевые матрицы, и частичные блоки составляют регулярный код LDPC, в котором весовое значение каждого столбца и весовое значение каждой строки в каждой из матриц перестановок, соответствующих частичным блокам, равны p и q соответственно. Здесь каждая из матриц перестановок, соответствующая частичным блокам, будет называться "частичной матрицей".

Поскольку (p-1) зависимых строк существуют во всей матрице проверки на четность, получают более высокую скорость кодирования, чем скорость кодирования, рассчитанная по уравнению (1). В случае блочного кода LDPC, если будет определено положение веса первой строки каждой из частичных матриц, составляющих всю матрицу проверки на четность, также можно будет определить положение весов для остальных строк (Ns- 1). Поэтому требуемый размер памяти уменьшается до 1/Ns по сравнению со случаем, когда веса выбирают нерегулярно для сохранения информации по всей матрице проверки на четность.

Как описано выше, термин "цикл" относится к петле, формируемой ребрами, соединяющими различные узлы с узлами проверки в фактор-графе кода LDPC, и длина цикла определяется как количество ребер, составляющих петлю. Длинный цикл означает, что количество ребер, соединяющих переменные узлы с узлами проверки, составляющими петлю в фактор-графе кода LDPC, велико. По мере того, как циклы в фактор-графе кода LDPC становятся более длинными, эффективность рабочих характеристик кода LDPC повышается.

В отличие от этого, по мере того, как циклы в фактор-графе кода LDPC становятся более короткими, возможности коррекции ошибки кода LDPC снижаются из-за деградации рабочих характеристик в результате возникновения минимального уровня ошибок. То есть в случае, когда в фактор-графе кода LDPC существует множество циклов с короткой длиной, информация о конкретном узле, принадлежащем циклу с более короткой длиной, начинающемуся от него, возвращается после небольшого количества итераций. По мере увеличения количества итераций информация возвращается к соответствующему узлу более часто, в результате чего информация не может быть правильно обновлена, что приводит к ухудшению способности коррекции ошибок кода LDPC.

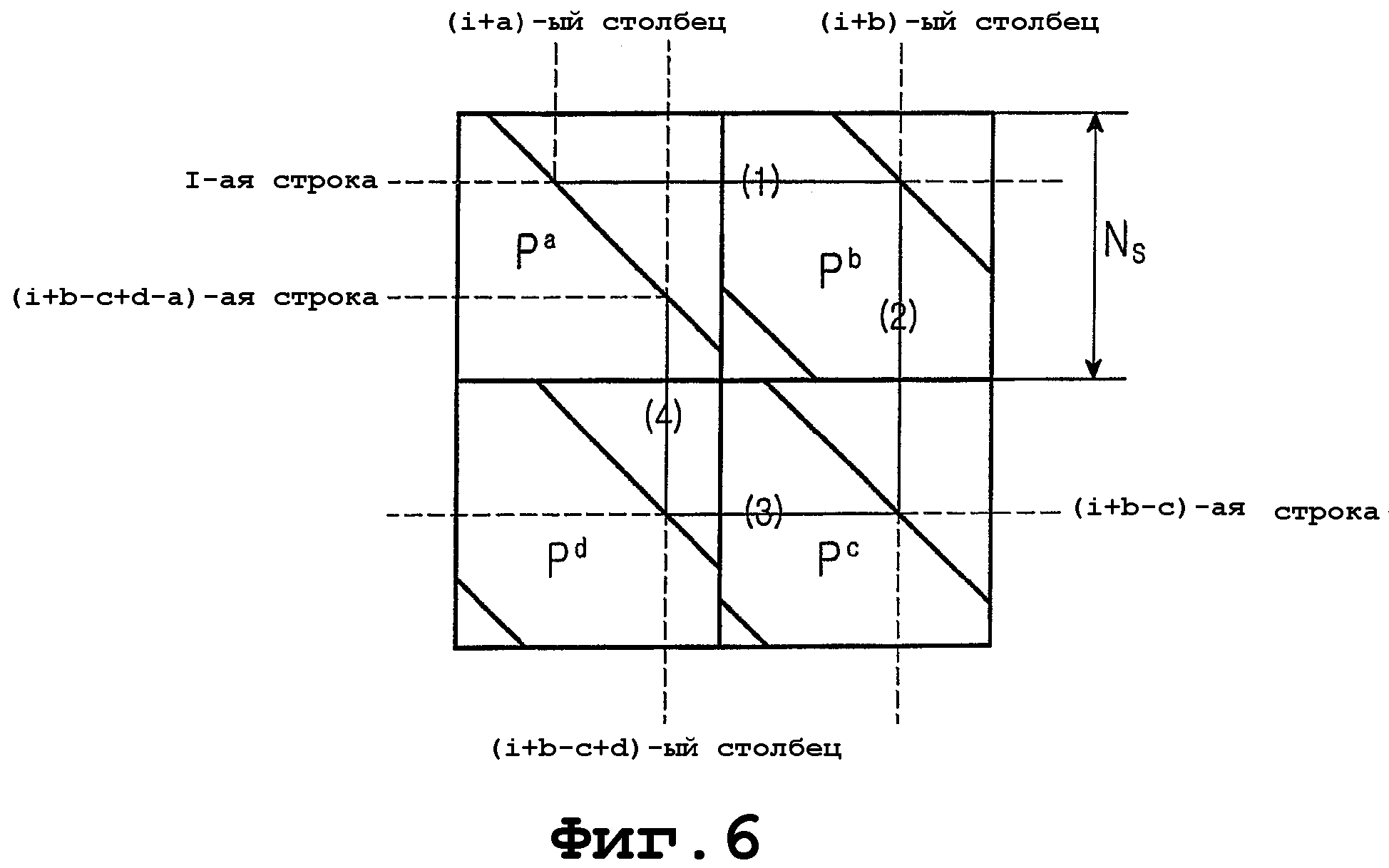

Ниже, со ссылкой на фиг. 6, приведено описание структуры цикла блочного кода LDPC.

На фиг. 6 показана схема, иллюстрирующая структуру цикла блочного кода LDPC, в котором матрица проверки на четность состоит из 4 частичных матриц. Перед описанием фиг. 6, следует отметить, что блочный код LDPC представляет собой новый код LDPC, для которого учитывается не только эффективное кодирование, но также и эффективное сохранение, и улучшение рабочих характеристик матрицы проверки на четность. Блочный код LDPC также представляет собой код LDPC, расширенный путем обобщения структуры регулярного кода LDPC. Матрица проверки на четность блочного кода LDPC, представленного на фиг. 6, состоит из 4 частичных блоков, диагональная линия представляет положение, где расположены элементы, имеющие значение 1, и другие части, кроме участков, расположенных на диагональной линии, представляют собой положения, где расположены элементы, имеющие значение, равное 0. Кроме того, "P" представляет ту же матрицу перестановок, что и матрица перестановок, описанная со ссылкой на фиг. 5.

Для анализа структуры цикла блочного кода LDPC, представленного на фиг. 6, элемент, имеющий значение 1, расположенный в i-ой строке частичной матрицы Pa, определен как эталонный элемент, и элемент, имеющий значение 1, расположенный в i-ой строке, будет называться " точкой 0 ". Здесь "частичная матрица" относится к матрице, соответствующей частичному блоку. Точка 0 расположена в (i+a)-ом столбце частичной матрицы Pa.

Элемент, имеющий значение 1 в частичной матрице Pb, расположенный в той же строке, что и точка 0, называется "точкой 1". По той же причине, что и точка 0, точка 1 расположена в (i+b)-ом столбце частичной матрицы Pb.

Далее элемент, имеющий значение 1 в частичной матрице Pc, расположенный в том же столбце, что и точка 1, будет называться "точкой 2". Поскольку частичная матрица Pc представляет собой матрицу, полученную путем сдвига соответствующих столбцов единичной матрицы I вправо относительно модуля Ns на c, точка 2 расположена в (i+b-c)-ой строке частичной матрицы Pc.

Кроме того, элемент, имеющий значение 1 в частичной матрице Pd, расположенный в той же строке, что и точка 2, будет называться "точкой 3". Точка 3 расположена в (i+b-c+d)-ом столбце частичной матрицы Pd.

Наконец, элемент, имеющий значение 1, в частичной матрицу Pa, расположенный в том же столбце, что и точка 3, будет называться "точкой 4". Точка 4 расположена в (i+b-c+d-a)-ой строке частичной матрицы Pa.

В структуре цикла кода LDPC, представленного на фиг. 6, если существует цикл с длиной 4, точка 0 и точка 4 расположены в одном и том же положении. То есть взаимосвязь между точкой 0 и точкой 4 определена уравнением (2)

Уравнение (2) может быть переписано как уравнение (3)

В результате, когда удовлетворяется взаимозависимость по уравнению (3), генерируется цикл с длиной 4. Обычно, когда точка 0 и точка 4p представляют собой первые идентичные друг другу точки, задается соотношение i

(modNs), и удовлетворяется следующее соотношение, показанное в уравнении (4)

Другими словами, если положительное целое число, имеющее минимальное значение среди положительных целых чисел, удовлетворяющих уравнение (4) для заданных a, b, c и d определено как "p", цикл с длиной 4p становится циклом, имеющим минимальную длину в структуре цикла блочного кода LDPC, представленного на фиг. 6.

В заключение, как описано выше, для (a-b+c-d) ≠ 0, если удовлетворяется условие gcd (Ns, a-b+c-d) = 1, тогда p = Ns. Здесь, gcd (Ns, a-b+c-d) представляет собой функцию для расчета "наибольшего общего делителя" для целых чисел Nsи a-b+c-d. Поэтому цикл с длиной 4NS становится циклом с минимальной длиной.

Методика Richardson-Urbanke будет использоваться как методика кодирования для кода блока LDPC. Поскольку методика Richardson-Urbanke используется как методика кодирования, степень кодирования можно минимизировать, по мере того, как форма матрицы проверки на четность становится аналогичной форме полной нижней треугольной матрицы.

Ниже, со ссылкой на фиг. 7, приведено описание матрицы проверки на четность, имеющей форму, аналогичную форме полной нижней треугольной матрицы.

На фиг. 7 показана схема, иллюстрирующая матрицу проверки на четность, имеющую форму, аналогичную форме полной нижней треугольной матрицы. Матрица проверки на четность, представленная на фиг. 7, отличается от матрицы проверки на четность, имеющей форму полной нижней треугольной матрицы, формой части проверки на четность. На фиг. 7 верхний индекс (или экспонента) apq матрицы P перестановок информационной части составляет либо 0 ≤ apq ≤ Ns- 1 или apq= ∞, как описано выше. Матрица P перестановок с верхним индексом apq=0, то есть матрица P0 перестановок в информационной части представляет собой единичную матрицу Ns×Ns, и матрица P перестановок с верхним индексом apq = ∞, то есть, матрица P∞ перестановок представляет собой нулевую матрицу. На фиг. 7 "p" представляет собой количество строк частичных блоков, отображенных на информационную часть, и "q" представляет собой количество столбцов частичных блоков, отображенных на часть проверки на четность. Кроме того, верхние индексы ap, x и y матриц P перестановок, отображенных на часть проверки на четность, представляют собой экспоненты матрицы P перестановок. Однако, для удобства пояснения, различные верхние индексы ap, x и y используются для различения части проверки на четность от информационной части. То есть на фиг. 7,

Самая большая проблема кода LDPC, имеющего матрицу проверки на четность по фиг. 7, состоит в том, что, если длина частичного блока будет определена как Ns, будет сгенерировано Nsузлов проверки, степени которых всегда равны 1 в фактор-графе блочного кода LDPC. Узлы проверки со степенью 1 не могут повлиять на улучшение рабочих характеристик на основе итеративного декодировании. Поэтому стандартный нерегулярный код LDPC, основанный на методике авторов Richardson-Urbanke, не включает в себя узел проверки со степенью 1. Поэтому предполагается, что матрица проверки на четность по фиг. 7 представляет собой основную матрицу проверки на четность для разработки матрицы проверки на четность так, что она обеспечивает возможность эффективного кодирования, когда она не включает в себя узел проверки со степенью 1. Если матрица проверки на четность по фиг. 7 содержит частичные матрицы, выбор частичной матрицы является очень важным фактором для улучшения рабочих характеристик блочного кода LDPC, так что поиск соответствующего критерия выбора для частичной матрицы также становится очень важным фактором.

Далее будет приведено описание способа разработки матрицы проверки на четность блочного кода LDPC, на основе приведенного выше блочного кода LDPC.

Для упрощения способа разработки матрицы проверки на четность блочного кода LDPC и способа кодирования блочного кода LDPC, предполагается, что матрица проверки на четность, показанная на фиг. 7, будет сформирована с 6 частичными матрицами, как показано на фиг. 8.

На фиг. 8 показана схема, иллюстрирующая матрицу проверки на четность по фиг. 7, которая разделена на 6 частичных блоков. Как показано на фиг. 8, матрица проверки на четность блочного кода LDPC, представленная на фиг. 7, разделена на информационную часть "s", первую часть p1 проверки на четность и вторую часть p2 проверки на четность. Информационная часть "s" представляет собой часть матрицы проверки на четность, отображенную на действительное информационное слово в процессе кодирования блочного кода LDPC, так же, как информационная часть, описанная со ссылкой на фиг. 7, но для удобства пояснения информационная часть "s" представлена другими буквами, обозначающими ссылочные позиции. Первая часть p1 проверки на четность и вторая часть p2 проверки на четность представляют собой часть матрицы проверки на четность, отображаемую на действительную четность во время процесса кодирования блочного кода LDPC, так же, как и часть проверки на четность, описанная со ссылкой на фиг. 7, и часть проверки на четность разделена на две части.

Частичные матрицы A и C соответствуют частичным блокам А (802) и C (804) информационной части "s", частичные матрицы B и D соответствуют частичным блокам B (806) и D (808) первой части p1 проверки на четность, и частичные матрицы T и E соответствуют частичным блокам T (810) и E (812) второй части p2 проверки на четность. Хотя матрица проверки на четность на фиг. 8 разделена на 7 частичных блоков, следует отметить, что "0" не является отдельным частичным блоком, и, поскольку частичная матрица T, соответствующая частичному блоку T (810), имеет полную нижнюю треугольную форму, область, где нулевые матрицы расположены в основании диагонали, представлена "0". Процесс упрощения способа кодирования с использованием частичных матриц информационной части "s" первой части p1проверки на четность и второй части p2 проверки на четность будет описан ниже со ссылкой на фиг. 10.

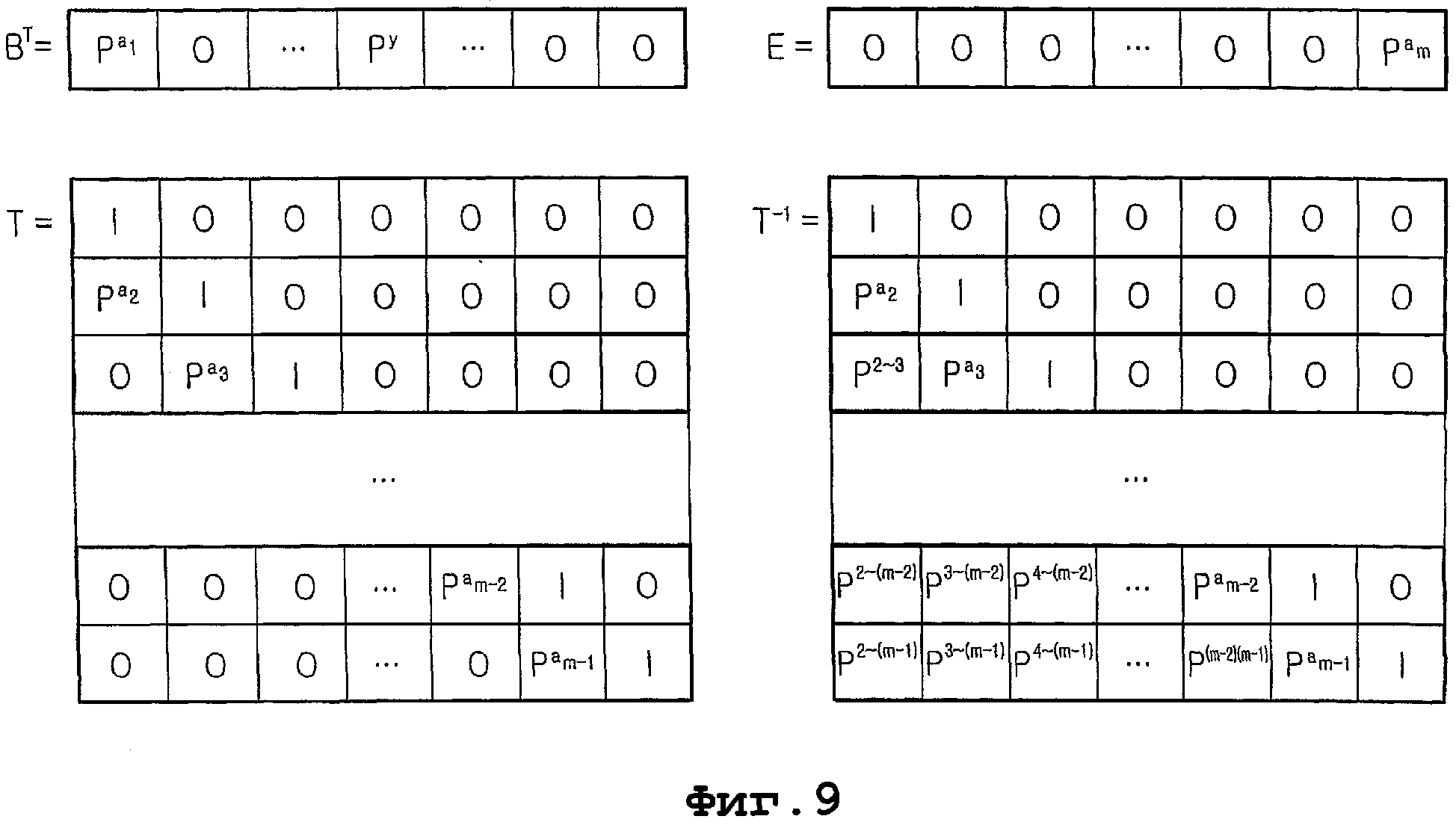

Частичные матрицы по фиг. 8 будут описаны ниже со ссылкой на фиг. 9.

На фиг. 9 показана схема, иллюстрирующая транспонированную матрицу частичной матрицы B, показанной на фиг. 8, частичной матрицы E, частичной матрицы T и обратной матрицы частичной матрицы T, в матрице проверки на четность по фиг. 7.

Как показано на фиг. 9, частичная матрица BT представляет собой транспонированную матрицу частичной матрицы B, и частичная матрица T-1 представляет собой обратную матрицу частичной матрицы T.

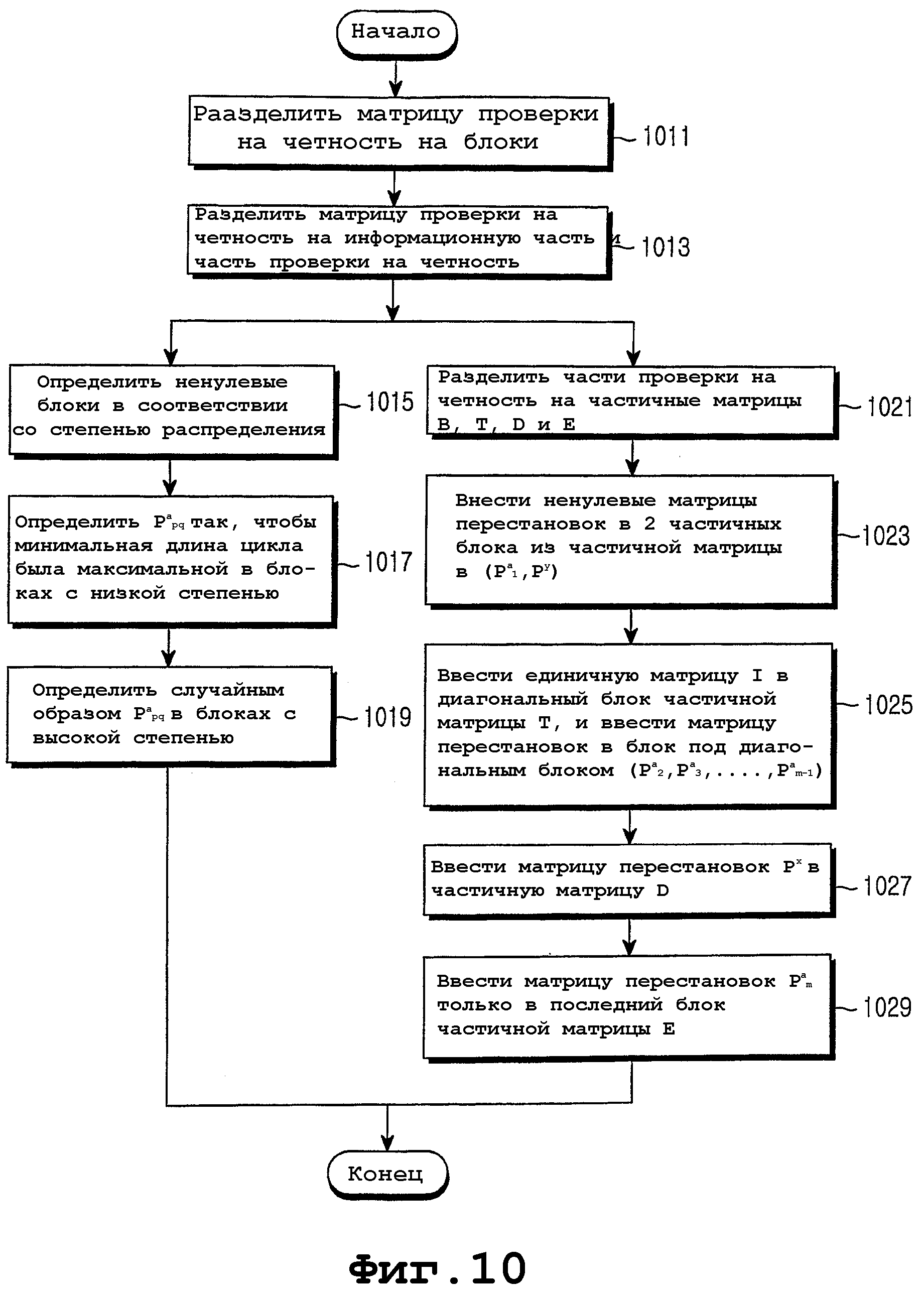

Ниже, со ссылкой на фиг. 10, приведено описание процесса разработки матрицы проверки на четность блочного кода LDPC.

На фиг. 10 показана блок-схема последовательности выполнения, иллюстрирующая процедуру генерирования матрицы проверки на четность общего блочного кода LDPC. Перед описанием фиг. 10 следует отметить, что для генерирования блочного кода LDPC необходимо определить размер ключевого слова и значения скорости кодирования блочного кода LDPC, который должен быть сгенерирован, а также размер матрицы проверки на четность должен быть определен в соответствии с определенным размером ключевого слова и значением скорости кодирования. Если размер ключевого слова блочного кода LDPC представлен как N и скорость кодирования представлена как R, размер матрицы проверки на четность становится равным N(1-R)×N. В действительности, процедура для генерирования матрицы проверки на четность блочного кода LDPC, представленная на фиг. 10, выполняется только один раз, поскольку матрица проверки на четность генерируется первоначально так, чтобы она соответствовала ситуации в системе передачи данных, и после этого используют сгенерированную матрицу проверки на четность.

На фиг. 10, на этапе 1011, контроллер разделяет матрицу проверки на четность с размером N(1-R) x N в общей сложности на pxq блоков, включающих p блоков по горизонтальной оси и q блоков по вертикальной оси, и затем переходит на этап 1013. Поскольку каждый из блоков имеет размер Ns×Ns, матрица проверки на четность состоит из Ns×p столбцов и Ns×q строк. На этапе 1013 контроллер классифицирует p×q блоков, выделенных из матрицы проверки на четность, на информационную часть "s", первую часть p1проверки на четность и вторую часть p2 проверки на четность, и затем переходит на этапы 1015 и 1021.

На этапе 1015 контроллер разделяет информационную часть "s" на ненулевые блоки, или ненулевые матрицы, и нулевые блоки, или нулевые матрицы в соответствии со степенью распределения, с тем, чтобы гарантировать хорошие рабочие характеристики блочного кода LDPC, и затем переходит на этап 1017. Поскольку степень распределения для гарантированно хороших рабочих характеристик блочного кода LDPC была описана выше, подробное ее описание здесь не приведено. На этапе 1017 контроллер определяет матрицы

На этапе 1019 контроллер случайным образом определяет матрицы

На этапе 1021 контроллер разделяет первую часть p1и вторую часть p2проверки на четность на 4 частичных матрицы B, T, D и E и затем переходит на этап 1023. На этапе 1023 контроллер вводит ненулевые матрицы

На этапе 1025 контроллер вводит единичные матрицы I в диагональные частичные блоки частичной матрицы T, вводит конкретные матрицы перестановок

На этапе 1027 контроллер вводит частичную матрицу Px в частичную матрицу D и затем переходит на этап 1029. На этапе 1029 контроллер вводит матрицы

Сущность изобретения

Как описано выше, известно, что код LDPC, так же как и турбокод, обладает высоким ростом рабочих характеристик во время высокоскоростной передачи данных и эффективно корректирует ошибку, вызываемую шумами, генерируемыми в канале передачи, способствуя повышению надежности передачи данных. Однако код LDPC имеет недостаток, связанный со скоростью кодирования, поскольку код LDPC имеет относительно высокую скорость кодирования, и имеет ограничения в смысле скорости кодирования. Среди доступных в настоящее время кодов LDPC, основные коды LDPC имеют скорость кодирования 1/2, и только незначительное количество кодов LDPC имеют скорость кодирования 1/3. Ограничение скорости кодирования оказывает фатальное влияние на передачу данных с высокой скоростью и высокой пропускной способностью. Конечно, хотя степень распределения, представляющая наилучшие рабочие характеристики, может быть рассчитана с использованием схемы эволюции плотности для выполнения относительно низкой скорости кодирования кода LDPC, трудно воплотить код LDPC, имеющий степень распределения, представляющую наилучшие рабочие характеристики, из-за различных ограничений, таких как структура цикла в фактор-графе, и при воплощении в аппаратных средствах.

Таким образом, задача настоящего изобретения состоит в создании устройства и способа кодирования/декодирования кода LDPC, имеющего переменную длину блока в системе мобильной связи.

Другая задача настоящего изобретения состоит в создании устройства и способа кодирования/декодирования кода LDPC, имеющего переменную длину блока, степень кодирования которого была бы минимизирована в мобильной системе связи.

В соответствии с одним аспектом настоящего изобретения предложен способ кодирования блочного кода проверки на четность с низкой плотностью (LDPC), имеющего переменную длину. Способ включает в себя этапы, на которых принимают информационное слово; и кодируют это информационное слово в блочный код LDPC на основе одной матрицы из первой матрицы проверки на четность и второй матрицы проверки на четность в зависимости от длины, которая должна использоваться при генерировании информационного слова в блочный код LDPC.

В соответствии с другим аспектом настоящего изобретения предложено устройство для кодирования блочного кода проверки на четность с низкой плотностью (LDPC), имеющего переменную длину. Это устройство включает в себя кодер для кодирования информационного слова в блочный код LDPC на основе одной из первой матрицы проверки на четность и второй матрицы проверки на четность в зависимости от длины, которая должна использоваться при генерировании информационного слова в блочный код LDPC; и модулятор для модуляции блочного кода LDPC в символ модуляции с использованием заданной схемы модуляции.

В соответствии с другим дополнительным аспектом настоящего изобретения предложен способ декодирования блочного кода проверки на четность с низкой плотностью (LDPC), имеющего переменную длину. Способ включает в себя этапы, на которых принимают сигнал и выбирают одну матрицу из первой матрицы проверки на четность и второй матрицы проверки на четность в соответствии с длиной блочного кода LDPC, предназначенного для декодирования, и декодируют принятый сигнал в соответствии с выбранной матрицей проверки на четность, детектируя, таким образом, блочный код LDPC.

В соответствии с еще одним аспектом настоящего изобретения предложено устройство для декодирования блочного кода проверки на четность с низкой плотностью (LDPC), имеющего переменную длину. Устройство включает в себя приемник для приема сигнала; и декодер для выбора одной матрицы из первой матрицы проверки на четность и второй матрицы проверки на четность в соответствии с длиной блочного кода LDPC, предназначенного для декодирования, и декодирования принятого сигнала в соответствии с выбранной матрицей проверки на четность с детектированием, таким образом, блочного кода LDPC.

Краткое описание чертежей

Указанные выше и другие задачи, признаки и преимущества настоящего изобретения будут более понятны из следующего подробного описания, которое следует рассматривать совместно с прилагаемыми чертежами, на которых:

на фиг. 1 представлена схема, иллюстрирующая структуру передатчика/приемника в обычной системе мобильной связи;

на фиг. 2 показана схема, иллюстрирующая матрицу проверки на четность общего кода LDPC (8, 2, 4);

на фиг. 3 показана схема, иллюстрирующая фактор-граф кода LDPC (8, 2, 4) по фиг. 2;

на фиг. 4 показана схема, иллюстрирующая матрицу проверки на четность обычного блочного кода LDPC;

на фиг. 5 показана схема, иллюстрирующая матрицу P перестановок по фиг. 4;

на фиг. 6 показана схема, иллюстрирующая структуру цикла блочного кода LDPC, в котором матрица проверки на четность состоит из 4 частичных матриц;

на фиг. 7 показана схема, иллюстрирующая матрицу проверки на четность, имеющую форму, аналогичную форме полной нижней треугольной матрицы;

на фиг. 8 показана схема, иллюстрирующая матрицу проверки на четность по фиг. 7, которая разделена на 6 частичных блоков;

на фиг. 9 показана схема, иллюстрирующая транспонированную матрицу частичной матрицы B, показанной на фиг. 8, частичной матрицы E, частичной матрицы T и обратную матрицу частичной матрицы T;

на фиг. 10 показана блок-схема последовательности операций, иллюстрирующая процедуру генерирования матрицы проверки на четность обычного блочного кода LDPC;

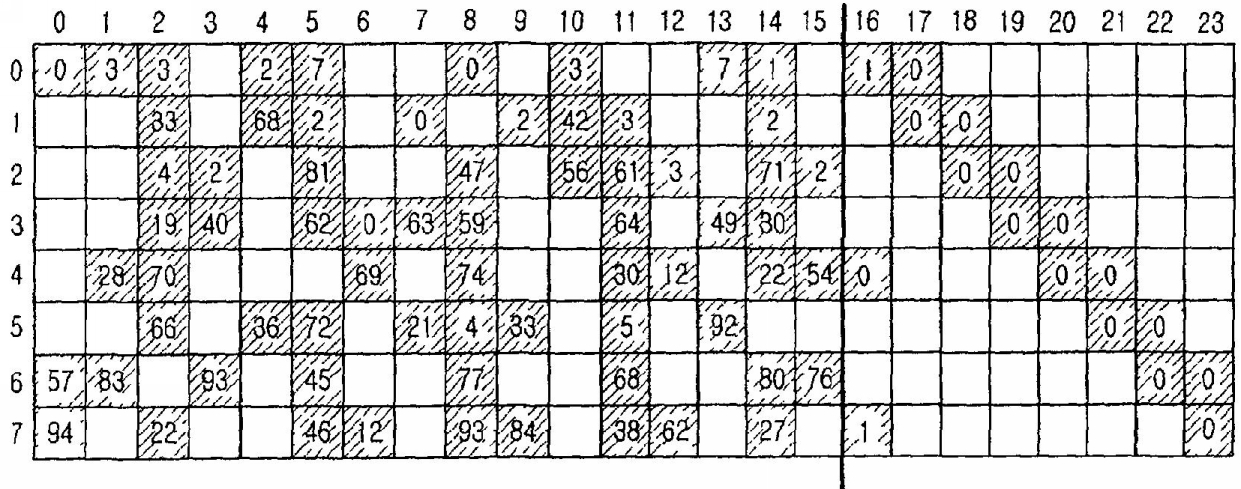

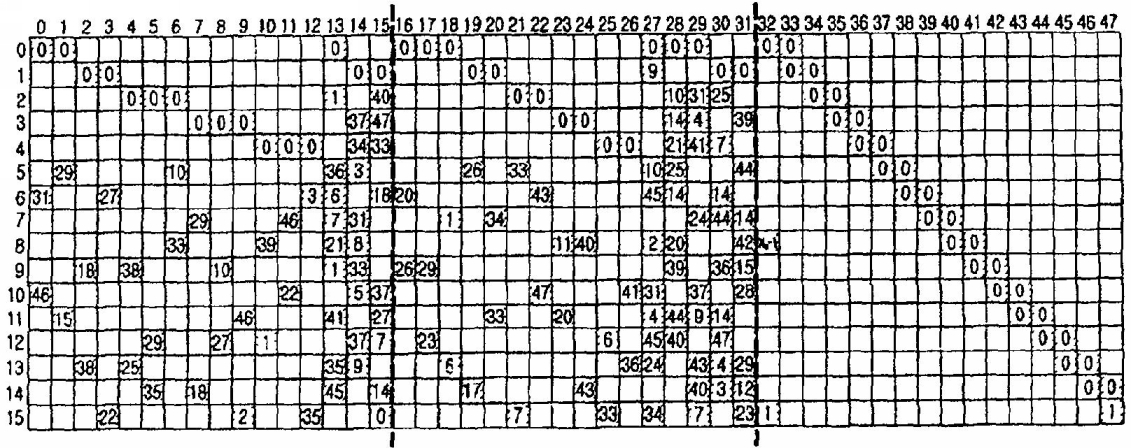

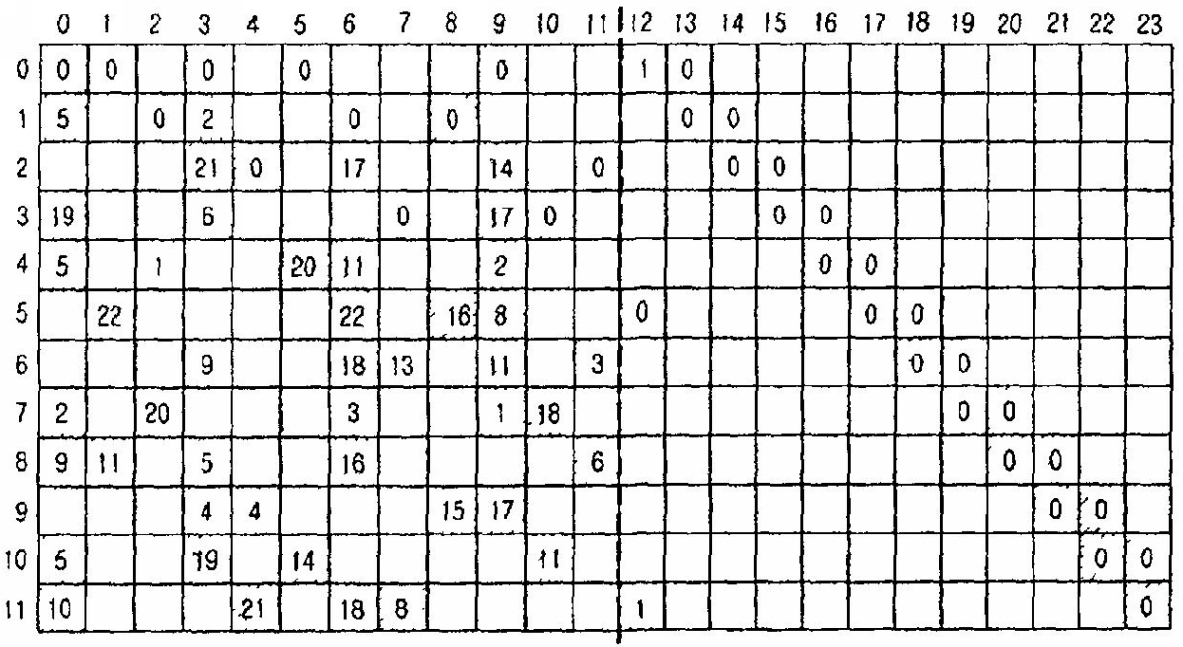

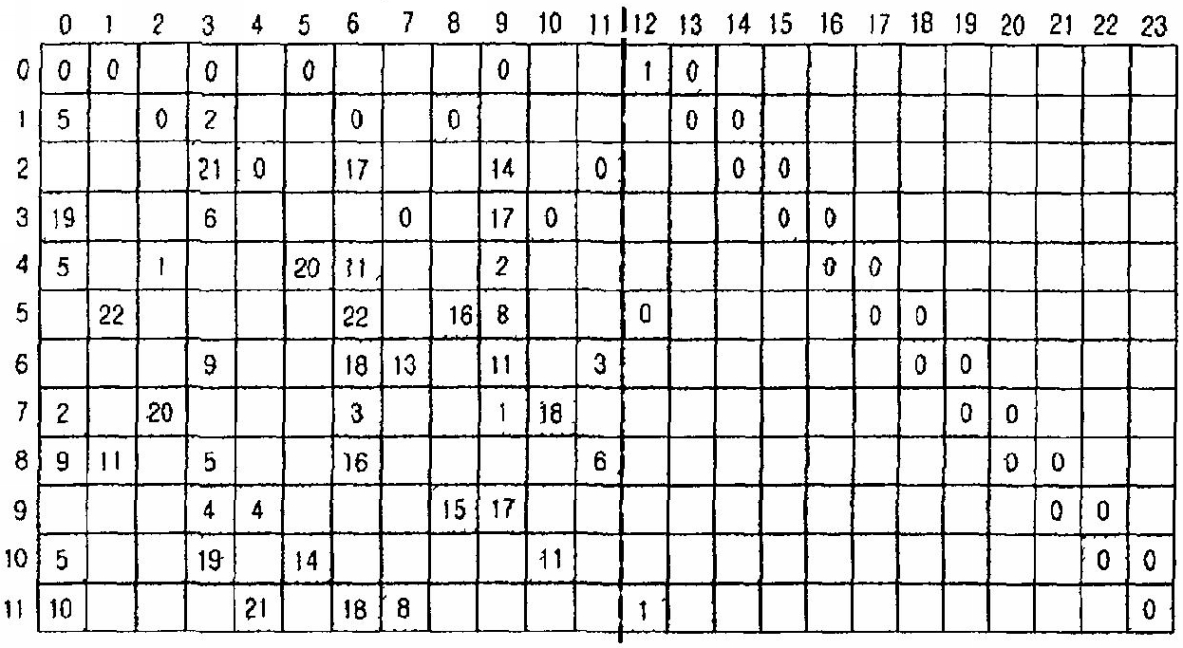

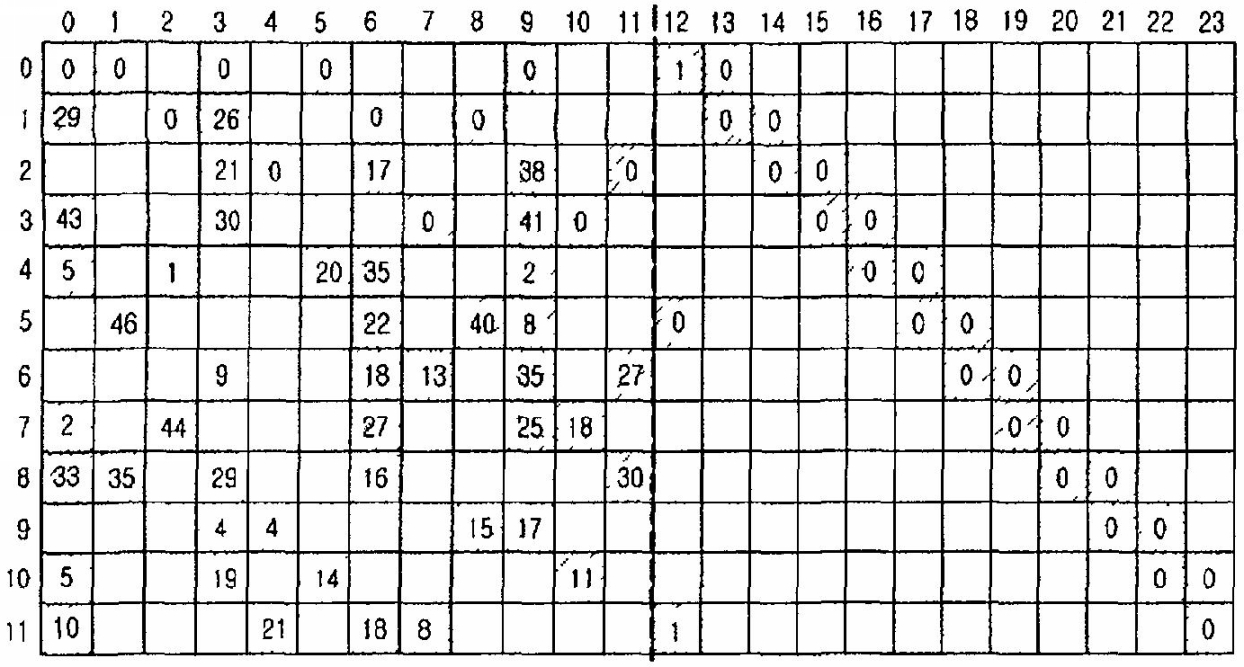

на фиг. 11 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока в соответствии с первым вариантом выполнения настоящего изобретения;

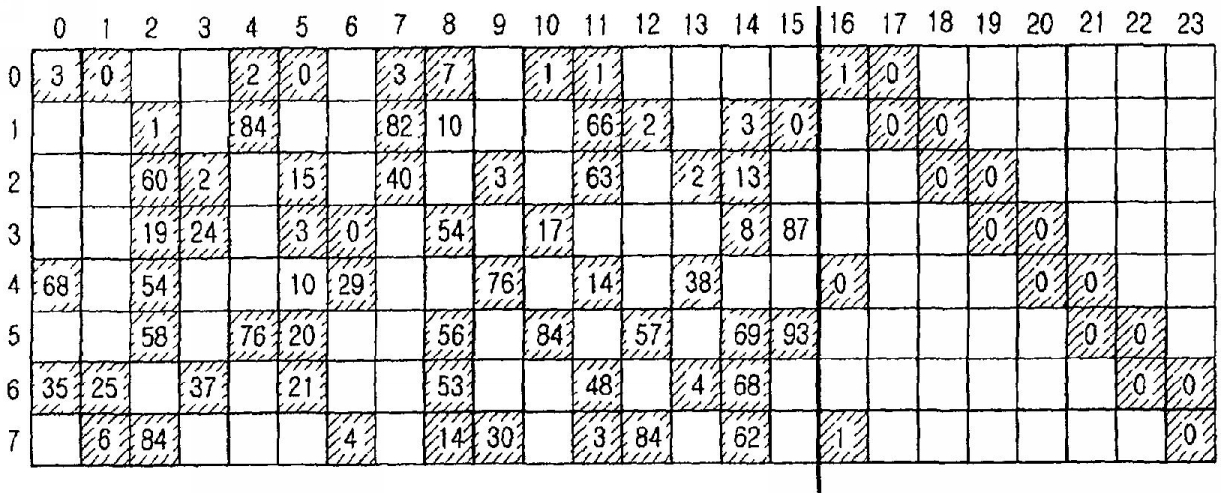

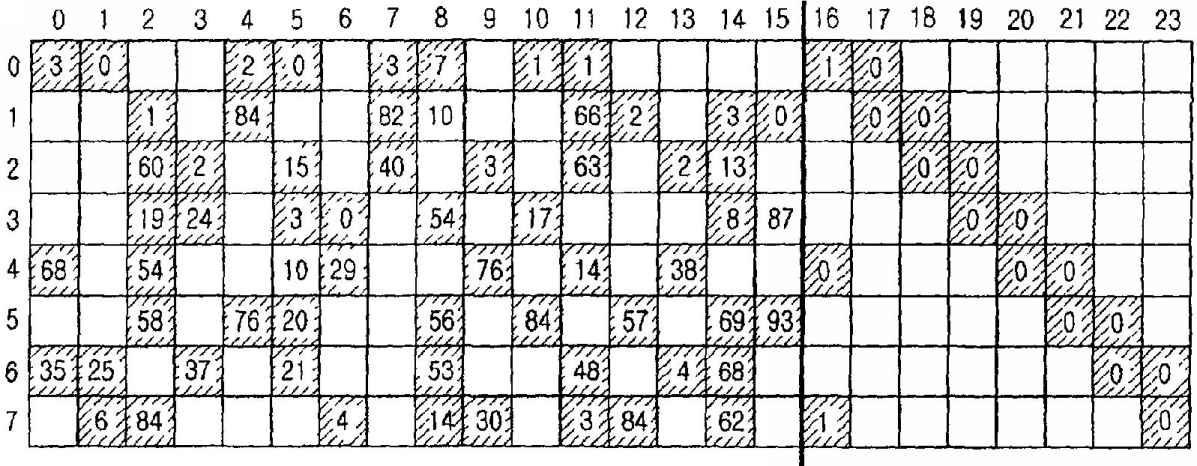

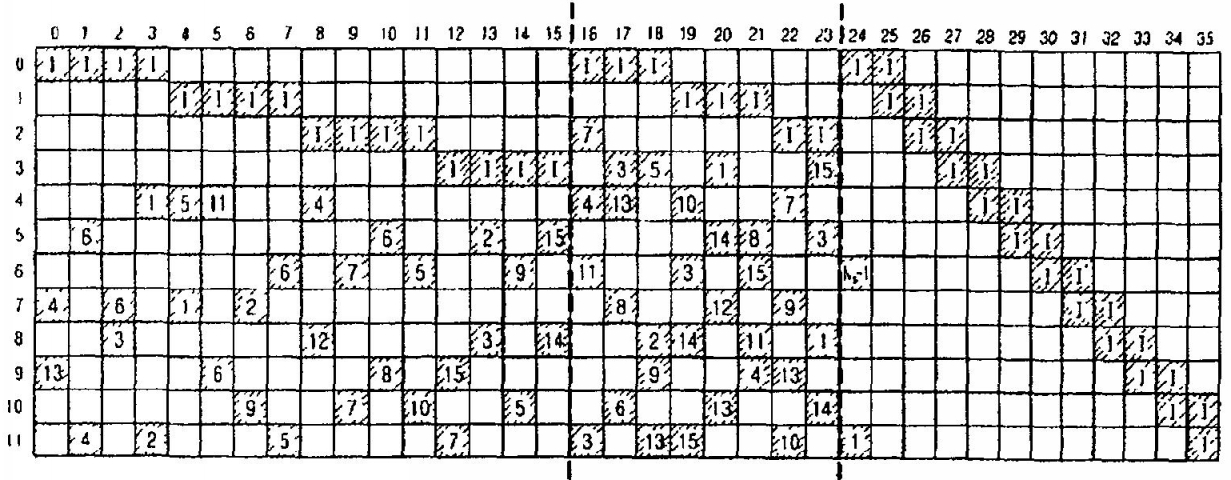

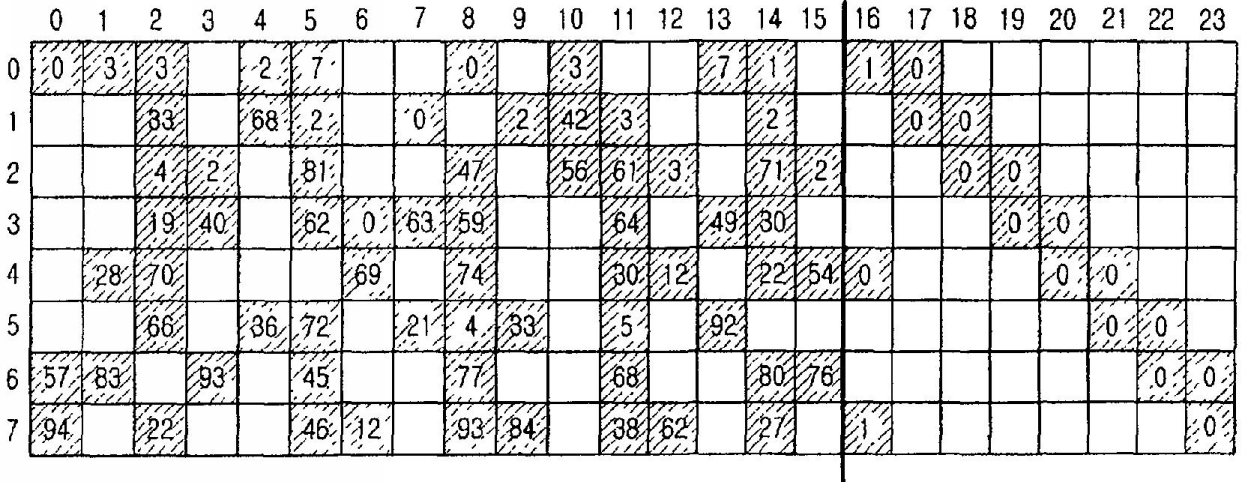

на фиг. 12 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока в соответствии со вторым вариантом выполнения настоящего изобретения;

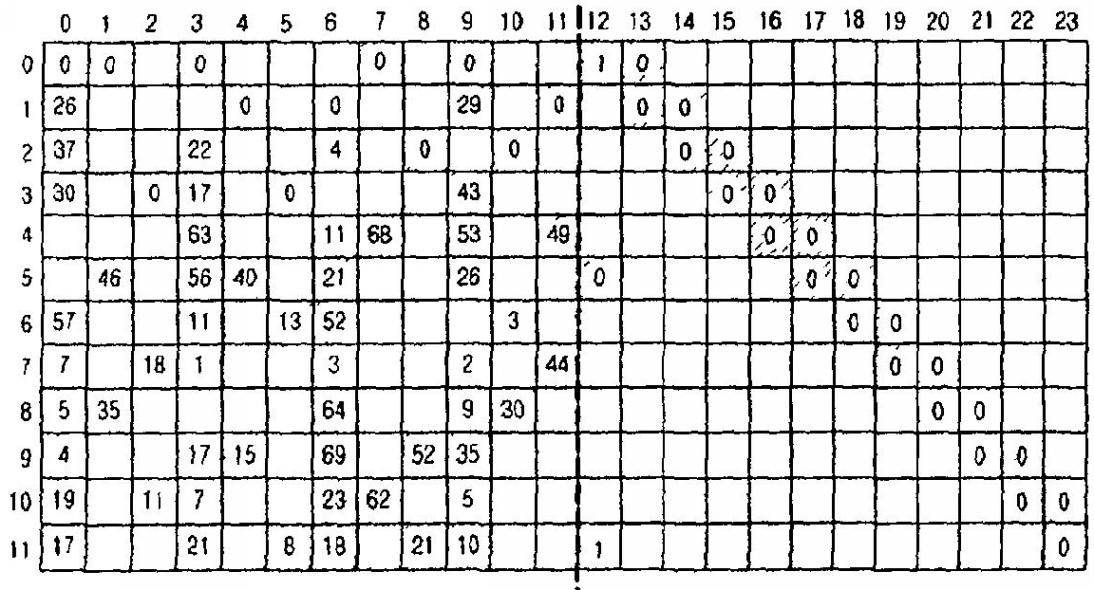

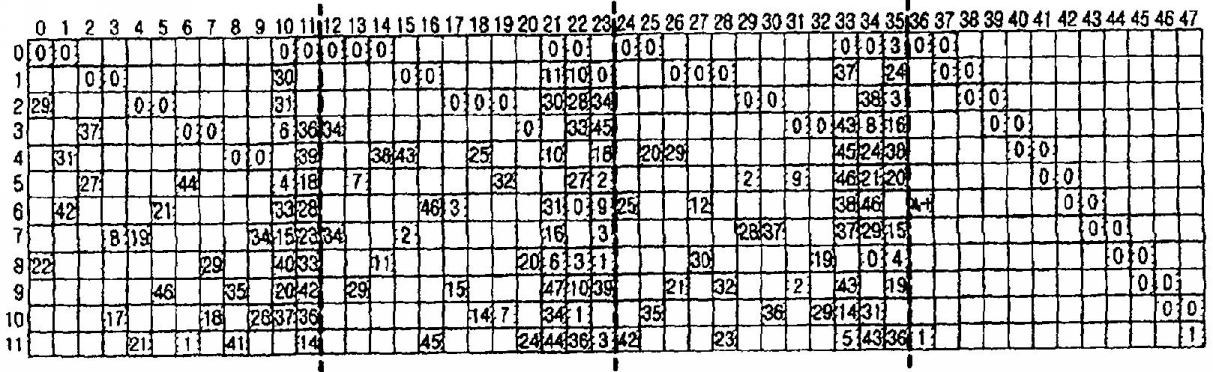

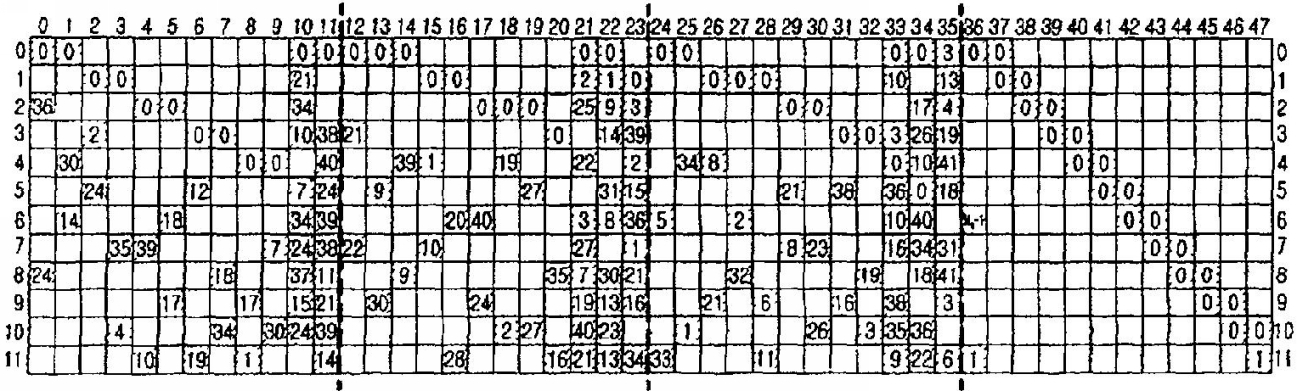

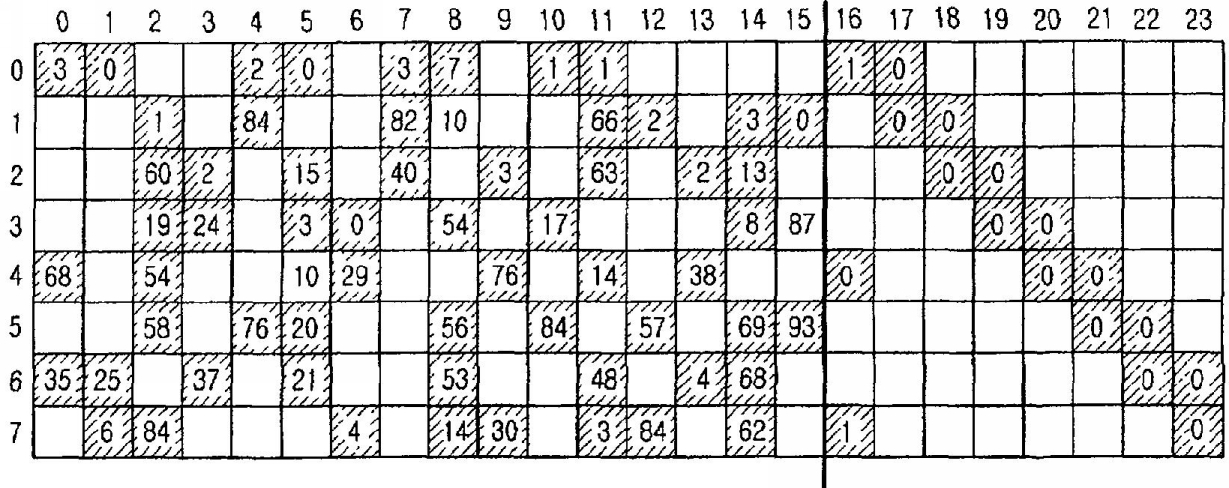

на фиг. 13 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока в соответствии с третьим вариантом выполнения настоящего изобретения;

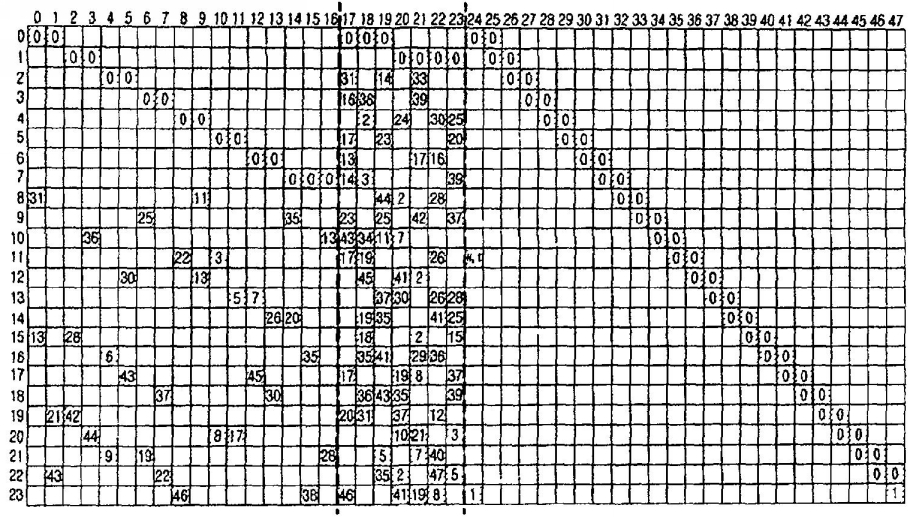

на фиг. 14 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока в соответствии с четвертым вариантом выполнения настоящего изобретения;

на фиг. 15 показана блок-схема последовательности операций, иллюстрирующая процесс кодирования блочного кода LDPC с переменной длиной блока в соответствии с первым-четвертым вариантами выполнения настоящего изобретения;

на фиг. 16 показана блок-схема, иллюстрирующая внутреннюю структуру устройства, предназначенного для кодирования блочного кода LDPC с переменной длиной блока в соответствии с вариантами выполнения настоящего изобретения;

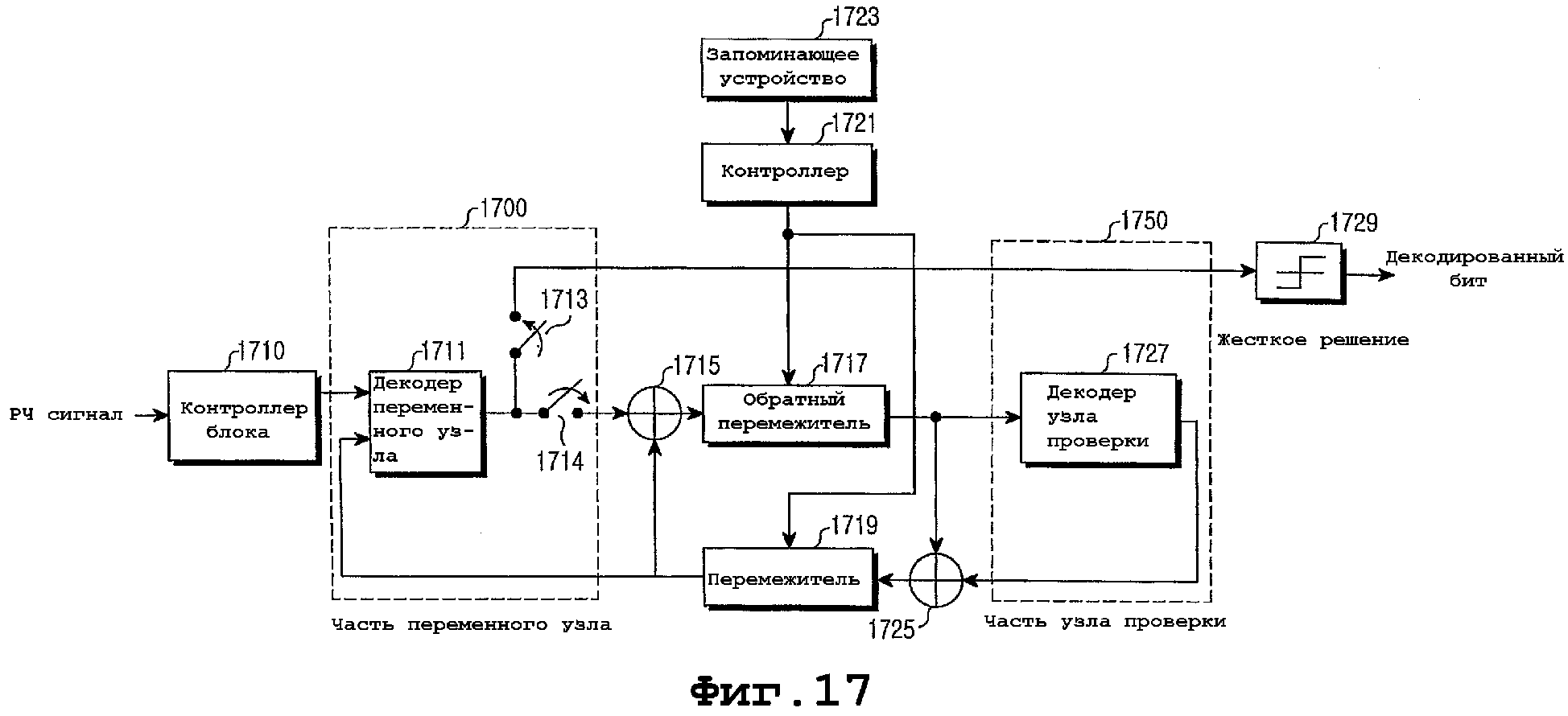

на фиг. 17 показана блок-схема, иллюстрирующая внутреннюю структуру устройства, предназначенного для декодирования блочного кода LDPC, в соответствии с вариантами выполнения настоящего изобретения;

на фиг. 18 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока в соответствии с пятым вариантом выполнения настоящего изобретения;

на фиг. 19 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока в соответствии с шестым вариантом выполнения настоящего изобретения;

на фиг. 20 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока, в соответствии с седьмым вариантом выполнения настоящего изобретения;

на фиг. 21 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока, в соответствии с восьмым вариантом выполнения настоящего изобретения;

на фиг. 22 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока, в соответствии с девятым вариантом выполнения настоящего изобретения;

на фиг. 23 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока, в соответствии с десятым вариантом выполнения настоящего изобретения;

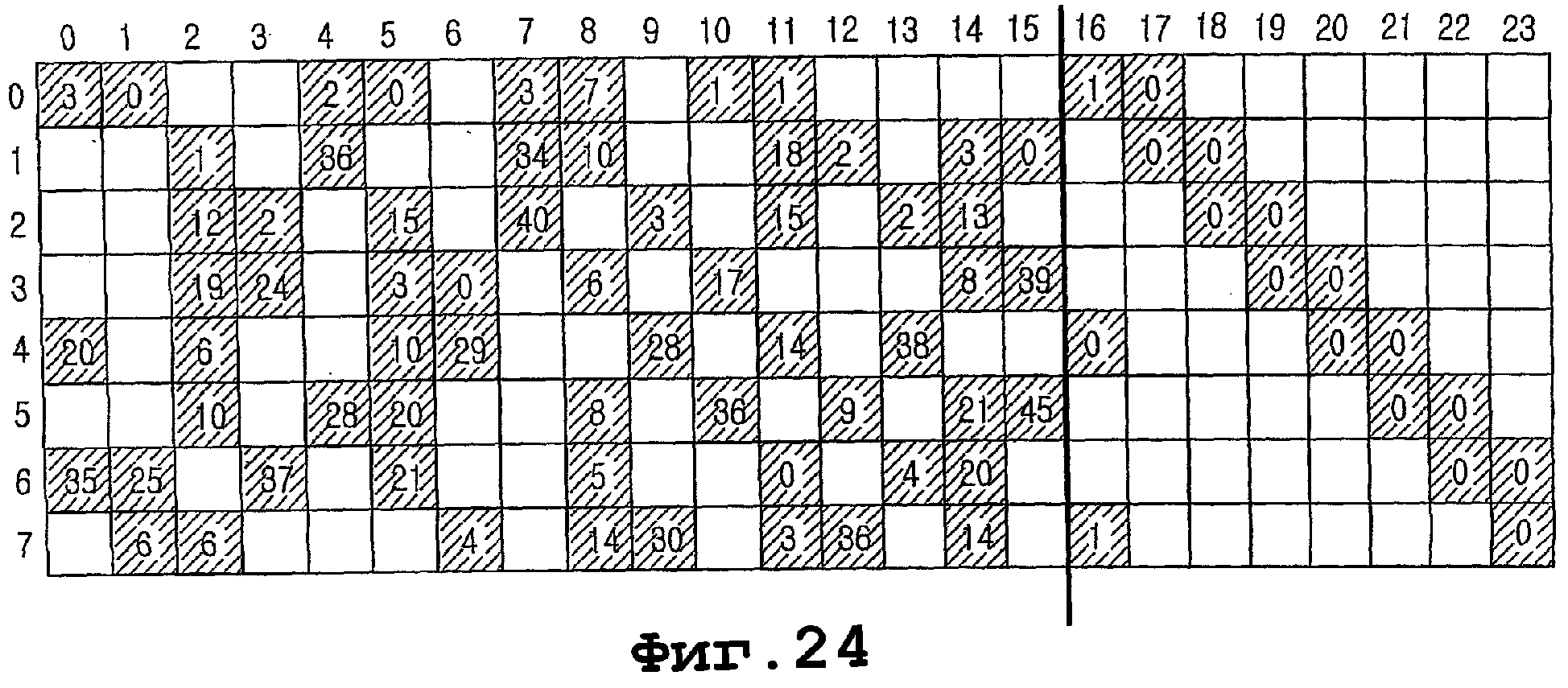

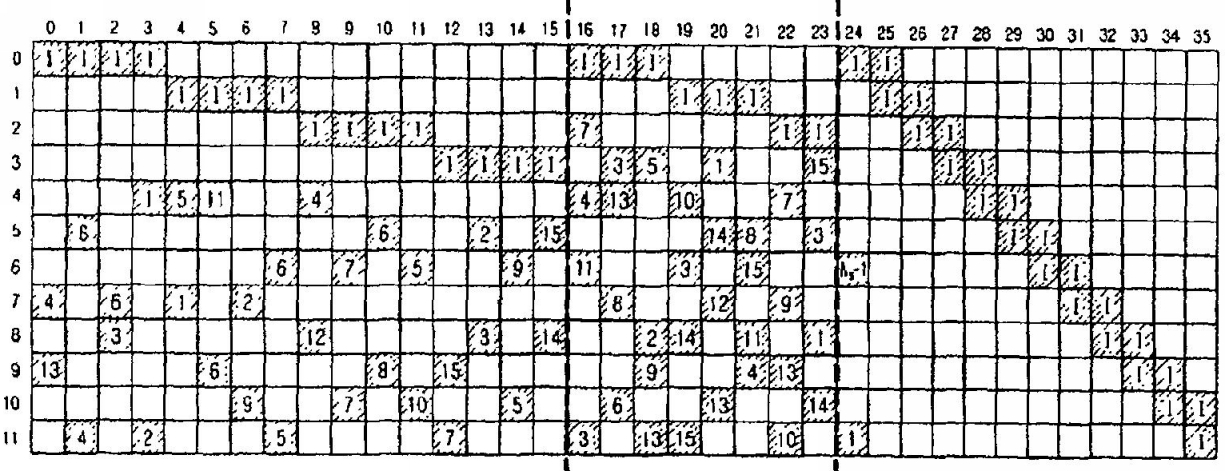

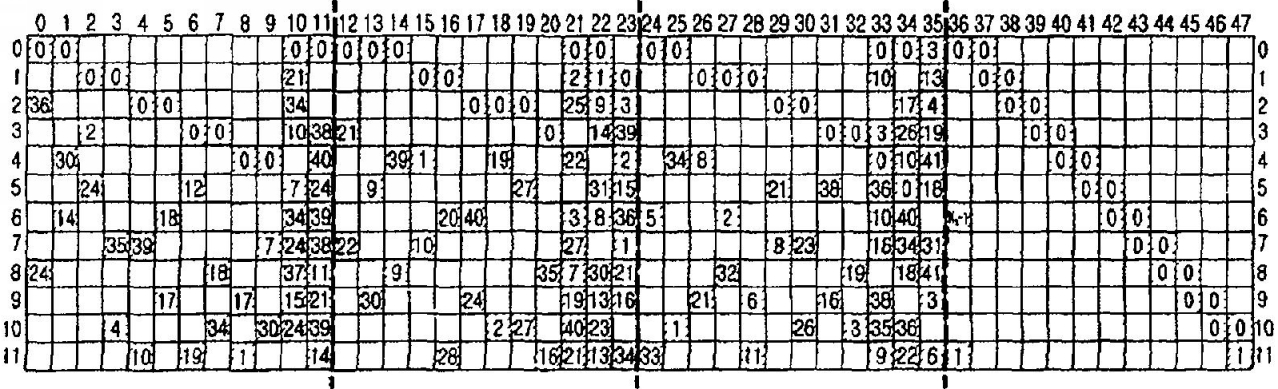

на фиг. 24 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока, в соответствии с одиннадцатым вариантом выполнения настоящего изобретения;

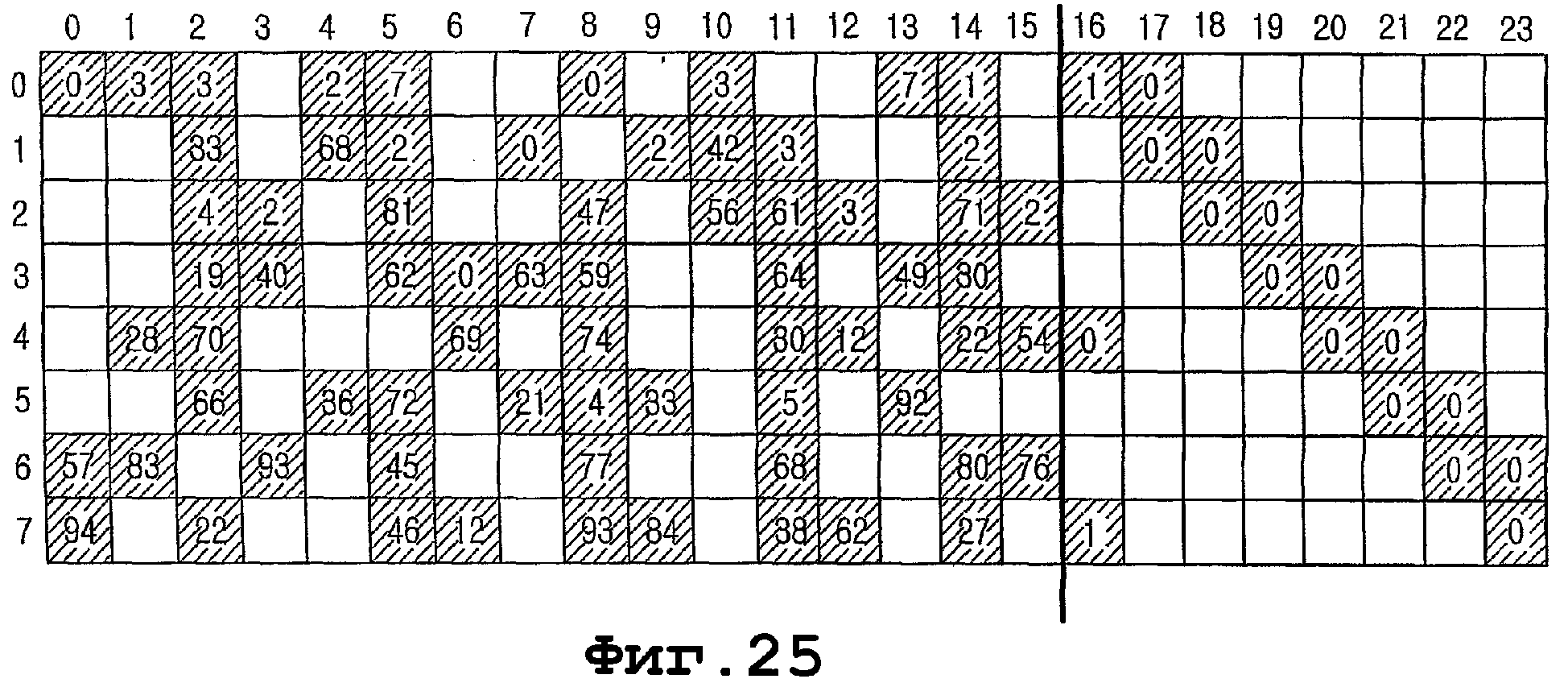

на фиг. 25 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока, в соответствии с двенадцатым вариантом выполнения настоящего изобретения;

на фиг. 26 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока, в соответствии с тринадцатым вариантом выполнения настоящего изобретения;

на фиг. 27 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока, в соответствии с четырнадцатым вариантом выполнения настоящего изобретения; и

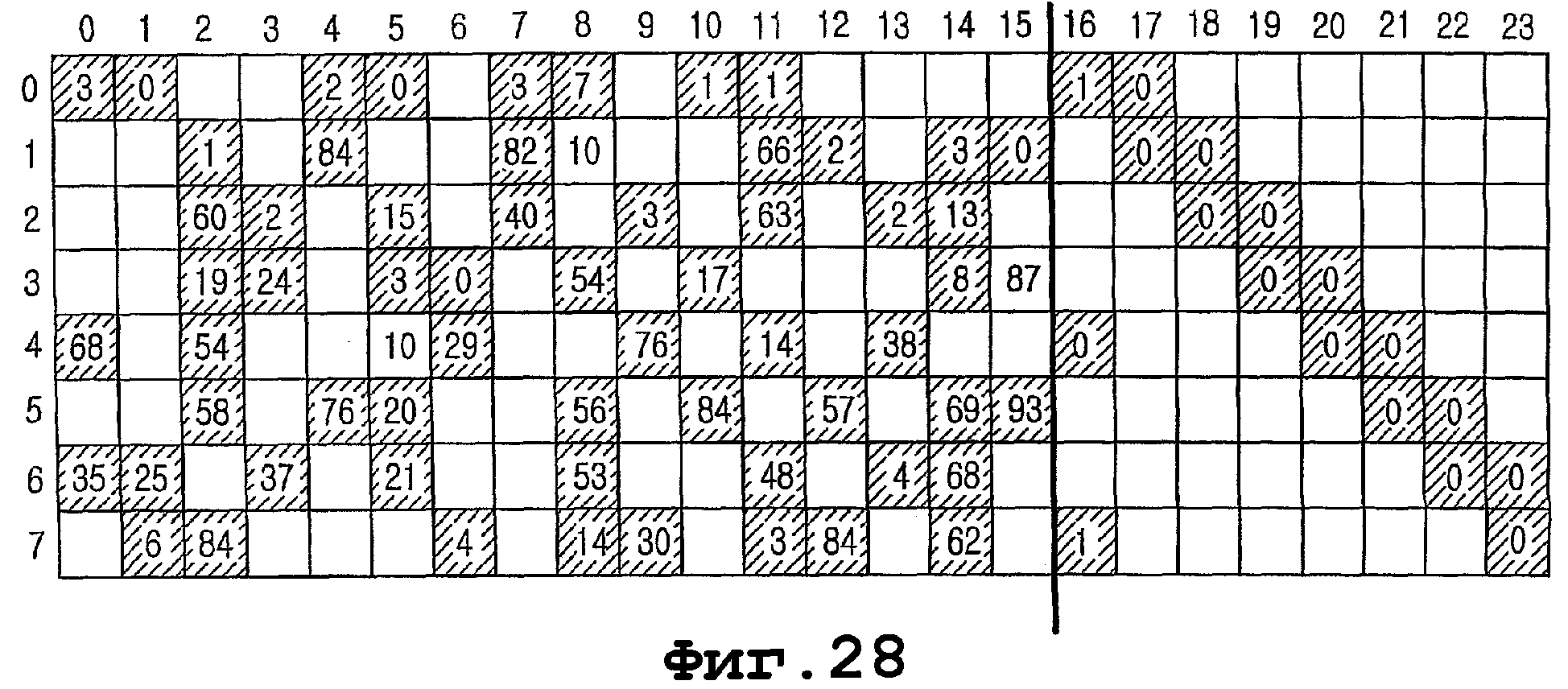

на фиг. 28 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока, в соответствии с пятнадцатым вариантом выполнения настоящего изобретения.

Подробное описание предпочтительного варианта осуществления

Несколько предпочтительных вариантов осуществления настоящего изобретения будут подробно описаны ниже со ссылкой на прилагаемые чертежи. В следующем описании подробное пояснение приведенных здесь известных функций и конфигураций не представлено для краткости изложения.

В настоящем изобретении предложены устройство и способ, предназначенные для кодирования и декодирования блочного кода проверки на четность с низкой плотностью (LDPC), имеющего переменную длину блока (ниже называется "блочный код LDPC с переменной длиной блока"). Таким образом, в настоящем изобретении предложены устройство и способ, предназначенные для кодирования и декодирования блочного кода LDPC с переменной длиной блока, в котором максимизирована длина минимального цикла в фактор-графе блочного кода LDPC, степень кодирования блочного кода LDPC минимизирована, степень распределения фактор-графа блочного кода LDPC имеет оптимальную величину 1, и поддерживаются переменные длины блока. Хотя это отдельно не представлено в описании, устройство кодирования и декодирования блочного кода LDPC с переменной длиной блока в соответствии с настоящим изобретением можно применять для передатчика/приемника, описанного со ссылкой на фиг. 1.

Система мобильной связи следующего поколения получила развитие как система передачи данных пакетного обслуживания, и система передачи данных пакетного обслуживания, которая представляет собой систему, предназначенную для передачи пакетных данных в множество мобильных станций, была разработана так, чтобы она соответствовала возможности передачи данных с высокой пропускной способностью. Для увеличения пропускной способности передачи данных были предложены схема гибридного автоматического запроса на повторную передачу данных (HARQ, ГАЗП) и схема адаптивной модуляции и кодирования (AMC, АМК). Поскольку схема HARQ и схема AMC поддерживают переменную скорость кодирования, существует потребность в блочных кодах LDPC, имеющих разные длины блоков.

Конструкция блочного кода LDPC с переменной длиной блока, так же, как и конструкция обычного кода LDPC, выполнена с использованием конструкции матрицы с проверкой на четность. Однако в мобильной системе связи для обеспечения блочного кода LDPC с переменной длиной блока, с одним кодеком, то есть для обеспечения блочного кода LDPC, имеющего разные длины блока, матрица проверки на четность должна включать в себя матрицы проверки на четность, позволяющие представлять блочные коды LDPC, имеющие разные длины блока. Ниже приведено описание матрицы проверки на четность блочного кода LDPC, обеспечивающего переменную длину блока.

Вначале блочный код LDPC, имеющий минимальную длину блока, требуемую в системе, разрабатывают для требуемой скорости кодирования. В матрице проверки на четность, если увеличивать Ns, обозначающий размер ее частичной матрицы, получают блочный код LDPC, имеющий большую длину блока. "Частичная матрица", как описано выше, относится к матрице перестановок, соответствующей каждому из частичных блоков, полученных путем разделения матрицы проверки на четность на множество частичных блоков. Если предположить, что блочный код LDPC расширен таким образом, что вначале будет разработан блочный код LDPC с короткой длиной блока, и затем будет разработан блочный код LDPC с большой длиной блока, ввиду увеличения размера Ns,частичная матрица приводит к модификации структуры цикла, при этом экспоненты матриц перестановок для матриц проверки на четность выбирают таким образом, чтобы длина цикла была максимизирована. Здесь размер частичной матрицы, составляющей Ns, означает, что частичная матрица представляет собой квадратную матрицу, имеющую размер Ns×Ns, и для удобства описания, размер частичной матрицы представлен как Ns.

Например, если предположить, что размер частичного блока основного блочного кода LDPC составляет Ns=2, когда требуется расширить базовый блочный код LDPC с Ns=2 до блочного кода LDPC с Ns=4 в 2 раза большей длины, чем основной блочный код LDPC, частичная матрица, экспонента которой равна 0, в матрице перестановок, может выбирать значение 0 или 2, если ее длина увеличивается от Ns=2 до Ns=4. Среди этих двух значений следует выбрать значение, позволяющее максимизировать цикл. Аналогично, в блочном коде LDPC с Ns=2 частичная матрица с экспонентой 1 может выбирать значение 1 или 3, если ее длина увеличивается от Ns=2 до Ns=4.

Как описано выше, возможно разработать блочный код LDPC, имеющий максимальные рабочие характеристики для каждой длины блока, путем разработки блочного кода LDPC с использованием основного блочного кода LDPC, при увеличении величины Ns. Кроме того, один случайный блочный код LDPC среди блочных кодов LDPC, имеющих различные длины блока, может быть определен как основной блочный код LDPC, способствующий увеличению эффективности использования запоминающего устройства. Далее будет приведено описание способа генерирования матрицы проверки на четность блочного кода LDPC с переменной длиной блока. В настоящем изобретении предложено 4 типа матриц проверки на четность для блочного кода LDPC с переменной длиной блока, в соответствии со скоростью кодирования, и значения скорости кодирования, рассматриваемые в настоящем изобретении, включают в себя 1/2, 2/3, 3/4 и 5/6.

Перед описанием матриц проверки на четность блочного кода LDPC с переменной длиной блока для скоростей кодирования 1/2, 2/3, 3/4, и 5/6, со ссылкой на фиг. 15 будет описан процесс кодирования блочного кода LDPC с переменной длиной блока, с использованием матрицы проверки на четность, разработанной в настоящем изобретении. 15.

На фиг. 15 показана блок-схема последовательности операций, иллюстрирующая процесс кодирования блочного кода LDPC с переменной длиной блока, в соответствии с первым-четвертым вариантами выполнения настоящего изобретения. Перед описанием фиг. 15, предполагается, что матрица проверки на четность для блочного кода LDPC с переменной длиной блока состоит из 6 частичных матриц, как описано со ссылкой на фиг. 8.

Как показано на фиг. 15, на этапе 1511, контроллер (не показан) принимает вектор "s" информационного слова, предназначенный для кодирования в блочный код LDPC с переменной длиной блока, и затем переходит на этапы 1513 и 1515. Здесь предполагается, что длина вектора "s" информационного слова, принимаемого для кодирования, в блочный код LDPC, равна k. На этапе 1513 контроллер выполняет матричное перемножение принятого вектора "s" информационного слова на частичную матрицу А матрицы (As) проверки на четность, и затем переходит на этап 1517. Здесь, поскольку количество элементов, имеющих значение 1, расположенных в частичной матрице A, намного меньше, чем количество элементов, имеющих значение 0, матричное умножение (As) вектора s информационного слова и частичной матрицы А матрицы проверки на четность может быть получено с относительно малым количеством операций суммирования-перемножения. Кроме того, в частичной матрице A, поскольку положения, где расположены элементы, имеющие значение 1, можно выразить как экспоненциальное умножение положения ненулевого блока и матрицы перестановок блока, перемножение матриц можно выполнить, используя очень простую операцию по сравнению со случайной матрицей проверки на четность. На этапе 1515 контроллер выполняет перемножение матриц (Cs) для частичной матрицы C в матрице проверки на четность и вектора "s" информационного слова и затем переходит на этап 1519.

На этапе 1517 контроллер выполняет перемножение матриц (ET-1As) на результат перемножения матриц (As) вектора "s" информационного слова и частичной матрицы А из матрицы проверки на четность, и матрицы ET-1, и затем переходит на этап 1519. Здесь, поскольку количество элементов, имеющих значение 1 в матрице ET-1, очень мало, как описано выше, если будет задана экспонента матрицы перестановок блока, умножение матриц может быть выполнено просто. На этапе 1519 контроллер рассчитывает первый вектор P1 проверки на четность путем суммирования ET-1As и Cs (P1 = ET-1As + Cs), и затем переходит на этап 1521. Здесь операция суммирования представляет собой операцию исключающее ИЛИ (XOR), и ее результат становится равным 0 для операций между битами, имеющими одинаковое значение, и 1 для операций между битами, имеющими разные значения. То есть процесс, вплоть до этапа 1519, представляет собой процесс расчета первого вектора P1 проверки на четность.

На этапе 1521 контроллер перемножает частичную матрицу B для матрицы проверки на четность на первый вектор P1проверки на четность (BP1), суммирует результат умножения (BP1) с As (As + BP1), и затем переходит на этап 1523. Если заданы вектор "s" информационного слова и первый вектор P1 проверки на четность, их следует умножить на обратную матрицу T-1 частичной матрицы T матрицы проверки на четность, для расчета второго вектора P2проверки на четность. Поэтому на этапе 1523 контроллер перемножает результат расчетов (As + BP1) на этапе 1521 на обратную матрицу T-1 частичной матрицы T для расчета второго вектора P2проверки на четность (P2 =T-1 (As + BP1), и затем переходит на этап 1525. Как описано выше, если будет задан вектор "s" информационного слова блочного кода LDPC, предназначенного для кодирования, можно будет рассчитать первый вектор P1проверки на четность и второй вектор P2проверки на четность, и, в результате, могут быть получены все векторы кодового слова. На этапе 1525 контроллер генерирует вектор "c" кодового слова, используя вектор "s" информационного слова, первый вектор P1 проверки на четность и второй вектор P2 проверки на четность, и передает сгенерированный вектор "c" кодового слова.

Далее, со ссылкой на фиг. 16, описана внутренняя структура устройства, предназначенного для кодирования блочного кода LDPC с переменной длиной блока, в соответствии с вариантами выполнения настоящего изобретения.

На фиг. 16 показана блок-схема, иллюстрирующая внутреннюю структуру устройства, предназначенного для кодирования блочного кода LDPC с переменной длиной блока, в соответствии с вариантами выполнения настоящего изобретения. Как показано на фиг. 16, устройство для кодирования блочного кода LDPC с переменной длиной блока включает в себя умножитель 1611 матрицы-А, умножитель 1613 матрицы-C, умножитель 1615 матрицы ET-1, сумматор 1617, умножитель 1619 матрицы-B, сумматор 1621, умножитель 1623 матрицы T-1 и переключатели 1625, 1627 и 1629.

Если будет принят входной сигнал, то есть вектор "s" информационного слова длиной k, которое должен быть закодировано в блочный код LDPC с переменной длиной блока, принятый вектор "s" информационного слова длиной k подают на переключатель 1625, умножитель 1611 матрицы-A и умножитель 1613 матрицы C, умножитель 1611 матрицы-A умножает вектор "s" информационного слова на частичную матрицу А полной матрицы проверки на четность, и выводит результат умножения в умножитель 1615 матрицы ET-1 и в сумматор 1621. Умножитель 1613 матрицы-C умножает вектор "s" информационного слова на частичную матрицу C полной матрицы проверки на четность, и выводит результат умножения в сумматор 1617. Умножитель 1615 матрицы ET-1 умножает сигнал, поступающий с выхода умножителя 1611 матрицы-A на частичную матрицу ET-1 полной матрицы проверки на четность, и выводит результат умножения в сумматор 1617.

Сумматор 1617 суммирует сигнал, поступающий с выхода калькулятора 1615 матрицы ET-1, с сигналом, поступающим с выхода умножителя 1613 матрицы-C, и выводит результат суммирования в умножитель 1619 матрицы-B и в переключатель 1627. Здесь сумматор 1617 выполняет операцию "исключающее ИЛИ" на побитовой основе. Например, если вектор длиной 3, представляющий собой x = (x1, x2, x3) и вектор длиной 3, представляющий собой y = (y1,y2, y3), подают на сумматор 1617, сумматор 1617 выводит вектор длиной 3, представляющий собой z = (x1

Умножитель 1619 матрицы-B умножает сигнал, поступающий с выхода сумматора 1617, то есть первый вектор P1проверки на четность, на частичную матрицу B полной матрицы проверки на четность, и выводит результат умножения в сумматор 1621. Сумматор 1621 добавляет сигнал, поступающий с выхода умножителя 1619 матрицы-B, к сигналу, поступающему с выхода умножителя 1611 матрицы-A, и выводит результат суммирования в умножитель 1623 матрицы T-1. Сумматор 1621, так же, как и сумматор 1617, выполняет операцию "исключающее ИЛИ" для сигнала, поступающего с выхода умножителя 1619 матрицы-B, и сигнала, поступающего с выхода умножителя 1611 матрицы-A, и выводит результат операции "исключающее ИЛИ" в умножитель 1623 матрицы T-1.

Умножитель 1623 матрицы T-1 умножает сигнал, поступающий с выхода сумматора 1621, на обратную матрицу T-1 частичной матрицы T полной матрицы проверки на четность, и выводит результат умножения в переключатель 1629. Выход умножителя 1623 матрицы T-1 становится вторым вектором P2 проверки на четность. Каждый из переключателей 1625, 1627 и 1629 включают только во время его передачи, для передачи ассоциированного с ним сигнала. Переключатель 1625 включают во время передачи вектора "s" информационного слова, переключатель 1627 включают во время передачи первого вектора P1 проверки на четность, и переключатель 1629 включают во время передачи второго вектора P2проверки на четность.

Поскольку варианты выполнения настоящего изобретения должны обеспечить возможность генерирования блочного кода LDPC с переменной длиной блока, каждую из матриц, используемых в устройстве кодирования по фиг. 16 для блочного кода LDPC с переменной длиной блока, изменяют каждый раз, когда изменяется матрица проверки на четность блочного кода LDPC с переменной длиной блока, как будет описано со ссылкой на фиг. 17. Поэтому, хотя это отдельно не показано на фиг. 16, контроллер модифицирует матрицы, используемые в устройстве кодирования для блочного кода LDPC с переменной длиной блока, по мере того, как изменяется матрица проверки на четность блочного кода LDPC с переменной длиной блока.

Выше приведено описание способа генерирования блочного кода LDPC с переменной длиной блока с учетом эффективного кодирования. Как описано выше, блочный код LDPC с переменной длиной блока из-за своей структурной характеристики, является предпочтительным для обеспечения эффективности использования памяти, для сохранения информации, связанной с матрицей проверки на четность, и позволяет обеспечить эффективное кодирование путем соответствующего выбора частичных матриц из матрицы проверки на четность. Однако, по мере того, как поблочно генерируется матрица проверки на четность, снижается ее произвольность, и снижение произвольности может привести к ухудшению рабочих характеристик блочного кода LDPC. Таким образом, поскольку нерегулярный блочный код LDPC обладает лучшими рабочими характеристиками по сравнению с блочным кодом LDPC с регулярной структурой, как описано выше, в процессе разработки блочного кода LDPC очень важно правильно выбрать частичные матрицы из полной матрицы проверки на четность.

Ниже, со ссылкой на фиг. 11, приведено описание подробного способа генерирования блочного кода LDPC с переменной длиной блока для скорости кодирования 1/2.

На фиг. 11 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока, в соответствии с первым вариантом выполнения настоящего изобретения. Перед описанием фиг. 11 следует отметить, что в первом варианте выполнения настоящего изобретения предложена матрица проверки на четность блочного кода LDPC с переменной длиной блока для скорости кодирования 1/2. Как показано на фиг. 11, если предположить, что возможный размер Ns частичных матриц составляет 4, 8, 12, 16, 20, 24, 28, 32, 36 и 40, становится возможным сгенерировать блочный код LDPC, имеющий длину 96, 192, 288, 384, 480, 576, 672, 768, 864 и 960, используя матрицу проверки на четность, представленную на фиг. 11. Значение, записываемое в каждом из частичных блоков, то есть в частичных матрицах, представленных на фиг. 11, представляет экспоненциальное значение соответствующей матрицы перестановок. Здесь матрица проверки на четность блочного кода LDPC с переменной длиной блока состоит из множества частичных блоков, и частичные матрицы, по отдельности соответствующие частичным блокам, составляют матрицу перестановок. Например, если матрица проверки на четность блочного кода LDPC с переменной длиной блока состоит из pxq частичных блоков, то есть если количество строк частичных блоков в матрице проверки на четность для блочного кода LDPC с переменной длиной блока составляет "p" и количество столбцов частичных блоков в матрице проверки на четность для блочного кода LDPC с переменной длиной блока составляет "q", матрицы перестановок, составляющие матрицу проверки на четность блочного кода LDPC с переменной длиной блока могут быть выражены как

0 ≤ apq ≤ Ns-1 или apq= ∞. Таким образом, матрица

Для подробного описания настоящего изобретения будет приведено определение следующих параметров.

Матрица проверки на четность блочного кода LDPC с переменной длиной блока, представленная на фиг. 11, называется "материнской матрицей", количество ненулевых матриц перестановок среди частичных матриц, то есть матриц перестановок, составляющих материнскую матрицу, определено как L, экспоненты L не равных нулю матриц перестановок, среди матриц перестановок составляющих материнскую матрицу, представлены как а1, a2,…., al и размер матриц перестановок, составляющих материнскую матрицу, предполагается, равен Ns. Поскольку количество ненулевых матриц перестановок среди матриц перестановок, составляющих материнскую матрицу, равно L, экспонента первой матрицы перестановок становится a1, экспонента второй матрицы перестановок становится равной a2, и таким образом, экспонента последней матрицы перестановок становится равной aL.

В отличие от материнской матрицы, матрица проверки на четность, которая должна быть вновь сгенерирована, называется "дочерней матрицей", количество ненулевых матриц перестановок среди частичных матриц, то есть, матриц перестановок, составляющих дочернюю матрицу, определено как L, размер матриц перестановок, составляющих дочернюю матрицу, определен как Ns′, и экспоненты матриц перестановок, составляющих дочернюю матрицу, представлены как а1', a2',…, al'. Поскольку количество ненулевых матриц перестановок среди матриц перестановок, составляющих дочернюю матрицу, составляет L, экспонента первой матрицы перестановок становится равной а1', экспонента второй матрицы перестановок становится равной a2' и, таким образом, экспонента последней матрицы перестановок становится равной aL'.

Используя приведенное ниже уравнение (5), можно сгенерировать дочернюю матрицу, имеющую переменную длину блока, путем выбора размера Ns' матриц перестановок, составляющих дочернюю матрицу, которая должна быть сгенерирована из одной материнской матрицы.

Далее, со ссылкой на фиг. 12, приведено подробное описание способа генерирования блочного кода LDPC с переменной длиной блока для скорости кодирования 2/3.

На фиг. 12 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока, в соответствии со вторым вариантом выполнения настоящего изобретения. Перед описанием фиг. 12 следует отметить, что во втором варианте выполнения настоящего изобретения предложена матрица проверки на четность блочного кода LDPC с переменной длиной блока для скорости кодирования 2/3. Как показано на фиг. 12, если предположить, что возможный размер Ns частичных матриц равен 8 и 16, возможно сгенерировать блочный код LDPC, имеющий длину 288 и 576, используя матрицу проверки на четность, показанную на фиг. 12. Значение, записанное в каждом из частичных блоков, то есть в частичных матрицах, представленных на фиг. 12, представляет собой экспоненциальное значение соответствующей матрицы перестановок. Поэтому путем выполнения операции модуль-Ns (где Nsсоответствует размеру частичной матрицы) для значения экспоненты матрицы перестановок можно вычислить значение экспоненты матрицы перестановок для матрицы проверки на четность для блочного кода LDPC, имеющего значение Ns. Если значение, полученное в результате выполнения операции модуль-Nsдля экспоненты матрицы перестановок, равно 0, соответствующая матрица перестановок становится единичной матрицей.

Далее, со ссылкой на фиг. 13, будет приведено подробное описание способа генерирования блочного кода LDPC с переменной длиной блока для скорости кодирования 3/4.

На фиг. 13 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока в соответствии с третьим вариантом выполнения настоящего изобретения. Перед описанием фиг. 13 следует отметить, что в третьем варианте выполнения настоящего изобретения предложена матрица проверки на четность блочного кода LDPC с переменной длиной блока для скорости кодирования 3/4. Как показано на фиг. 13, если предположить, что возможный размер Ns частичных матриц составляет 3, 6, 9, 12, 15 и 18, можно сгенерировать блочный код LDPC, имеющий переменную длину 96, 192, 288, 384, 480 и 576, используя матрицу проверки на четность, показанную на фиг. 13. Значение, записанное в каждом из частичных блоков, то есть в частичных матрицах, показанных на фиг. 13, представляет собой значение экспоненты соответствующей матрицы перестановок. Поэтому, выполняя операцию модуль-Ns (где Ns соответствует размеру частичной матрицы) для значения экспоненты матрицы перестановок, можно вычислить значение экспоненты матрицы перестановок для матрицы проверки на четность для блочного кода LDPC, имеющего значение Ns. Если значение, полученное в результате выполнения операции модуль-Ns для экспоненты матрицы перестановок, равно 0, соответствующая матрица перестановок становится единичной матрицей.

Далее, со ссылкой на фиг. 14 будет приведено подробное описание способа генерирования блочного кода LDPC с переменной длиной блока для скорости кодирования 5/6.

На фиг. 14 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока в соответствии с четвертым вариантом выполнения настоящего изобретения. Перед описанием фиг. 14 следует отметить, что в четвертом варианте выполнения настоящего изобретения предложена матрица проверки на четность блочного кода LDPC с переменной длиной блока для скорости кодирования 5/6. Как показано на фиг. 14, если предположить, что возможный размер Ns частичных матриц составляет 8 и 16, можно сгенерировать блочный код LDPC, имеющий длину 288 и 576, используя матрицу проверки на четность, показанную на фиг. 14. Значение, записанное в каждом из частичных блоков, то есть в частичных матрицах, показанных на фиг. 14, представляет собой значение экспоненты соответствующей матрицы перестановок. Поэтому, выполняя операцию модуль-Ns (где Ns соответствует размеру частичной матрицы) для значения экспоненты матрицы перестановок, можно вычислить значение экспоненты матрицы перестановок для матрицы проверки на четность для блочного кода LDPC, имеющего значение Ns. Если значение, полученное в результате выполнения операции модуль-Ns для экспоненты матрицы перестановок, равно 0, соответствующая матрица перестановок становится единичной матрицей.

Далее, со ссылкой на фиг. 18, будет приведено подробное описание способа генерирования блочного кода LDPC с переменной длиной блока для скорости кодирования 1/2.

На фиг. 18 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока в соответствии с пятым вариантом выполнения настоящего изобретения. Перед описанием фиг. 18 следует отметить, что в пятом варианте выполнения настоящего изобретения предложена матрица проверки на четность блочного кода LDPC с переменной длиной блока для скорости кодирования 1/2. Как показано на фиг. 18, можно сгенерировать блочный код LDPC длиной 48NS в соответствии с размером Ns частичной матрицы, используя матрицу проверки на четность, показанную на фиг. 18. Значение, записанное в каждом из частичных блоков, то есть в частичных матрицах, показанных на фиг. 18 представляет собой значение экспоненты соответствующей матрицы перестановок. Поэтому, выполняя операцию модуль-Ns (где Ns соответствует размеру частичной матрицы) для значения экспоненты матрицы перестановок, можно вычислить значение экспоненты матрицы перестановок для матрицы проверки на четность для блочного кода LDPC, имеющего значение Ns. Если значение, полученное в результате выполнения операции модуль-Ns для экспоненты матрицы перестановок, равно 0, соответствующая матрица перестановок становится единичной матрицей.

Далее, со ссылкой на фиг. 19, будет приведено подробное описание способа генерирования блочного кода LDPC с переменной длиной блока для скорости кодирования 2/3.

На фиг. 19 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока в соответствии с шестым вариантом выполнения настоящего изобретения. Перед описанием фиг. 19 следует отметить, что в пятом варианте выполнения настоящего изобретения предложена матрица проверки на четность блочного кода LDPC с переменной длиной блока для скорости кодирования 2/3. Как показано на фиг. 19, можно сгенерировать блочный код LDPC длиной 48NS в соответствии с размером Ns частичной матрицы, используя матрицу проверки на четность, показанную на фиг. 19. Значение, записанное в каждом из частичных блоков, то есть в частичных матрицах, показанных на фиг. 19, представляет собой значение экспоненты соответствующей матрицы перестановок. Поэтому, выполняя операцию модуль-Ns (где Ns соответствует размеру частичной матрицы) для значения экспоненты матрицы перестановок, можно вычислить значение экспоненты матрицы перестановок для матрицы проверки на четность для блочного кода LDPC, имеющего значение Ns. Если значение, полученное в результате выполнения операции модуль-Ns для экспоненты матрицы перестановок, равно 0, соответствующая матрица перестановок становится единичной матрицей.

Далее, со ссылкой на фиг. 20, будет приведено подробное описание способа генерирования блочного кода LDPC с переменной длиной блока для скорости кодирования 3/4.

На фиг. 20 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока в соответствии с седьмым вариантом выполнения настоящего изобретения. Перед описанием фиг. 20 следует отметить, что в пятом варианте выполнения настоящего изобретения предложена матрица проверки на четность блочного кода LDPC с переменной длиной блока для скорости кодирования 3/4. Как показано на фиг. 20, можно сгенерировать блочный код LDPC длиной 48NS в соответствии с размером Ns частичной матрицы, используя матрицу проверки на четность, показанную на фиг. 20. Значение, записанное в каждом из частичных блоков, то есть в частичных матрицах, показанных на фиг. 20, представляет собой значение экспоненты соответствующей матрицы перестановок. Поэтому, выполняя операцию модуль-Ns (где Ns соответствует размеру частичной матрицы) для значения экспоненты матрицы перестановок, можно вычислить значение экспоненты матрицы перестановок для матрицы проверки на четность для блочного кода LDPC, имеющего значение Ns. Если значение, полученное в результате выполнения операции модуль-Ns для экспоненты матрицы перестановок, равно 0, соответствующая матрица перестановок становится единичной матрицей.

Далее, со ссылкой на фиг. 21, будет приведено подробное описание способа генерирования блочного кода LDPC с переменной длиной блока для скорости кодирования 3/4.

На фиг. 21 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока в соответствии с восьмым вариантом выполнения настоящего изобретения. Перед описанием фиг. 21 следует отметить, что в пятом варианте выполнения настоящего изобретения предложена матрица проверки на четность блочного кода LDPC с переменной длиной блока для скорости кодирования 3/4. Как показано на фиг. 21, можно сгенерировать блочный код LDPC длиной 48NS в соответствии с размером Ns частичной матрицы, используя матрицу проверки на четность, показанную на фиг. 21. Значение, записанное в каждом из частичных блоков, то есть в частичных матрицах, показанных на фиг. 21, представляет собой значение экспоненты соответствующей матрицы перестановок. Поэтому, выполняя операцию модуль-Ns (где Ns соответствует размеру частичной матрицы) для значения экспоненты матрицы перестановок, можно вычислить значение экспоненты матрицы перестановок для матрицы проверки на четность для блочного кода LDPC, имеющего значение Ns. Если значение, полученное в результате выполнения операции модуль-Ns для экспоненты матрицы перестановок, равно 0, соответствующая матрица перестановок становится единичной матрицей.

Далее, со ссылкой на фиг. 22, будет приведено подробное описание способа генерирования блочного кода LDPC с переменной длиной блока для скорости кодирования 1/2.

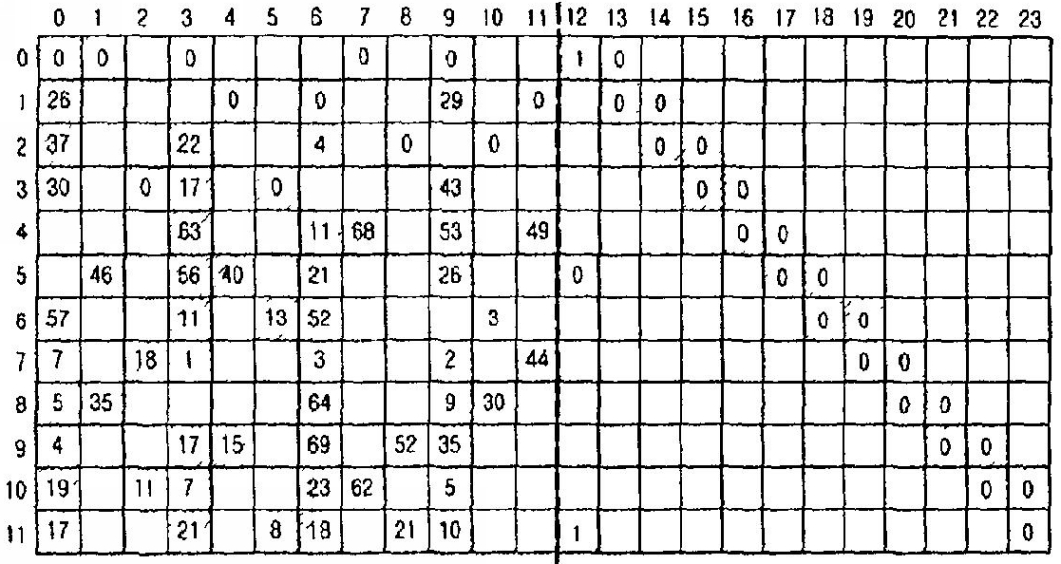

На фиг. 22 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока в соответствии с девятым вариантом выполнения настоящего изобретения. Перед описанием фиг. 22 следует отметить, что в пятом варианте выполнения настоящего изобретения предложена матрица проверки на четность блочного кода LDPC с переменной длиной блока для скорости кодирования 1/2. Как показано на фиг. 22, можно сгенерировать блочный код LDPC длиной 24NS в соответствии с размером Ns частичной матрицы, используя матрицу проверки на четность, показанную на фиг. 22. Значение, записанное в каждом из частичных блоков, то есть в частичных матрицах, показанных на фиг. 22, представляет собой значение экспоненты соответствующей матрицы перестановок. Поэтому, выполняя операцию модуль-Ns (где Ns соответствует размеру частичной матрицы) для значения экспоненты матрицы перестановок, можно вычислить значение экспоненты матрицы перестановок для матрицы проверки на четность для блочного кода LDPC, имеющего значение Ns. Если значение, полученное в результате выполнения операции модуль-Ns для экспоненты матрицы перестановок, равно 0, соответствующая матрица перестановок становится единичной матрицей.

Далее, со ссылкой на фиг. 23, будет приведено подробное описание способа генерирования блочного кода LDPC с переменной длиной блока для скорости кодирования 1/2.

На фиг. 23 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока в соответствии с десятым вариантом выполнения настоящего изобретения. Перед описанием фиг. 23 следует отметить, что в пятом варианте выполнения настоящего изобретения предложена матрица проверки на четность блочного кода LDPC с переменной длиной блока для скорости кодирования 1/2. Как показано на фиг. 23, можно сгенерировать блочный код LDPC длиной 24NS в соответствии с размером Ns частичной матрицы, используя матрицу проверки на четность, показанную на фиг. 23. Значение, записанное в каждом из частичных блоков, то есть в частичных матрицах, показанных на фиг. 23, представляет собой значение экспоненты соответствующей матрицы перестановок. Поэтому, выполняя операцию модуль-Ns (где Ns соответствует размеру частичной матрицы) для значения экспоненты матрицы перестановок, можно вычислить значение экспоненты матрицы перестановок для матрицы проверки на четность для блочного кода LDPC, имеющего значение Ns. Если значение, полученное в результате выполнения операции модуль-Ns для экспоненты матрицы перестановок, равно 0, соответствующая матрица перестановок становится единичной матрицей.

Далее, со ссылкой на фиг. 24, будет приведено подробное описание способа генерирования блочного кода LDPC с переменной длиной блока для скорости кодирования 2/3.

На фиг. 24 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока в соответствии с одиннадцатым вариантом выполнения настоящего изобретения. Перед описанием фиг. 24 следует отметить, что в пятом варианте выполнения настоящего изобретения предложена матрица проверки на четность блочного кода LDPC с переменной длиной блока для скорости кодирования 2/3. Как показано на фиг. 24, можно сгенерировать блочный код LDPC длиной 24NS в соответствии с размером Ns частичной матрицы, используя матрицу проверки на четность, показанную на фиг. 24. Значение, записанное в каждом из частичных блоков, то есть в частичных матрицах, показанных на фиг. 24, представляет собой значение экспоненты соответствующей матрицы перестановок. Поэтому, выполняя операцию модуль-Ns (где Ns соответствует размеру частичной матрицы) для значения экспоненты матрицы перестановок, можно вычислить значение экспоненты матрицы перестановок для матрицы проверки на четность для блочного кода LDPC, имеющего значение Ns. Если значение, полученное в результате выполнения операции модуль-Ns для экспоненты матрицы перестановок, равно 0, соответствующая матрица перестановок становится единичной матрицей.

Далее, со ссылкой на фиг. 25, будет приведено подробное описание способа генерирования блочного кода LDPC с переменной длиной блока для скорости кодирования 2/3.

Фиг. 25 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока в соответствии с двенадцатым вариантом выполнения настоящего изобретения. Перед описанием фиг. 25 следует отметить, что в пятом варианте выполнения настоящего изобретения предложена матрица проверки на четность блочного кода LDPC с переменной длиной блока для скорости кодирования 2/3. Как показано на фиг. 25, можно сгенерировать блочный код LDPC длиной 24NS в соответствии с размером Ns частичной матрицы, используя матрицу проверки на четность, показанную на фиг. 25. Значение, записанное в каждом из частичных блоков, то есть в частичных матрицах, показанных на фиг. 25, представляет собой значение экспоненты соответствующей матрицы перестановок. Поэтому, выполняя операцию модуль-Ns (где Ns соответствует размеру частичной матрицы) для значения экспоненты матрицы перестановок, можно вычислить значение экспоненты матрицы перестановок для матрицы проверки на четность для блочного кода LDPC, имеющего значение Ns. Если значение, полученное в результате выполнения операции модуль-Ns для экспоненты матрицы перестановок, равно 0, соответствующая матрица перестановок становится единичной матрицей.

Далее, со ссылкой на фиг. 26, будет приведено подробное описание способа генерирования блочного кода LDPC с переменной длиной блока для скорости кодирования 1/2.

На фиг. 26 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока в соответствии с тринадцатым вариантом выполнения настоящего изобретения. Перед описанием фиг. 26 следует отметить, что в пятом варианте выполнения настоящего изобретения предложена матрица проверки на четность блочного кода LDPC с переменной длиной блока для скорости кодирования 1/2. Как показано на фиг. 26, можно сгенерировать блочный код LDPC длиной 24NS в соответствии с размером Ns частичной матрицы, используя матрицу проверки на четность, показанную на фиг. 26. Значение, записанное в каждом из частичных блоков, то есть в частичных матрицах, показанных на фиг. 26, представляет собой значение экспоненты соответствующей матрицы перестановок. Поэтому, выполняя операцию модуль-Ns (где Ns соответствует размеру частичной матрицы) для значения экспоненты матрицы перестановок, можно вычислить значение экспоненты матрицы перестановок для матрицы проверки на четность для блочного кода LDPC, имеющего значение Ns. Если значение, полученное в результате выполнения операции модуль-Ns для экспоненты матрицы перестановок, равно 0, соответствующая матрица перестановок становится единичной матрицей.

Далее, со ссылкой на фиг. 27, будет приведено подробное описание способа генерирования блочного кода LDPC с переменной длиной блока для скорости кодирования 1/2.

На фиг. 27 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока в соответствии с четырнадцатым вариантом выполнения настоящего изобретения. Перед описанием фиг. 27 следует отметить, что в пятом варианте выполнения настоящего изобретения предложена матрица проверки на четность блочного кода LDPC с переменной длиной блока для скорости кодирования 1/2. Как показано на фиг. 27, можно сгенерировать блочный код LDPC длиной 24NS в соответствии с размером Ns частичной матрицы, используя матрицу проверки на четность, показанную на фиг. 27. Значение, записанное в каждом из частичных блоков, то есть в частичных матрицах, показанных на фиг. 27, представляет собой значение экспоненты соответствующей матрицы перестановок. Поэтому, выполняя операцию модуль-Ns (где Ns соответствует размеру частичной матрицы) для значения экспоненты матрицы перестановок, можно вычислить значение экспоненты матрицы перестановок для матрицы проверки на четность для блочного кода LDPC, имеющего значение Ns. Если значение, полученное в результате выполнения операции модуль-Ns для экспоненты матрицы перестановок, равно 0, соответствующая матрица перестановок становится единичной матрицей.

Далее, со ссылкой на фиг. 28, будет приведено подробное описание способа генерирования блочного кода LDPC с переменной длиной блока для скорости кодирования 2/3.

На фиг. 28 показана схема, иллюстрирующая матрицу проверки на четность блочного кода LDPC с переменной длиной блока в соответствии с пятнадцатым вариантом выполнения настоящего изобретения. Перед описанием фиг. 28 следует отметить, что в пятом варианте выполнения настоящего изобретения предложена матрица проверки на четность блочного кода LDPC с переменной длиной блока для скорости кодирования 2/3. Как показано на фиг. 28, можно сгенерировать блочный код LDPC длиной 24NS в соответствии с размером Ns частичной матрицы, используя матрицу проверки на четность, показанную на фиг. 28. Значение, записанное в каждом из частичных блоков, то есть в частичных матрицах, показанных на фиг. 28, представляет собой значение экспоненты соответствующей матрицы перестановок. Поэтому, выполняя операцию модуль-Ns (где Ns соответствует размеру частичной матрицы) для значения экспоненты матрицы перестановок, можно вычислить значение экспоненты матрицы перестановок для матрицы проверки на четность для блочного кода LDPC, имеющего значение Ns. Если значение, полученное в результате выполнения операции модуль-Ns для экспоненты матрицы перестановок, равно 0, соответствующая матрица перестановок становится единичной матрицей.

Все коды семейства LDPC можно декодировать в фактор-графе, используя алгоритм промежуточного результата. Схема декодирования кода LDPC может быть примерно разделена на схему двунаправленной передачи и схему передачи потока. Когда операцию декодирования выполняют, используя схему двунаправленной передачи, каждый узел проверки имеет процессор узла, который увеличивает сложность декодирования пропорционально количеству узлов проверки. Однако, поскольку все узлы проверки обновляют одновременно, скорость декодирования существенно повышается.

В отличие от этого, схема передачи потока имеет один процессор узла, и процессор узла обновляет информацию, проходящую через все узлы в фактор-графе. Поэтому схема передачи потока имеет меньшую сложность декодирования, но при увеличении размера матрицы проверки на четность, то есть при увеличении количества узлов, уменьшается скорость декодирования. Однако если матрица проверки на четность генерируется поблочно, как в блочном коде LDPC с переменной длиной блока, имеющем различные длины блока в соответствии со скоростью кодирования, предложенном в настоящем изобретении, тогда используют количество процессоров узлов, равных количеству блоков, составляющих матрицу проверки на четность. В этом случае возможно выполнить декодер, который имеет меньшую сложность декодирования, чем схема двунаправленной передачи, и более высокую скорость декодирования, чем схема передачи потока.

Далее, со ссылкой на фиг. 17, приведено описание внутренней структуры устройства декодирования, предназначенного для декодирования блочного кода LDPC с переменной длиной блока с использованием матрицы проверки на четность, в соответствии с вариантом выполнения настоящего изобретения.