Устройство сдвига групп данных - RU2674934C1

Код документа: RU2674934C1

Чертежи

Описание

Изобретение относится к области вычислительной техники и может быть использовано в процессорах обработки сигналов и процессорах общего назначения, устройствах преобразования информации, кодирования и декодирования данных, устройствах криптографии.

Известно устройство Circuit for rotating, left shifting, or right shifting bits (US 5978822 (А) МПК G06F 5/01, G06F 7/76, заявлено 29.12.1995, опубликовано 02.11.1999), в котором описано устройство для выполнения логических, циклических и арифметических сдвигов входных данных влево и вправо на заданное количество разрядов. Устройство содержит матрицу мультиплексоров сдвига только в одну сторону - влево, старших разрядов, мультиплексор передачи входных данных в прямом или в «перевернутом» обратном порядке разрядов, мультиплексор передачи разрядов кода величины сдвига или их инверсию, выходы которого управляют матрицей мультиплексоров, выходной мультиплексор передачи сдвинутых данных в прямом порядке разрядов или в «перевернутом» обратном порядке разрядов со сдвигом на один разряд.

Недостатками данного устройства является низкое быстродействие, так как входные данные кроме матрицы мультиплексоров дополнительно проходят через мультиплексор передачи входных данных и выходной мультиплексор, и потеря старших выдвигаемых разрядов при логическом сдвиге.

Известно устройство Fast conversion two's complement encoded shift value for a barrel shifter (US 5948050 (А) МПК G06F 5/01, заявлено 19.12.1996, опубликовано 07.09.1999), в котором описано устройство для выполнения циклических или логических сдвигов влево или вправо N разрядных входных данных на величину сдвига в диапазоне от 0 до N-1 разряда, который задается М разрядами, где M=log2N. Устройство сдвига содержит N разрядные входные данные, N разрядные выходные данные, М разрядов задания значения количества сдвигов, двунаправленную матрицу сдвига размерностью N×N, группу из М элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, дешифратор направления сдвига, дешифратор и мультиплексор количества и направления сдвига.

Недостатками данного устройства является большой объем оборудования и низкое быстродействие, а также не возможность выполнения сдвигов на N и более N разрядов и потеря старших выдвигаемых разрядов при логическом сдвиге.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятое за прототип, устройство сдвига (RU №2613533 С1, МПК G06F 5/01, G11C 19/00, Н03М 13/00 заявлено 08.02.2016, опубликовано 16.03.2017, Бюл. №8), содержащее N разрядов внешних входных данных D0, D1, …, D(N-1), N разрядов выходных данных Y0, Y0, …, Y(N-1), V разрядов задания значения количества сдвигов К0, К1, …, К(V-1), двунаправленную матрицу сдвига размерностью N×M, где M≤log2N, из М каскадов, содержащих группы элементов 2И-2И-2И-3ИЛИ и 2И-2И-2ИЛИ, блок модификации количества сдвигов, блок управления направлением сдвига и блок формирования флага нулевого результата, причем в матрице сдвигов каскады содержат по три группы элементов.

Недостатками данного устройств является потеря старших выдвигаемых разрядов при логическом сдвиге, не возможность выполнения групповых сдвигов входных данных заданной разрядности и большой объем оборудования.

Техническим результатом предлагаемого устройства является возможность сдвига групп двоичных данных различной разрядности без потери выдвигаемых разрядов и снижение аппаратных затрат.

Указанный технический результат при осуществлении изобретения достигается тем, что устройство сдвига групп данных содержит

N групп внешних входных данных DG1, DG2, …, DGN, с разрядностью групп W1, W2, …, WN соответственно, U разрядов внешних входов задания значения количества сдвигов V0, V1, …, V(U-1) на величину сдвига групп от 0 до L, где U=[log2L]+1 (меньшее целое), (N+L) групп внешних выходных данных QG1, QG2, …, QG(N+L), (U+1) внутренних шин сдвига SB0, SB1, …, SBU, U каскадов модулей элементов с 0-го по (U-1), из которых каждый i-й каскад, где i=0, 1, …, (U-1), содержит по (N+2i+1-1) модулей элементов объединенных в три секции,

причем первые секции каскадов состоят из модулей содержащих группы элементов 2И со вторым инверсным входом, вторые секции каскадов состоят из модулей содержащих группы элементов 2И со вторым инверсным входом, элементов 2И и элементов 2ИЛИ, а третьи секции каскадов состоят из модулей содержащих группы элементов 2И,

причем в каждом i-м каскаде первые секции содержат по 2i модулей элементов, начиная с первого до 2i модуля i-го каскада, вторые секции содержат по (N-1) модулей элементов, начиная с (2i+1)-го до (N+2i-1) модуля i-го каскада, а третьи секции содержат по 2i модулей элементов, начиная с (N+2i)-го до (N+2i+1-1) модуля i-го каскада,

причем N групп внешних входных данных DG1, DG2, …, DGN являются N группами разрядов 0-й внутренней шины сдвига SB0 с разрядностью групп K(0, 1), K(0, 2), …, K(0, N) соответственно, а выходы модулей элементов каждого i-го каскада образуют соответствующие группы выходов каскадов и являются группами разрядов последующей (i+1)-й внутренней шины сдвига SB(i+1) с разрядностью групп К(i+1, j), где j=1, 2, …, (N+2i+1-1) - номер модуля в каскаде, при этом разряды групп первых U внутренних шин сдвига SB0, SB1, …, SB(U-1), кроме последней внутренней шины SBU, соединены с входами групп модулей элементов соответствующих одноименных каскадов с 0-го по (U-1)-й каскад,

причем в каждом i-м каскаде в первых секциях модулей в каждом j1-м модуле, где j1=1, 2, …, 2i, содержится группа из К(i, j1) элементов 2И со вторым инверсным входом, выходы которых являются выходами первых младших 2i модулей, с первого до (2i)-го модуля i-го каскада,

во вторых секциях модулей каждого i-го каскада в каждом j2-м модуле содержится К(i, j2) элементов 2И со вторым инверсным входом, К(i, j2-2i) элементов 2И, где j2=2i+1, 2i+2, …, (2i+N-1) и (min(К(i, j2), К(i, j2-2i))) элементов 2ИЛИ, у которых первые и вторые входы соединены с выходами соответствующих первых элементов 2И со вторым инверсным входом и соответствующих первых элементов 2И j2-го модуля, при этом каждый j2-й модуль имеет (max(К(i, j2), К(i, j2-2i))) выходов, из которых первые (min(К(i, j2), К(i, j2-2i))) выходы j2-го модуля соединены с выходами элементов 2 ИЛИ, а выходы j2-го модуля с (min(К(i, j2), К(i, j2-2i))+1)-го до (max(К(i, j2), К(i, j2-2i)))-го соединены с выходами одноименных элементов 2И со вторым инверсным входом модуля при К(i, j2)>К(i, j2-2i) или соединены с выходами одноименных элементов 2И модуля при К(i, j2)<К(i, j2-2i),

а в третьих секциях каждого i-го каскада в каждом j3-м модуле, где j3=2i+N, 2i+N+1, …, (2i+1+N-1), содержится группа из К(i, j3) элементов 2И, выходы которых являются выходами последних старших 2i модулей, с (N+2i)-го до (N+2i+1-1)-го модуля i-го каскада,

причем в каждом i-м каскаде первые входы всех элементов 2И со вторым инверсным входом соединены с первыми входами соответствующих одноименных элементов 2И и также соединены с соответствующими разрядами групп соответствующей i-й внутренней шины сдвига SBi, а вторые инверсные входы всех элементов 2И со вторым инверсным входом соединены между собой, а также соединены со вторыми входами всех элементов 2И и соединены с соответствующим Vi-м разрядом внешних входов задания значения количества сдвигов,

выходы (N+L) групп последней старшей (U+1)-й внутренней шины сдвига SBU являются (N+L) группами внешних выходных данных QG1, QG2, …, QG(N+L) с разрядностью групп К(U, 1), К(U, 2), …, К(U, (N+L)) соответственно.

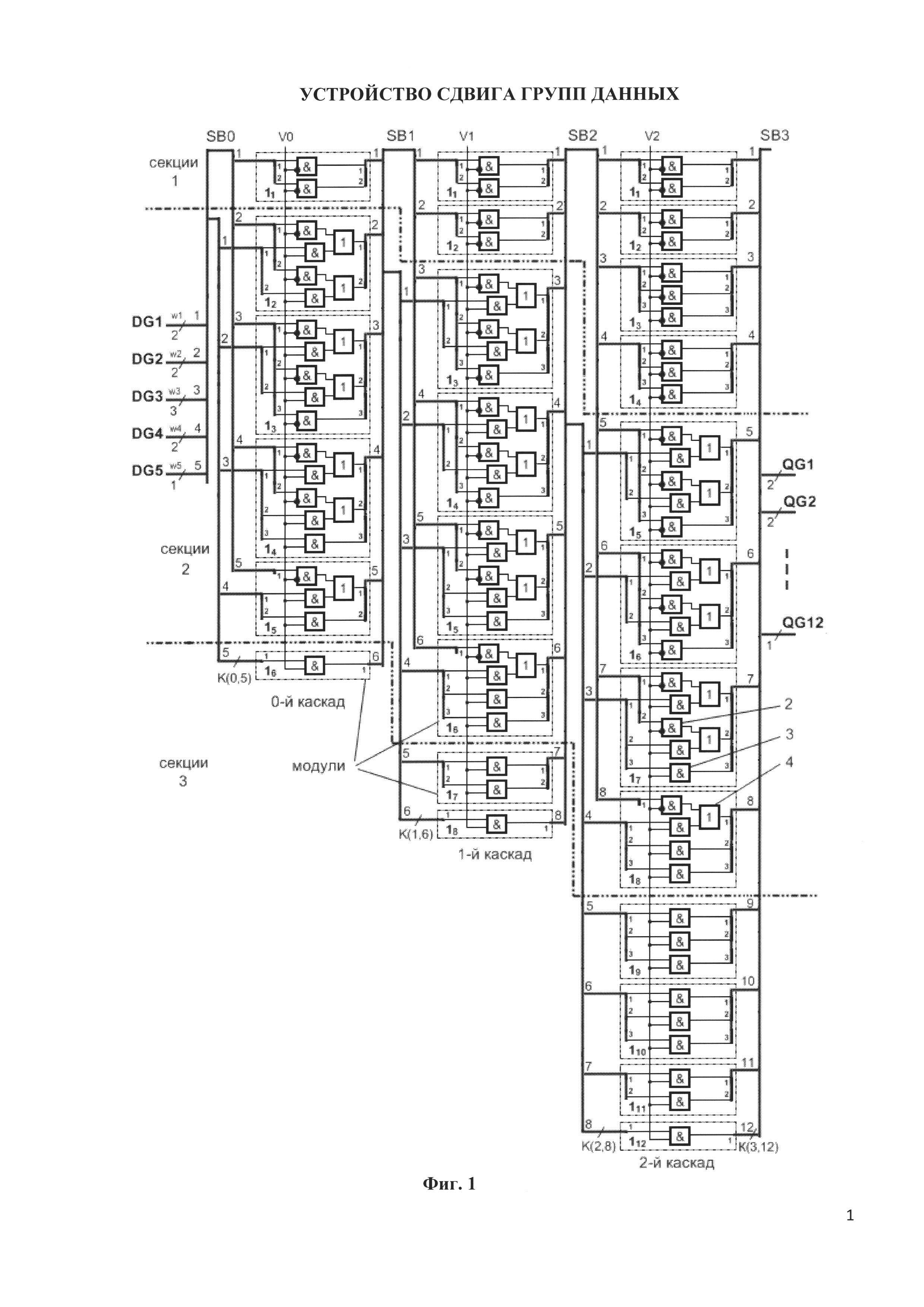

На фиг. 1 представлена схема предлагаемого устройства сдвига групп данных при количестве групп N=5 с разрядностью групп соответственно W1=2, W2=2, W3=3, W4=2, W5=1 и величиной сдвига L=7.

На фиг. 1 и в тексте введены следующие обозначения:

DG1, DG2, …, DGN - N групп внешних входных данных, с разрядностью W1, W2, …, WN соответственно,

L - величина сдвига групп,

V0, V1, …, V(U-1) - U разрядов внешних входов задания значения количества сдвигов, где U=[log2L]+1 (меньшее целое),

QG1, QG2, …, QG(N+L) - (N+L) групп внешних выходных данных,

К(U, 1), К(U, 2), …, К(U, (N+L)) - разрядность групп внешних выходных данных,

SB0, SB1, …, SBU - (U+1) внутренних шин сдвига,

i - номер каскада, где i=0, 1, …, (U-1),

j1 - номер модуля в первых секциях каждого i-го каскада, где j1=1, 2, …, 2i,

j2 - номер модуля во вторых секциях каждого i-го каскада, где j2=2i+1, 2i+2, …, (2i+N-1),

j3 - номер модуля в третьих секциях каждого i-го каскада, где j3=2i+N, 2i+N+1, …, (2i+1+N-1),

j - номер модуля в каскаде, где j=1, 2, …, (N+2i+1-1),

К(i, j) - разрядность групп j-го модуля в i-м каскаде,

1j - j-й модуль элементов в каскаде,

2 - элемент 2И со вторым инверсным входом,

3 - элемент 2И,

4 - элемент 2ИЛИ.

Устройство имеет N групп внешних входных данных DG1, DG2, …, DGN, с разрядностью групп W1, W2, …, WN соответственно, U разрядов внешних входов задания значения количества сдвигов V0, V1, …, V(U-1) на величину сдвига групп от 0 до L, где U=[log2L]+1 (меньшее целое), (N+L) групп внешних выходных данных QG1, QG2, …, QG(N+L), (U+1) внутренних шин сдвига SB0, SB1, …, SBU, U каскадов модулей элементов с 0-го по (U-1), из которых каждый i-й каскад, где i=0, 1, …, (U-1), содержит по (N+2i+1-1) модулей элементов объединенных в три секции.

Первые секции каскадов состоят из модулей содержащих группы элементов 2И со вторым инверсным входом, вторые секции каскадов состоят из модулей содержащих группы элементов 2И со вторым инверсным входом, элементов 2И и элементов 2ИЛИ, а третьи секции каскадов состоят из модулей содержащих группы элементов 2И.

В каждом i-м каскаде, где i=0, 1, …, (U-1), первые секции содержат по 2i модулей элементов, начиная с первого до 2i модуля i-го каскада, вторые секции содержат по (N-1) модулей элементов, начиная с (2i+1)-го до (N+2i-1) модуля i-го каскада, а третьи секции содержат по 2i модулей элементов, начиная с (N+2i)-го до (N+2i+1-1) модуля i-го каскада.

N групп внешних входных данных DG1, DG2, …, DGN являются N группами разрядов 0-й внутренней шины сдвига SB0 с разрядностью групп K(0, 1), K(0, 2), …, K(0, N) соответственно. Выходы модулей элементов каждого i-го каскада образуют соответствующие группы выходов каскадов и являются группами разрядов последующей (i+1)-й внутренней шины сдвига SB(i+1) с разрядностью групп К(i+1, j), где j=1, 2, …, (N+2i+1-1) - номер модуля в каскаде. Разряды групп первых U внутренних шин сдвига SB0, SB1, …, SB(U-1), кроме последней внутренней шины SBU, соединены с входами групп модулей элементов соответствующих одноименных каскадов с 0-го по (U-1)-й каскад.

В каждом i-м каскаде в первых секциях модулей в каждом j1-м модуле, где j1=1, 2, …2i, содержится группа из К(i, j1) элементов 2И со вторым инверсным входом, выходы которых являются выходами первых младших 2i модулей, с первого до (2i)-го модуля i-го каскада.

Во вторых секциях модулей каждого i-го каскада в каждом j2-м модуле содержится К(i, j2) элементов 2И со вторым инверсным входом, К(i, j2-2i) элементов 2И, где j2=2i+1, 2i+2, …, (2i+N-1) и (min(К(i, j2), …, К(i, j2-2i))) элементов 2ИЛИ, у которых первые и вторые входы соединены с выходами соответствующих первых элементов 2И со вторым инверсным входом и соответствующих первых элементов 2И j2-го модуля. При этом каждый j2-й модуль имеет (max(К(i, j2), К(i, j2-2i))) выходов, из которых первые (min(К(i, j2), К(i, j2-2i))) выходы j2-го модуля соединены с выходами элементов 2 ИЛИ, а выходы j2-го модуля с (min(К(i, j2), К(i, j2-2i))+1)-го до (max(К(i, j2), К(i, j2-2i)))-го соединены с выходами одноименных элементов 2И со вторым инверсным входом модуля при К(i, j2)>К(i, j2-2i) или соединены с выходами одноименных элементов 2И модуля при К(i, j2)<К(i, j2-2i).

В третьих секциях каждого i-го каскада в каждом j3-м модуле, где j3=2i+N, 2i+N+1, …, (2i+1+N-1), содержится группа из К(i, j3) элементов 2И, выходы которых являются выходами последних старших 2i модулей, с (N+2i)-го до (N+2i+1-1)-го модуля i-го каскада.

Кроме того в каждом i-м каскаде первые входы всех элементов 2И со вторым инверсным входом соединены с первыми входами соответствующих одноименных элементов 2И и также соединены с соответствующими разрядами групп соответствующей i-й внутренней шины сдвига SBi, а вторые инверсные входы всех элементов 2И со вторым инверсным входом соединены между собой, а также соединены со вторыми входами всех элементов 2И и соединены с соответствующим Vi-м разрядом внешних входов задания значения количества сдвигов.

Выходы (N+L) групп последней старшей (U+1)-й внутренней шины сдвига SBU являются (N+L) группами внешних выходных данных QG1, QG2, …, QG(N+L) с разрядностью групп К(U, 1), К(U, 2), …, К(U, (N+L)) соответственно.

Принцип работы устройства состоит в следующем.

Устройство предназначено для групповых сдвигов влево в сторону старших групп N групп внешних входных данных DG1, DG2, …, DGN, с заданной разрядностью групп W1, W2, …, WN соответственно, на величину сдвига групп от 0 до L. Группы входных данных являются целыми числами без знака. Во входных данных группа DG1 является младшей группой, а группа DGN является старшей группой. Сдвиг групп данных осуществляется в U каскадах модулей содержащих группы элементов 2И со вторым инверсным входом, элементов 2И и элементов 2ИЛИ, где U=[log2L]+l (меньшее целое). Величина сдвига групп L задается U разрядами внешних входов задания значения количества сдвигов V0, V1, …, V(U-1).

В каждом i-м каскаде на первые входы всех элементов 2И со вторым инверсным входом и первые входы всех элементов 2И поступают данные соответствующих разрядов групп с внутренней шины SBi, а на вторые входы всех элементов 2И со вторым инверсным входом и вторые входы всех элементов 2И поступает значение с соответствующего Vi-го разряда задания значения количества сдвигов. Но так как элементы 2И расположены в модулях каскадов со сдвигом влево (в сторону старших групп) относительно элементов 2И с инверсным входом на 2i модулей, то данные с внутренних шин на выходы элементов 2И инверсным входом передаются без сдвига при Vi=0, а на выходы элементов 2И со сдвигом на 2' групп при Vi=1.

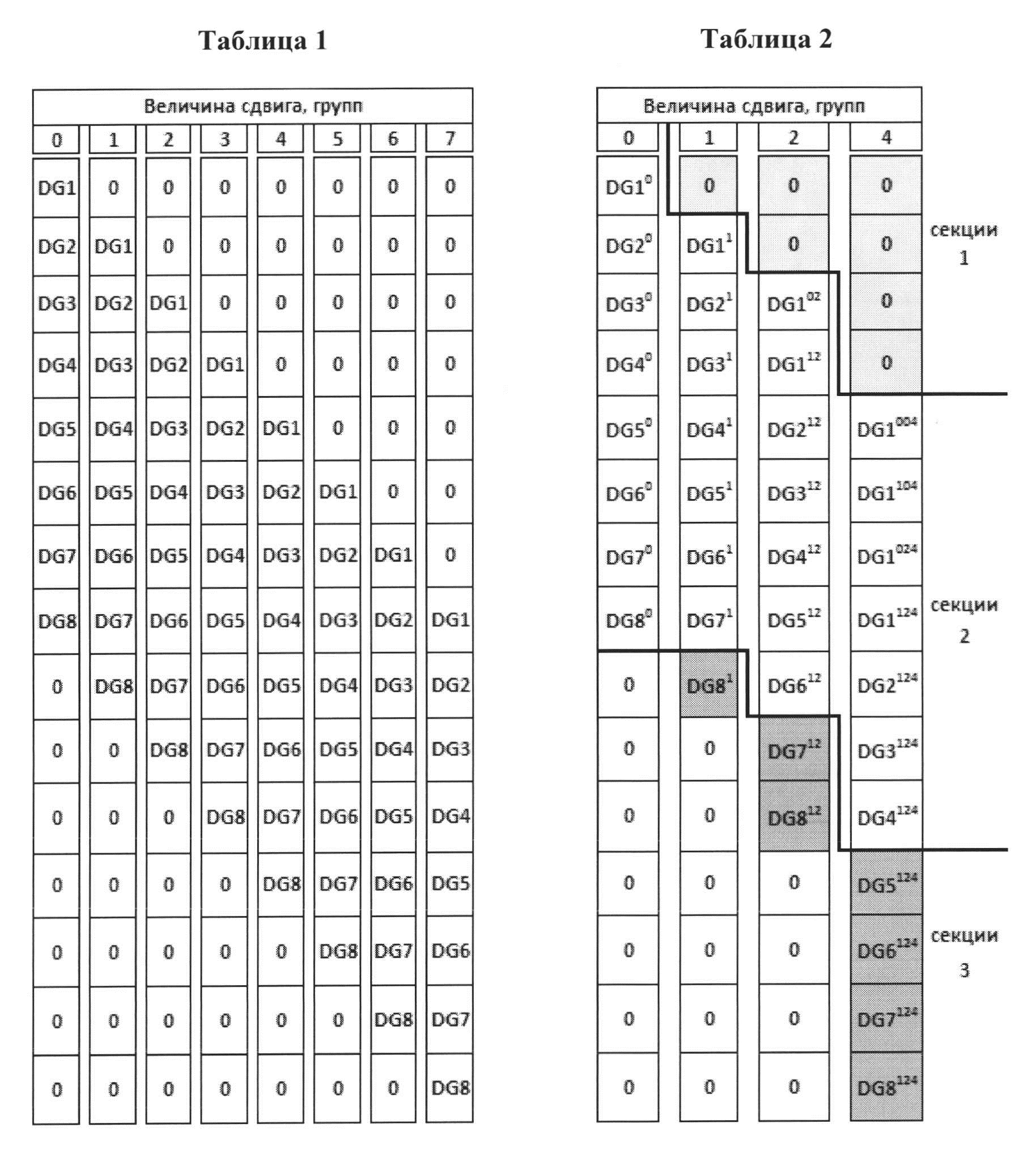

При сдвиге разряды входных данных по группам сдвигаются влево в сторону старших групп на величину сдвига L без потери выдвигаемых разрядов групп. При этом разряды L младших групп заполняются нулями. В таблице 1 приведен пример сдвига восьми групп входных данных DG1, DG2, …, DG8 на величину сдвига в диапазоне от 0 до 7 групп. В таблице 2 приведен пример сдвига входных групп данных по каскадам. В каждом i-м каскаде, где i=0, 1, …, (U-1), выполняется передача групп данных без сдвига или со сдвигом на 2i групп влево. На входы 0-го каскада поступают группы входных данных. Далее с выходов предыдущего i-го каскада группы данных передаются на внутреннюю шину SB(i+1) и далее на входы последующего (i+1)-го каскада.

В таблице 2 в каскадах выделены три секции групп данных:

- в первых секциях, младших групп каскадов, на выходы каскадов при нулевом значении входа задания сдвига Vi=0 передаются значение входных групп каскада с внутренней шины SBi без сдвига, а при единичном значении Vi=1 формируются нулевые значения разрядов, что реализуется на элементах 2И с инверсным входом (входом запрета) соединенным с входом задания сдвига Vi,

- во вторых секциях, средних группах каскадов, выполняется передача на выходы данных без сдвига (Vi=0) или со сдвигом на 2i групп (Vi=1) влево, что реализуется на элементах 2И с инверсным входом и элементах 2И, выходы которых соединены по разрядам с входами соответствующих элементов 2ИЛИ,

- в третьих секциях, старших группах каскадов, выполняется передача на выходы данных с внутренней шины SBi со сдвигом на 2i групп (Vi=1) влево или формируются нулевые значения разрядов (Vi=0), что реализуется на элементах 2И.

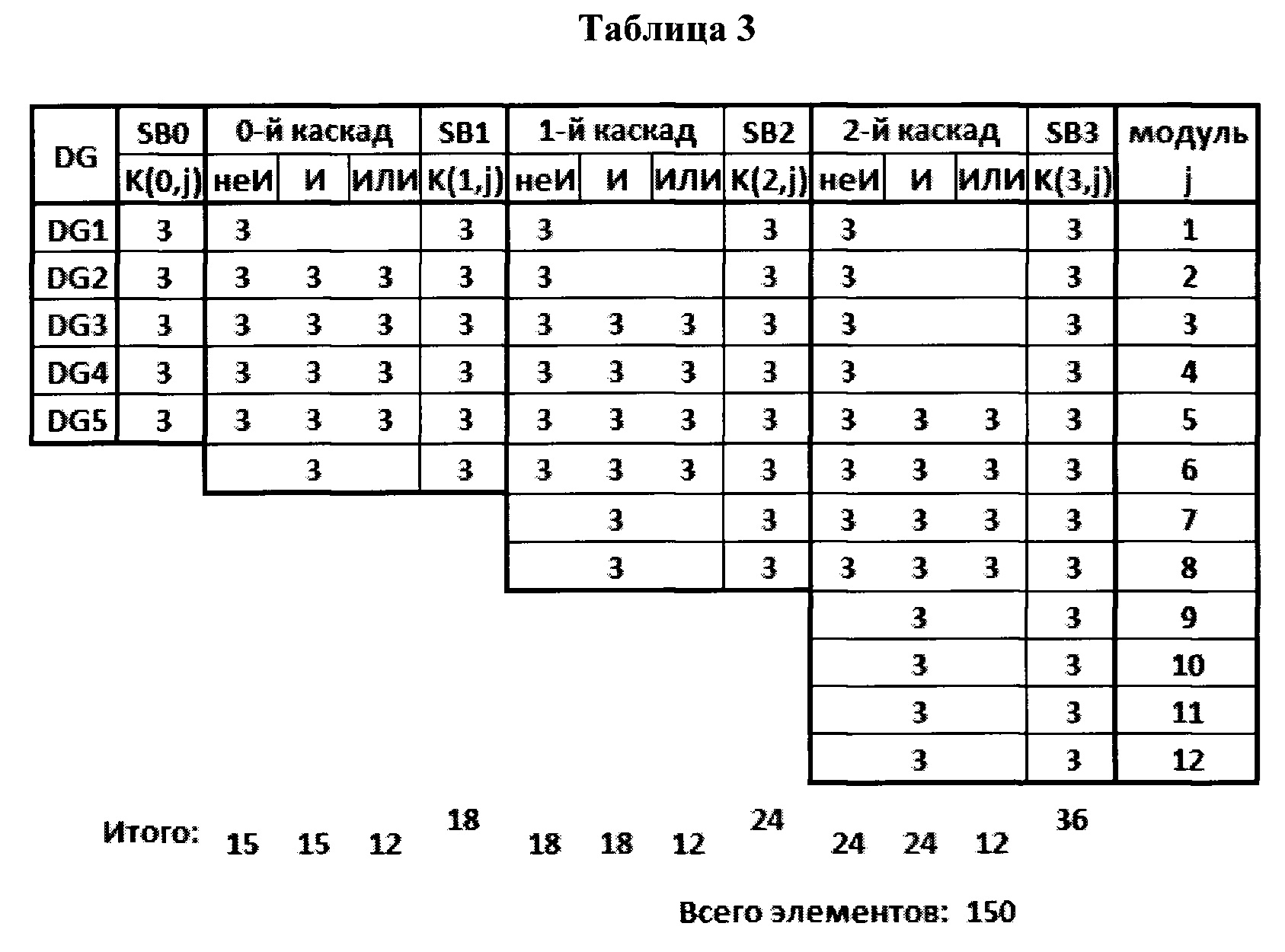

Если все группы входных данных DG1, DG2, …, DGN имеют одинаковую разрядность групп W1=W2=…=WN=w, то во всех модулях элементов всех каскадов количество входных разрядов групп и количество выходов модуля равны w. Например, в таблице 3, для пяти групп входных данных DG1, DG2, …, DG5 и разрядности всех групп w=3 при величине сдвига групп от 0 до L=7, приведен пример расчета необходимого количества элементов 2И с инверсным входом (обозначен неИ), элементов 2И (И) и элементов 2ИЛИ (ИЛИ) по каскадам и модулям, а также отмечены разрядности групп К(i, j) внутренних шин сдвига SB0, SBI, SB2, SB3. Общее количество элементов в трех каскадах составляет 150 элементов.

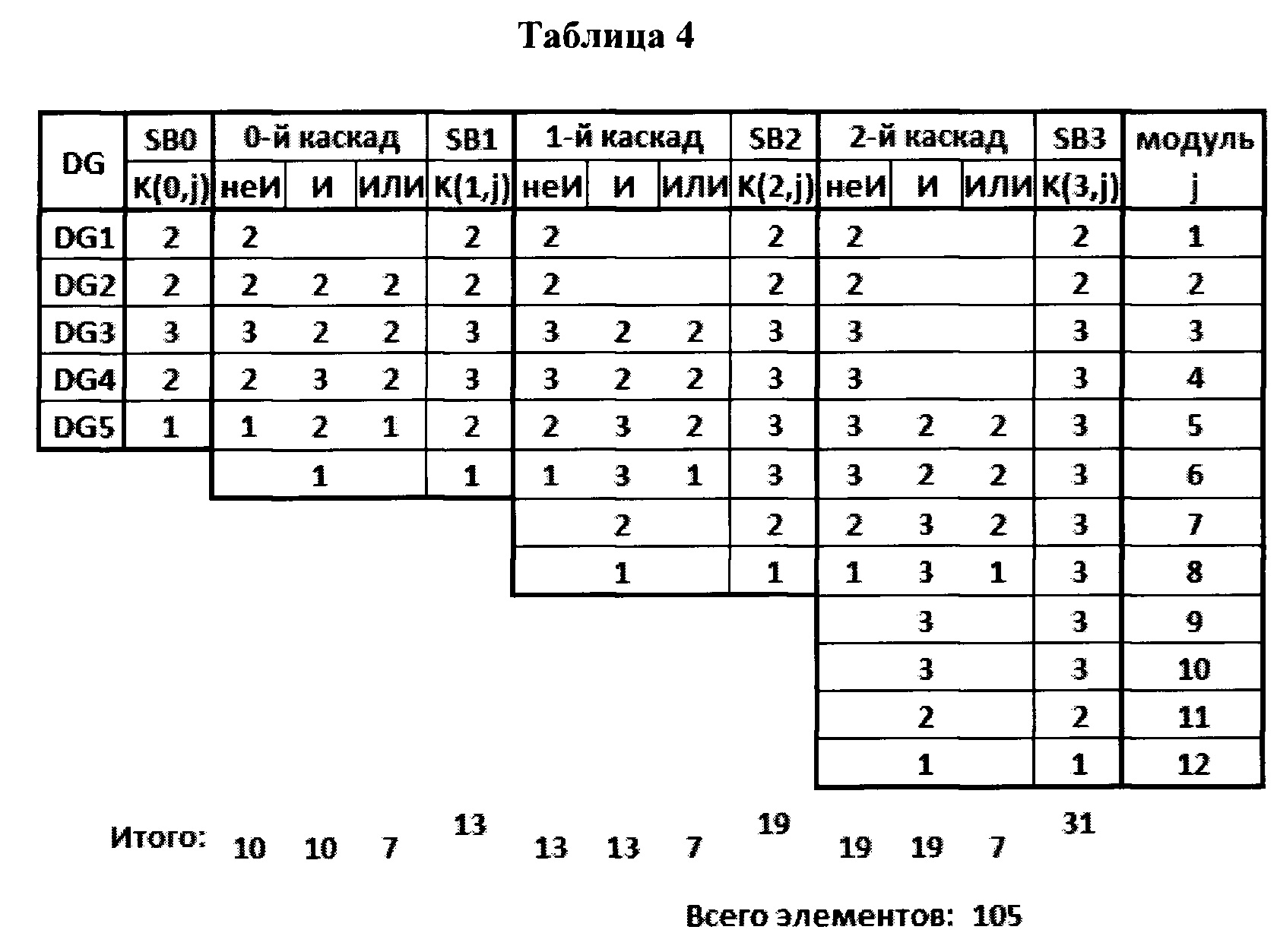

В таблице 4 приведены расчеты количества элементов по каскадам и модулям для пяти групп входных данных DG1, DG2, …, DG5 и разрядности групп W1=2, W2=2, W3=3, W4=2, W5=1 при величине сдвига групп от 0 до L=7, при величине сдвига групп от 0 до L=7. В этом случае в модулях первых секций количество выходных разрядов равно количеству входных разрядов в группе и значения выходов передаются с выходов элементов 2И с инверсным входом, количество которых равно входной разрядности модуля. В модулях вторых секций при равенстве количества разрядов групп без сдвига и групп со сдвигом количество выходных разрядов также равно количеству входных разрядов в группах. В каждом модуле вторых секций при превышении разрядности входных групп без сдвига над разрядностью групп со сдвигом старшие разряды выходов модуля соединены с выходами элементов 2И с инверсным входом, а при превышении разрядности входных групп со сдвигом над разрядностью групп без сдвига старшие разряды выходов модуля соединены с выходами элементов 2И. В модулях третьих секций количество выходных разрядов равно количеству входных разрядов в группе и значения выходов передаются с выходов элементов 2И, количество которых равно входной разрядности модуля.

Значения внешних (N+L) групп выходных данных QG1, QG2, …, QG(N+L) снимаются с последней старшей (U+1)-й внутренней шины сдвига SBU, а разрядность выходных групп соответствует разрядности модулей элементов последнего (U-1)-го каскада, которые являются разрядами групп внутренней шины SBU - К(U, 1), К(U, 2), …, К(U, (N+L)) соответственно.

Предлагаемое устройство работает следующим образом.

На входы устройства подаются N групп внешних входных данных DG1, DG2, …, DGN с заданной разрядностью W1, W2, …, WN соответственно, U разрядов внешних входов задания значения количества сдвигов V0, V1, …, V(U-1), задающие величину сдвига от 0 до L групп.

Далее N групп внешних входных данных DG1, DG2, …, DGN поступают на внутреннюю шину сдвига SB0 и далее на 0-й каскад модулей элементов. Например, в таблице 4 приведены количество элементов и разрядность модулей каскадов для пяти N=5 групп входных данных DG1, DG2, …, DG5 с заданной разрядностью групп W1=2, W2=2, W3=3, W4=2, W5=1 при величине сдвига групп от 0 до L=7. В 0-м каскаде содержится 10 элементов 2И с инверсным входом и 10 элементов 2И, что соответствует входной разрядности всех групп. В первом модуле 11 (j=1) 0-го каскада входная группа DG1 имеет разрядность два К(0, 1)=2, поэтому в первом модуле содержится два элемента 2И с инверсным входом, выходы которых передаются на выходы каскада и внутреннюю шину SB1 и имеют разрядность К(1, 1)=2. Во втором модуле 12 (j=2) 0-го каскада разрядности данных без сдвига К(0, 2)=2 и со сдвигом К(0, 1)=2 равны между собой, поэтому второй модуль 12 0-го каскада содержит два элемента 2И с инверсным входом, два элемента 2И и два элемента 2ИЛИ, а также разрядность выходов каскада передаваемых на внутреннюю шину SB1 равна двум К(1, 2)=2. В третьем модуле 13 (j=3) 0-го каскада разрядность группы данных без сдвига равна трем К(0, 3)=3, а разрядность группы данных со сдвигом равна двум К(0, 2)=2, поэтому третий модуль 13 содержит три элемента 2И с инверсным входом, два элемента 2И и два элемента 2ИЛИ - равное минимальному значению разрядности (min(К(0, 3), К(0, 2)))=2. Выходная разрядность третьего модуля 13 0-го каскада передаваемых на внутреннюю шину SB1 равна трем К(1, 3)=3 - максимальное значение разрядности входных групп модуля (max(К(0, 3), К(0, 2)))=3. При этом на выходы двух младших разрядов третьего модуля 13 (j=3) передаются значения с выходов двух элементов 2ИЛИ, а на третий выход передается значение с выхода третьего элемента 2И с инверсным входом. В четвертом модуле 14 (j=4) 0-го каскада разрядность группы данных без сдвига равна двум К(0, 4)=2, а разрядность группы данных со сдвигом равна трем К(0, 3)=3, поэтому четвертый модуль 14 содержит два элемента 2И с инверсным входом, три элемента 2И и два элемента 2ИЛИ - равное минимальному значению разрядности (min(К(0, 4), К(0, 3)))=2. Выходная разрядность четвертого модуля 14 0-го каскада передаваемых на внутреннюю шину SB1 равна трем К(1, 4)=3 - максимальное значение разрядности входных групп модуля (max(К(0, 4), К(0, 3)))=3. При этом на выходы двух младших разрядов четвертого модуля 14 (j=4) передаются значения с выходов двух элементов 2ИЛИ, а на третий выход передается значение с выхода третьего элемента 2И. В пятом модуле 15 (j=5) 0-го каскада содержится один элемент 2И с инверсным входом, два элемента 2И и один элемент 2ИЛИ - равен минимальному значению разрядности (min(К(0, 5), К(0, 4)))=1. Выходная разрядность пятого модуля 15 0-го каскада передаваемых на внутреннюю шину SB1 равна двум К(1, 5)=2 - максимальное значение разрядности входных групп модуля (max(К(0, 5), К(0, 4)))=2. В шестом модуле 16 (j=6) 0-го каскада содержится только один элемент 2И, выход которого передается на выход модуля и на внутреннюю шину SB1 К(1, 6)=1. Таким образом, в 0-м каскаде содержится 27 элементов, в т.ч. десять элементов 2И с инверсным входом, десять элементов 2И и семь элементов 2ИЛИ, а разрядность выходов шести групп (модулей) составляет 13 разрядов.

Далее в первом каскаде может выполниться сдвиг на 21 групп или передача входных групп с 0-го каскада без сдвига в зависимости от значения разряда V1 внешних входов задания количества сдвигов. В первом каскаде содержится 33 элемента (см. таблицу 4), а разрядность выходов восьми групп (модулей) составляет 19 разрядов. Аналогично далее во втором каскаде содержится 45 элементов (см. таблицу 4), а разрядность выходов двенадцати групп (модулей) составляет 31 разряд, которые передаются на выходы двенадцати внешних выходных групп QG1, QG2, …, QG12) с соответствующими разрядностями К(3, 1), К(3, 2), …, К(3, 12).

Таким образом, в устройстве можно выполнять сдвиги N групп входных данных различной разрядности на величину сдвига в диапазоне от 0 до L групп.

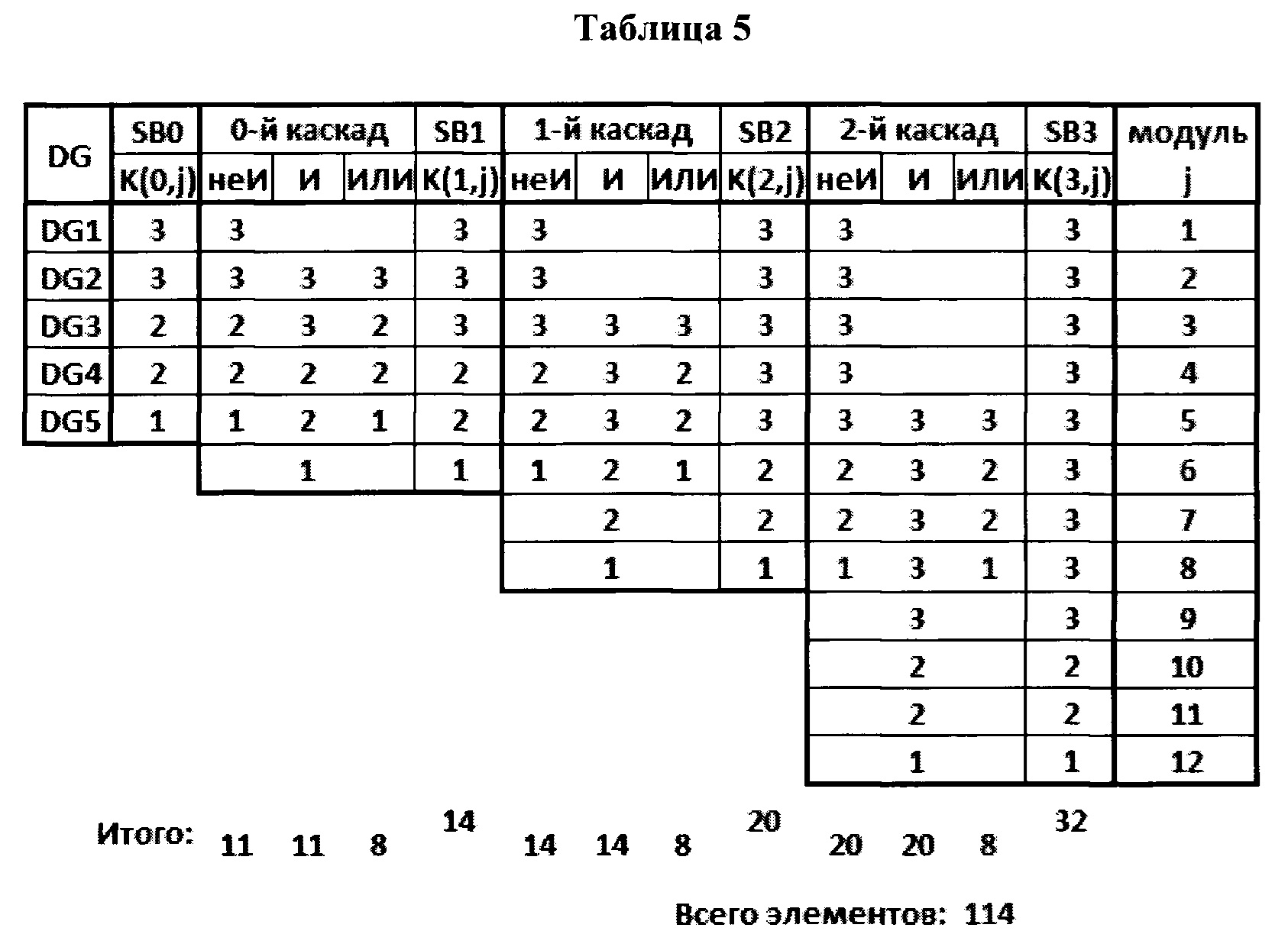

В предлагаемом устройстве для сдвига пяти N=5 групп входных данных DG1, DG2, …, DG5 с заданной разрядностью групп W1=2, W2=2, W3=3, W4=2, W5=1 при величине сдвига групп от 0 до L=7 требуется 105 элементов (см. таблицу 4). При реализации устройства для сдвига данных пяти групп и задания разрядности групп, равной максимальному количеству разрядов в группах, w=W3=3 для всех групп необходимо 150 элементов (см. расчеты в таблице 3) и общая разрядность выходных групп составляет 36. Таким образом, в предлагаемом устройстве для реализации сдвига пяти N=5 групп входных данных DG1, DG2, …, DG5 с заданной разрядностью групп W1=2, W2=2, W3=3, W4=2, W5=1 необходимо на 30% меньше аппаратных средств. Аналогично в таблице 5 приведены распределения элементов и разрядность групп по каскадам и модулям элементов для пяти N=5 групп входных данных DG1, DG2, DG5 с заданной разрядностью групп W1=3, W2=3, W3=3, W4=2, W5=1 при величине сдвига групп от 0 до L=7. Общее количество элементов 114, а общая разрядность выходных групп 32, т.е. в предлагаемом устройстве необходимо на 24% меньше аппаратных средств. Следовательно, в предлагаемом устройстве требуется меньше аппаратных средств для сдвига групп данных.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство сдвига групп данных обладает регулярностью узлов и связей, и соответствует заявляемому техническому результату - расширение функциональных возможностей, в части возможности сдвига групп двоичных данных различной разрядности без потери выдвигаемых разрядов, и снижение аппаратных затрат.

Реферат

Изобретение относится к области вычислительной техники и может быть использовано в процессорах обработки сигналов и процессорах общего назначения, устройствах преобразования информации, кодирования и декодирования данных, устройствах криптографии. Техническим результатом является возможность сдвига групп двоичных данных различной разрядности без потери выдвигаемых разрядов и снижение аппаратных затрат. Устройство содержит N групп внешних входных данных DG1, DG2, …, DGN с разрядностью W1, W2, …, WN соответственно, U разрядов внешних входов задания значения количества сдвигов V0, V1, …, V(U-1) на величину сдвига групп от 0 до L, где U=[logL]+1 (меньшее целое), (N+L) групп внешних выходных данных QG1, QG2, …, QG(N+L), U каскадов модулей элементов с 0-го по (U-1), каждый i-й каскад из которых, где i=0, 1, …, (U-1), содержит по (N+2-1) модулей элементов, объединенных в три секции, (U+1) внутренних шин сдвига SB0, SB1, …, SBU с разрядностью групп K(i, j), где j=1, 2, …, (N+2-1) - номер модуля в каскаде, причем первые секции каскадов состоят из модулей содержащих группы элементов 2И со вторым инверсным входом, вторые секции каскадов состоят из модулей, содержащих группы элементов 2И со вторым инверсным входом, элементов 2И и элементов 2ИЛИ, а третьи секции каскадов состоят из модулей, содержащих группы элементов 2И. 1 ил., 5 табл.

Формула

Документы, цитированные в отчёте о поиске

Устройство сдвига

Комментарии