Устройство сдвига - RU2613533C1

Код документа: RU2613533C1

Чертежи

Описание

Изобретение относится к области вычислительной техники и может быть использовано в процессорах обработки сигналов и процессорах общего назначения, устройствах кодирования и декодирования данных, устройствах криптографии.

Известно устройство управляемого циклического сдвига (RU №2419174 C1, МПК G11C 19/00, заявлено 14.09.2009, опубликовано 20.05.2011, Бюл. №14), содержащее N входов данных, N выходов данных, M≤log2N битовых входов управляющего кода и входа тактовых импульсов, входного регистра данных с N входами данных, образующими входы данных устройства, входом тактовых импульсов, электрически соединенным с входом тактовых импульсов устройства, при этом входной регистр N выходами данных электрически соединен с входами коммутационной матрицы, образованной переключателями, расположенными по N линиям и М уровням и имеющими битовый вход управляющего сигнала, первый и второй входы данных и выход данных.

Недостатком данного устройства является то, что циклический сдвиг выполняется только в одну сторону старших разрядов, устройство не может выполнять логические сдвиги влево и вправо и величина сдвига может принимать значение в диапазоне от 0 до N-1.

Известно устройство управляемого циклического сдвига и способ циклического сдвига (RU №2480905 C2, МПК Н03M 13/19, заявлено 08.10.2009, опубликовано 27.04.2013, Бюл. №12), в котором описано устройство для сдвига N разрядных входных данных в сторону старших разрядов на величину сдвига от 0 до N-1, задаваемую K разрядами, где K≤log2N, содержит селекторы с двумя входами, одним выходом и вводом управления, причем селекторы объединены в K последовательно расположенных ступеней и управляемых соответствующим разрядом кода величины сдвига, причем выходы предыдущей ступени являются входами следующей ступени.

Недостатком данного устройства является то, что циклический сдвиг выполняется только в одну сторону старших разрядов, устройство не может выполнять логические сдвиги влево и вправо и величина сдвига может принимать значение в диапазоне от 0 до N-1.

Известно устройство Circuit for rotating, left shifting, or right shifting bits (US 5978822 (А), МПК G06F 5/01, G06F 7/76, заявлено 29.12.1995, опубликовано 02.11.1999), в котором описано устройство для выполнения логических, циклических и арифметических сдвигов входных данных влево и вправо на заданное количество разрядов. Устройство содержит матрицу мультиплексоров сдвига только в одну сторону - влево старших разрядов, мультиплексор передачи входных данных в прямом или в «перевернутом» обратном порядке разрядов, мультиплексор передачи разрядов кода величины сдвига или их инверсию, выходы которого управляют матрицей мультиплексоров, выходной мультиплексор передачи сдвинутых данных в прямом порядке разрядов или в «перевернутом» обратном порядке разрядов со сдвигом на один разряд.

Недостатком данного устройства является низкое быстродействие, так как входные данные, кроме матрицы мультиплексоров, дополнительно проходят через мультиплексор передачи входных данных и выходной мультиплексор.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятое за прототип устройство Fast conversion two's complement encoded shift value for a barrel shifter (US 5948050 (А), МПК G06F 5/01, заявлено 19.12.1996, опубликовано 07.09.1999), в котором описано устройство для выполнения циклических или логических сдвигов влево или вправо N разрядных входных данных на величину сдвига в диапазоне от 0 до N-1 разряда, который задается М разрядами, где M=log2N. Устройство сдвига содержит N разрядные входные данные, N разрядные выходные данные, М разрядов задания значения количества сдвигов, двунаправленную матрицу сдвига размерностью N x N, группу из M элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, дешифратор направления сдвига, дешифратор и мультиплексор количества и направления сдвига.

Недостатками данного устройства является большой объем оборудования и низкое быстродействие, а также невозможность выполнения сдвигов на N и более N разрядов.

Техническим результатом предлагаемого устройства является увеличение быстродействия, а также расширение функциональных возможностей в части возможности задания величины логических сдвигов в диапазоне от 0 до N разрядов и более N разрядов.

Указанный технический результат при осуществлении изобретения достигается тем, что в устройство сдвига, содержащее N разрядов внешних входных данных D0, D1, …, D(N-1), N разрядов выходных данных Y0, Y0, …, Y(N-1), двунаправленную матрицу сдвига размерностью NxM, где M≤log2N, группу из (M-1) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8, входящих в блок модификации количества сдвигов 1, V разрядов задания значения количества сдвигов K0, K1, …, K(V-1), где V≥M, причем входы задания количества сдвигов, начиная с первого входа К1 до входа K(М-1), соединены со вторыми входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8,

дополнительно введены блок управления направлением сдвига 2, блок формирования флага нулевого результата 3, третий элемент ИЛИ 19 и четыре внешних управляющих входа задания циклического сдвига вправо SRC, циклического сдвига влево SLC, логического сдвига вправо SRL и логического сдвига влево SLL,

причем внешние входы циклического сдвига вправо SRC и циклического сдвига влево SLC соединены с входами третьего элемента ИЛИ 19, выход которого является входом управления циклическим сдвигом RLC,

причем матрица сдвига содержит М каскадов, содержащих группы элементов 2И-2И-2И-3ИЛИ 4 и 2И-2И-2ИЛИ 5,

блок модификации количества сдвигов 1 содержит группу из (М-2) элементов ИЛИ 6, первую группу из (М-1) элементов И 7,

блок управления направлением сдвига 2 содержит вторую группу из (М-1) элементов И 9, группу из (М-1) элементов И 10 с входом запрета, группу из (М-1) элементов НЕ 11, третью группу из (М-1) элементов И 12,

блок формирования флага нулевого результата 3 содержит первый 13, второй 14 и третий 15 элементы И с входом запрета, первый 16 и второй 17 элементы ИЛИ и элемент И-НЕ 18,

причем в матрице сдвигов с нулевого по (М-2)-й каскады содержатся по три группы элементов, причем в каждом из них первые группы содержат по 2i элементов 2И-2И-2И-3ИЛИ 4, где i=0, 1, …, (M-2) - номер каскада, вторые группы содержат по (N-2i+1) элементов 2И-2И-2И-3ИЛИ 4, третьи группы содержат по 2i элементов 2И-2И-2ИЛИ 5, а выходы элементов этих групп образуют соответствующие выходы каскадов и соединены с входами последующих каскадов с первого по (М-1)-й каскад, а (M-1)-й каскад матрицы сдвигов содержит две группы по N/2 элементов 2И-2И-2ИЛИ 5, выходы которых являются соответствующими N разрядами выходных данных Y0, Y0, …, Y(N-1), N разрядов внешних входных данных D0, D1, …, D(N-1) являются соответствующими входами нулевого каскада матрицы сдвига,

причем в блоке модификации количества сдвигов 1 вторые входы элементов ИЛИ 6 группы из (М-2) элементов соединены с соответствующими разрядами входов задания количества сдвигов, начиная с первого K1 до K(М-2) входов, а первые входы элементов ИЛИ 6, начиная со второго до последнего (М-2), соединены с соответствующими выходами предыдущих элементов ИЛИ 6, начиная с первого до предпоследнего (М-3), а первый выход первого элемента ИЛИ 6 соединен с нулевым входом K0 входов задания количества сдвигов, первые входы всех элементов И 7 группы из (М-1) элементов соединены между собой и с входом задания циклического сдвига вправо SRC, второй вход первого элемента И 7 соединен с нулевым входом K0 входов задания количества сдвигов, а вторые входы элементов И 7, начиная со второго до последнего (М-1), соединены с соответствующими выходами элементов ИЛИ 6 группы из (М-2) элементов, начиная с первого элемента ИЛИ 6, выходы элементов И 7 группы из (М-1) элементов соединены с соответствующими первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8 группы из (М-1) элементов, выходы которых являются (М-1) выходами DK1, DK2, …, DK(M-1) блока модификации количества сдвигов 1,

причем в блоке управления направлением сдвига 2 внешний вход задания логического сдвига вправо SRL соединен с первыми входами элементов И 9 группы из (М-1) элементов и входом запрета элементов И 10 с входом запрета группы из (М-1) элементов, а второй вход первого элемента И 9 группы из (М-1) элементов соединен со вторым входом первого элемента И 10 с входом запрета группы из (М-1) элементов соединен с входом первого элемента НЕ 11 группы из (М-1) элементов и соединен с нулевым входом K0 входов задания количества сдвигов, а вторые входы элементов И 9, вторые входы элементов И 10, вход элемента НЕ 11 и вторые входы элементов И 12 соответствующих групп из (М-1) элементов, начиная со второго до последнего (М-1) элементов, соединены между собой и с соответствующими выходами блока модификации количества сдвигов 1, начиная с первого до предпоследнего (М-2) выхода DK1, DK2, DK(M-2), первые входы элементов И 12 группы из (М-1) элементов соединены между собой и соединены с выходом третьего элемента ИЛИ 19,

выходы элементов И 9 группы из (М-1) элементов являются первой группой из (М-1) выходов задания сдвига вправо R0, R1, …, R(M-2), выходы элементов И 10 с входом запрета группы из (М-1) элементов являются второй группой из (М-1) выходов задания сдвига влево L0, L1, …, L(M-2), выходы элементов НЕ 11 группы из (М-1) элементов являются третьей группой из (М-1) выходов передачи данных без сдвига W0, W1, …, W(M-2), выходы элементов И 12 группы из (М-1) элементов являются четвертой группой из (М-1) выходов задания циклического сдвига влево LC0, LC1, …, LC(M-2),

причем в блоке формирования флага нулевого результата 3 входы первого элемента ИЛИ 16 соединены соответственно с внешними входами задания количества сдвигов, начиная с М-го входа КМ до последнего входа K(V-1), а входы второго элемента ИЛИ 17 соединены с внешними входами задания логического сдвига влево SLL и логического сдвига вправо SRL, выходы первого 16 и второго 17 элементов ИЛИ соединены с входами элемента И-НЕ 18, выход которого является флагом нулевого результата NFZ и соединен с третьими входами первого 13 и второго 14 элементов И с входом запрета и со вторым входом третьего 15 элемента И с входом запрета, вторые входы первого 13 и второго 14 элементов И с входом запрета и первый вход запрета третьего 15 элемента И с входом запрета соединены между собой и соединены с выходом DK(M-l) последнего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 группы из (М-1) элементов из блока модификации количества сдвигов 1, первый вход запрета первого элемента И 13 с входом запрета соединен с внешним входом задания логического сдвига вправо SRL, а первый вход запрета второго элемента И 14 с входом запрета соединен с внешним входом задания логического сдвига влево SLL,

выход первого 13 элемента И с входом запрета является первым выходом задания сдвига влево L(M-1) в (М-1)-й каскад матрицы сдвигов, выход второго 14 элемента И с входом запрета является вторым выходом задания сдвига вправо R(M-1) в (М-1)-й каскад матрицы сдвигов, выход третьего 15 элемента И с входом запрета является третьим выходом задания передачи данных без сдвига W(M-1) в (М-1)-й каскад матрицы сдвигов,

причем в матрице сдвигов в каждом i-м каскаде, начиная с нулевого по (М-2)-й каскад, первые входы элементов всех групп соединены между собой и подключены к соответствующему выходу третьей группы передачи данных без сдвига W0, W1, …, W(M-2) блока управления направлением сдвига 2, вторые входы элементов всех групп соединены с соответствующим j-м входом каскада, где j=0, 1, (N-1), третьи входы первых групп элементов 2И-2И-2И-3ИЛИ 4 соединены между собой и подключены к соответствующему выходу четвертой группы задания циклического сдвига влево LC0, LC1, …, LC(M-2) блока управления направлением сдвига 2, третьи входы вторых групп элементов 2И-2И-2И-3ИЛИ 4 и третьих групп 2И-2И-2ИЛИ 5 соединены между собой и подключены к соответствующему выходу второй группы задания сдвига влево L0, L1, …, L(M-2) блока управления направлением сдвига 2, четвертые входы всех групп элементов соединены с соответствующими (N-2i+j)mod(N) входами каскада, где mod(N) - остаток от деления (N-2i+j) на N, пятые входы первых групп элементов 2И-2И-2И-3ИЛИ 4 и вторых групп элементов 2И-2И-2И-3ИЛИ 4 соединены между собой и подключены к соответствующему выходу первой группы задания сдвига вправо R0, R1, …, R(M-2), а шестые входы первых групп элементов 2И-2И-2И-3ИЛИ 4 и вторых групп элементов 2И-2И-2И-3ИЛИ 4 соединены с соответствующими (2i+u) входами каскада, где u=0, 1, …, (N-1-2i),

а в (М-1)-м каскаде матрицы сдвигов первые входы элементов первой и второй групп элементов 2И-2И-2ИЛИ 5 соединены между собой и подключены к соответствующему выходу передачи данных без сдвига W(M-1) третьего элемента И 15 с входом запрета, а вторые входы групп элементов соединены с соответствующим j-м входом каскада, где j=0, 1, …, (N-1), третьи входы первой группы элементов 2И-2И-2ИЛИ 5 соединены между собой и подключены к соответствующему выходу задания сдвига вправо R(M-1) второго элемента И 14 с входом запрета, а третьи входы второй группы элементов 2И-2И-2ИЛИ 5 соединены между собой и подключены к соответствующему выходу задания сдвига влево L(M-1) первого элемента И 13 с входом запрета, четвертые входы первой и второй групп элементов 2И-2И-2ИЛИ 5 соединены с соответствующими (2M-1+j)mod(N) входами каскада, где mod(N) - остаток от деления (2M-1+j) на N.

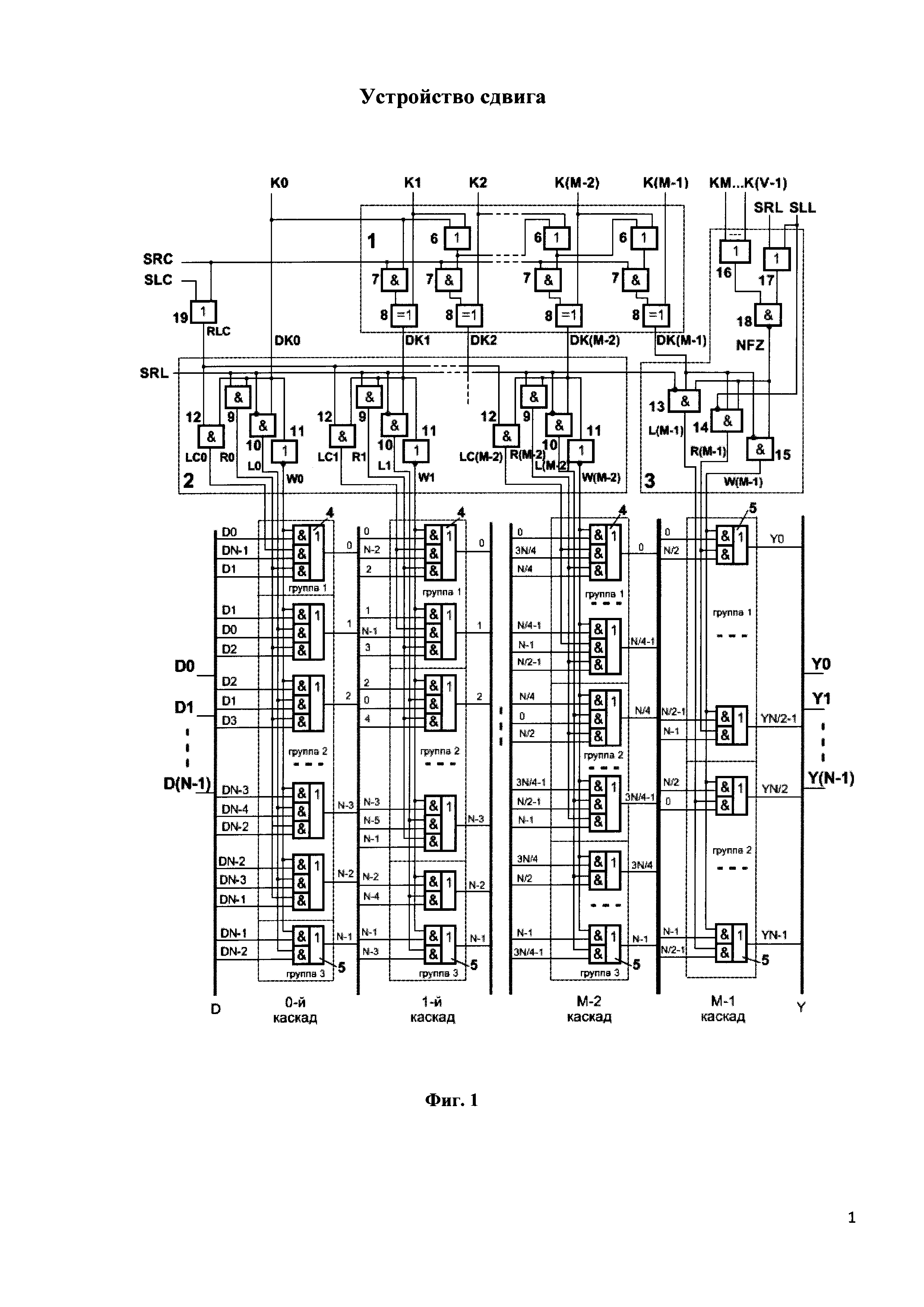

На фиг. 1 представлена схема предлагаемого устройства сдвига.

На фиг. 1 введены следующие обозначения:

D0, D1, …, D(N-1) - N разрядов внешних входных данных,

Y0, Y0, …, Y(N-1) - N разрядов выходных данных,

K0, K1, …, K(V-1) - V разрядов задания значения количества сдвигов,

SRC - внешний управляющий вход задания циклического сдвига вправо,

SLC - внешний управляющий вход задания циклического сдвига влево,

SRL - внешний управляющий вход задания логического сдвига вправо,

SLL - внешний управляющий вход задания циклического сдвига влево,

M≤log2N - количество каскадов в матрице сдвигов,

1 - блок модификации количества сдвигов,

2 - блок управления направлением сдвига,

3 - блок формирования флага нулевого результата,

4 - элементы 2И-2И-2И-3ИЛИ,

5 - элементы 2И-2И-2ИЛИ,

6 - группа из (М-2) элементов ИЛИ,

7 - первая группа из (М-1) элементов И,

8 - группа из (М-1) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ,

9 - вторая группа из (М-1) элементов И,

10 - группа из (М-1) элементов И с входом запрета,

11 - группа из (М-1) элементов НЕ,

12 - третья группа из (М-1) элементов И,

13 - первый элемент И с входом запрета,

14 - второй элемент И с входом запрета,

15 - третий элемент И с входом запрета,

16 - первый элемент ИЛИ,

17 - второй элемент ИЛИ,

18 - элемент И-НЕ,

19 - третий элемент ИЛИ,

DK0, DK1, …, DK(M-1) - модифицированные разряды величины кода сдвига, RLC - вход управления циклическим сдвигом,

R0, R1, …, R(M-2) - первая группа из (М-1) выходов задания сдвига вправо,

L0, L1, …, (M-2) - вторая группа из (М-1) выходов задания сдвига влево,

W0, W1, …, W(M-2) - третья группа из (М-1) выходов передачи данных без сдвига,

LC0, LC1, …, LC(M-2) - четвертая группа из (М-1) выходов задания циклического сдвига влево,

NFZ - флаг нулевого результата.

Устройство имеет N разрядов внешних входных данных D0, D1, …, D(N-1) и N разрядов выходных данных Y0, Y0, …, Y(N-1), содержит двунаправленную матрицу сдвига размерностью NxM, где M≤log2N, V разрядов задания значения количества сдвигов K0, K1, …, K(V-1), где V>M, блок модификации количества сдвигов 1, блок управления направлением сдвига 2, блок формирования флага нулевого результата 3, третий элемент ИЛИ 19 и четыре внешних управляющих входа задания циклического сдвига вправо SRC, циклического сдвига влево SLC, логического сдвига вправо SRL и логического сдвига влево SLL.

Матрица сдвига содержит М каскадов, содержащих группы элементов 2И-2И-2И-3ИЛИ 4 и 2И-2И-2ИЛИ 5.

Блок модификации количества сдвигов 1 содержит группу из (М-2) элементов ИЛИ 6, первую группу из (М-1) элементов И 7 и группу из (М-1) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8.

Блок управления направлением сдвига 2 содержит вторую группу из (М-1) элементов И 9, группу из (М-1) элементов И 10 с входом запрета, группу из (М-1) элементов НЕ 11 и третью группу из (М-1) элементов И 12.

Блок формирования флага нулевого результата 3 содержит первый 13, второй 14 и третий 15 элементы И с входом запрета, первый 16 и второй 17 элементы ИЛИ и элемент И-НЕ 18.

Внешние входы циклического сдвига вправо SRC и циклического сдвига влево SLC соединены с входами третьего элемента ИЛИ 19, выход которого является входом управления циклическим сдвигом RLC.

В матрице сдвигов с нулевого по (М-2)-й каскады содержат по три группы элементов, причем в каждом из них первые группы содержат по 2i элементов 2И-2И-2И-3ИЛИ 4, где i=0, 1, …, (М-2) - номер каскада, вторые группы содержат по (N-2i+1) элементов 2И-2И-2И-3ИЛИ 4, третьи группы содержат по 2i элементов 2И-2И-2ИЛИ 5, а выходы элементов этих групп образуют соответствующие выходы каскадов и соединены с входами последующих каскадов с первого по (М-1)-й каскад.

(М-1)-й каскад матрицы сдвигов содержит две группы по N/2 элементов 2И-2И-2ИЛИ 5, выходы которых являются соответствующими N разрядами выходных данных Y0, Y0, …, Y(N-1), N разрядов внешних входных данных D0, D1, …, D(N-1) являются соответствующими входами нулевого каскада матрицы сдвига.

В блоке модификации количества сдвигов 1 вторые входы элементов ИЛИ 6 группы из (М-2) элементов соединены с соответствующими разрядами входов задания количества сдвигов, начиная с первого К1 до K(М-2) входов, а первые входы элементов ИЛИ 6, начиная со второго до последнего (М-2), соединены с соответствующими выходами предыдущих элементов ИЛИ 6, начиная с первого до предпоследнего (М-3). Первый выход первого элемента ИЛИ 6 соединен с нулевым входом K0 входов задания количества сдвигов. Первые входы всех элементов И 7 группы из (М-1) элементов соединены между собой и с входом задания циклического сдвига вправо SRC. Второй вход первого элемента И 7 соединен с нулевым входом K0 входов задания количества сдвигов, а вторые входы элементов И 7, начиная со второго до последнего (М-1), соединены с соответствующими выходами элементов ИЛИ 6 группы из (М-2) элементов, начиная с первого элемента ИЛИ 6. Входы задания количества сдвигов, начиная с первого входа К1 до входа К(М-1), соединены со вторыми входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8 группы из (М-1) элементов. Выходы элементов И 7 группы из (М-1) элементов соединены с соответствующими первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8 группы из (М-1) элементов, выходы которых являются (М-1) выходами DK1, …, DK2, DK(M-1) блока модификации количества сдвигов 1.

В блоке управления направлением сдвига 2 внешний вход задания логического сдвига вправо SRL соединен с первыми входами элементов И 9 группы из (М-1) элементов и входом запрета элементов И 10 с входом запрета группы из (М-1) элементов. Второй вход первого элемента И 9 группы из (М-1) элементов соединен со вторым входом первого элемента И 10 с входом запрета, группы из (М-1) элементов, соединен с входом первого элемента НЕ 11 группы из (М-1) элементов и соединен с нулевым входом K0 входов задания количества сдвигов. Вторые входы элементов И 9, вторые входы элементов И 10, вход элемента НЕ 11 и вторые входы элементов И 12 соответствующих групп из (М-1) элементов, начиная со второго до последнего (М-1) элементов, соединены между собой и с соответствующими выходами блока модификации количества сдвигов 1, начиная с первого до предпоследнего (М-2) выхода DK1, DK2, DK(M-2). Первые входы элементов И 12 группы из (М-1) элементов соединены между собой и соединены с выходом третьего элемента ИЛИ 19.

Выходы элементов И 9 группы из (М-1) элементов являются первой группой из (М-1) выходов задания сдвига вправо R0, R1, …, R(M-2), выходы элементов И 10 с входом запрета группы из (М-1) элементов являются второй группой из (М-1) выходов задания сдвига влево L0, L1, …, L(M-2), выходы элементов НЕ 11 группы из (М-1) элементов являются третьей группой из (М-1) выходов передачи данных без сдвига W0, W1, …, W(M-2), выходы элементов И 12 группы из (М-1) элементов являются четвертой группой из (М-1) выходов задания циклического сдвига влево LC0, LC1, …, LC(M-2).

В блоке формирования флага нулевого результата 3 входы первого элемента ИЛИ 16 соединены соответственно с внешними входами задания количества сдвигов, начиная с М-го входа КМ до последнего входа K(V-1), а входы второго элемента ИЛИ 17 соединены с внешними входами задания логического сдвига влево SLL и логического сдвига вправо SRL. Выходы первого 16 и второго 17 элементов ИЛИ соединены с входами элемента И-НЕ 18, выход которого является флагом нулевого результата NFZ и соединен с третьими входами первого 13 и второго 14 элементов И с входом запрета и со вторым входом третьего 15 элемента И с входом запрета. Вторые входы первого 13 и второго 14 элементов И с входом запрета и первый вход запрета третьего 15 элемента И с входом запрета соединены между собой и соединены с выходом DK(M-1) последнего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 группы из (М-1) элементов из блока модификации количества сдвигов 1. Первый вход запрета первого элемента И 13 с входом запрета соединен с внешним входом задания логического сдвига вправо SRL, а первый вход запрета второго элемента И 14 с входом запрета соединен с внешним входом задания логического сдвига влево SLL.

Выход первого 13 элемента И с входом запрета является первым выходом задания сдвига влево L(M-1) в (М-1)-й каскад матрицы сдвигов, выход второго 14 элемента И с входом запрета является вторым выходом задания сдвига вправо R(M-1) в (М-1)-й каскад матрицы сдвигов, выход третьего 15 элемента И с входом запрета является третьим выходом задания передачи данных без сдвига W(M-1) в (М-1)-й каскад матрицы сдвигов.

В матрице сдвигов в каждом i-м каскаде, начиная с нулевого по (М-2)-й каскад, первые входы элементов всех групп соединены между собой и подключены к соответствующему выходу третьей группы передачи данных без сдвига W0, W1, …, W(M-2) блока управления направлением сдвига 2. Вторые входы элементов всех групп соединены с соответствующим j-м входом каскада, где j=0, 1, …, (N-1). Третьи входы первых групп элементов 2И-2И-2И-3ИЛИ 4 соединены между собой и подключены к соответствующему выходу четвертой группы задания циклического сдвига влево LC0, LC1, …, LC(M-2) блока управления направлением сдвига 2. Третьи входы вторых групп элементов 2И-2И-2И-3ИЛИ 4 и третьих групп 2И-2И-2ИЛИ 5 соединены между собой и подключены к соответствующему выходу второй группы задания сдвига влево L0, L1, …, L(М-2) блока управления направлением сдвига 2. Четвертые входы всех групп элементов соединены с соответствующими (N-2i+j)mod(N) входами каскада, где mod(N) - остаток от деления (N-2i+j) на N. Пятые входы первых групп элементов 2И-2И-2И-3ИЛИ 4 и вторых групп элементов 2И-2И-2И-3ИЛИ 4 соединены между собой и подключены к соответствующему выходу первой группы задания сдвига вправо R0, R1, …, R(M-2), а шестые входы первых групп элементов 2И-2И-2И-3ИЛИ 4 и вторых групп элементов 2И-2И-2И-3ИЛИ 4 соединены с соответствующими (2i+u) входами каскада, где u=0, 1, …, (N-1-2i).

В (М-1)-м каскаде матрицы сдвигов первые входы элементов первой и второй групп элементов 2И-2И-2ИЛИ 5 соединены между собой и подключены к соответствующему выходу передачи данных без сдвига W(M-1) третьего элемента И 15 с входом запрета. Вторые входы групп элементов соединены с соответствующим j-м входом каскада, где j=0, 1, (N-1). Третьи входы первой группы элементов 2И-2И-2ИЛИ 5 соединены между собой и подключены к соответствующему выходу задания сдвига вправо R(M-1) второго элемента И 14 с входом запрета, а третьи входы второй группы элементов 2И-2И-2ИЛИ 5 соединены между собой и подключены к соответствующему выходу задания сдвига влево L(M-1) первого элемента И 13 с входом запрета. Четвертые входы первой и второй групп элементов 2И-2И-2ИЛИ 5 соединены с соответствующими (2M-1+j)mod(N) входами каскада, где mod(N) - остаток от деления (2M-1+j) на N.

Принцип работы устройства состоит в следующем.

Устройство предназначено для сдвига влево или вправо N разрядных входных данных D0, D1, …, D(N-1) на величину сдвига в диапазоне от 0 до N и более N разрядов. Входные данные являются целыми числами без знака в диапазоне от 0 до 2N-1. Во входных данных разряд D0 является младшим правым разрядом, а разряд D(N-1) является старшим левым разрядом. Сдвиг данных осуществляется в двунаправленной матрице сдвигов размерностью NxM, где M=log2N, содержащей М каскадов из групп элементов 2И-2И-2И-3ИЛИ 4 и 2И-2И-2ИЛИ 5. Величина сдвига K задается V разрядами задания значения количества сдвигов K0, K1, … K(V-1), где V≥M.

Направление и вид сдвига задается управляющими входами:

SRC - вход задания циклического сдвига вправо,

SLC - вход задания циклического сдвига влево,

SRL - вход задания логического сдвига вправо,

SLL - вход задания циклического сдвига влево.

При логическом сдвиге влево SLL все биты разрядов входного слова сдвигаются влево в сторону старших разрядов на величину сдвига К. При этом К старших разрядов выдвигаются и теряются, а К младших разрядов заполняются нулями. Логический сдвиг влево может быть использован для умножения целых чисел без знака на 2К.

При логическом сдвиге вправо SRL все биты разрядов входного слова сдвигаются вправо в сторону младших разрядов на величину сдвига К. При этом К младших разрядов выдвигаются и теряются, а К старших разрядов заполняются нулями. Логический сдвиг вправо может быть использован для деления целых чисел без знака на 2К.

При циклических сдвигах осуществляется кольцевая передача бит между старшими и младшими разрядами.

При циклическом сдвиге влево SLC все биты разрядов входного слова сдвигаются влево в сторону старших разрядов на величину сдвига К. При этом К старших разрядов выдвигаются и передаются в К младших разрядов.

При циклическом сдвиге вправо SRC все биты разрядов входного слова сдвигаются вправо в сторону младших разрядов на величину сдвига К. При этом К младших разрядов выдвигаются и передаются в К старших разрядов.

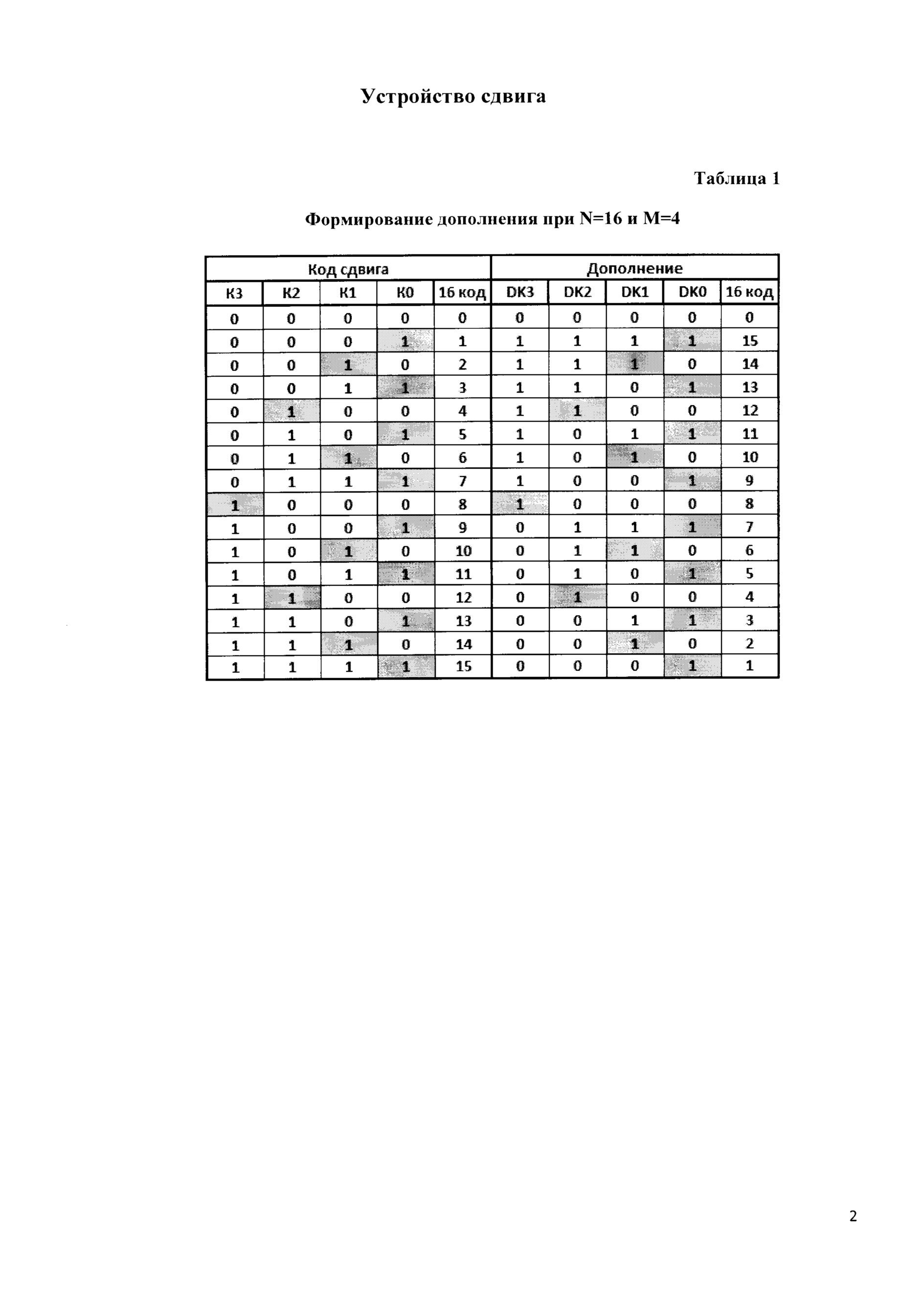

Для сокращения аппаратных затрат циклические сдвиги как вправо SRC, так и влево SLC выполняются как циклический сдвиг влево. При этом для циклического сдвига вправо SRC величина сдвига К преобразуется в разряды DKi дополнения до N в блоке модификации количества сдвигов 1. В таблице 1 приведен пример формирования дополнения при N=16 и М=4.

Дополнение получается после изменения всех старших единиц на нули, кроме последней младшей единицы, и всех старших нулей на единицы до последней младшей единицы, т.е. выполняется инверсия старших разрядов до последней младшей единицы (в таблице 1 младшая единица, значение которой сохраняется, выделена во входных данных и в дополнении). При этом самый младший разряд K0 всегда остается неизменным (таблица 1).

Анализ единиц начинается с младшего разряда K0 величины сдвига К в группе из (М-2) элементов ИЛИ 6. При этом выявление единицы в одном из младших разрядов передается последовательно на все старшие разряды и при задании циклического сдвига вправо SRC через группу из (М-1) элементов И 7 поступает на группу из (М-1) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8, на которых проводится инверсия битов разрядов. В других видах сдвигов, кроме циклического сдвига вправо SRC, на выходах группы из (М-1) элементов И 7 формируется нулевой сигнал, поэтому через группу из (М-1) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8, который можно рассматривать как элемент «управляемый инвертор», передается величина сдвига без преобразования.

В матрице сдвигов в каждом i-м каскаде, где i=0, 1, …, (М-2) - номер каскада, выполняется передача данных без сдвига или со сдвигом на 2i разрядов влево или вправо и заполнением сдвигаемых разрядов нулями при логическом сдвиге или выдвигаемыми разрядами при циклическом сдвиге. На входы 0-го каскада поступают входные данные. Далее с выходов предыдущего каскада данные передаются на входы последующего каскада.

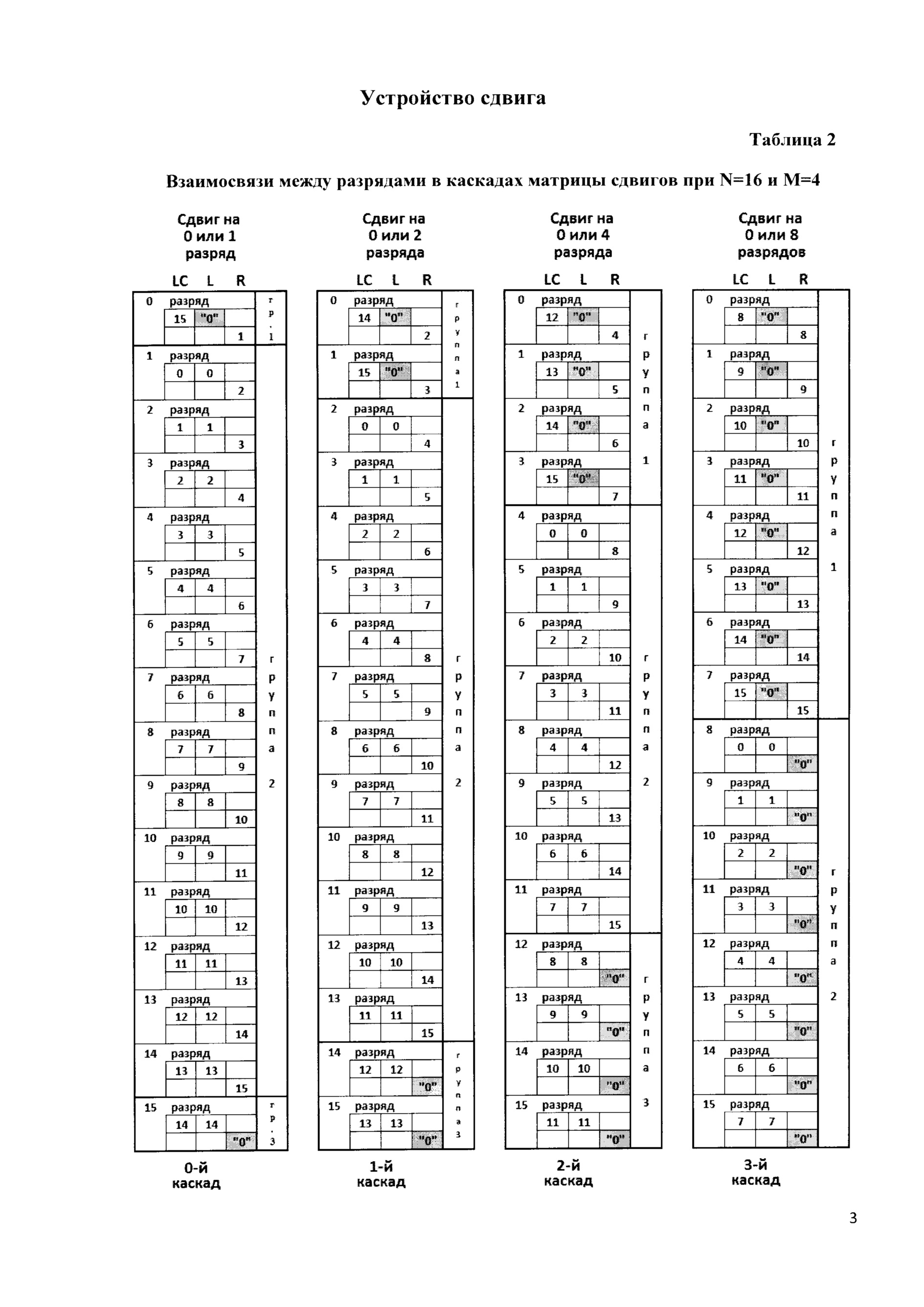

В таблице 2 приведены связи между разрядами для сдвигов 16 разрядных (N=16 и М=3) входных данных D0, D1, …, D15. В таблице 2 в 0-м, 1-ми 2-м каскадах выделены три группы разрядов, в которых отмечены одноименные связи для сдвигов между разрядами. При передаче без сдвига во всех группах передается соответствующий j-й вход каскада, где j=0, 1, …, (N-1).

В каждом i-м каскаде в первых группах, содержащих по 2i элементов 2И-2И-2И-3ИЛИ 4, при логическом сдвиге L в 2i разрядах формируются нулевые значения, при циклическом сдвиге LC передаются 2i выдвигаемых старших разрядов, а при логическом сдвиге вправо R передаются 2i старших разрядов, начиная с 2i-го разряда.

В каждом i-м каскаде во вторых группах, содержащих по (N-2i+1) элементов 2И-2И-2И-3ИЛИ 4, при логическом сдвиге L и циклическом сдвиге влево LC передаются соответствующие (N-2i+j)mod(N) выходы предыдущего каскада, где mod(N) - остаток от деления (N-2i+j) на N, а при логическом сдвиге вправо R передаются соответствующие (2i+u) выходы предыдущего каскада, где u=0, 1, …, (N-1-2i).

В каждом i-м каскаде в третьих группах, содержащих по 2i элементов 2И-2И-2ИЛИ 5, при логическом сдвиге L и циклическом сдвиге влево LC передаются соответствующие (N-2i+j)mod(N) выходы предыдущего каскада, где mod(N) - остаток от деления (N-2i+j) на N, а при логическом сдвиге вправо R формируются в 2i разрядах нулевые значения.

В (М-1)-м каскаде матрицы сдвигов содержится две группы по N/2 элементов 2И-2И-2ИЛИ 5. В первой группе при циклическом сдвиге влево LC и при логическом сдвиге вправо R передаются соответствующие старшие N/2, …, N-1 разряды с выходов предпоследнего (М-2)-го каскада, а при логическом сдвиге влево L в N/2 младших разрядах формируются нулевые значения. Во второй группе при циклическом сдвиге влево LC и при логическом сдвиге влево L передаются соответствующие младшие 0, …, N/2-1 разряды с выходов предпоследнего (М-2)-го каскада, а при логическом сдвиге вправо R в N/2 старших разрядах формируются нулевые значения.

При циклическом сдвиге на K разрядов, когда K≥N, старшие разряды величины сдвига КМ…KV не учитываются.

При логическом сдвиге на K разрядов, когда K≥N, анализируются старшие разряды величины сдвига КМ…KV и при наличии среди них единичных значений в блоке формирования нулевого результата 3 формируется значение флага NFZ=0, по которому на управляющих выходах L(M-1), R(M-1) и W(M-1) формируются нулевые значения, по которым на выходах (M-1)-го каскада матрицы сдвигов, соединенных с N разрядами выходных данных Y0, Y0, …, Y(N-1) устройства, также формируются нулевые значения.

Таким образом, в устройстве можно выполнить циклические и логические сдвиги влево или вправо N разрядных входных данных D0, D1, …, D(N-1) на величину сдвига K в диапазоне от 0 до N разрядов или более чем на N разрядов.

Предлагаемое устройство сдвига работает следующим образом.

На входы устройства подаются N разрядов внешних входных данных D0, D1, …, D(N-1), V разрядов задания значения количества сдвигов K0, K1, …, K(V-1) и на четырех внешних управляющих входах задается направление и вид сдвига: циклический сдвиг вправо SRC, циклический сдвиг влево SLC, логический сдвиг вправо SRL или логический сдвиг влево SLL (единичное значение устанавливается на одном из управляющих входов).

N разрядов внешних входных данных D0, D1, … D(N-1) поступают на нулевой каскад матрицы сдвигов.

На выходы DK0, DK1, …, DK(M-1) блока модификации количества сдвигов 1 передается входное значение битов разрядов количества сдвигов K0, К1, …, К(М-1), где M≤log2N, или модифицированное значение для циклического сдвига вправо SRC, соответствующее дополнению величины сдвига K до N.

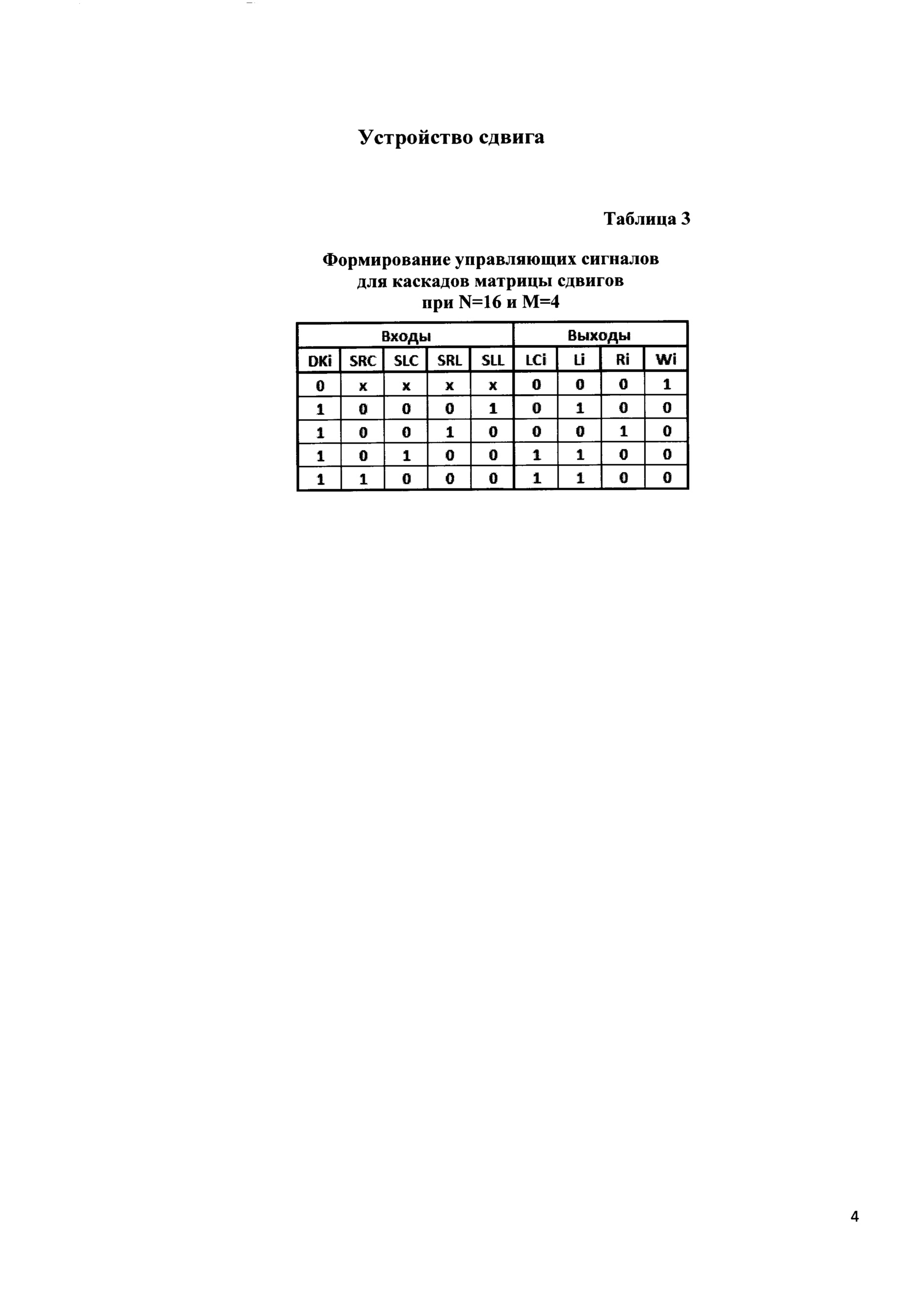

Блок управления направлением сдвига 2 формирует на 0, 1, …, М-2 каскады матрицы сдвигов единичные управляющие сигналы для выполнения логических сдвигов влево L0, L1, …, L(М-2) на выходах группы из (M-1)-го элементов И 10 с входом запрета, или логических сдвигов вправо R0, R1, …, R(M-2) на выходах второй группы из (M-1)-го элемента И 9, или циклического сдвига влево LC0, LC1, …, LC(M-2) на выходах третьей группы из (M-1)-го элемента И 12, или передачи данных без сдвига W0, W1, …, W(M-2) на выходах группы из (M-1)-го элементов НЕ 11 входных данных каскадов. В таблице 3 приведены условия формирования управляющих сигналов в зависимости от внешних сигналов задания направления сдвига SRC, SLC, SRL, SLL и модифицированных значений разрядов DKi величины сдвига.

В блоке формирования флага нулевого результата 3 старшие разряды величины сдвига КМ…KV поступают на первый элемент ИЛИ 16, на выходе которого формируется единичное значение при наличии среди них единичных значений, когда величина сдвига K≥N. На выходе второго элемента ИЛИ 17 формируется единичное значение при наличии единичных сигналов выполнения логического сдвига вправо SRL или влево SLL. При единичных сигналах на выходах первого 16 и второго 17 элементов ИЛИ на выходе элемента И-НЕ 18 формируется нулевое значение флага нулевого результата NFZ=0. По этому сигналу нулевые значения также формируются на управляющих выходах логического сдвига влево L(M-1), логического сдвига вправо R(M-1) и передачи данных без сдвига W(M-1), которые поступают на входы управления последнего (M-1)-го каскада матрицы сдвигов, выходы которого являются N разрядными выходными данными Y0, Y0, …, Y(N-1) устройства, на которых также будут сформированы нулевые значения при K≥N.

При величине сдвига K≤N в М каскадах матрицы сдвигов осуществляется заданный вид сдвига битов N разрядов внешних входных данных D0, D1, …, D(N-1). При этом в 0-м каскаде может выполниться сдвиг на 1 разряд (20) или передача входных данных без сдвига в зависимости от значения младшего модифицированного разряда DK0 величины сдвига. В первом каскаде может выполниться сдвиг на 2 разряда (21) или передача входных данных без сдвига в зависимости от значения первого модифицированного разряда DK1 величины сдвига. Далее в i-м каскаде может выполниться сдвиг на 2i разрядов или передача входных данных без сдвига в зависимости от значения модифицированного разряда DKi величины сдвига. В (М-1)-м каскаде может выполниться сдвиг на N/2 разрядов или передача входных данных без сдвига в зависимости от значения старшего модифицированного разряда DK(M-1) величины сдвига.

Таким образом, в устройстве можно выполнять циклические и логические сдвиги влево или вправо на величину сдвига K в диапазоне от 0 до N разрядов и более чем на N разрядов. При выполнении сдвигов не требуется дополнительных последовательно включаемых блоков аппаратуры для дешифрации и мультиплексирования количества и направления сдвига или входного мультиплексора для передачи входных данных в прямом или в «перевернутом» обратном порядке разрядов и выходного мультиплексора передачи сдвинутых данных в прямом порядке разрядов или в «перевернутом» обратном порядке разрядов со сдвигом на один разряд, а следовательно, устройство обладает большим быстродействием.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство сдвига обладает регулярностью узлов и связей и соответствует заявляемому техническому результату - увеличение быстродействия и расширение функциональных возможностей.

Реферат

Изобретение относится к области вычислительной техники и может быть использовано в процессорах обработки сигналов и процессорах общего назначения, устройствах кодирования и декодирования данных, устройствах криптографии. Технический результат - увеличение быстродействия, обеспечение возможности задания величины логических сдвигов в диапазоне от 0 до N разрядов и более N разрядов. Устройство сдвига содержит двунаправленную матрицу сдвига размерностью NxM, где M=logN, из М каскадов элементов 2И-2И-2И-3ИЛИ и 2И-2И-2ИЛИ, блок модификации количества сдвигов, содержащий группу из (М-2) элементов ИЛИ, первую группу из (М-1) элементов И и группу из (М-1) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блок управления направлением сдвига, содержащий вторую группу из (М-1) элементов И, группу из (М-1) элементов И с входом запрета, группу из (М-1) элементов НЕ и третью группу из (М-1) элементов И, блок формирования флага нулевого результата, содержащий первый, второй и третий элементы И с входом запрета, первый и второй элементы ИЛИ и элемент И-НЕ, четыре управляющих входа задания направления и вида сдвига. 1 ил., 3 табл.

Формула

Документы, цитированные в отчёте о поиске

Устройство циклического сдвига, способ циклического сдвига, устройство декодирования ldpc-кода, телевизионный приемник и приемная система

Комментарии