Триггер, регистр сдвига, схема возбуждения устройства отображения, устройство отображения и панель устройства отображения - RU2507680C2

Код документа: RU2507680C2

Чертежи

Описание

Область техники, к которой относится изобретение

Настоящее изобретение относится к триггеру и к различным схемам возбуждения устройства отображения.

Уровень техники

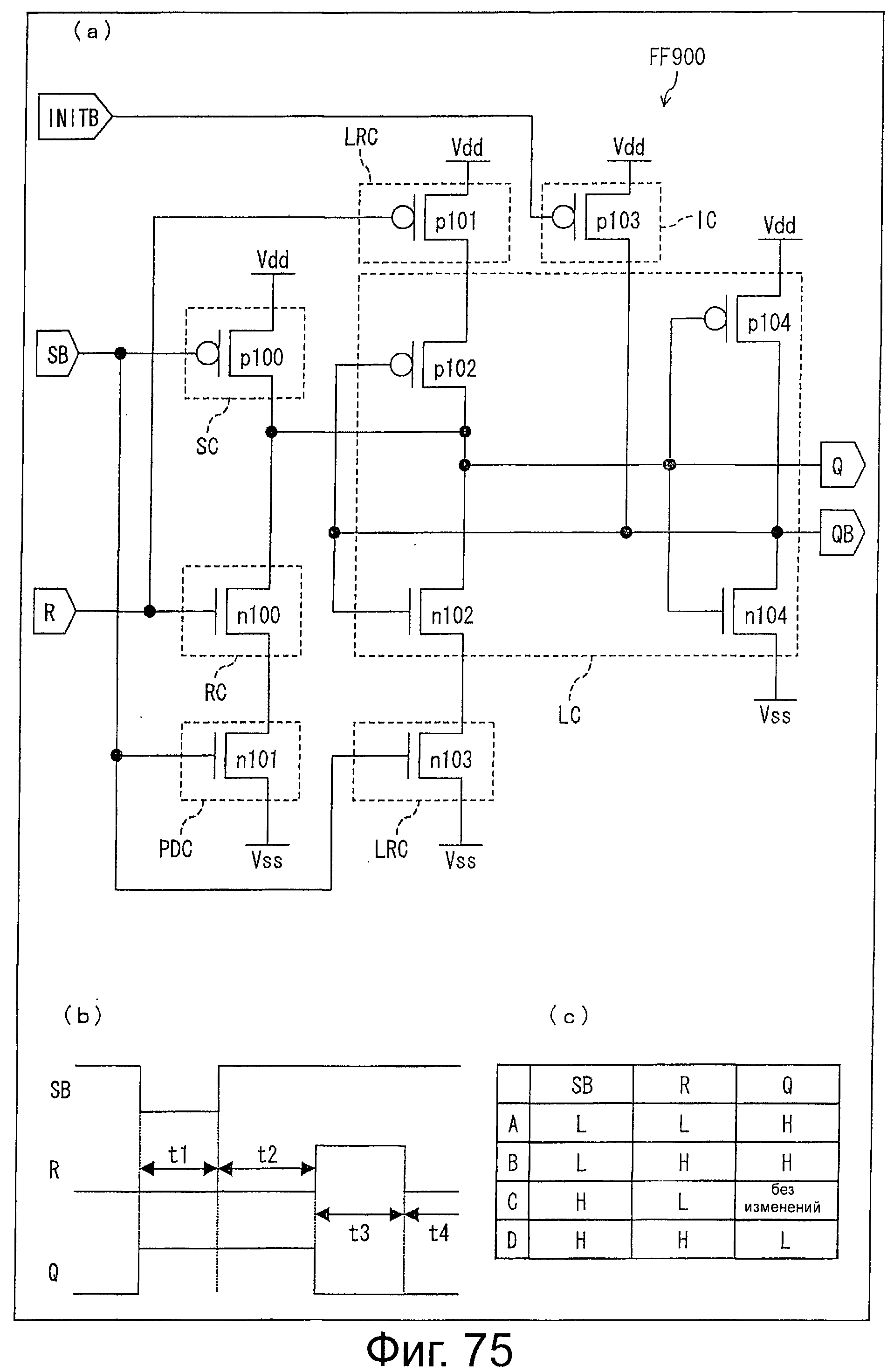

На фиг.75 (а) показана схема известного триггера, используемого в качестве схемы возбуждения затворов для жидкокристаллического устройства отображения или аналогичного устройства. Известный триггер (FF) 900, показанный на фиг.75 (а), включает пять p-канальных транзисторов (р100, р101, р102, р103, р104), пять n-канальных транзисторов (n100, n101, n102, n103, n104), клемму SB инвертированного сигнала установки, клемму R сигнала сброса, выходную клемму Q, клемму QB инвертированного выхода и клемму INITB инвертированного сигнала инициализации. В дальнейшем сигнал, поступающий на клемму SB, будет именоваться "SB-сигнал" (инвертированный сигнал установки), сигнал, поступающий на клемму R, будет именоваться "R-сигнал" (сигнал сброса), сигнал, поступающий на клемму INITB, (инвертированный сигнал инициализации) будет именоваться "INITB-сигнал", сигнал, снимаемый (выходящий) с клеммы Q, (выходной сигнал) будет именоваться "Q-сигнал" и сигнал, снимаемый (выходящий) с клеммы QB, (клеммы инвертированного выхода) будет именоваться "QB-сигнал". Далее, электрический потенциал VDD (источник питания высокого напряжения) будет именоваться "Vdd" и электрический потенциал VSS (источник питания низкого напряжения) будет именоваться "Vss".

Здесь, в схеме триггера FF900 (i) исток транзистора р100 соединен с клеммой VDD (источник питания высокого напряжения), (ii) сток транзистора р100, сток транзистора n100, сток транзистора р102, сток транзистора nl02, затвор транзистора р104, затвор транзистора n104 и клемма Q соединены одно с другими, (hi) исток транзистора n100 и сток транзистора nl01 соединены один с другим и (iv) исток транзистора nl01 соединен с клеммой VSS (источник питания низкого напряжения). Далее, в триггере FF900 (i) исток транзистора р101 соединен с клеммой VDD, (ii) сток транзистора р101 и исток транзистора р102 соединены один с другим, (iii) исток транзистора n102 и сток транзистора n103 соединены один с другим, (iv) исток транзистора n103 соединен с клеммой VSS, (v) исток транзистора p104 соединен с клеммой VDD, (vi) сток транзистора р104 и сток транзистора n104 соединены один с другим и (vii) исток транзистора n104 соединен с клеммой VSS. Кроме того, в триггере FF 900 (i) затвор транзистора р101, затвор транзистора n100 и клемма R соединены одно с другим, (ii) затвор транзистора р100, затвор транзистора n101, затвор транзистора n103 и клемма SB соединены одно с другим, (iii) исток транзистора р103 соединен с клеммой VDD, (iv) затвор транзистора р103 соединен с клеммой INITB и (v) затвор транзистора р102, затвор транзистора n102, сток транзистора р103 и клемма QB соединены одно с другим. В схеме триггера FF900 (i) транзистор р100 составляет схему SC установки, (ii) транзистор n100 составляет схему RC сброса, (iii) транзистор n101 составляет схему PDC определения приоритета, (iv) транзистор р103 составляет схему IC инициализации, (v) транзистор р101 и транзистор n103, соответственно, составляет схемы LRC освобождения защелки и (vi) транзистор р102, транзистор n102, транзистор р104 и транзистор n104 составляют схему LC защелки.

Фиг.75 (b) представляет временную диаграмму, иллюстрирующую работу триггера FF900, и фиг.75 (с) представляет таблицу истинности для триггера FF900.

Когда SB-сигнал активен (=низкий уровень) и R-сигнал неактивен (=высокий уровень) (период t1 времени, показанный на фиг.75 (b)), триггер FF900 работает, как описано ниже. Когда SB-сигнал становится активным (=низкий уровень), транзистор р100 (схема SC установки) отпирается. Это приводит к электрическому соединению клеммы Q с клеммой VDD (источник питания высокого напряжения) через транзистор р100. В результате Q-сигнал становится активным (=высокий уровень). Клемма SB электрически соединена с затвором транзистора n103. Поскольку транзистор n103 (схема LRC освобождения защелки) заперт в течение периода времени, когда SB-сигнал имеет низкий уровень, клемма Q не имеет короткого замыкания на клемму VSS (источник питания низкого напряжения). Соответственно, можно устойчиво поддерживать Q-сигнал в активном состоянии (=высокий уровень). Клемма Q соединена с затвором транзистора р104 и затвором транзистора n104. По этой причине, в течение периода времени, когда Q-сигнал имеет высокий уровень, транзистор р104 заперт, а транзистор n104 открыт. Соответственно, клемма QB электрически соединена с клеммой VSS (источник питания низкого напряжения) через транзистор n104, так что QB-сигнал стал активным (=низкий уровень). Клемма QB соединена с затвором транзистора р102 и затвором транзистора n10. По этой причине, в течение периода времени, когда QB-сигнал имеет низкий уровень, транзистор р102 открыт, а транзистор n10 заперт. Кроме того, в течение периода времени, когда R-сигнал имеет низкий уровень, транзистор р101 (схема LRC освобождения защелки) открыт. Соответственно, клемма Q электрически соединена с клеммой VDD (источник питания высокого напряжения) через транзистор р101 и транзистор р102. Как описано выше, в течение периода t1 времени Q-сигнал активен (=высокий уровень), в то время как QB-сигнал тоже активен (=низкий уровень) (см. А на фиг.75 (с)).

Если SB-сигнал неактивен (=высокий уровень) и R-сигнал неактивен (=низкий уровень) (период t2 времени, показанный на фиг.75 (b)), триггер FF900 работает, как описано ниже. Когда R-сигнал перешел на низкий уровень и SB-сигнал перешел на высокий уровень, транзистор n103 отпирается. В этом случае оба транзистора р101 и n103 (схемы LRC освобождения защелки) открыты, так что эта схема защелки образована (i) инвертором, составленным из транзистора р102 и транзистора n102, и (ii) другим инвертором, составленным из транзистора р104 и транзистора n104 (схема LC защелки включена). Здесь, поскольку оба транзистора - транзистор р100 (схема SC установки), передающий напряжение от клеммы VDD к клемме Q, и транзистор n100 (схема RC сброса) передающий напряжение Vss к клемме Q, заперты, электрическое напряжение в схему LC защелки не поступает. В таком защелкнутом состоянии сохраняется состояние, в котором SB-сигнал не изменялся, т.е. состояние, имевшее место в период t1 времени (Q-сигнал имеет высокий уровень, когда QB-сигнал имеет низкий уровень), сохраняется в течение периода t2 времени (см. С на фиг.75 (с)).

Когда SB-сигнал неактивен (=высокий уровень) и R-сигнал активен (=высокий уровень) (период t3 времени показан на фиг.75 (b)), триггер FF 900 работает, как описано ниже. Когда R-сигнал стал активным (=высокий уровень), транзистор n100 (схема RC сброса) отпирается. Поскольку SB-сигнал имеет высокий уровень, транзистор n101 (схема PDC определения приоритета) открыт. Поскольку оба транзистора - транзистор n100 и транзистор n101, открыты, клемма Q электрически соединена с источником напряжения VSS. Транзистор р101 (схема определения защелки) заперт в течение периода времени, когда R-сигнал имеет высокий уровень, так что клемма Q и клемма VDD не будут короткозамкнуты одна с другой. Соответственно, можно устойчиво поддерживать Q-сигнал в неактивном состоянии (=низкий уровень). Далее, поскольку транзистор n104 заперт и транзистор р104 открыт в течение периода времени, когда Q-сигнал имеет низкий уровень, клемма QB оказывается соединена с клеммой VDD электрически. В результате QB-сигнал переходит на высокий уровень. Более того, поскольку в период времени, когда QB-сигнал имеет высокий уровень и SB-сигнал имеет высокий уровень, (i) оба транзистора - транзистор n102 и транзистор n103, (схема LRC освобождения защелки) открыты и (ii) транзистор р102 заперт. Соответственно, клемма Q электрически соединена с клеммой VSS через транзистор n102 и транзистор n103. Как описано выше, в течение периода t3 времени Q-сигнал неактивен (=низкий уровень) и QB-сигнал неактивен (=высокий уровень) (см. D на фиг.75 (с)).

Когда SB-сигнал неактивен (=высокий уровень) и R-сигнал неактивен (=низкий уровень) (период t4 времени, показанный на фиг.75 (b)), триггер FF900 работает, как описано ниже. Когда SB-сигнал перешел на высокий уровень и R-сигнал перешел на низкий уровень, оба транзистора - транзистор р101 и транзистор n103, (схемы LRC освобождения защелки) отпираются. Это включает схему LC защелки. Соответственно, состояние, в котором R-сигнал не изменил свое состояние, сохраняется, т.е. состояние, имевшее место в течение периода t3 времени (Q-сигнал имеет низкий уровень, когда QB-сигнал имеет высокий уровень), сохраняется в течение периода t4 времени.

Инвертированный сигнал инициализации, т.е. INITB-сигнал, в нормальном состоянии неактивен (=высокий уровень), так что транзистор р103 (схема 1C инициализации) в нормальном состоянии заперт. Для инициализации триггера можно принудительно установить выходной сигнал (Q-сигнал) триггера, переведя INITB-сигнал в активное состояние. В триггере FF900, когда INITB-сигнал стал активным (=низкий уровень), транзистор р103 отпирается. В результате клемма QB и клемма VDD оказываются электрически соединены одна с другой, так что QB-сигнал переходит на высокий уровень. Транзистор n10 открыт в течение периода времени, когда QB-сигнал имеет высокий уровень. Далее, транзистор n103 открыт в течение периода времени, когда SB-сигнал неактивен (высокий уровень). Соответственно, клемма Q оказывается электрически соединена с клеммой VSS через транзистор n102 и транзистор n103, так что Q-сигнал становится неактивным (=низкий уровень).

Отметим, что транзистор n101 (схема определения приоритета) задает, какой из сигналов - SB-сигнал или R-сигнал, имеет приоритет, в случае, когда оба сигнала - SB-сигнал и R-сигнал, стали активными одновременно. В триггере FF900, когда SB-сигнал стал активным (=низкий уровень) и R-сигнал стал активным (=высокий уровень), оба транзистора - транзистор р100 и транзистор n100, отпираются. В этом случае транзистор n101 (схема определения приоритета) запирается, так что схема RC сброса и клемма VSS оказываются отделены электрически одна от другой, а клемма Q электрически соединена с клеммой VDD через транзистор р100. Другими словами, SB-сигнал имеет приоритет.

Перечень литературы

[Патентная литература]

Патентная литература 1

Публикация заявки на патент Японии, Tokukai, No. 2001-135093 А (дата публикации: 18 мая 2001 г.)

Сущность изобретения

Техническая проблема

В описанном выше известном триггере схема занимает большую площадь. Это было препятствием для уменьшения размеров устройства (такого как регистр сдвига и различные схемы возбуждения устройства отображения), включающего такой известный триггер.

Целью настоящего изобретения является создание компактного триггера или различных компактных схем возбуждения устройства отображения.

Решение проблемы

Триггер согласно настоящему изобретению включает: первый транзистор, представляющий собой p-канальный транзистор; второй транзистор, представляющий собой n-канальный транзистор; третий транзистор, представляющий собой p-канальный транзистор; четвертый транзистор, представляющий собой n-канальный транзистор; несколько входных клемм; первую выходную клемму; вторую выходную клемму; и входной транзистор, первый транзистор и второй транзистор составляют первую КМОП-схему, так что затворы этих транзисторов соединены один с другим и стоки соединены один с другим, третий транзистор и четвертый транзистор составляют вторую КМОП-схему, так что затворы этих транзисторов соединены один с другим и стоки соединены один с другим, первая выходная клемма соединена с затворной стороной первой КМОП-схемы и стоковой стороной второй КМОП-схемы, вторая выходная клемма соединена с затворной стороной второй КМОП-схемы и стоковой стороной первой КМОП-схемы, затвор входного транзистора соединен с одной из нескольких входных клемм, а исток этого транзистора соединен с другой из этих нескольких входных клемм. Отметим, что сток входного транзистора соединен с первой выходной клеммой прямо или не прямо (через релейный транзистор).

В настоящем описании один (на выходной стороне) из двух электропроводных электродов транзистора (p-канального транзистора или n-канального транзистора) называется «сток». В описанной выше конфигурации, если оба сигнала, поступающие на разные входные клеммы, стали активными одновременно, один из этих сигналов, поступающих на разные входные клеммы, может быть передан на выход, поскольку указанный один из сигналов имеет приоритет и без использования схемы определения приоритета, которая была нужна в известном триггере. Это делает возможным создание еще более компактного триггера.

Преимущества изобретения

Как описано выше, при использовании такой схемы становится возможным создать компактный триггер, компактный регистр сдвига или компактную схему возбуждения устройства отображения.

Краткое описание чертежей

Фиг.1 представляет пояснительный вид, иллюстрирующий триггер в соответствии с вариантом 1 настоящего изобретения: фиг.1 (а) показывает электрическую схему, фиг.1 (b) показывает временную диаграмму и фиг.1 (с) показывает таблицу истинности.

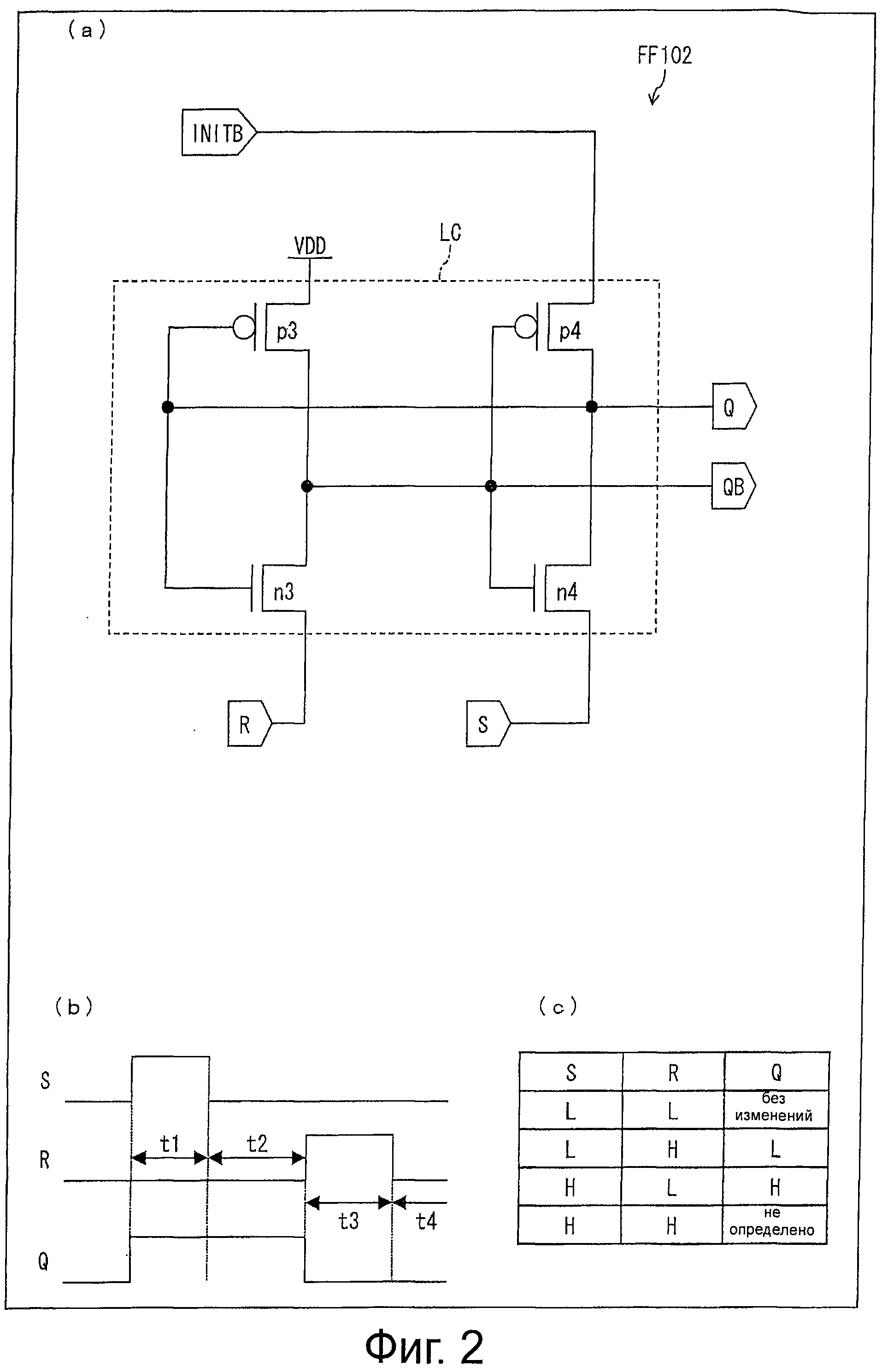

Фиг.2 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 1 настоящего изобретения: фиг.2 (а) показывает электрическую схему, фиг.2 (b) показывает временную диаграмму и фиг.2 (с) показывает таблицу истинности.

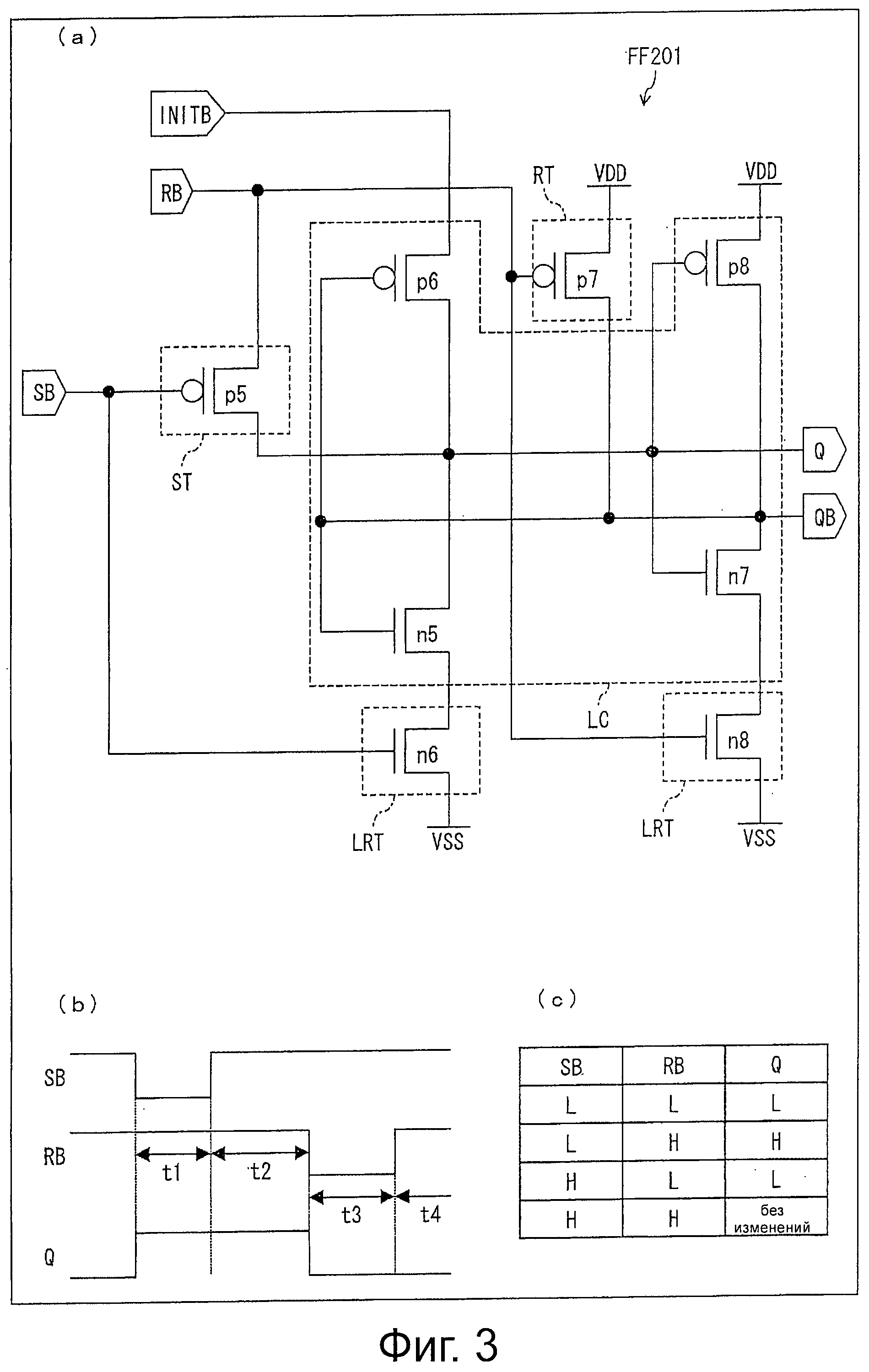

Фиг.3 представляет пояснительный вид, иллюстрирующий триггер в соответствии с вариантом 2 настоящего изобретения: фиг.3 (а) показывает электрическую схему, фиг.3 (b) показывает временную диаграмму и фиг.3 (с) показывает таблицу истинности.

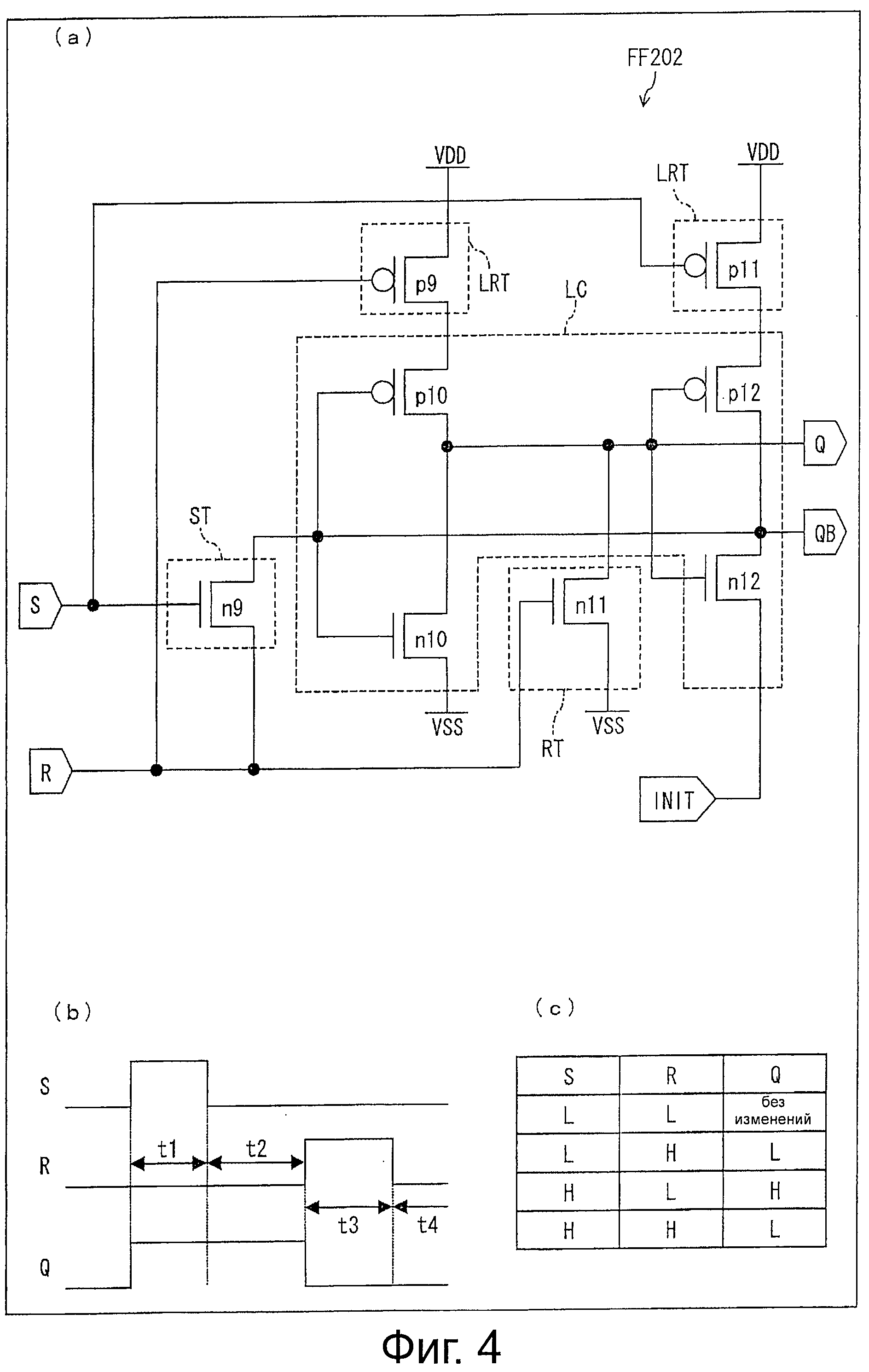

Фиг.4 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 2 настоящего изобретения: фиг.4 (а) показывает электрическую схему, фиг.4 (b) показывает временную диаграмму и фиг.4 (с) показывает таблицу истинности.

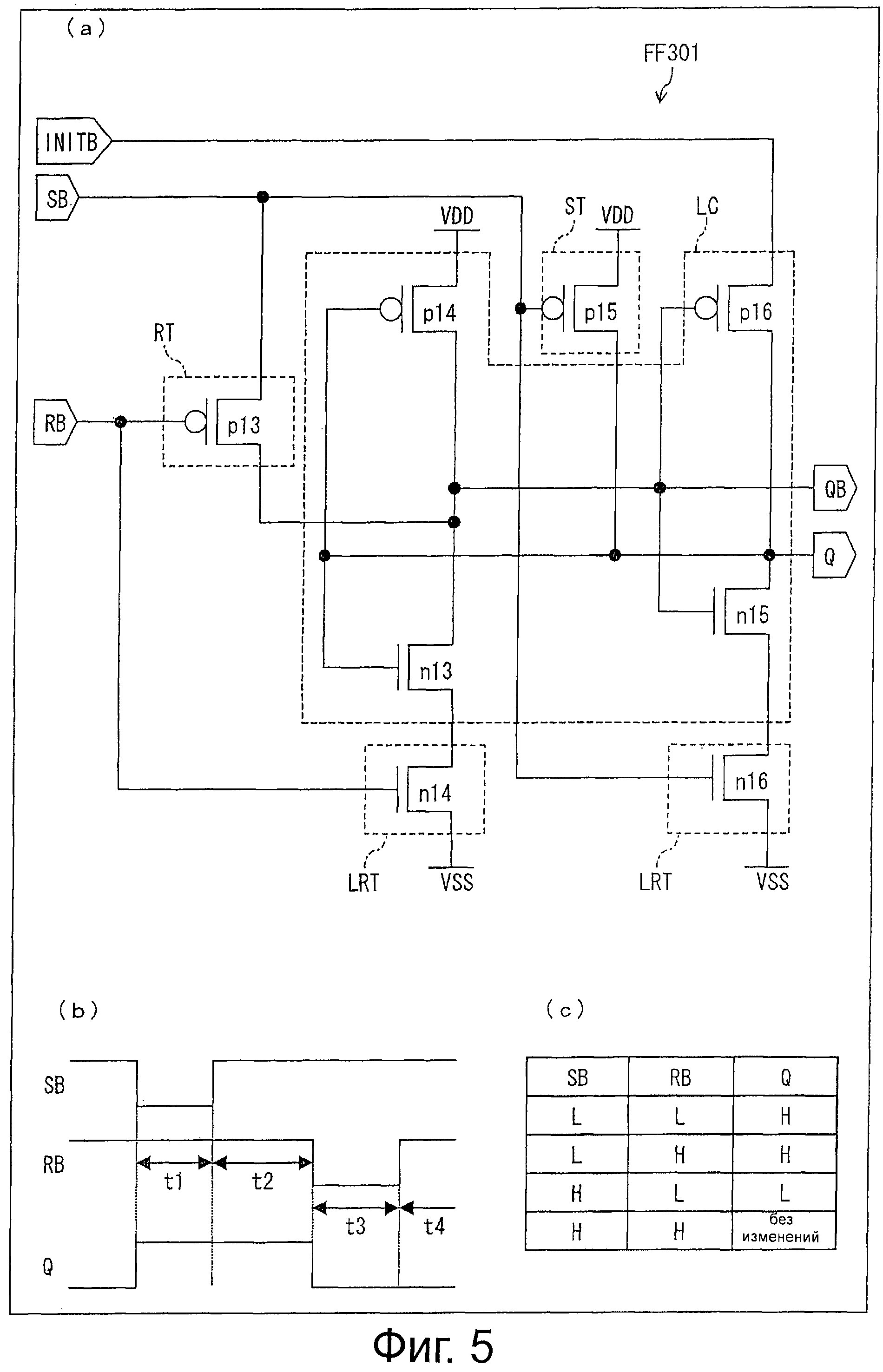

Фиг.5 представляет пояснительный вид, иллюстрирующий триггер в соответствии с вариантом 3 настоящего изобретения: фиг.5 (а) показывает электрическую схему, фиг.5 (b) показывает временную диаграмму и фиг.5 (с) показывает таблицу истинности.

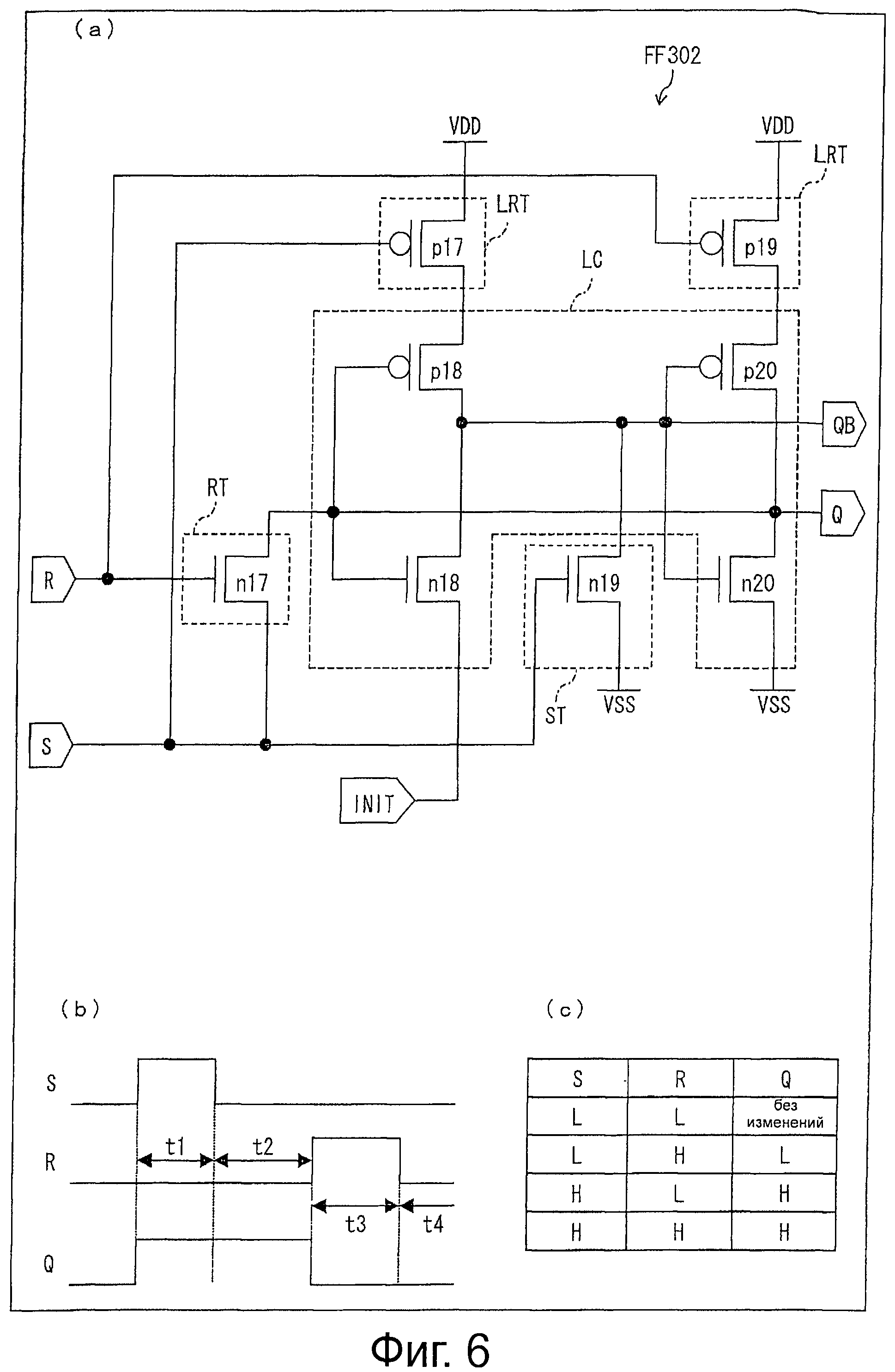

Фиг.6 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 3 настоящего изобретения: фиг.6 (а) показывает электрическую схему, фиг.6 (b) показывает временную диаграмму и фиг.6 (с) показывает таблицу истинности.

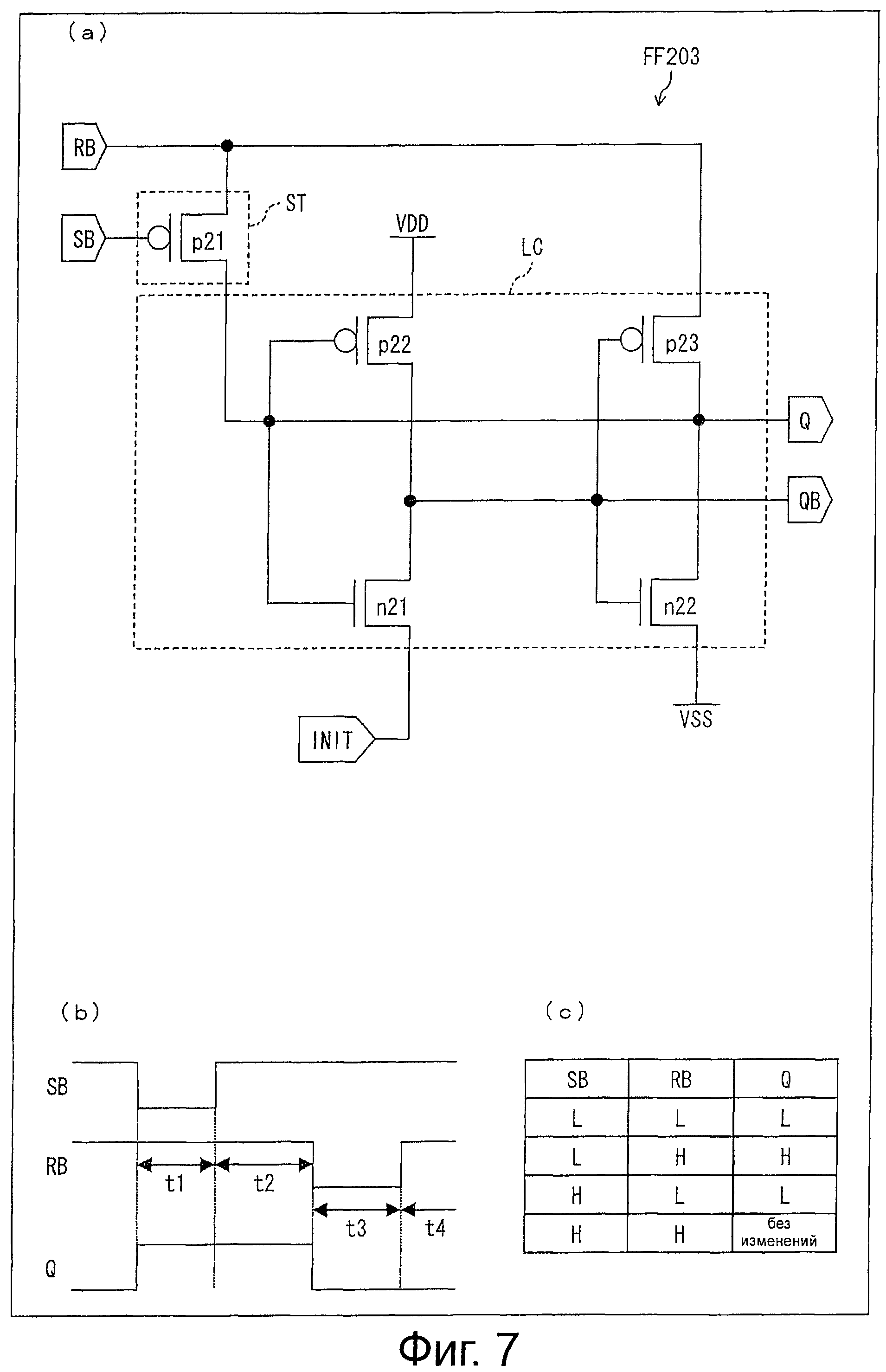

Фиг.7 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 2 настоящего изобретения: фиг.7 (а) показывает электрическую схему, фиг.7 (b) показывает временную диаграмму и фиг.7 (с) показывает таблицу истинности.

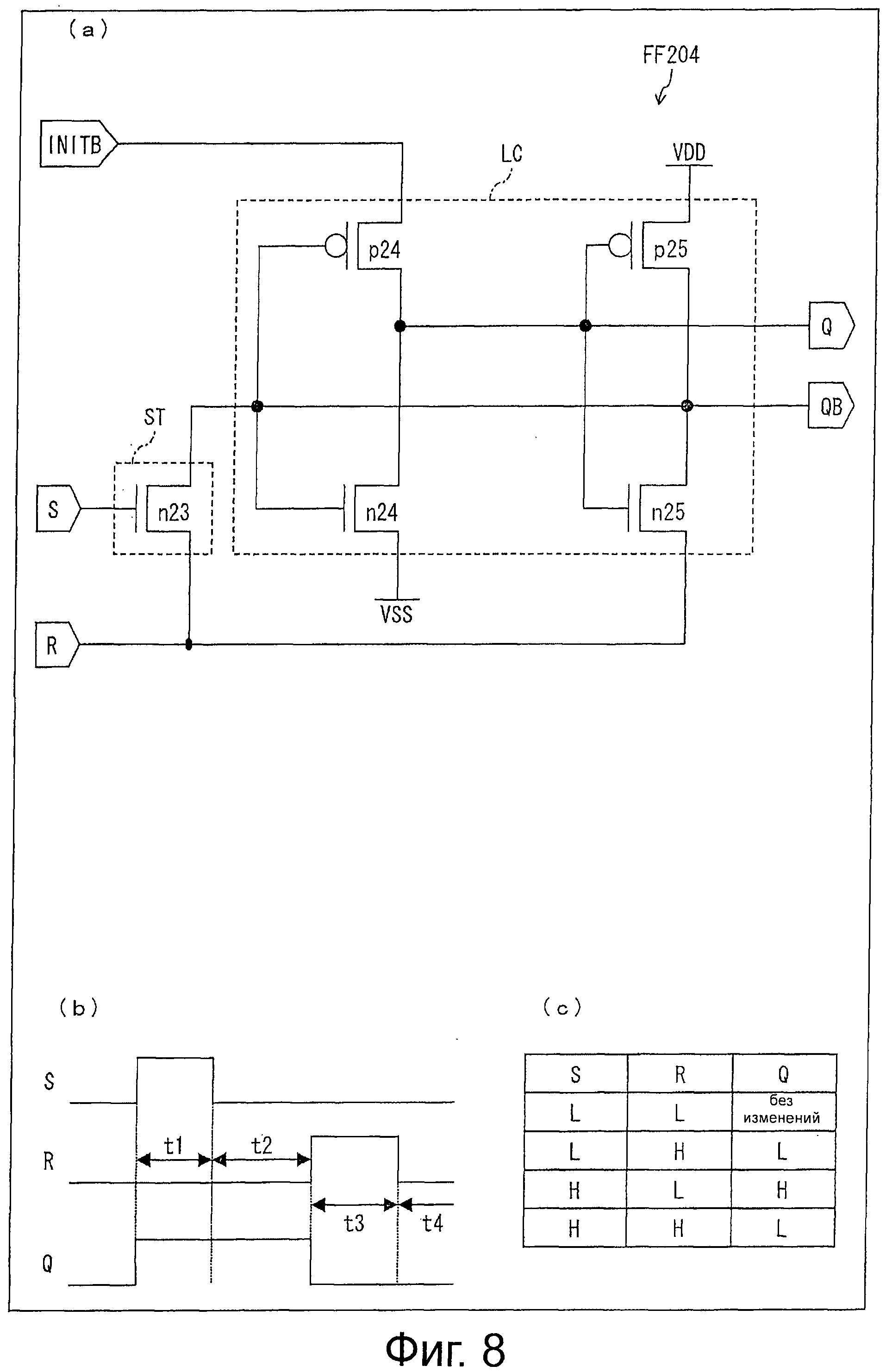

Фиг.8 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 2 настоящего изобретения: фиг.8 (а) показывает электрическую схему, фиг.8 (b) показывает временную диаграмму и фиг.8 (с) показывает таблицу истинности.

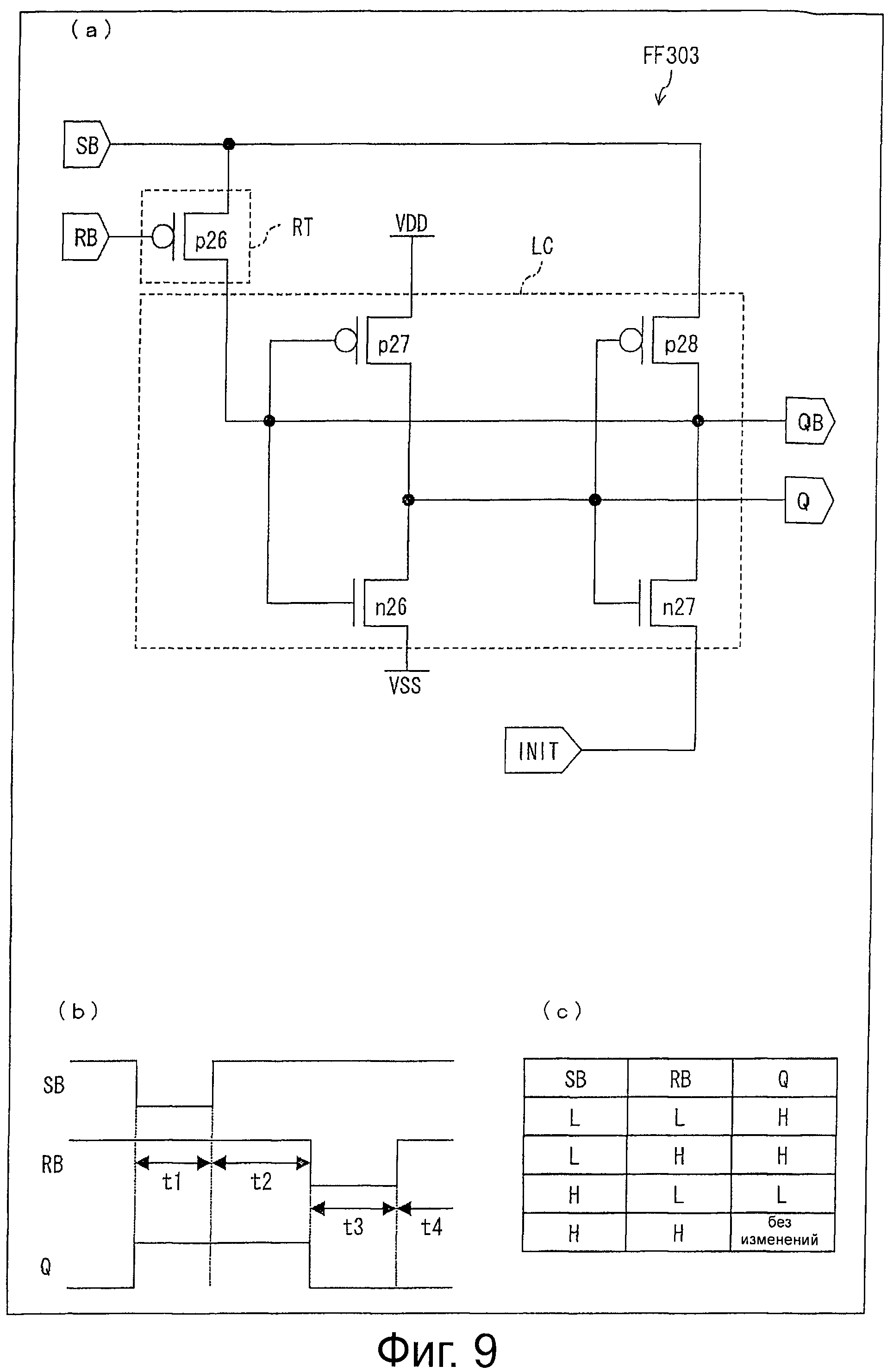

Фиг.9 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 3 настоящего изобретения: фиг.9 (а) показывает электрическую схему, фиг.9 (b) показывает временную диаграмму и фиг.9 (с) показывает таблицу истинности.

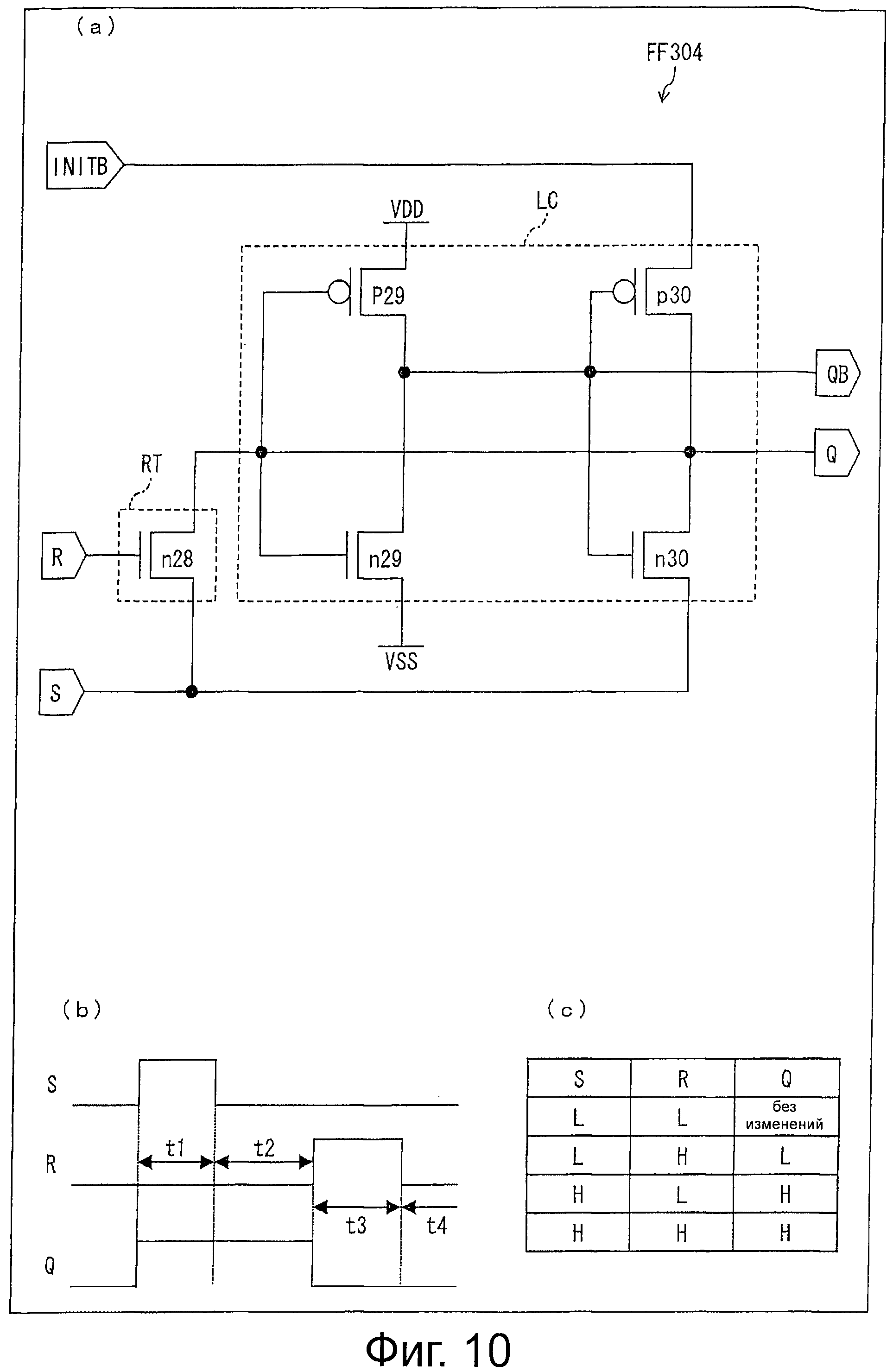

Фиг.10 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 3 настоящего изобретения: фиг.10 (а) показывает электрическую схему, фиг.10 (b) показывает временную диаграмму и фиг.10 (с) показывает таблицу истинности.

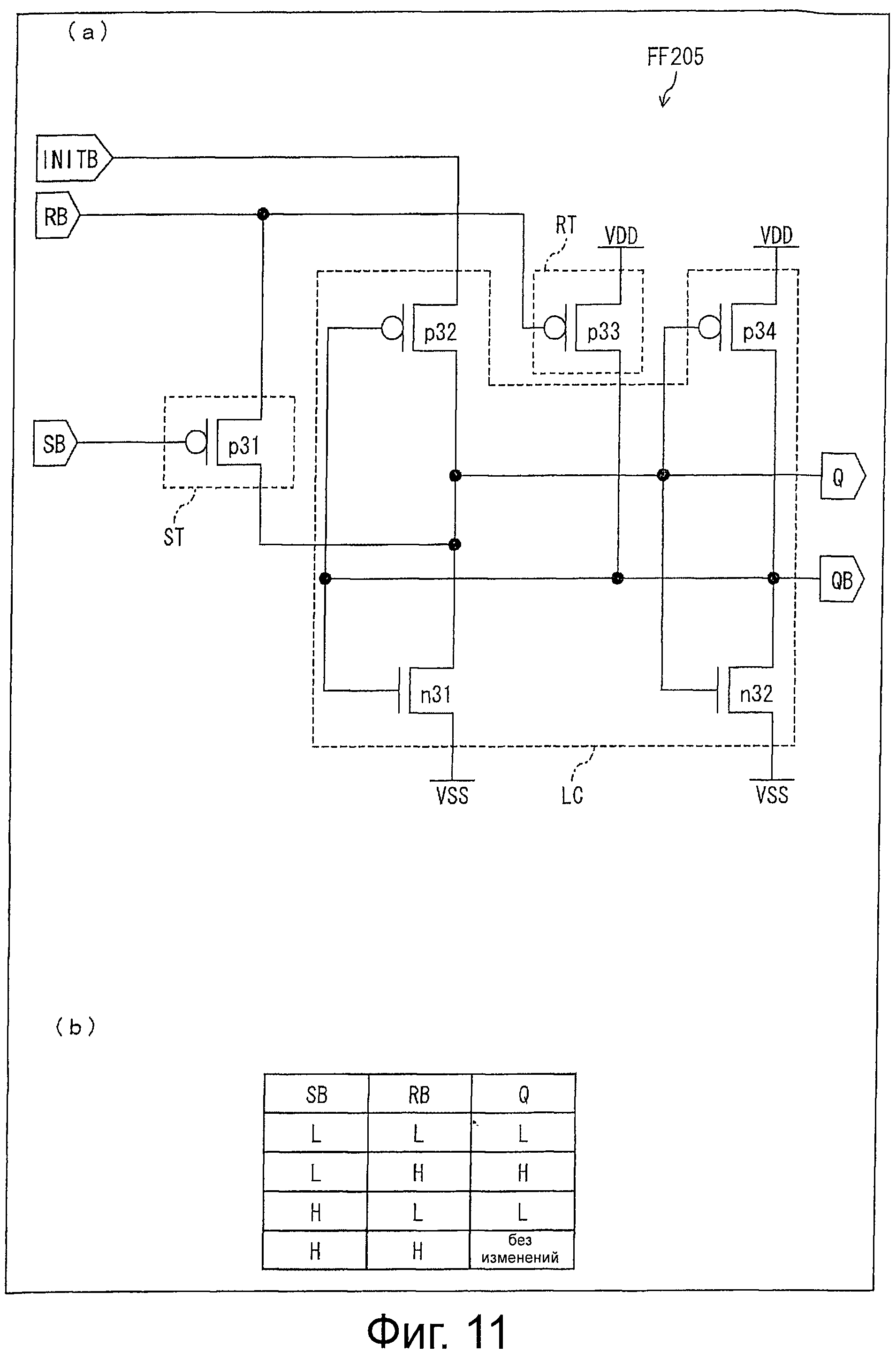

Фиг.11 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 2 настоящего изобретения: фиг.11 (а) показывает электрическую схему, фиг.11 (b) показывает таблицу истинности.

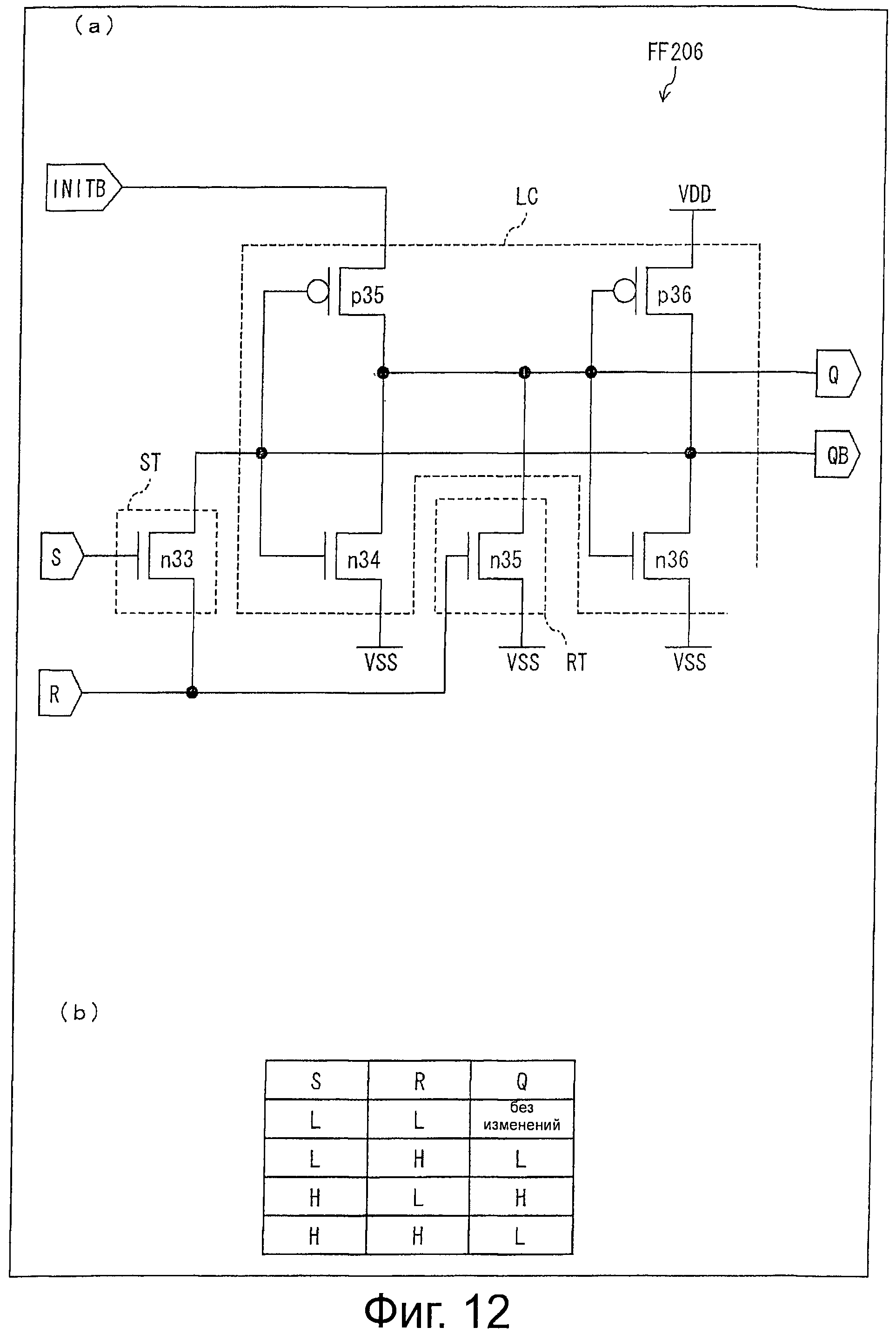

Фиг.12 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 2 настоящего изобретения: фиг.12 (а) показывает электрическую схему, фиг.12 (b) показывает таблицу истинности.

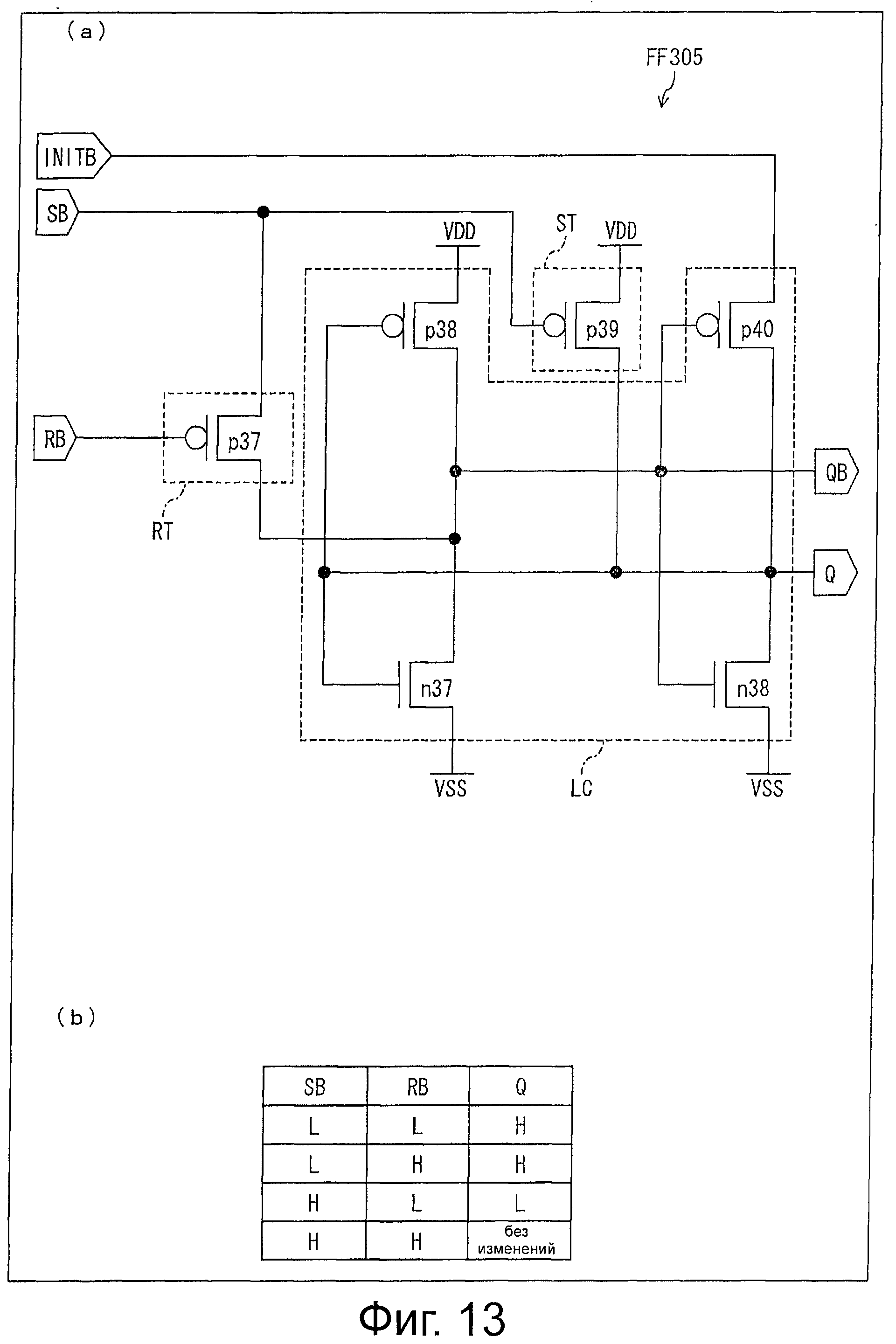

Фиг.13 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 3 настоящего изобретения: фиг.13 (а) показывает электрическую схему, фиг.13 (b) показывает таблицу истинности.

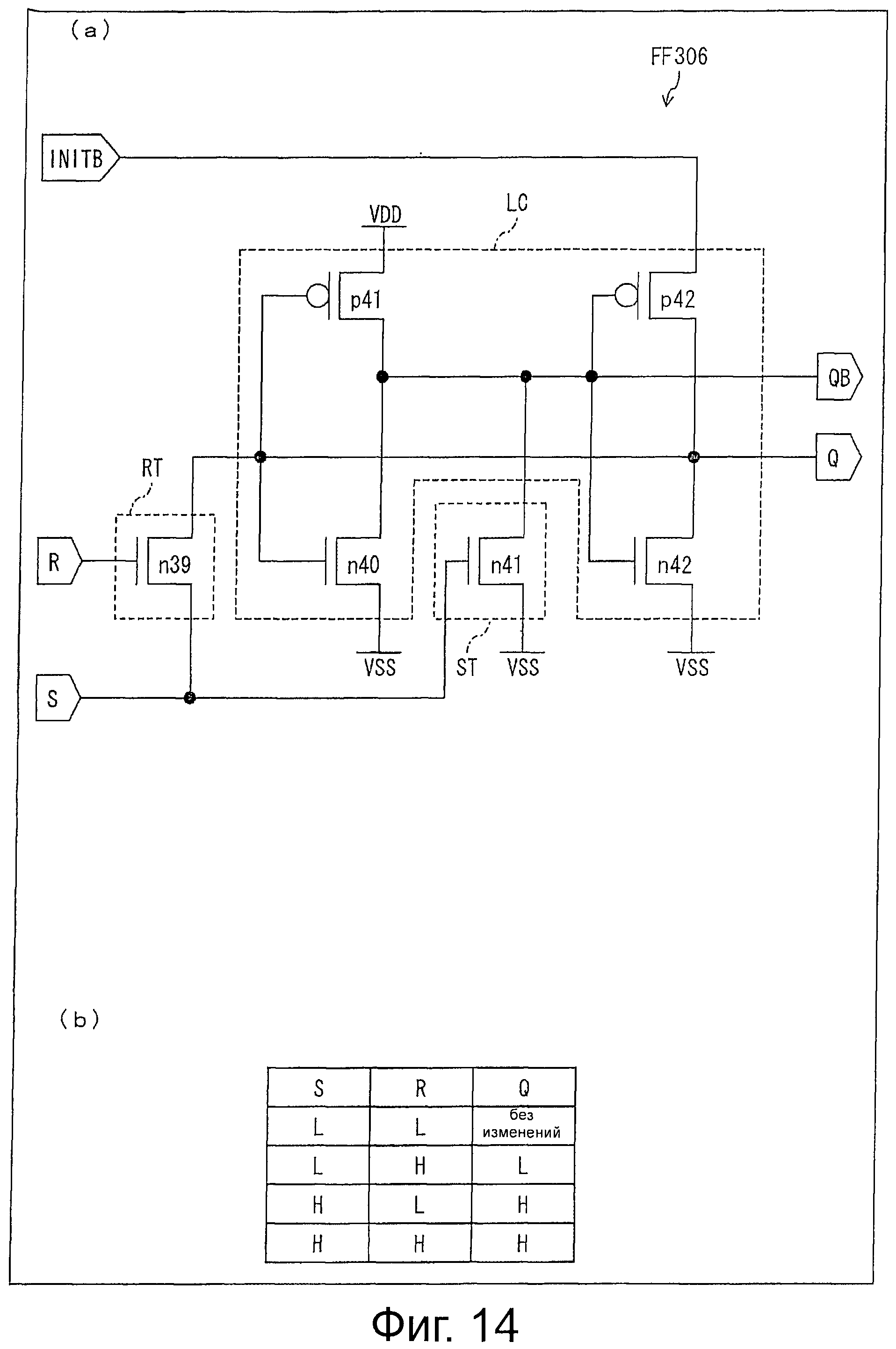

Фиг.14 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 3 настоящего изобретения: фиг.14 (а) показывает электрическую схему, фиг.14 (b) показывает таблицу истинности.

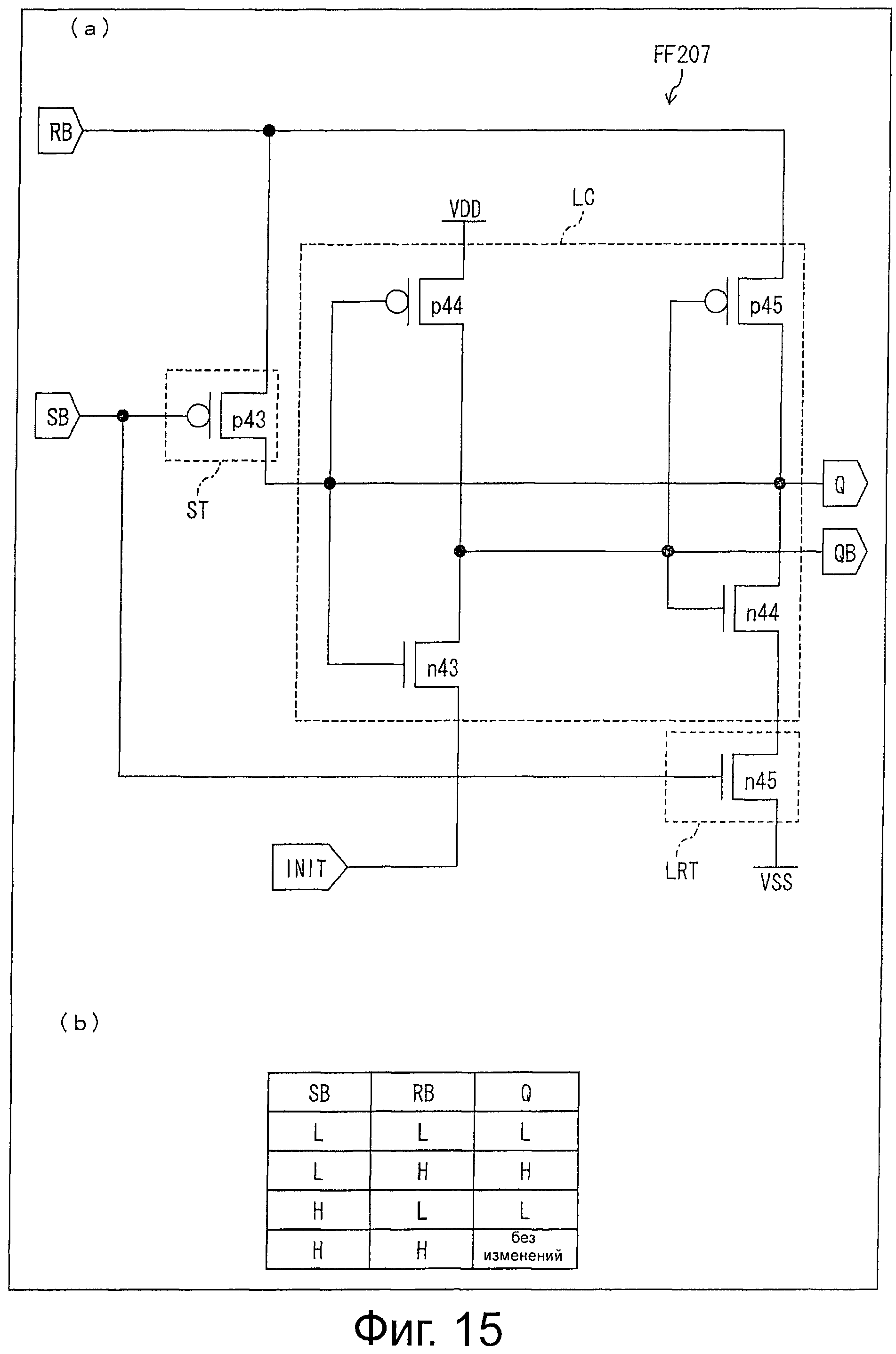

Фиг.15 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 2 настоящего изобретения: фиг.15 (а) показывает электрическую схему, фиг.15 (b) показывает таблицу истинности.

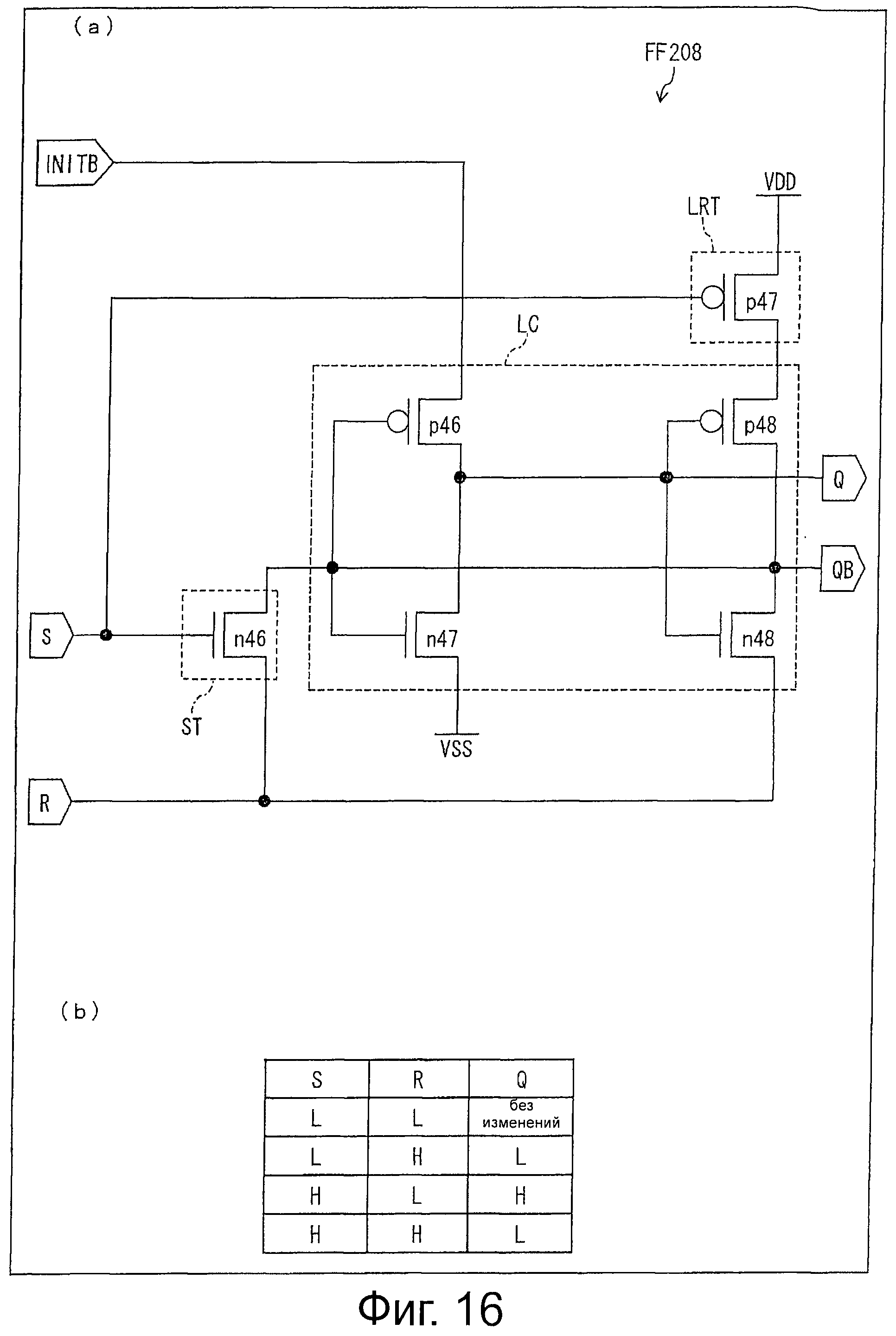

Фиг.16 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 2 настоящего изобретения: фиг.16 (а) показывает электрическую схему, фиг.16 (b) показывает таблицу истинности.

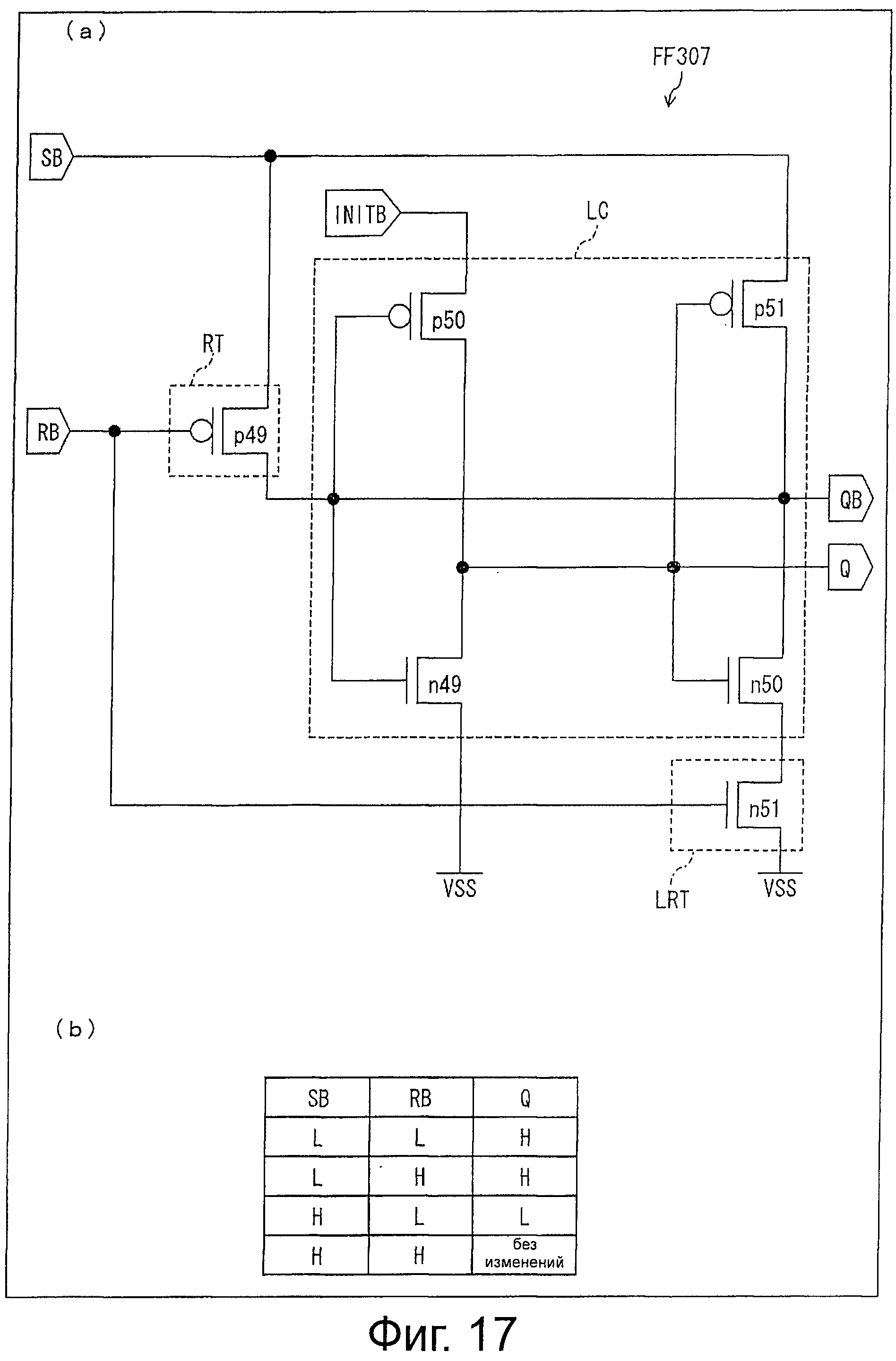

Фиг.17 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 3 настоящего изобретения: фиг.17 (а) показывает электрическую схему, фиг.17 (b) показывает таблицу истинности.

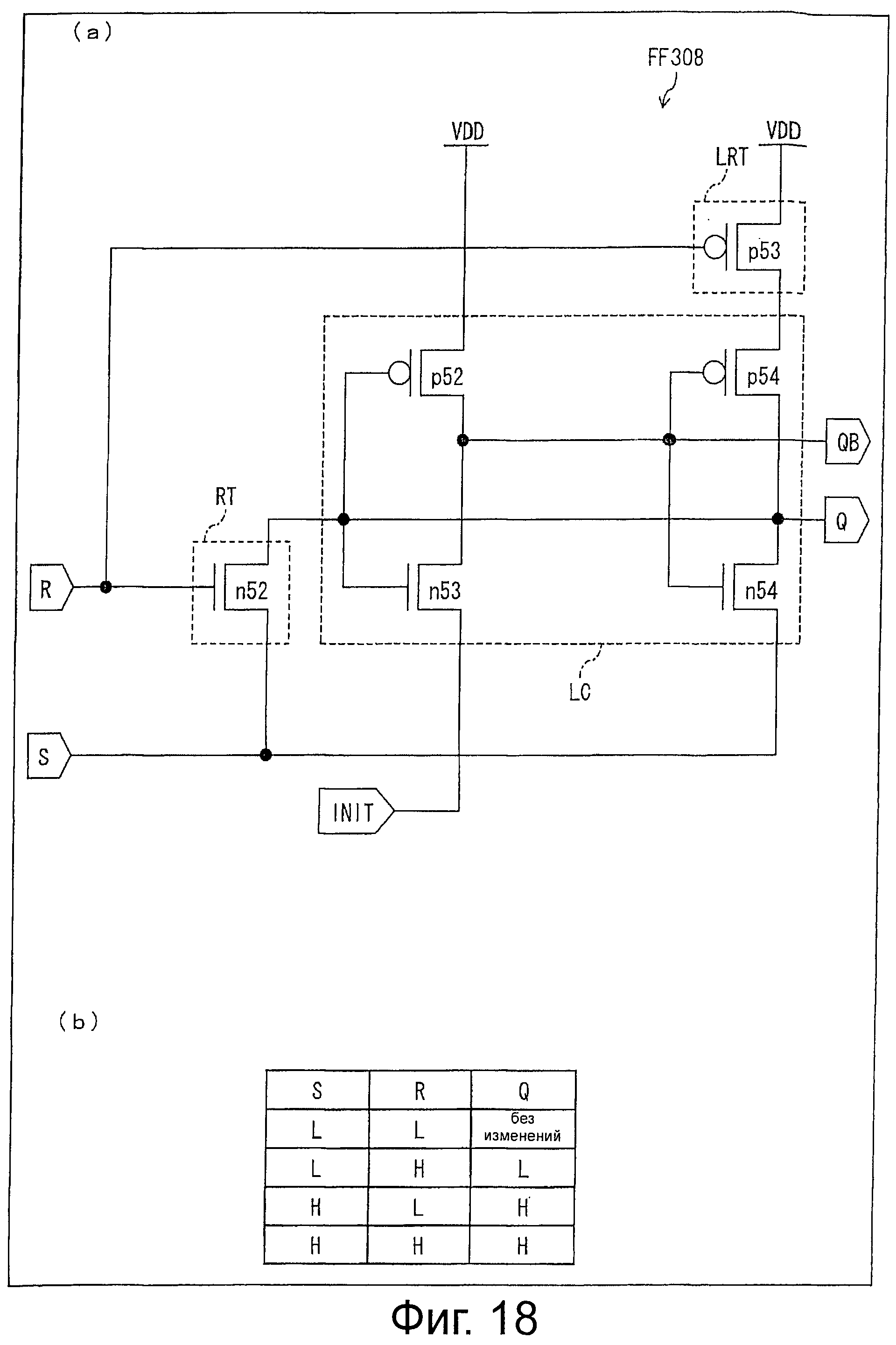

Фиг.18 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 3 настоящего изобретения: фиг.18 (а) показывает электрическую схему, фиг.18 (b) показывает таблицу истинности.

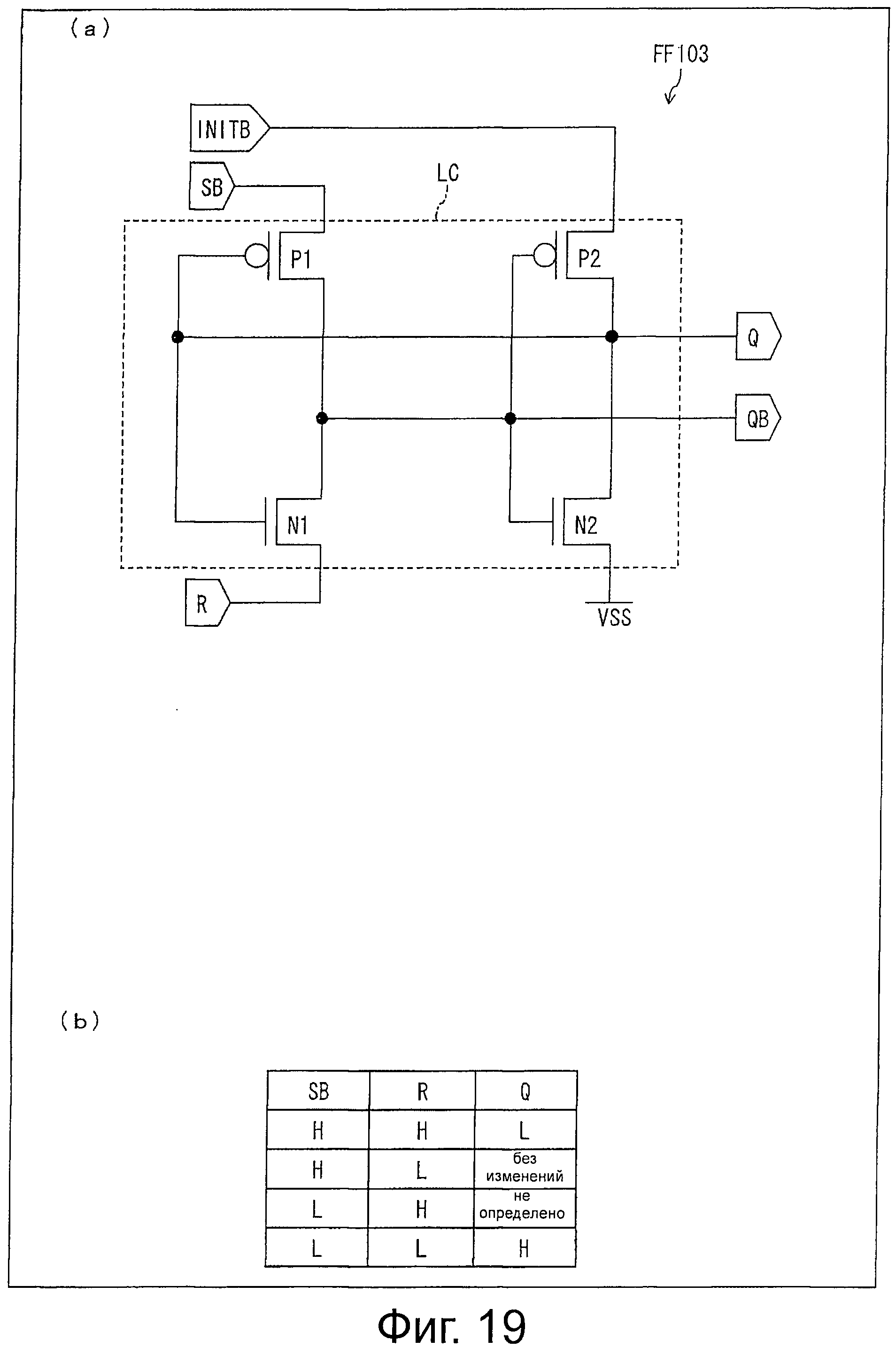

Фиг.19 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 1 настоящего изобретения: фиг.19 (а) показывает электрическую схему, фиг.19 (b) показывает таблицу истинности.

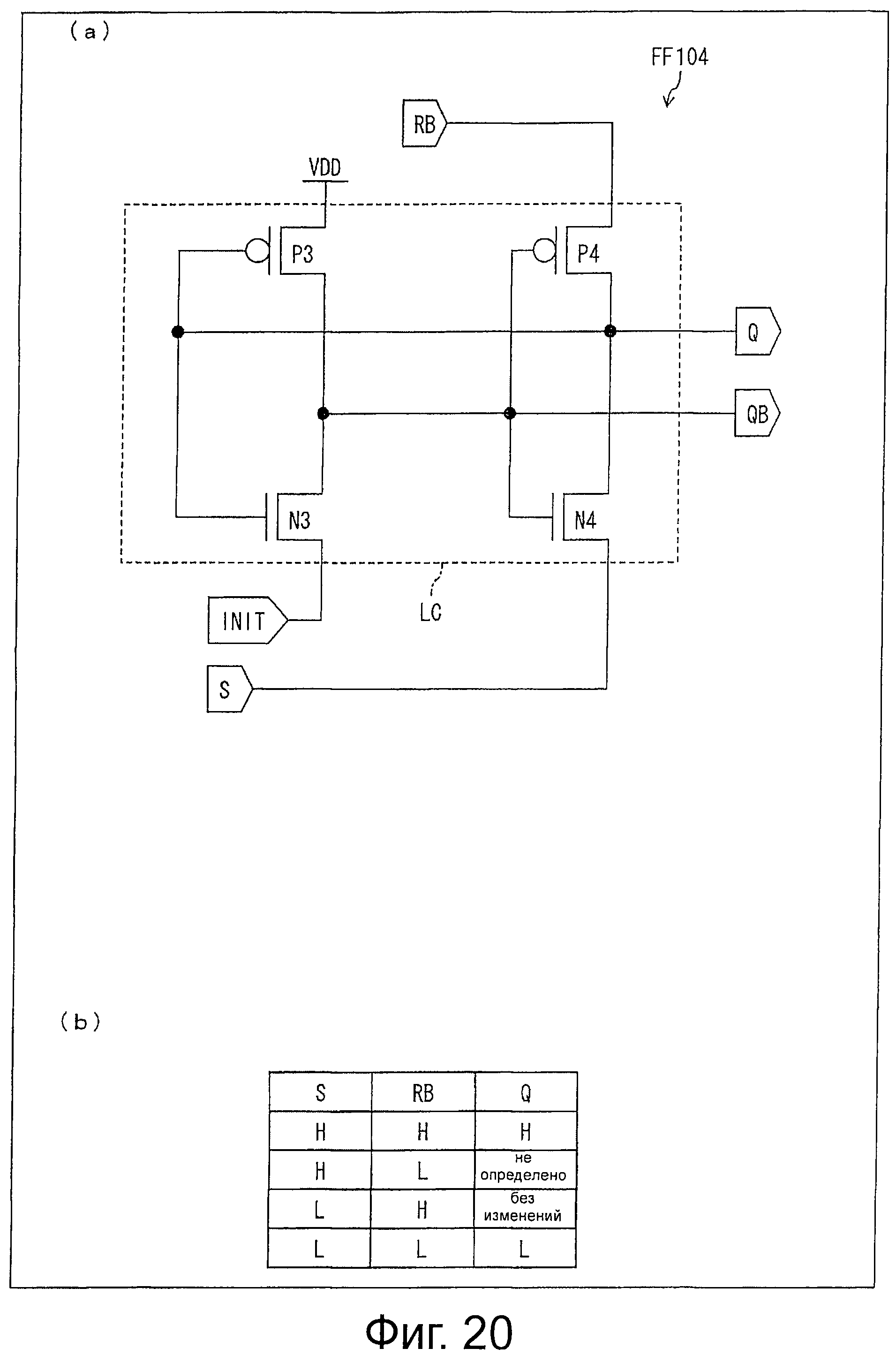

Фиг.20 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 1 настоящего изобретения: фиг.20 (а) показывает электрическую схему, фиг.20 (b) показывает таблицу истинности.

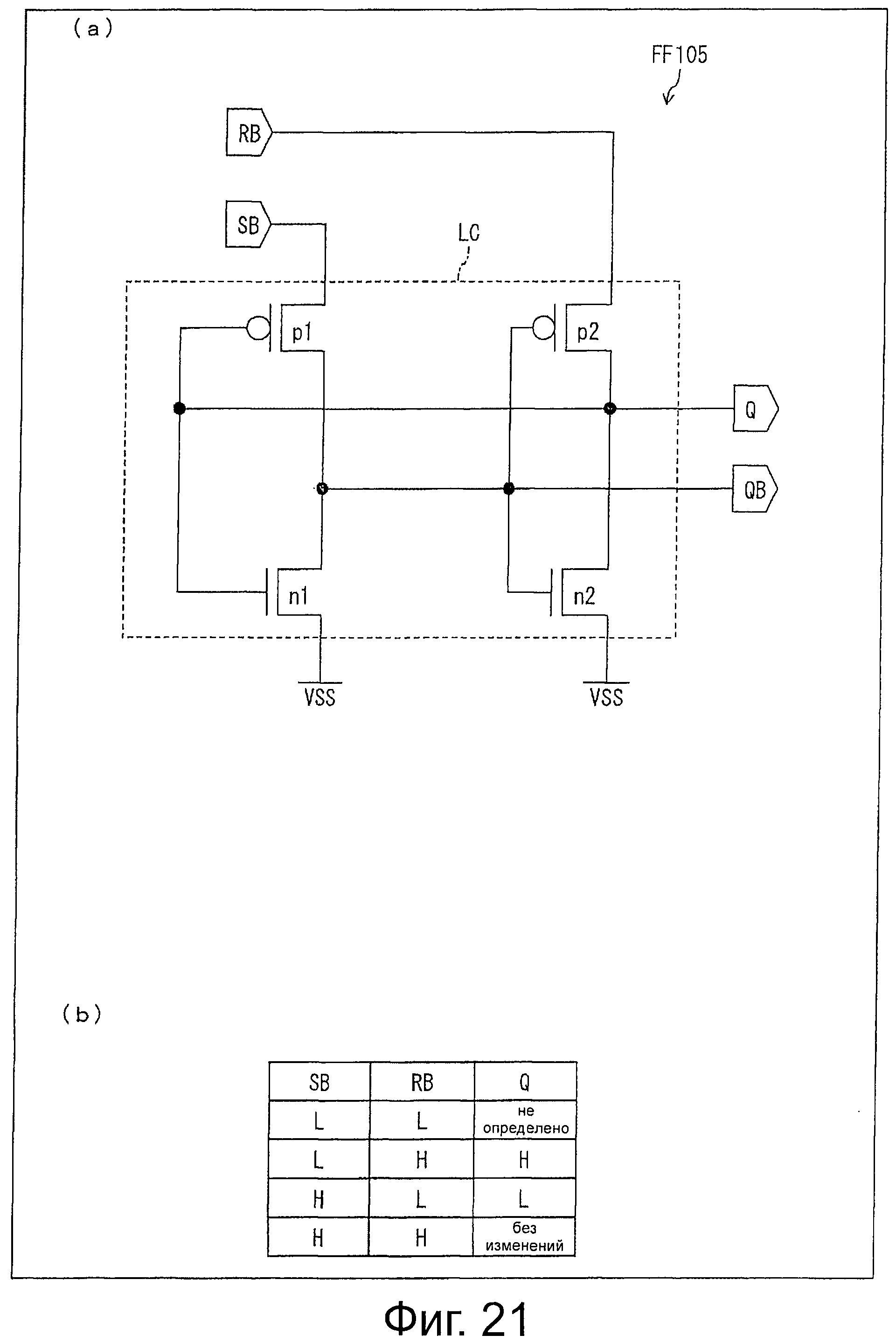

Фиг.21 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 1 настоящего изобретения: фиг.21 (а) показывает электрическую схему, фиг.21 (b) показывает таблицу истинности.

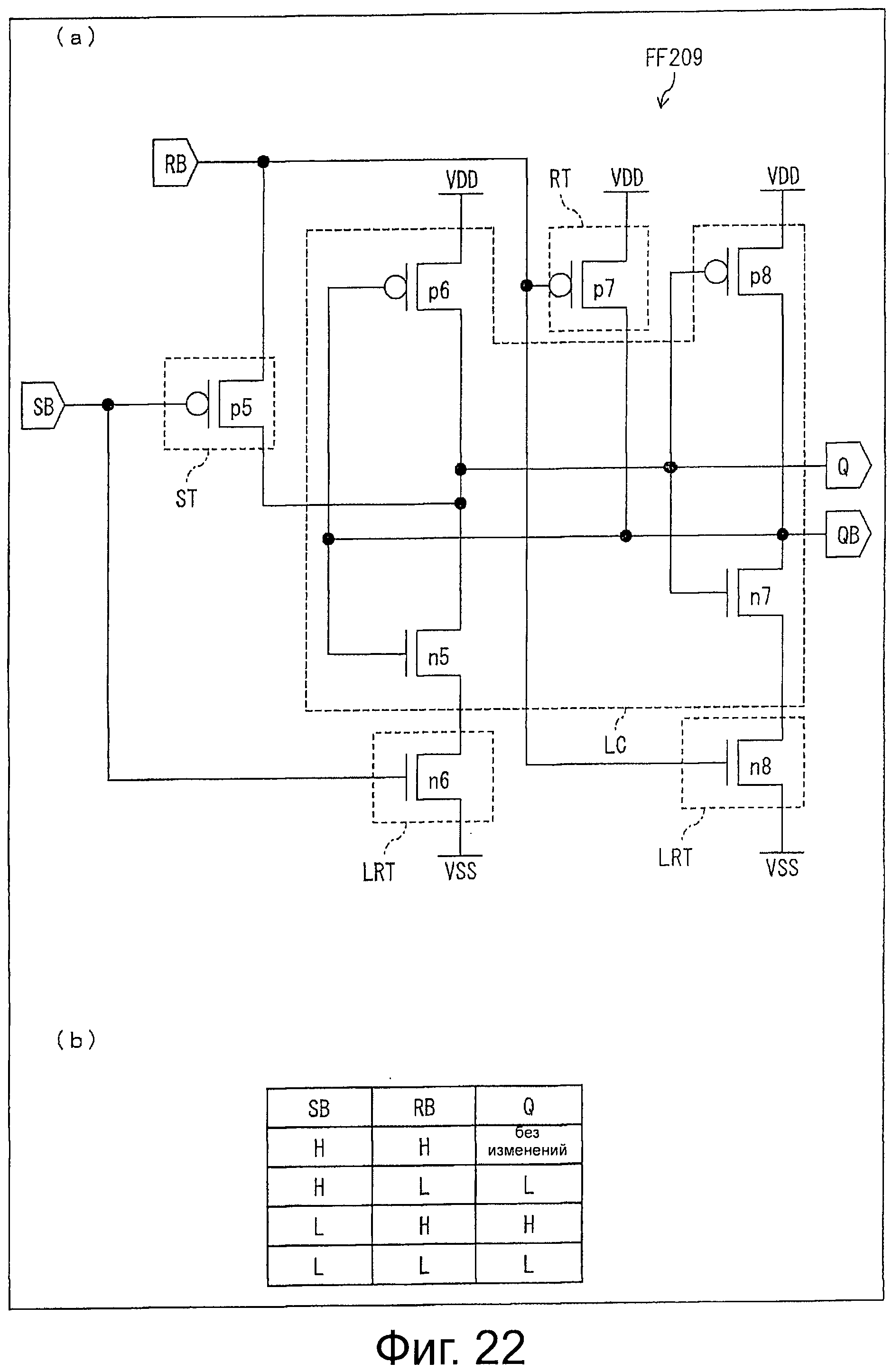

Фиг.22 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 2 настоящего изобретения: фиг.22 (а) показывает электрическую схему, фиг.22 (b) показывает таблицу истинности.

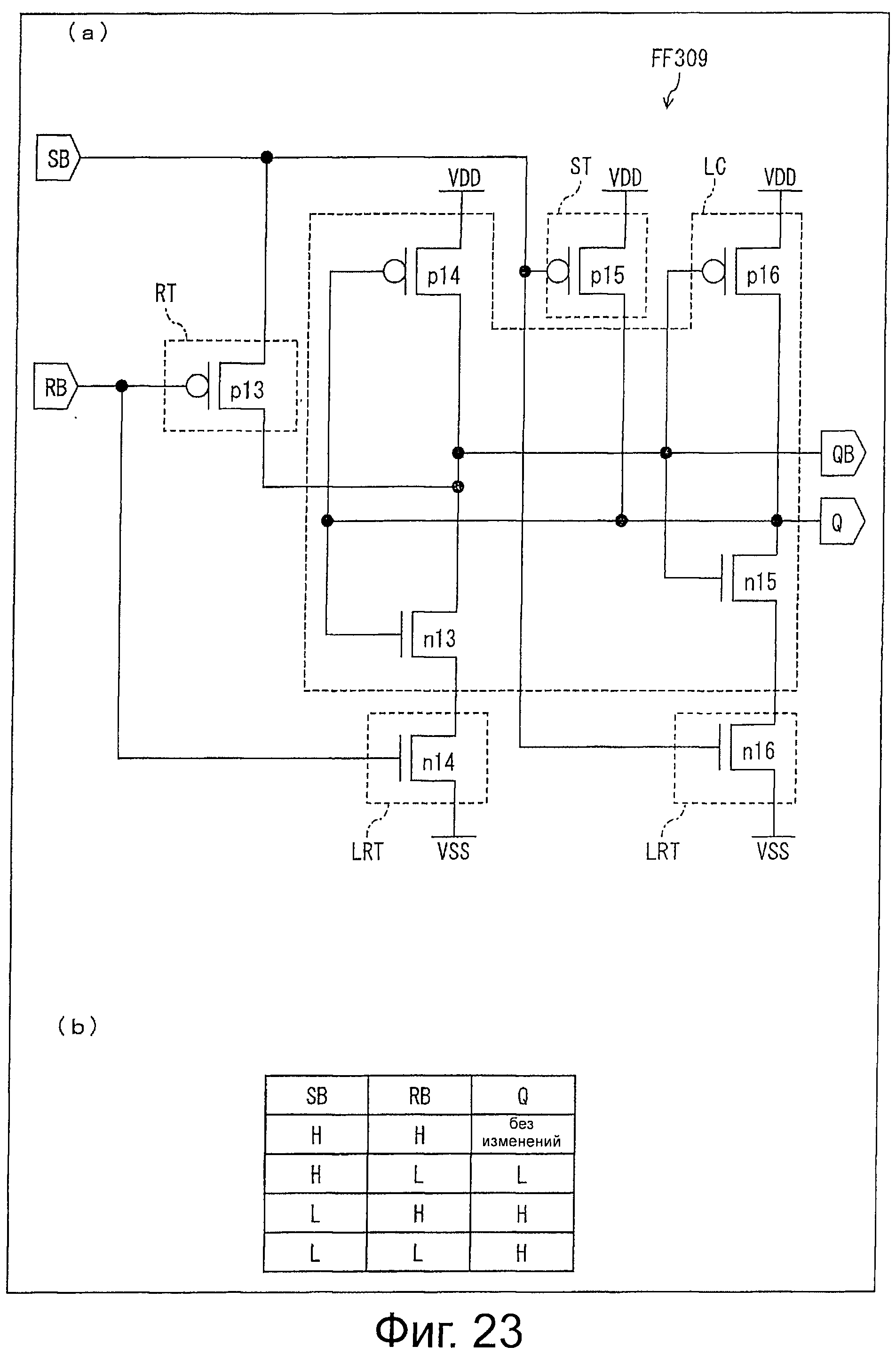

Фиг.23 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 3 настоящего изобретения: фиг.23 (а) показывает электрическую схему, фиг.23 (b) показывает таблицу истинности.

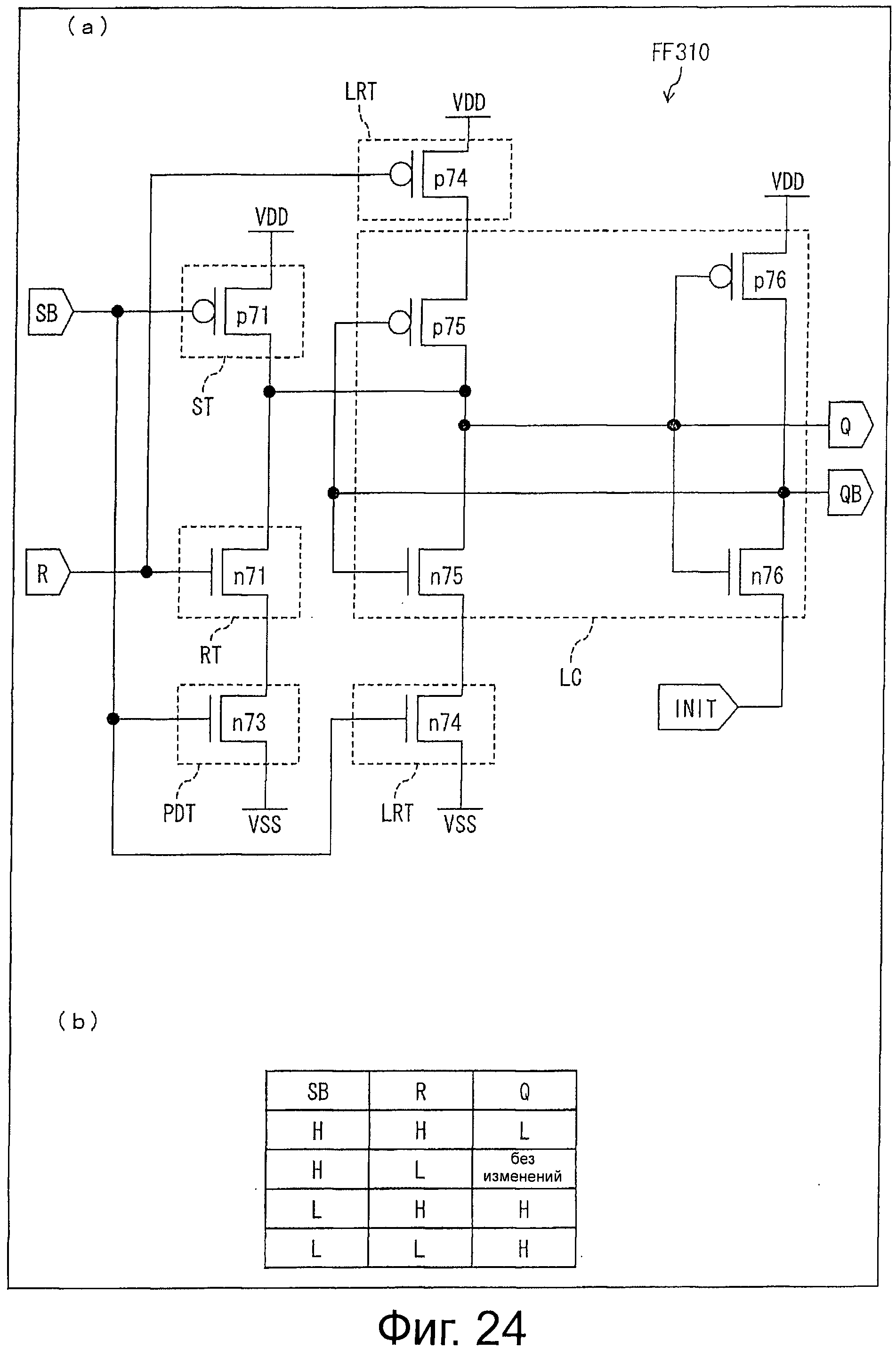

Фиг.24 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 1 настоящего изобретения: фиг.24 (а) показывает электрическую схему, фиг.24 (b) показывает таблицу истинности.

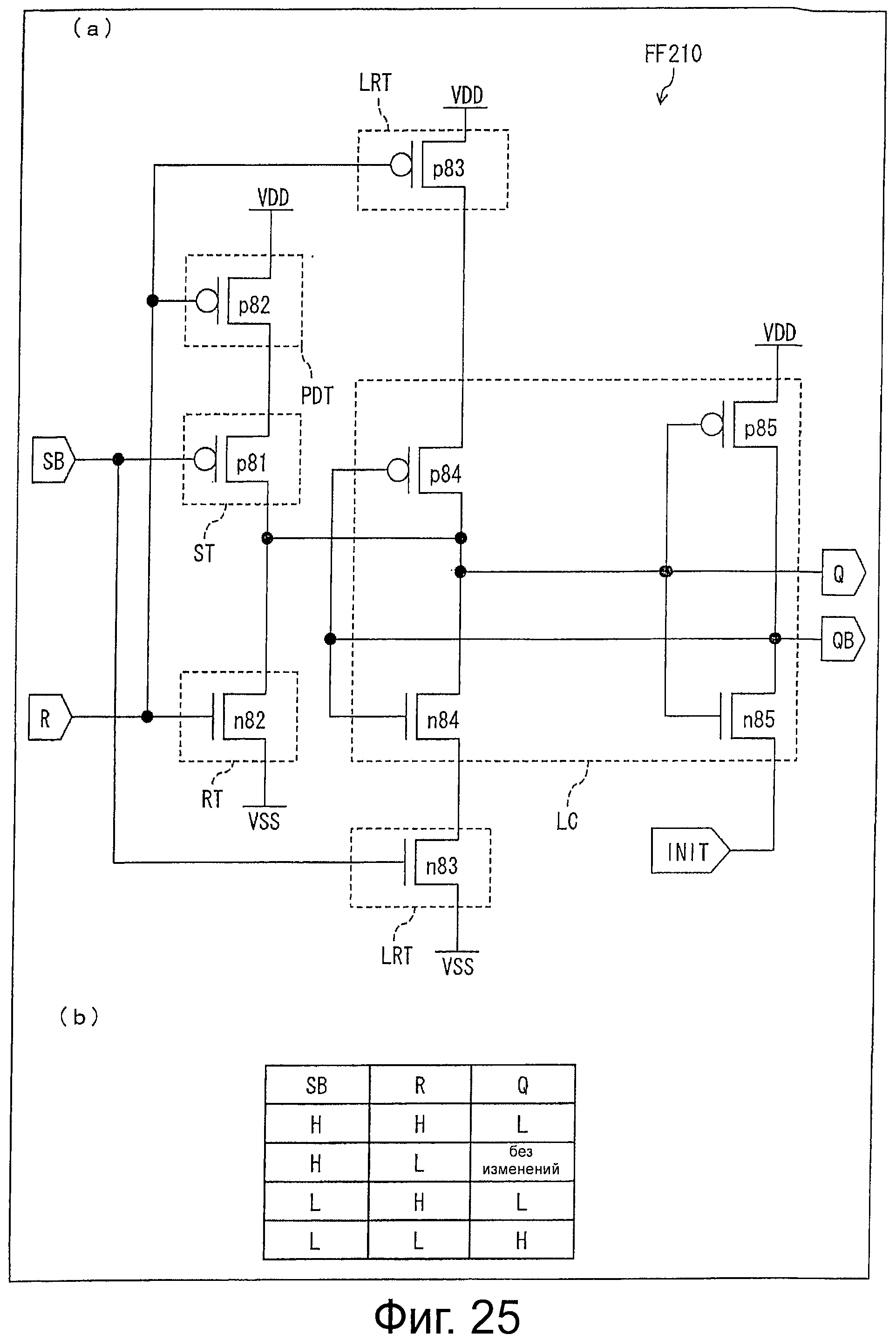

Фиг.25 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 1 настоящего изобретения: фиг.25 (а) показывает электрическую схему, фиг.25 (b) показывает таблицу истинности.

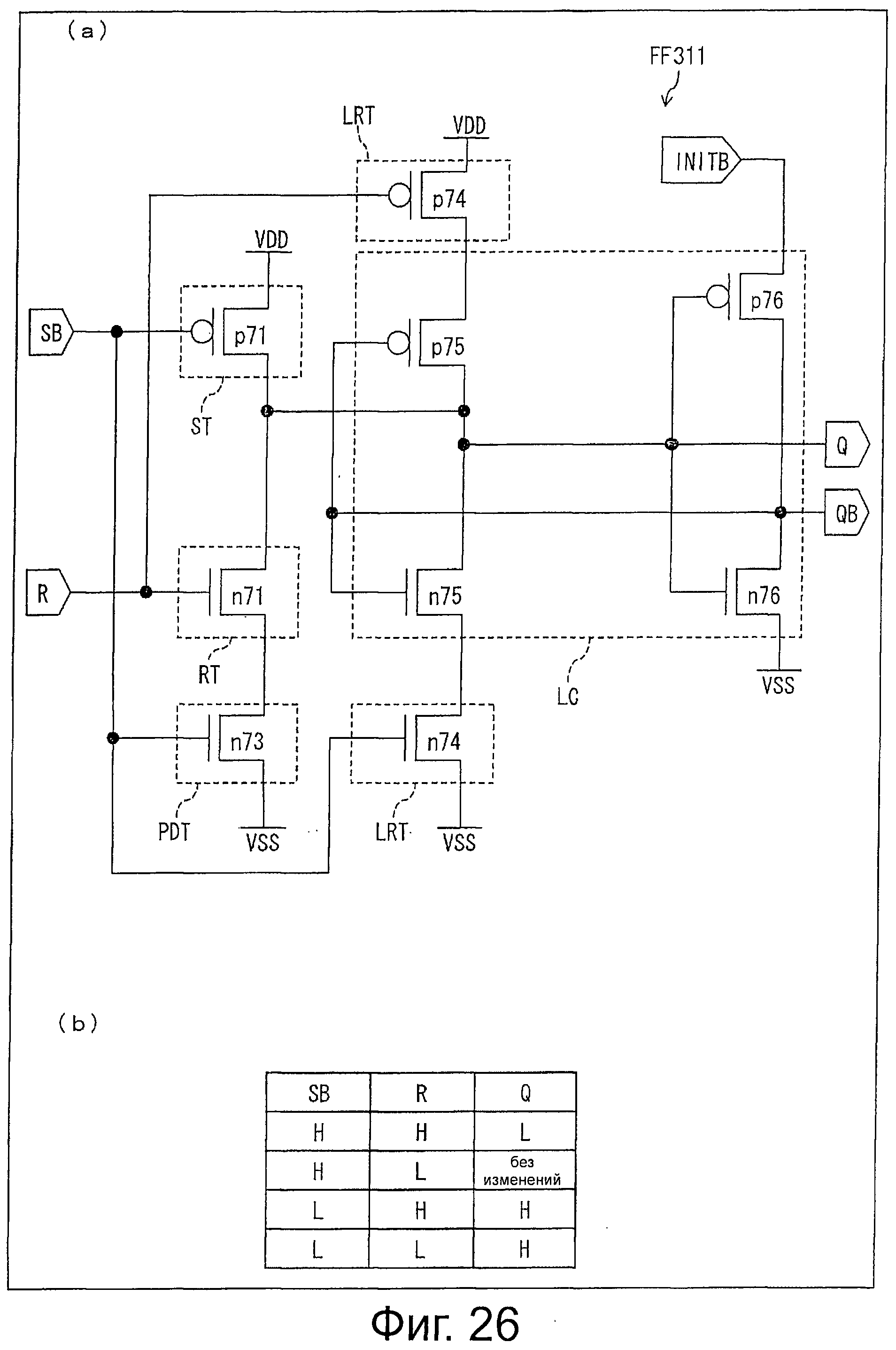

Фиг.26 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 1 настоящего изобретения: фиг.26 (а) показывает электрическую схему, фиг.26 (b) показывает таблицу истинности.

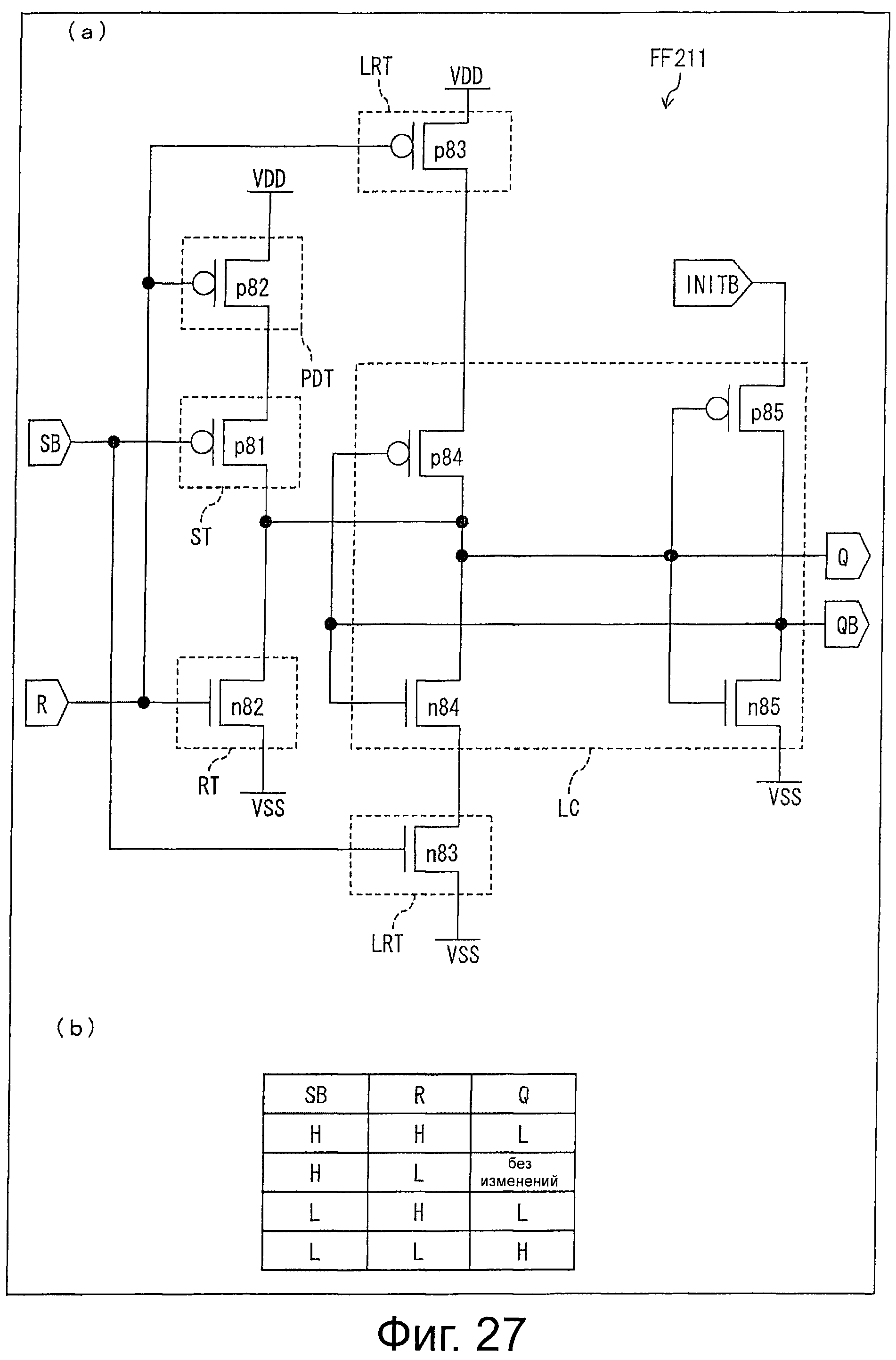

Фиг.27 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 1 настоящего изобретения: фиг.27 (а) показывает электрическую схему, фиг.27 (b) показывает таблицу истинности.

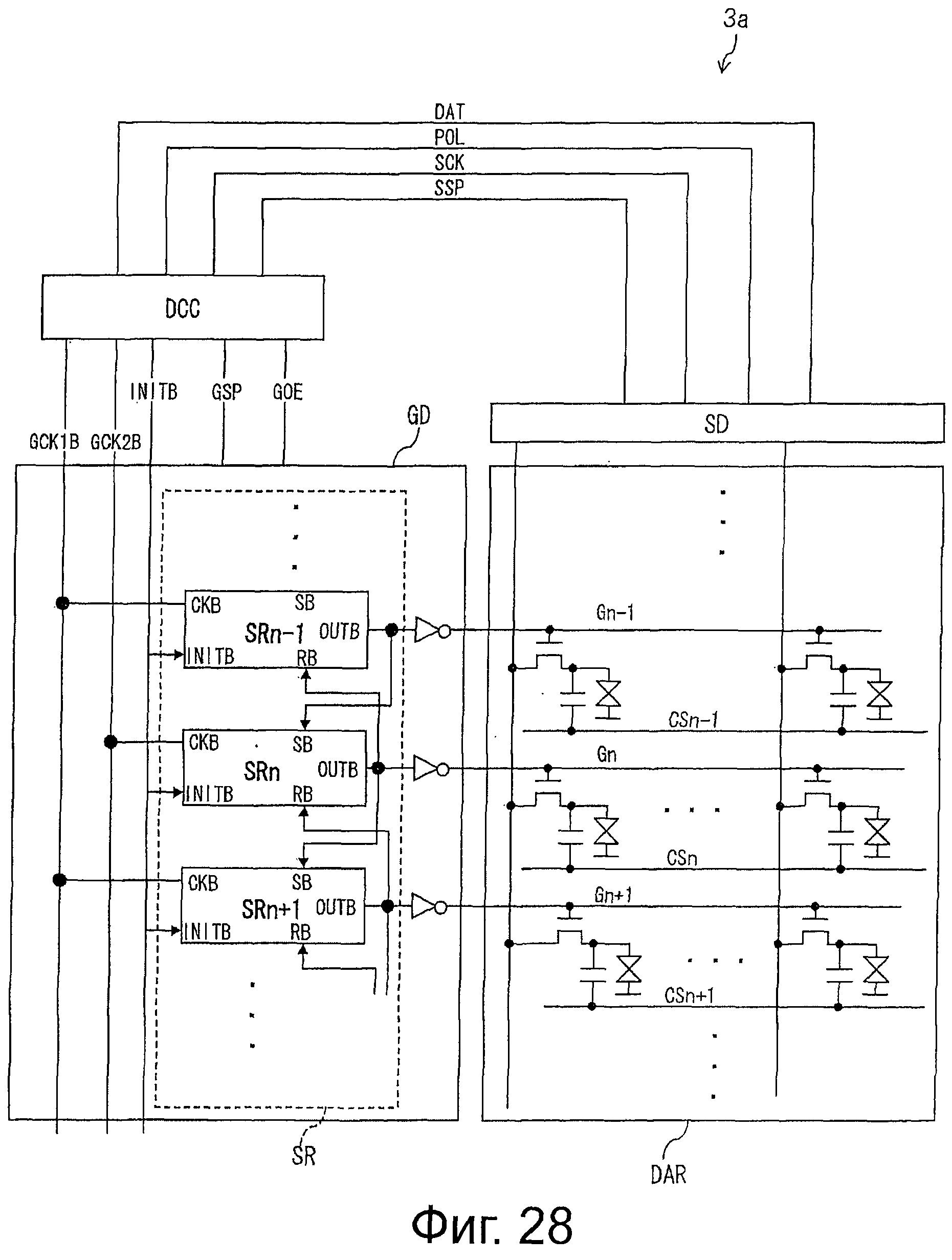

Фиг.28 представляет вид, схематично иллюстрирующий конфигурацию устройства отображения согласно настоящему изобретению.

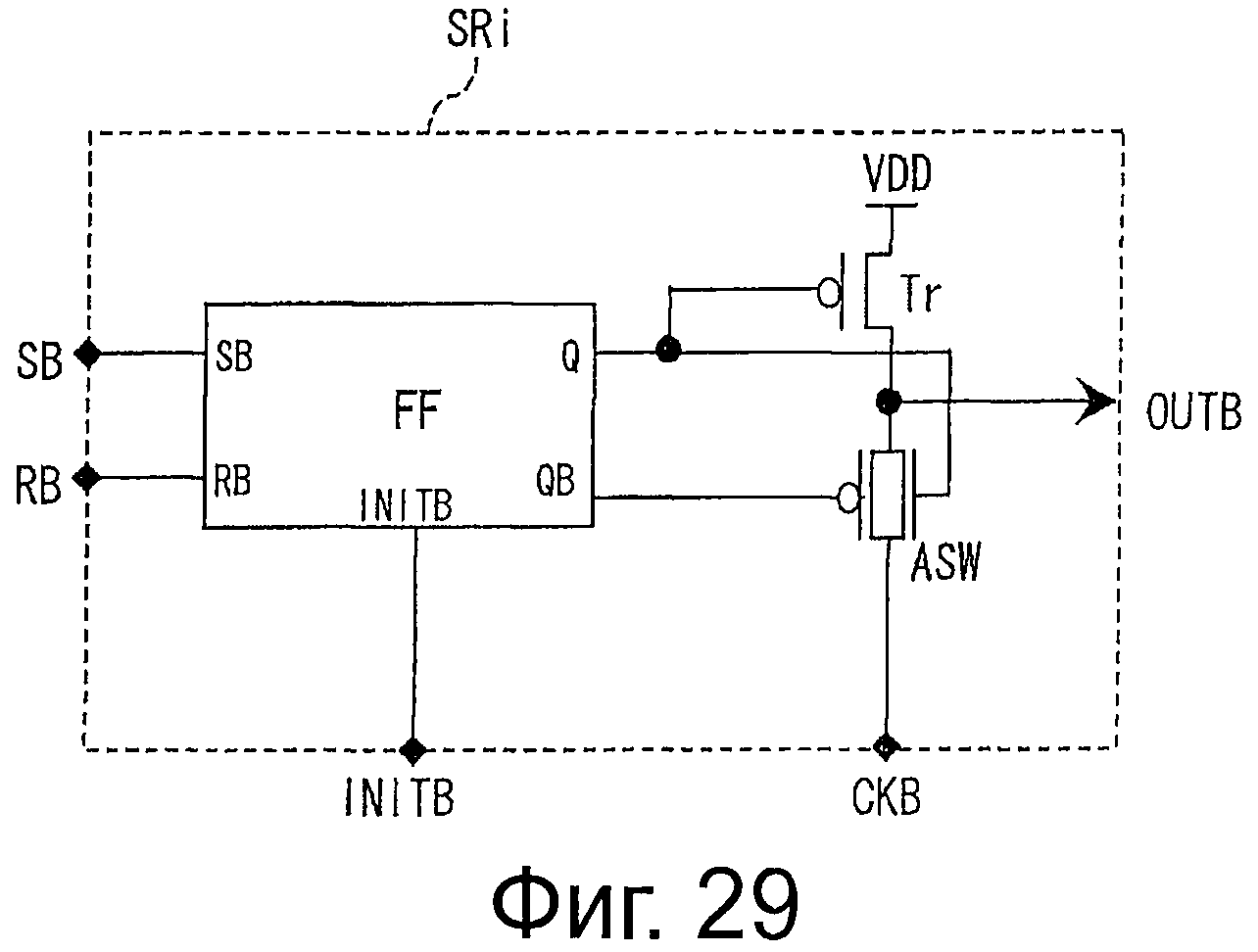

Фиг.29 представляет электрическую схему, иллюстрирующую каждый из нескольких каскадов регистра сдвига в устройстве отображения, показанном на фиг.28.

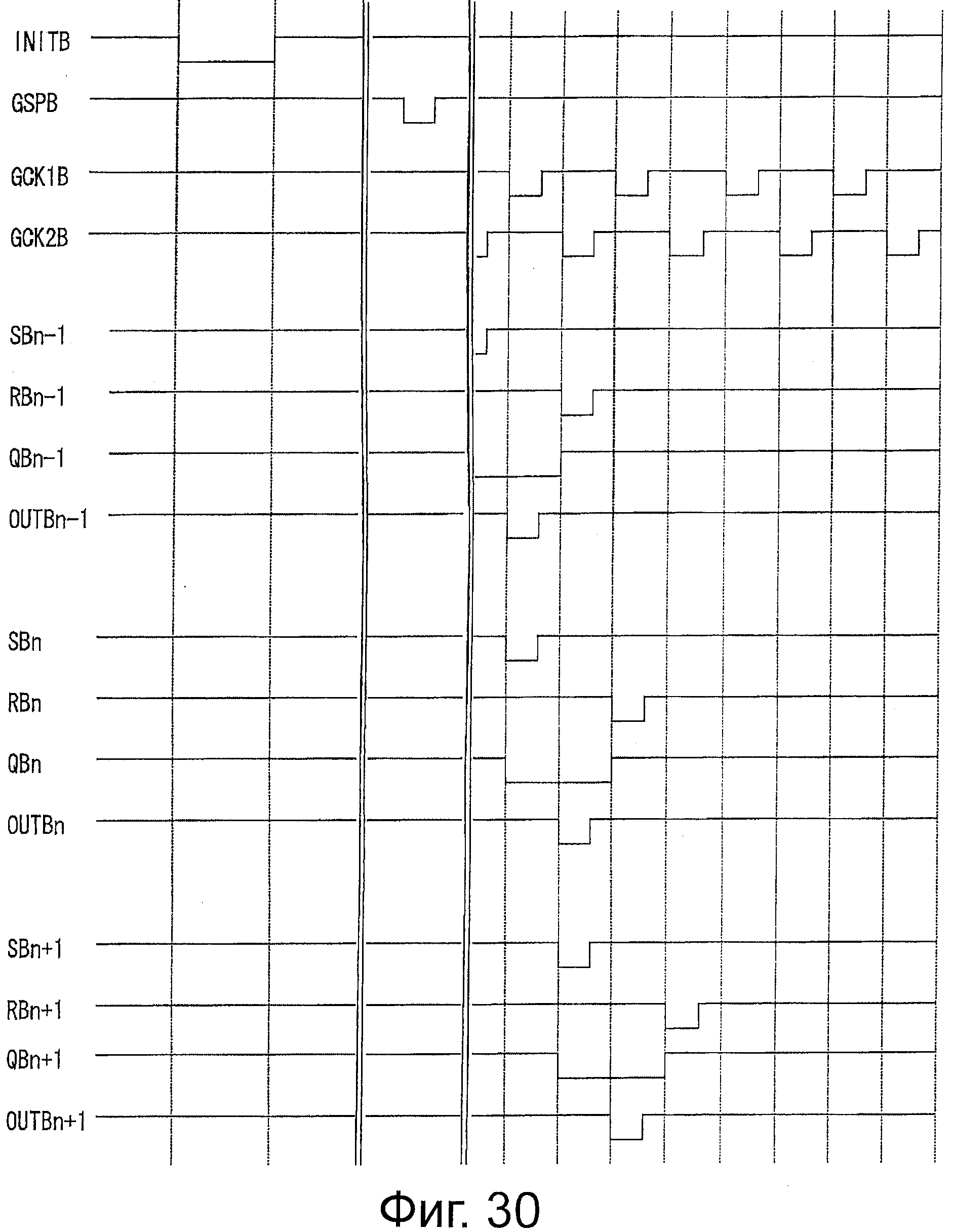

Фиг.30 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.28.

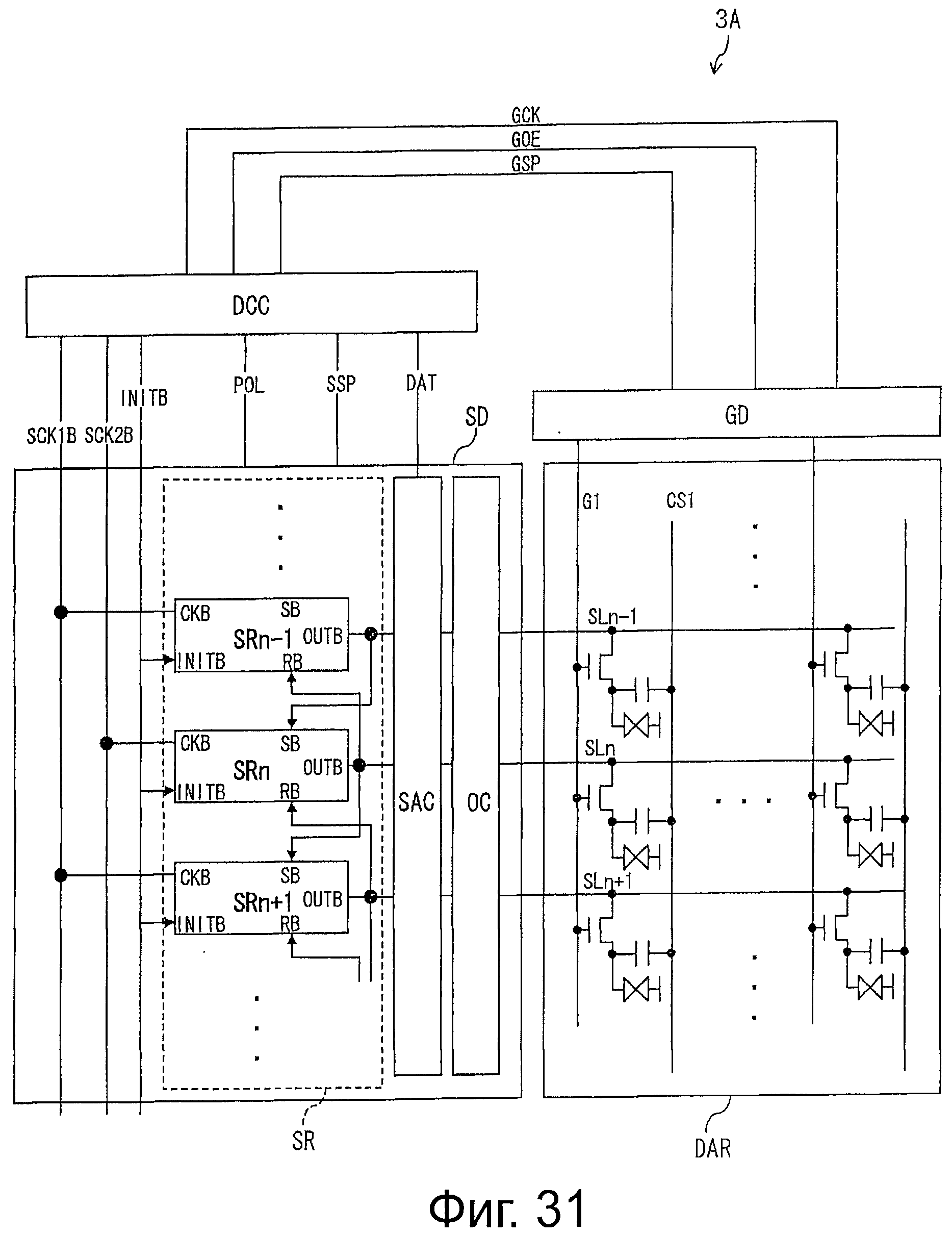

Фиг.31 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

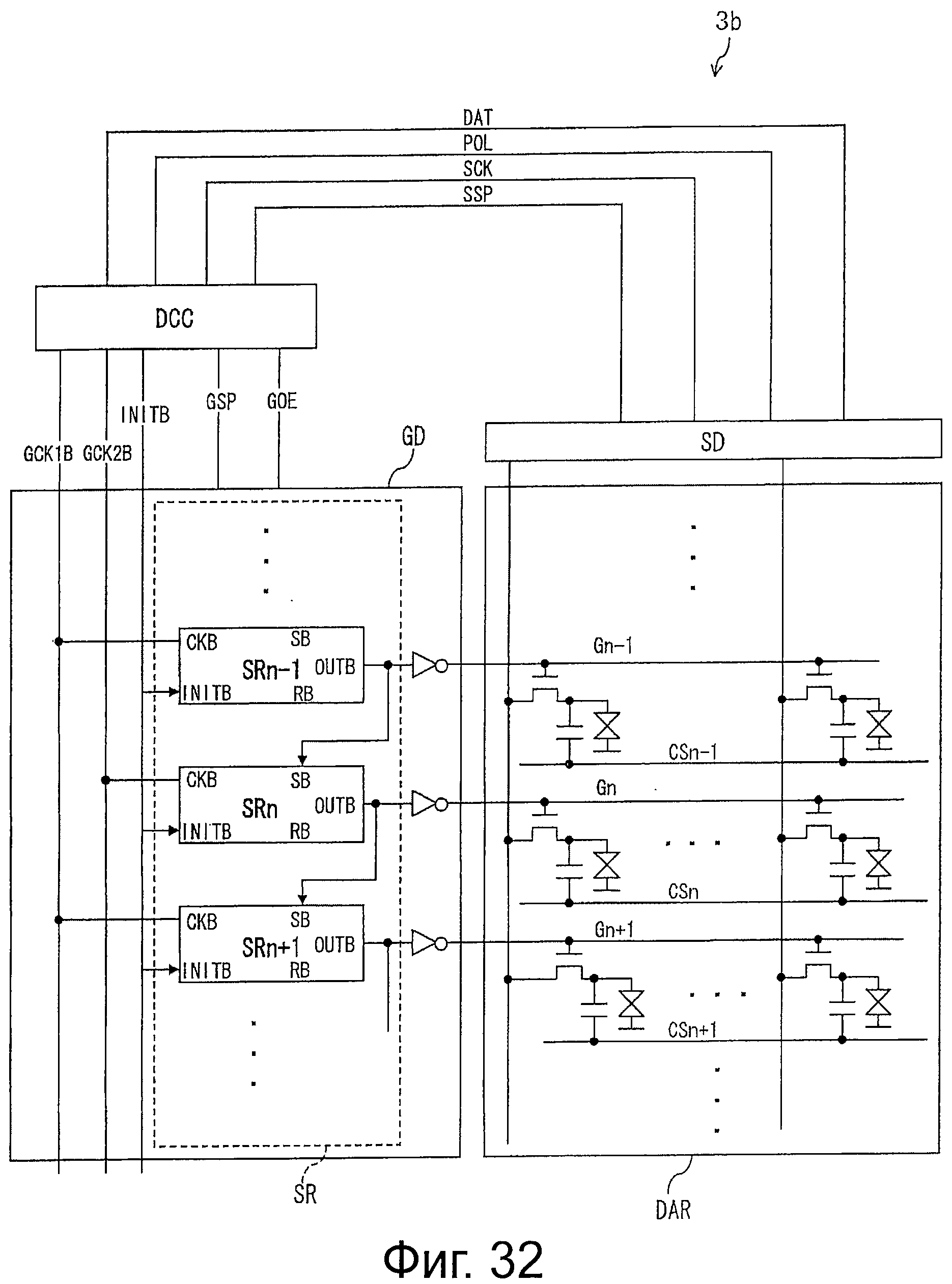

Фиг.32 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

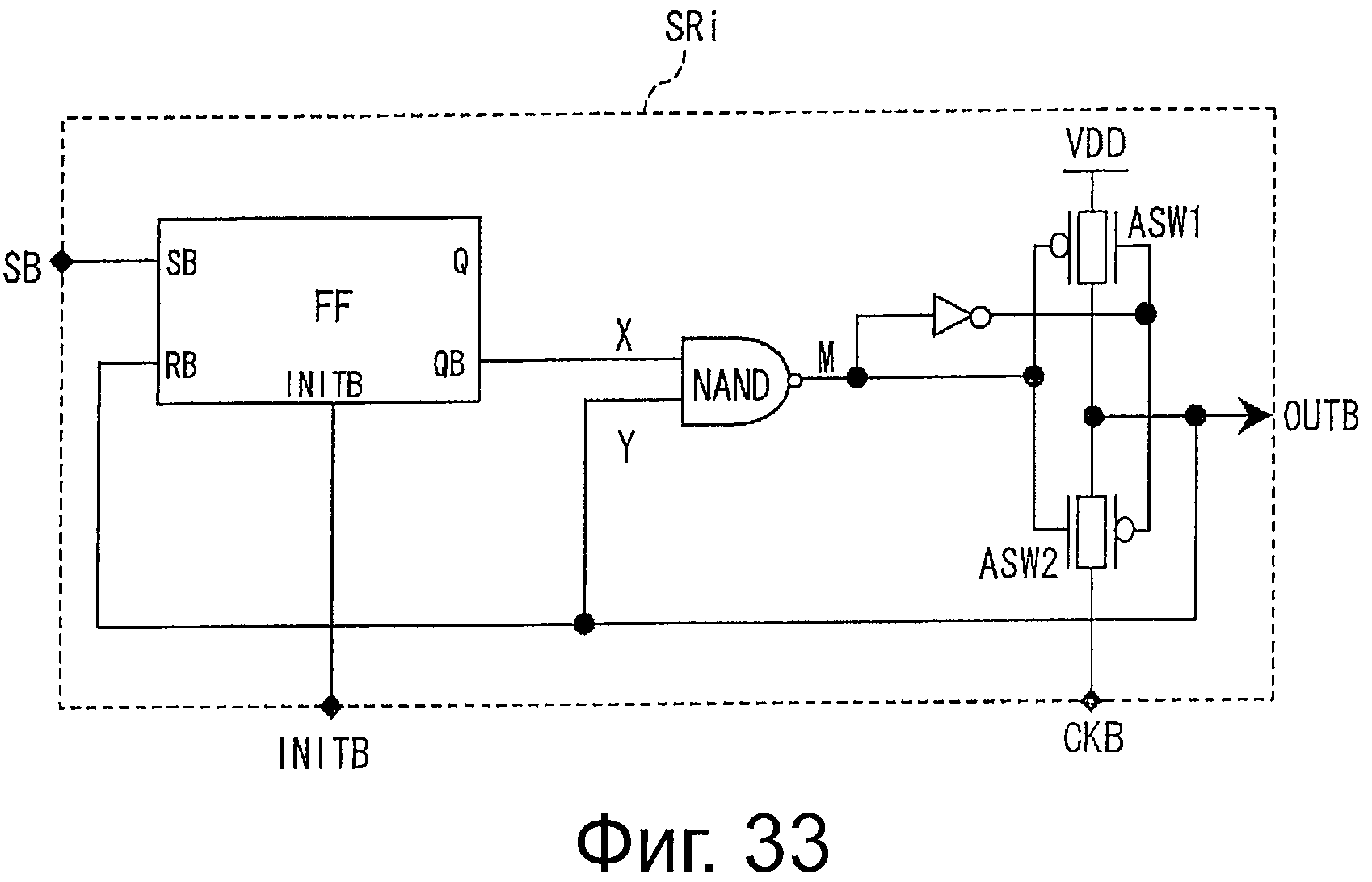

Фиг.33 представляет электрическую схему, иллюстрирующую каждый из нескольких каскадов регистра сдвига в устройстве отображения, показанном на фиг.32.

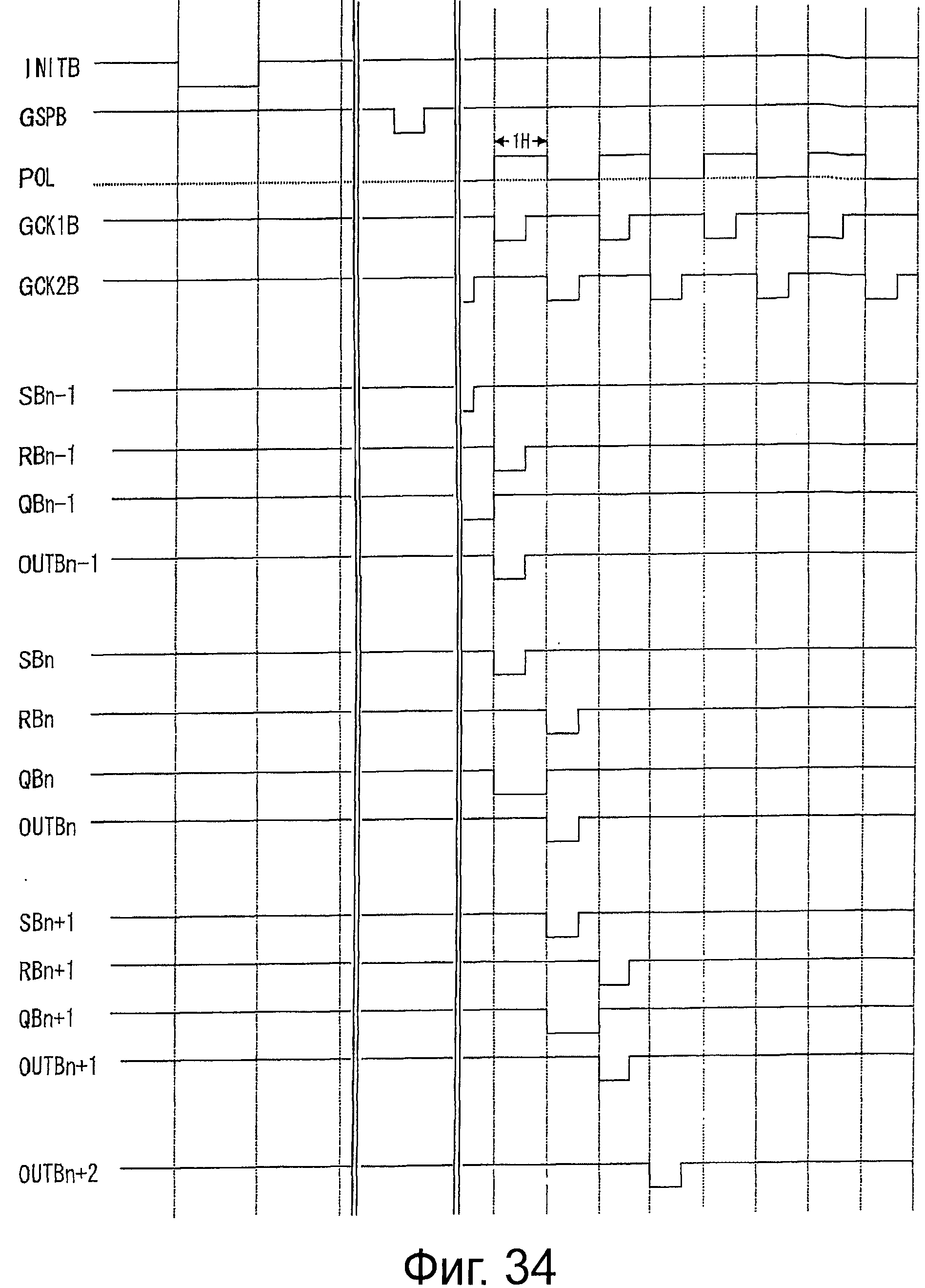

Фиг.34 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.32.

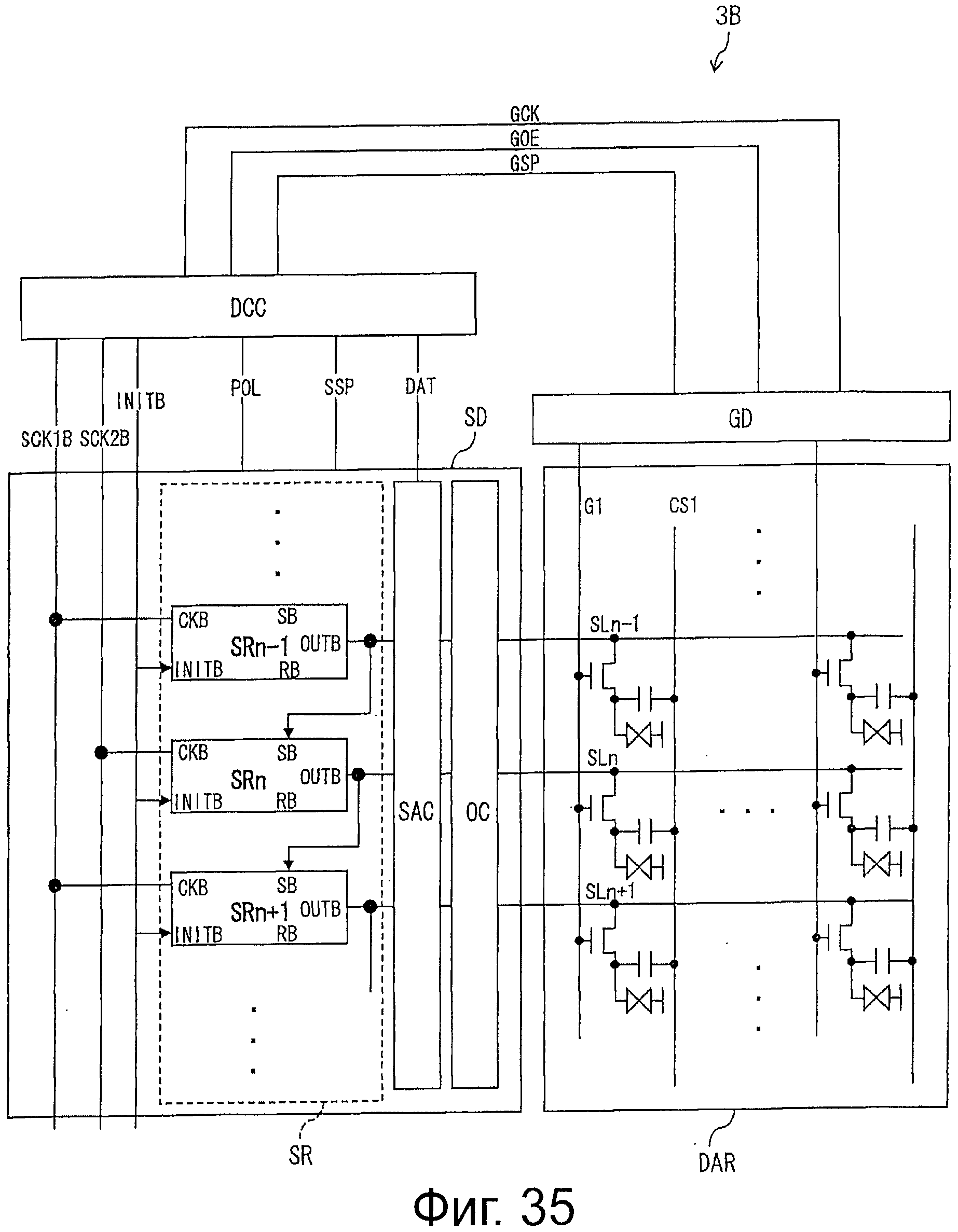

Фиг.35 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

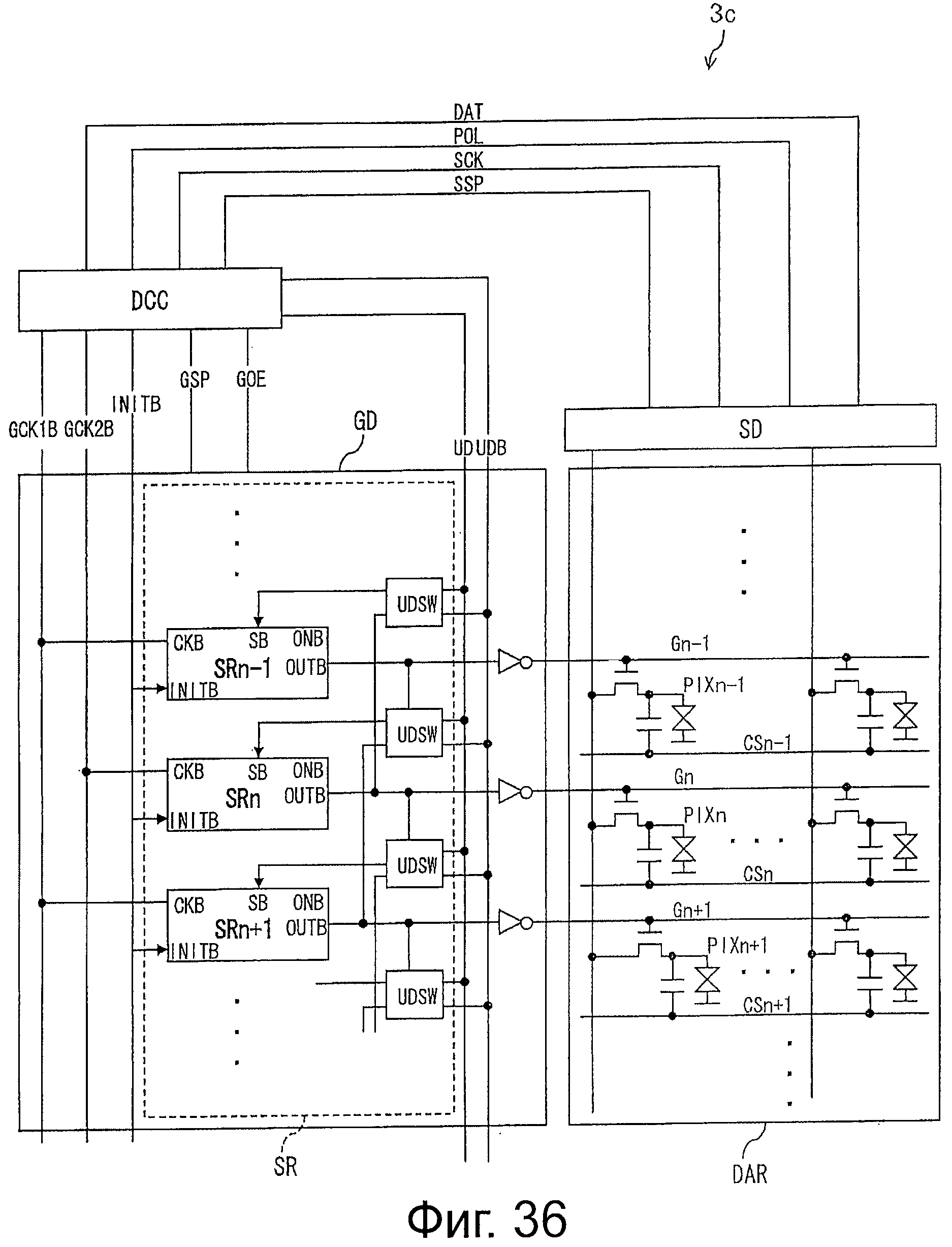

Фиг.36 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

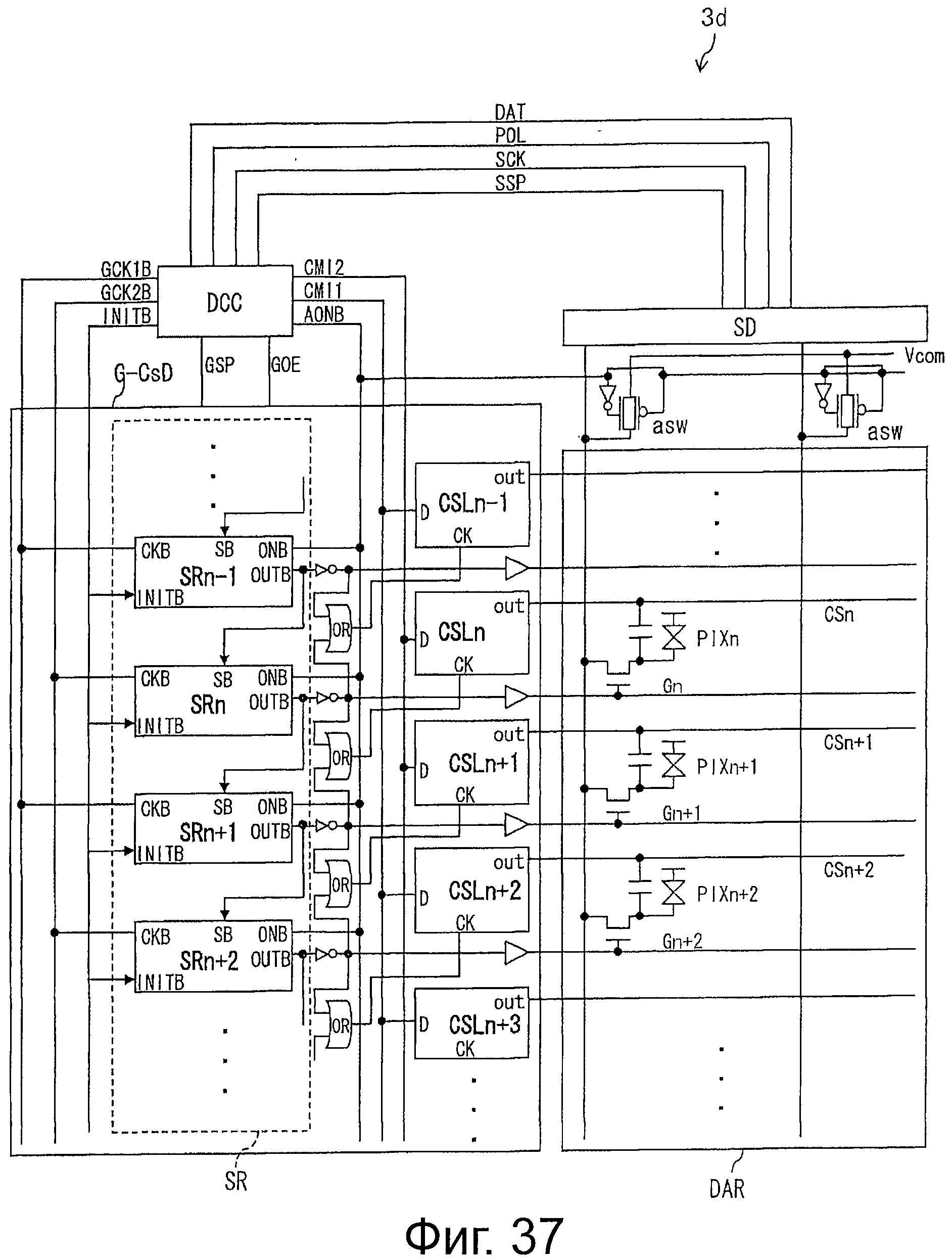

Фиг.37 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

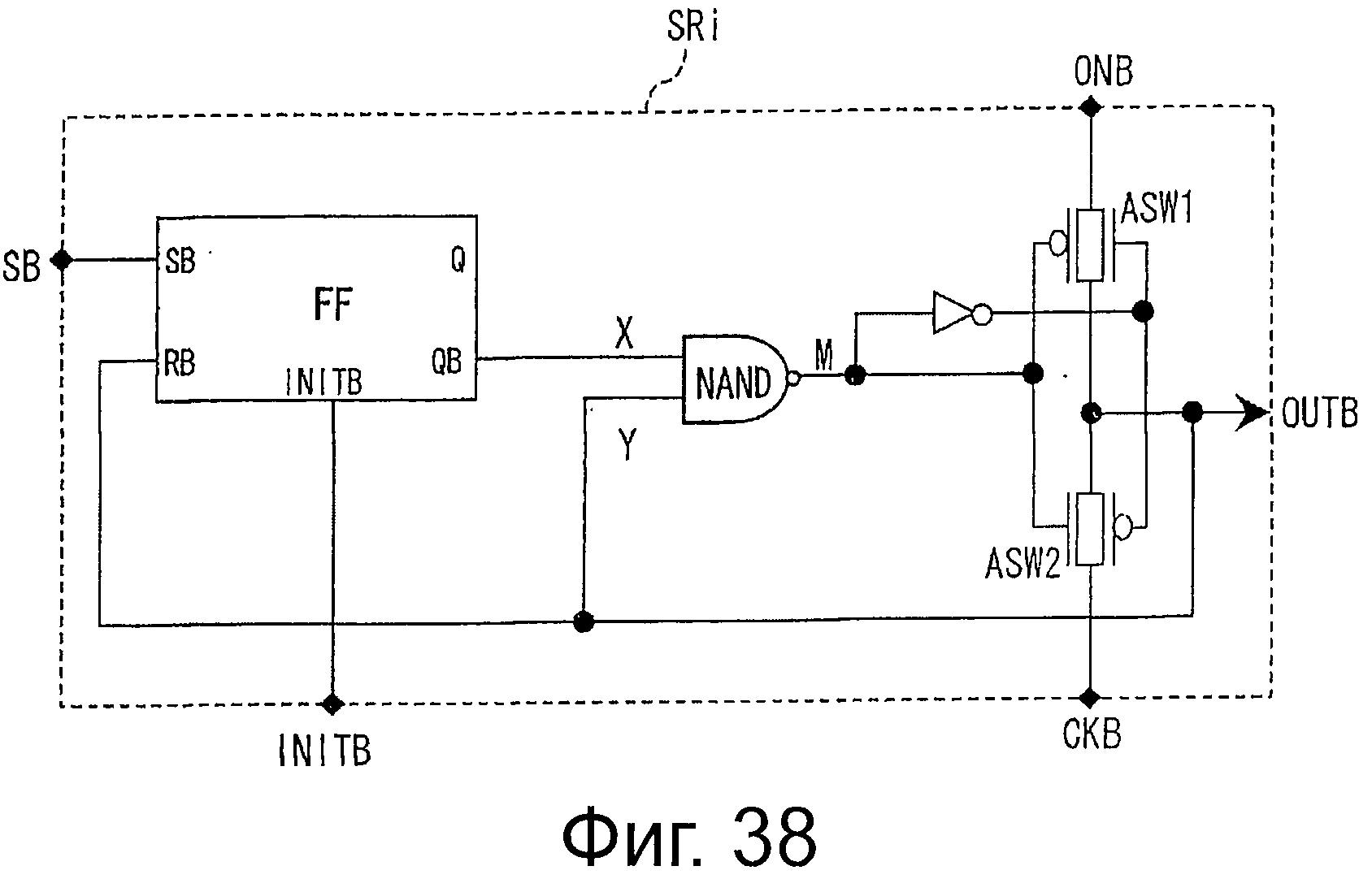

Фиг.38 представляет электрическую схему, иллюстрирующую каждый из нескольких каскадов регистра сдвига в устройстве отображения, показанном на фиг.37.

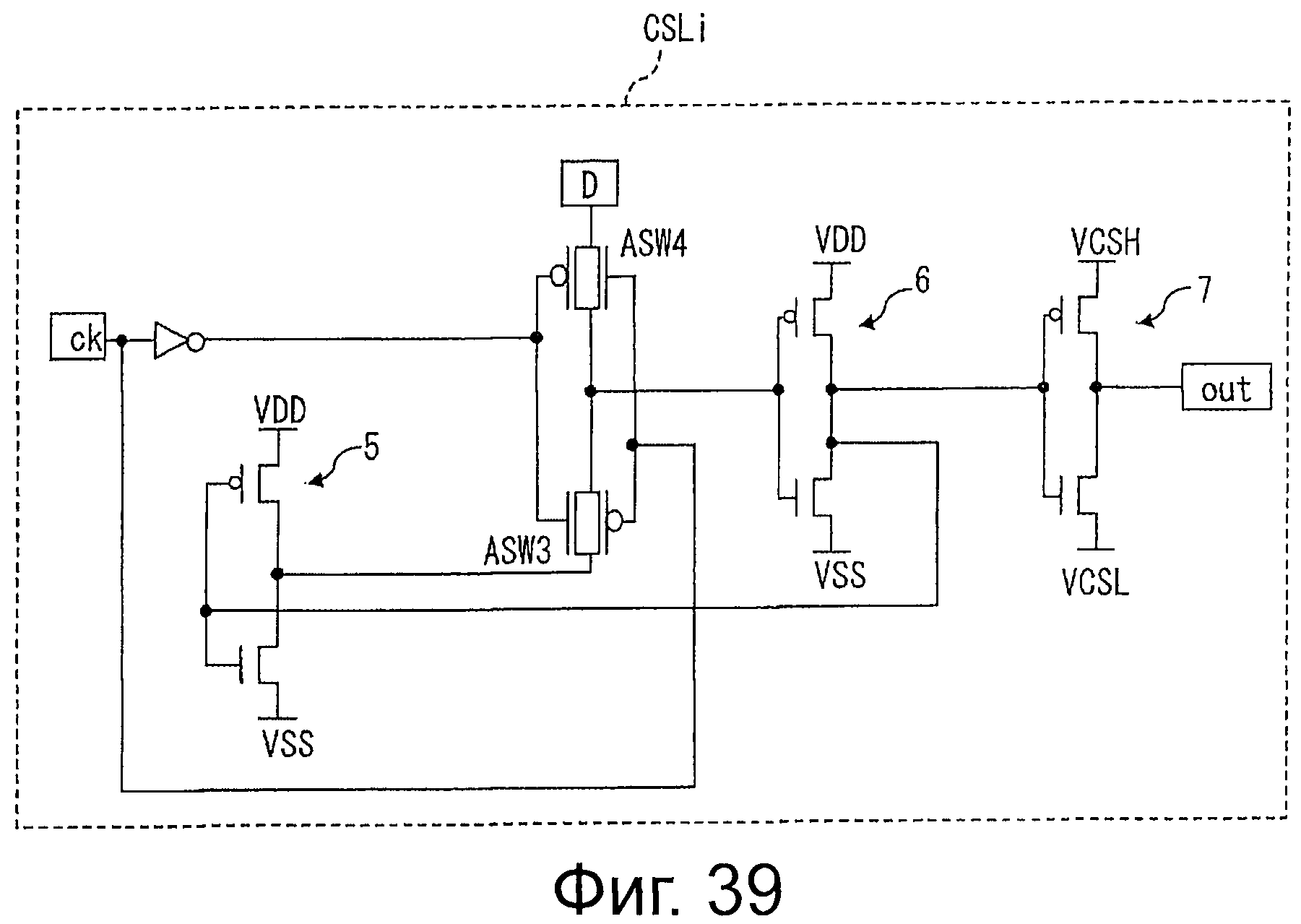

Фиг.39 представляет электрическую схему, показывающую D-защелку в схеме возбуждения G-Gs устройства отображения, изображенного на фиг.37.

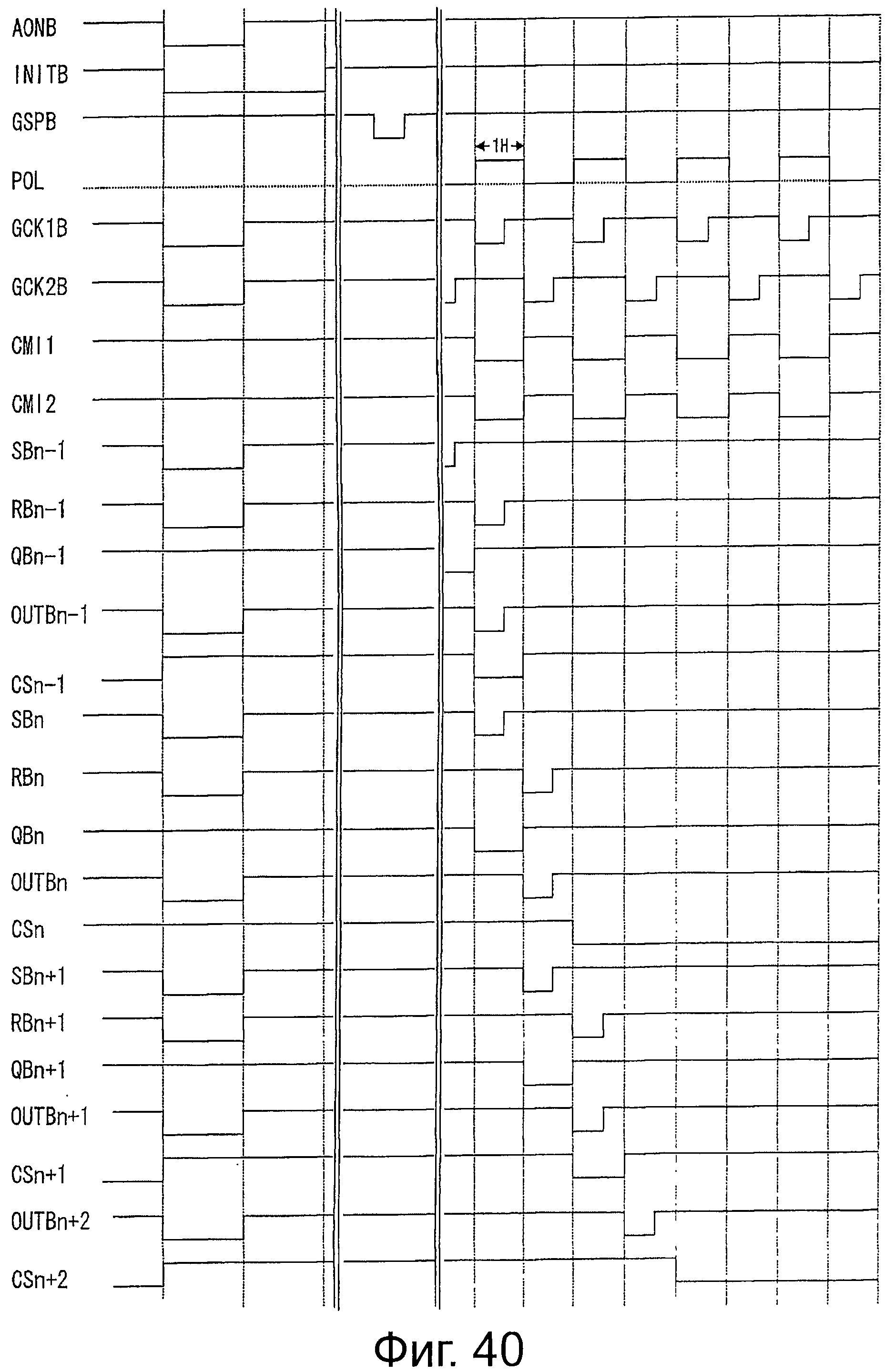

Фиг.40 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.37.

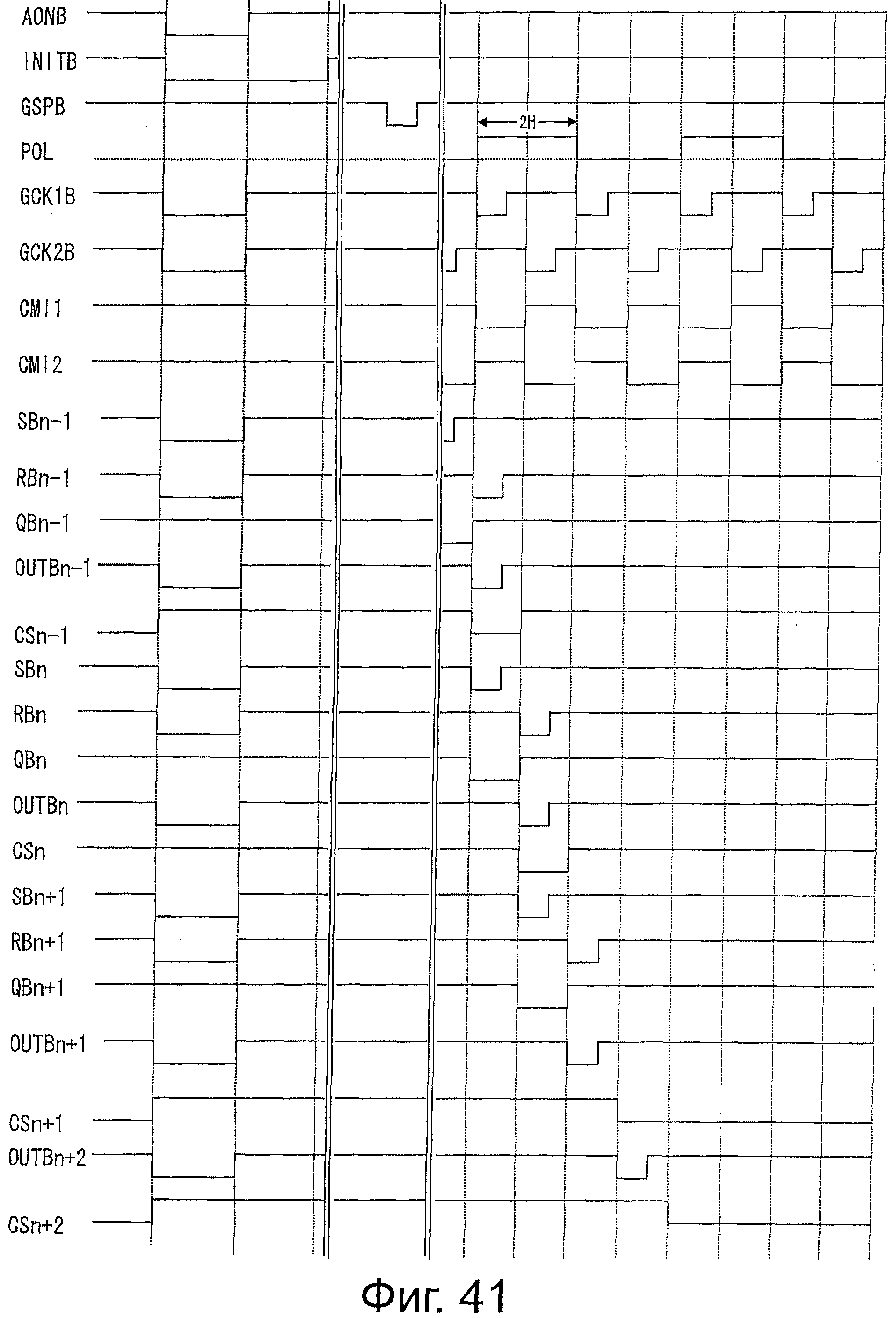

Фиг.41 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.37.

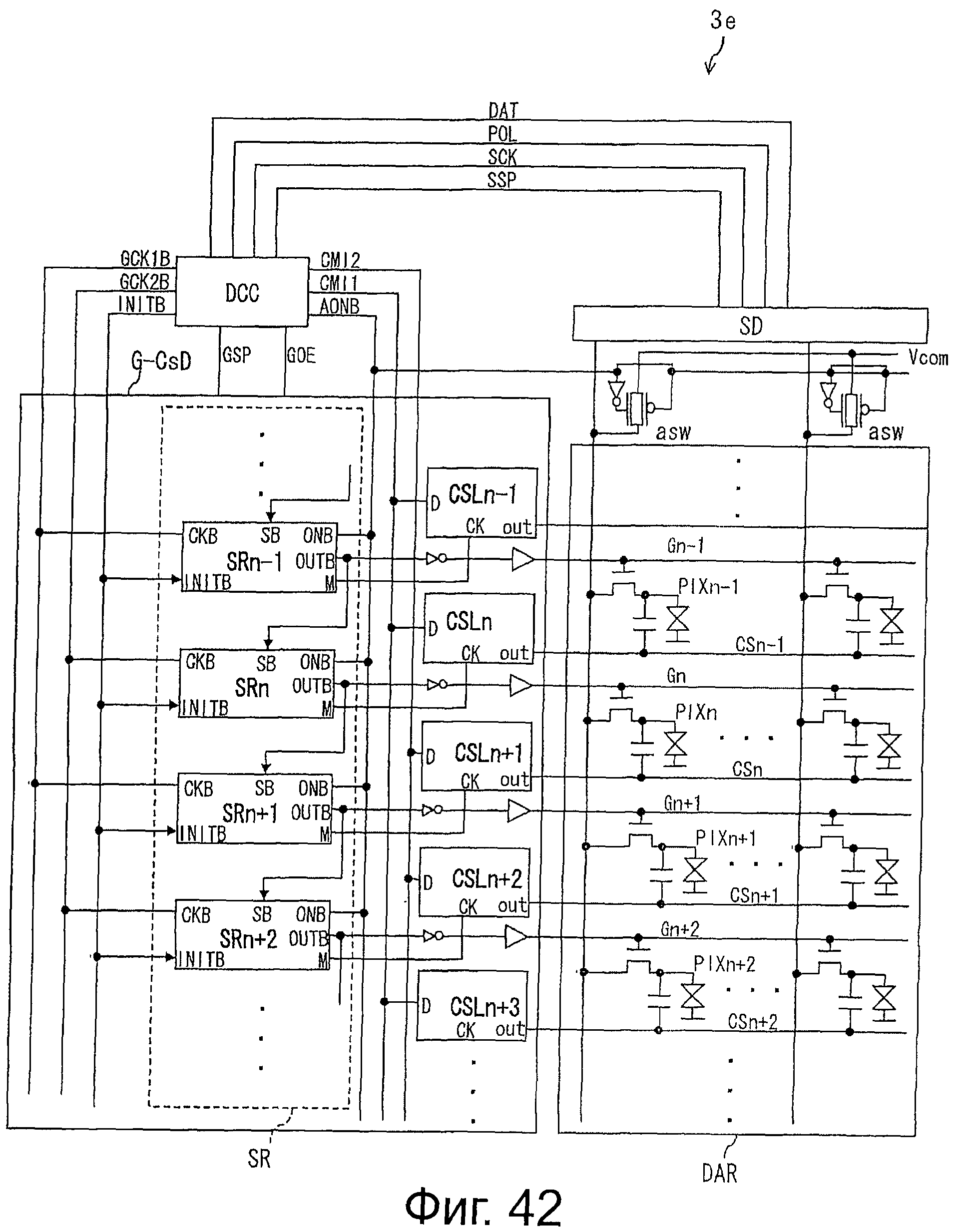

Фиг.42 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

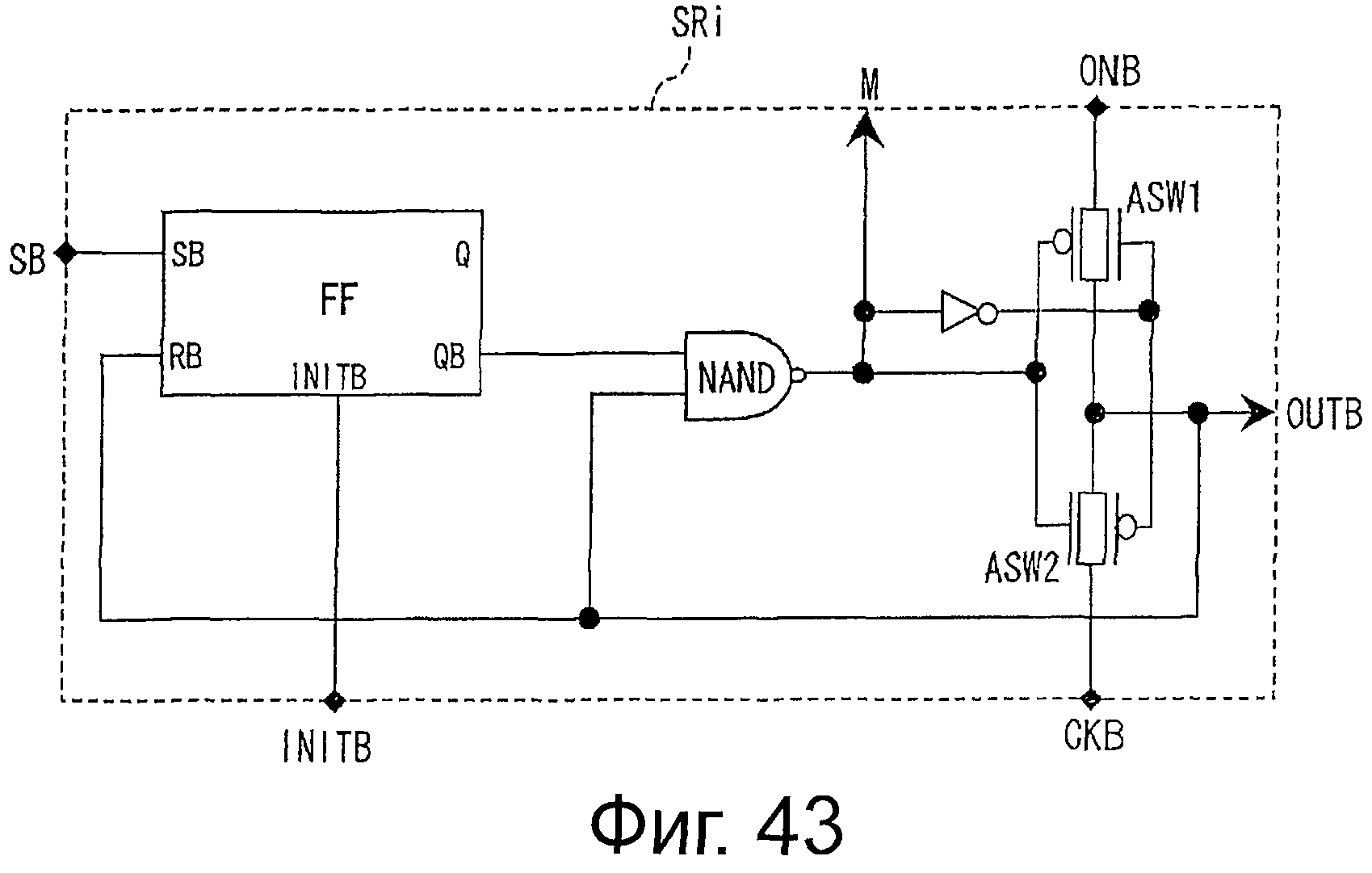

Фиг.43 представляет электрическую схему, иллюстрирующую каждый из нескольких каскадов регистра сдвига в устройстве отображения, показанном на фиг.42.

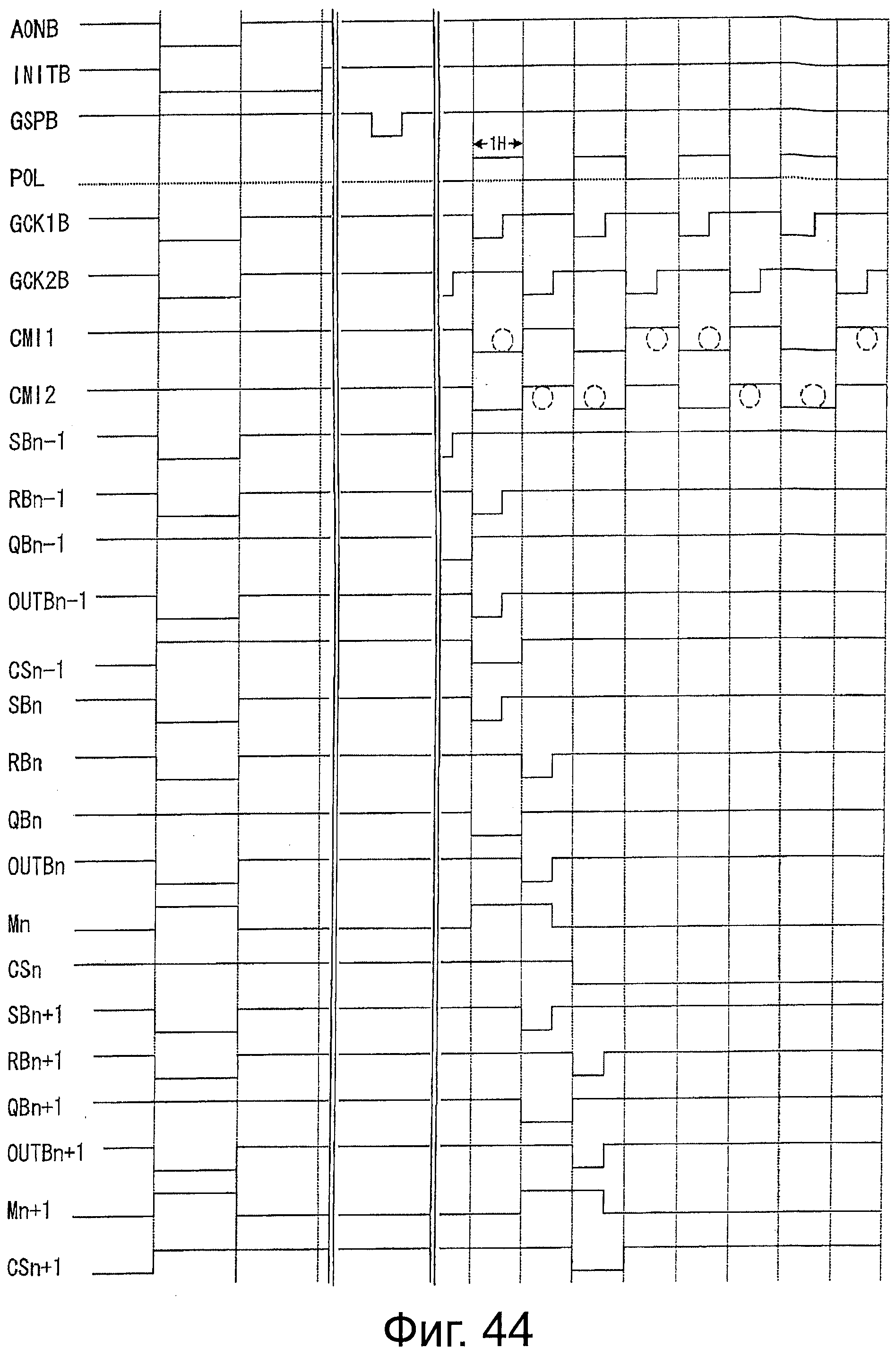

Фиг.44 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.42.

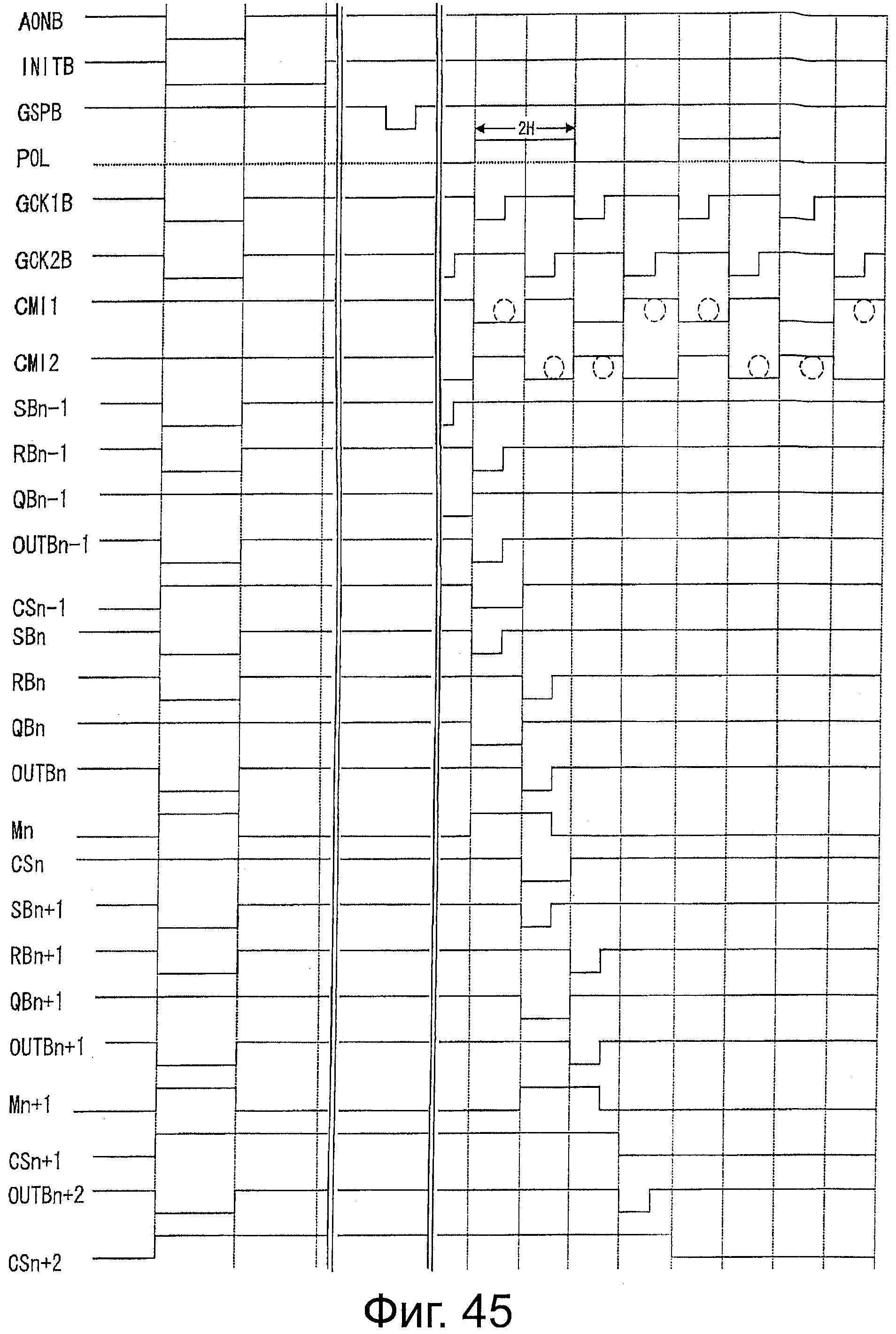

Фиг.45 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.42.

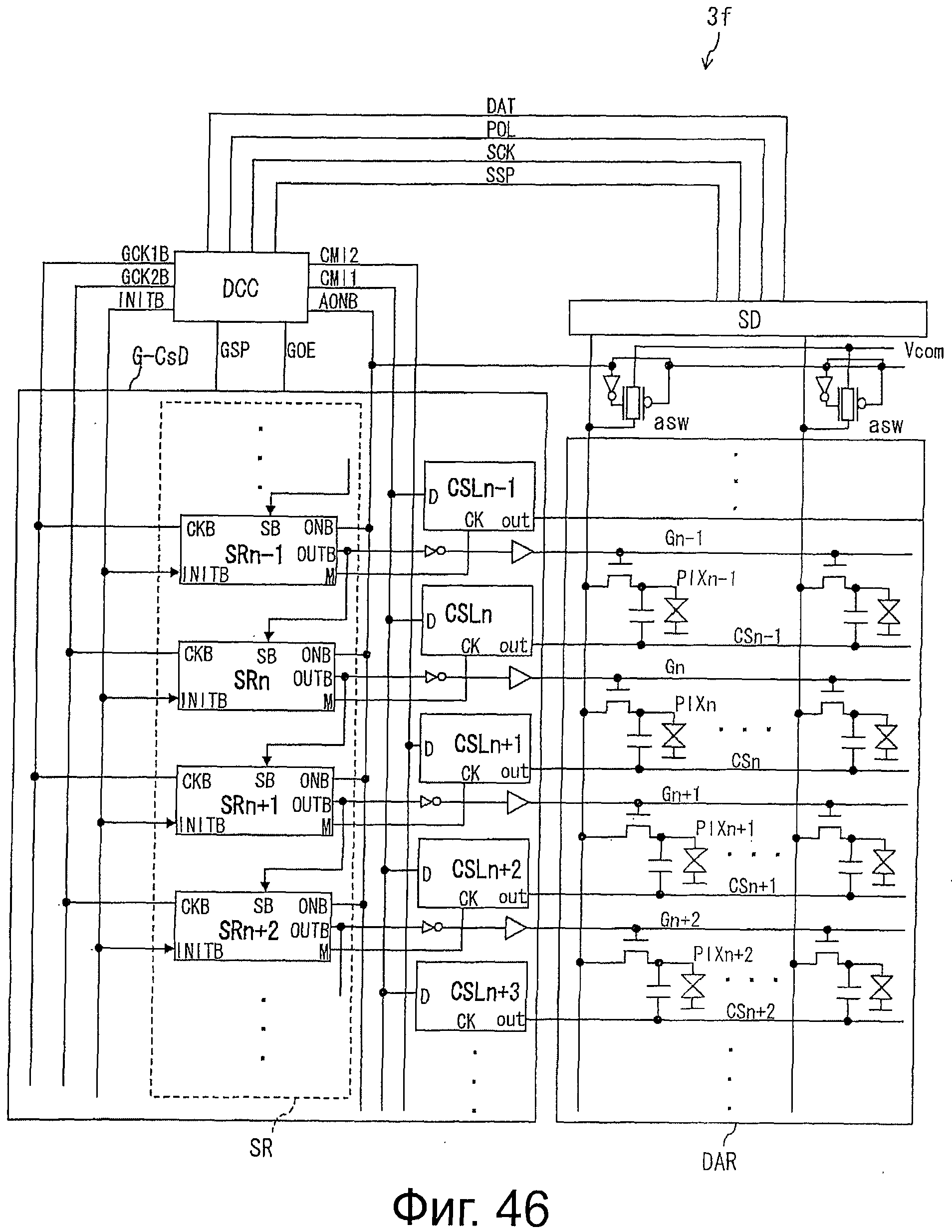

Фиг.46 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

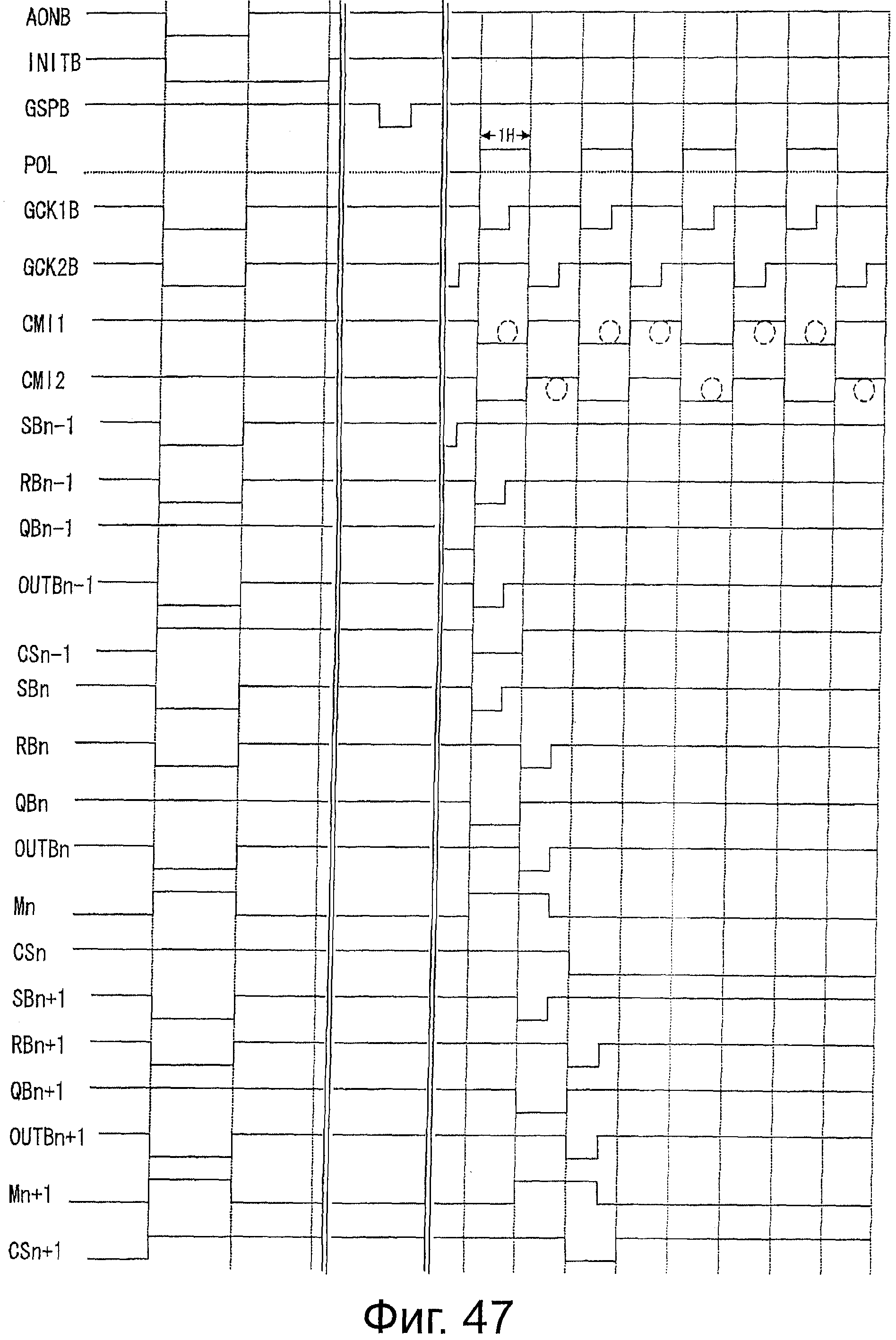

Фиг.47 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.46.

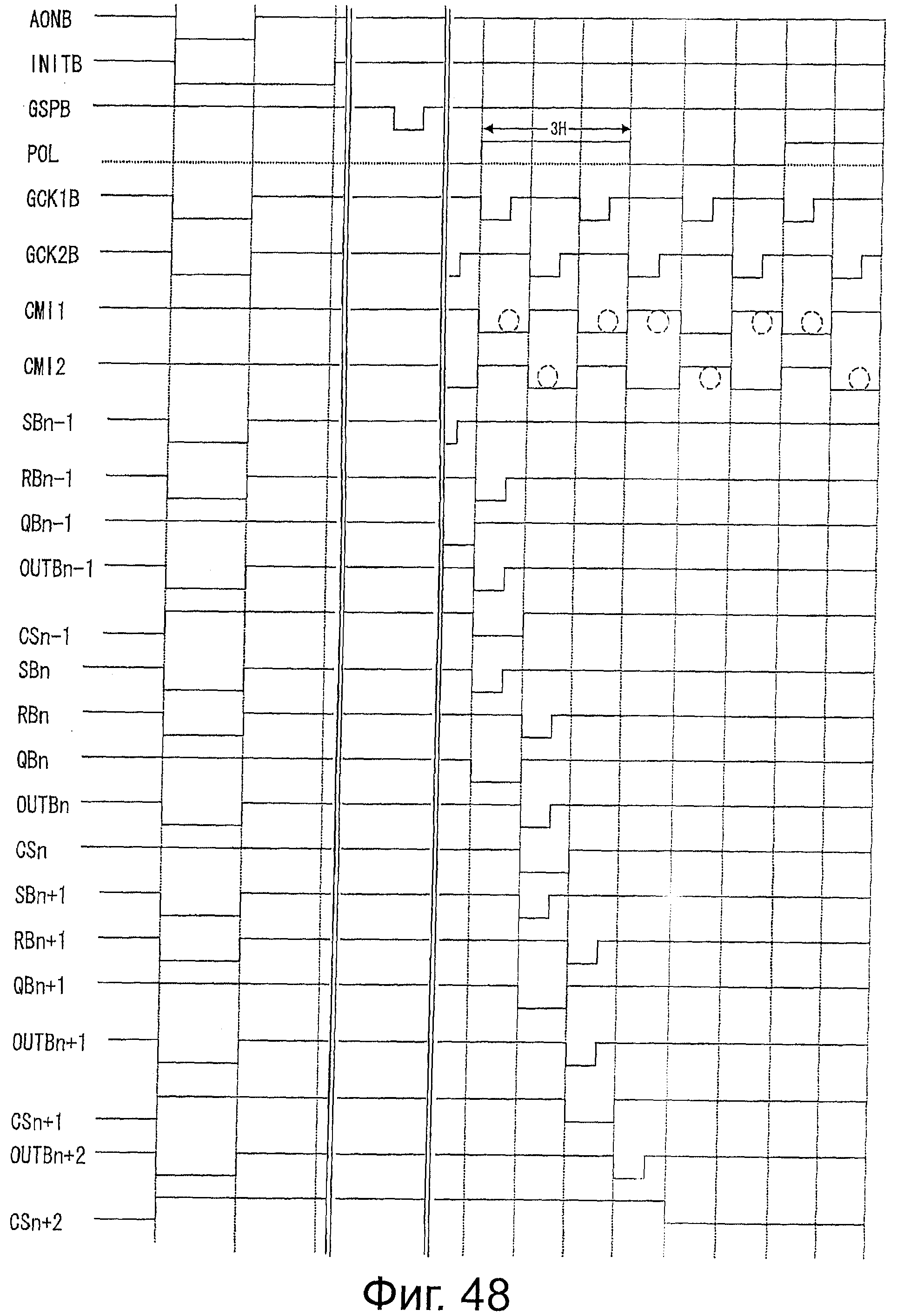

Фиг.48 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.46.

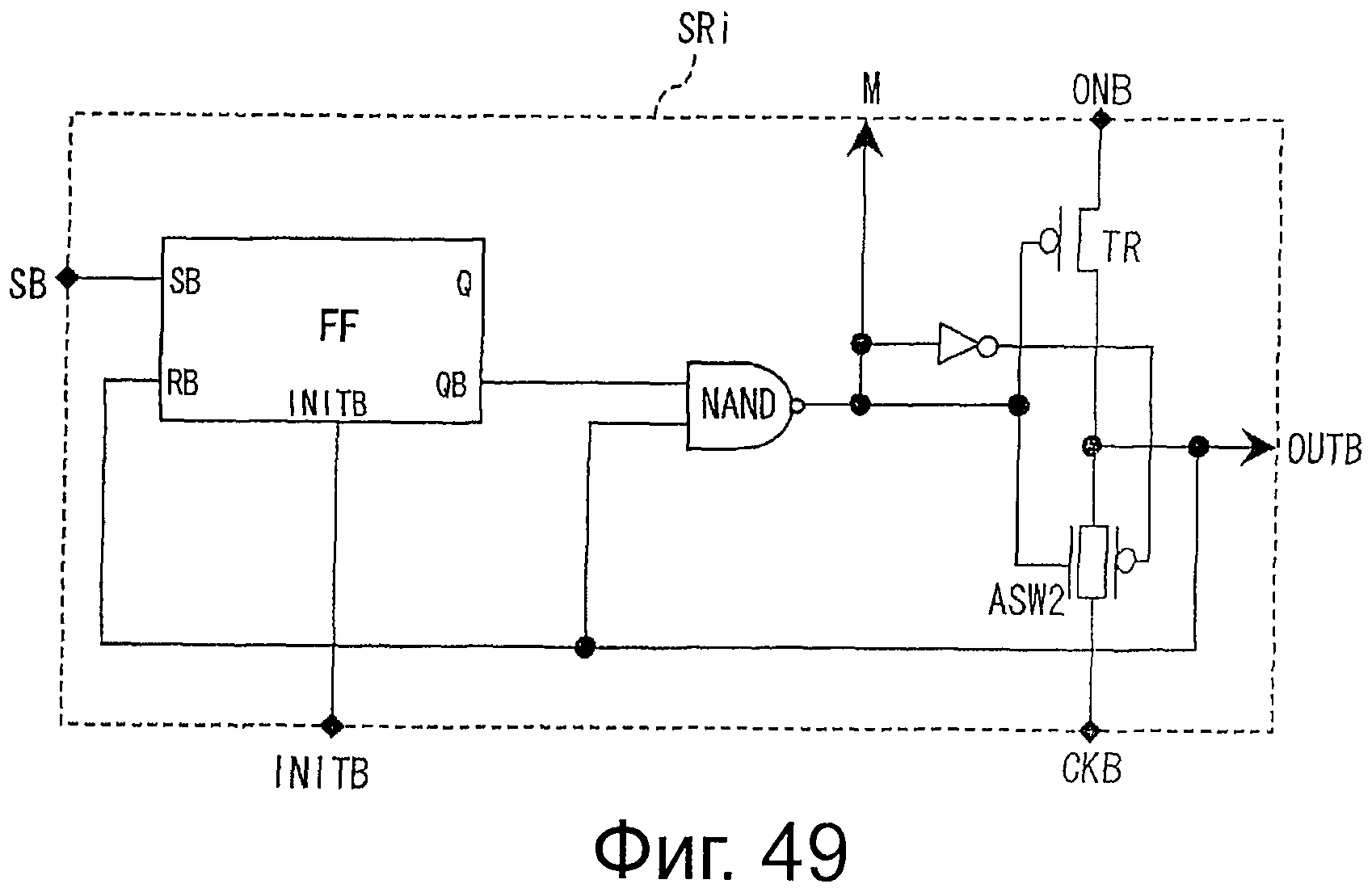

Фиг.49 представляет электрическую схему, иллюстрирующую модифицированный пример схемы, изображенной на фиг.43.

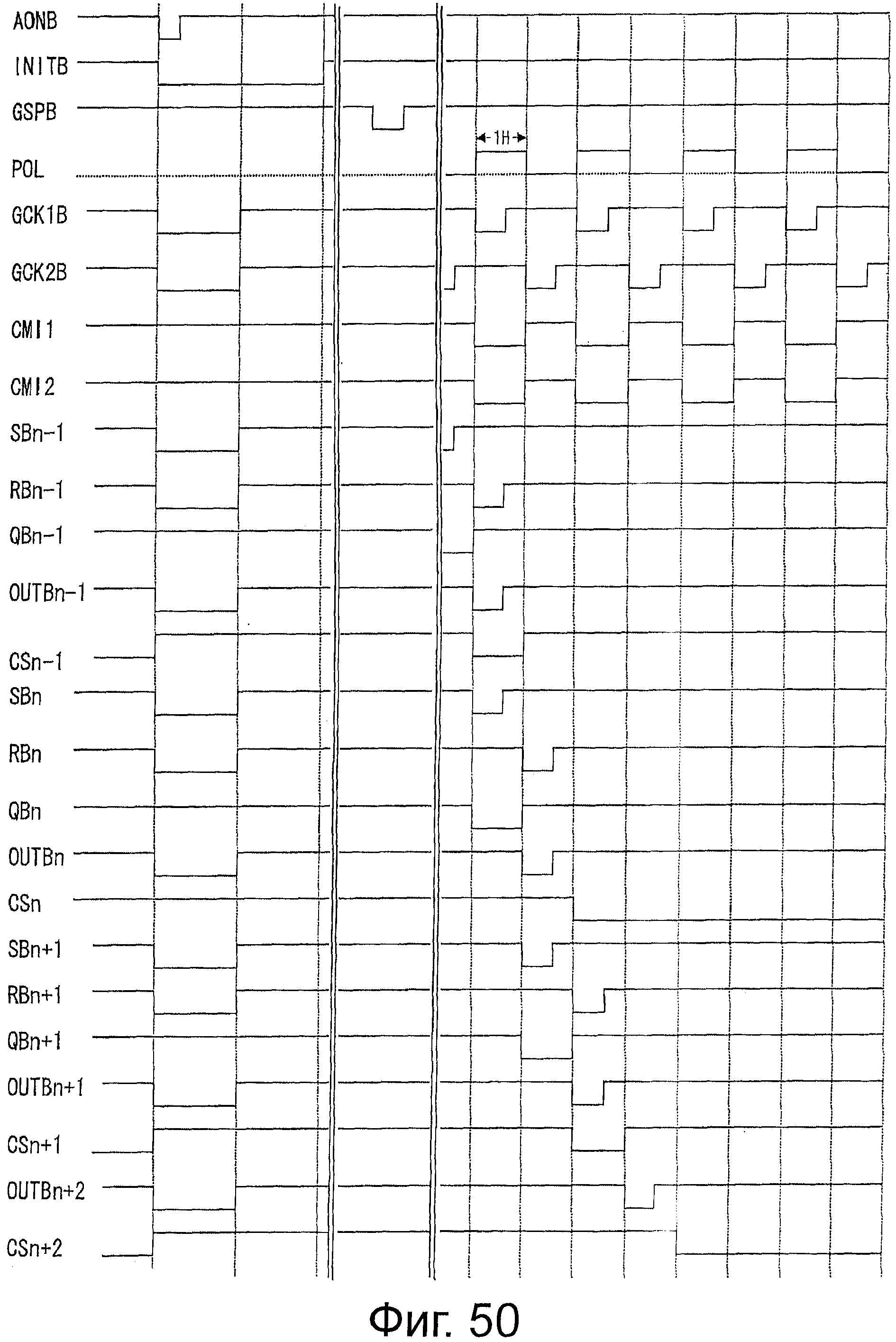

Фиг.50 представляет временную диаграмму, показывающую модифицированный пример временной диаграммы, изображенной на фиг.40 или фиг.44.

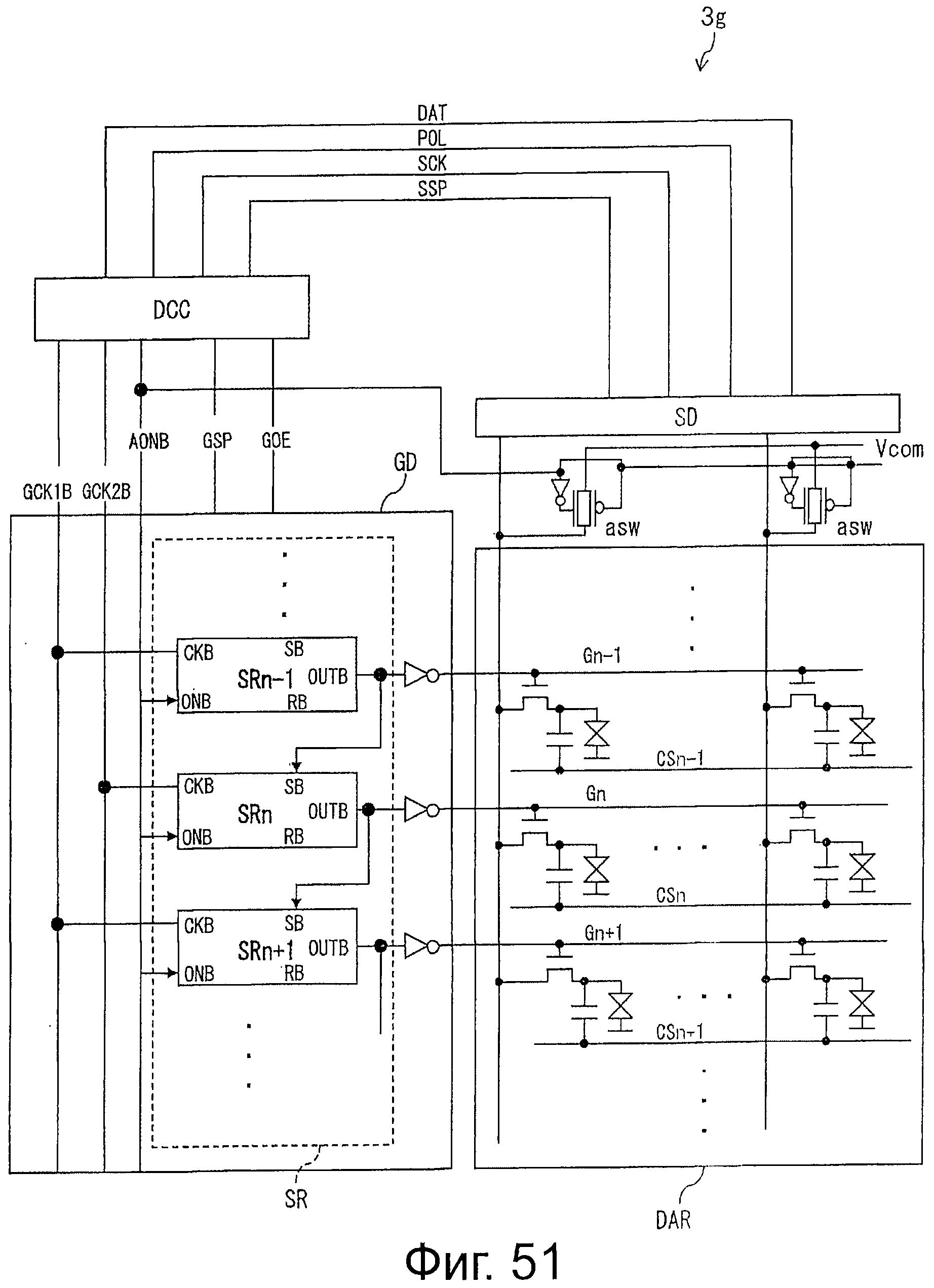

Фиг.51 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

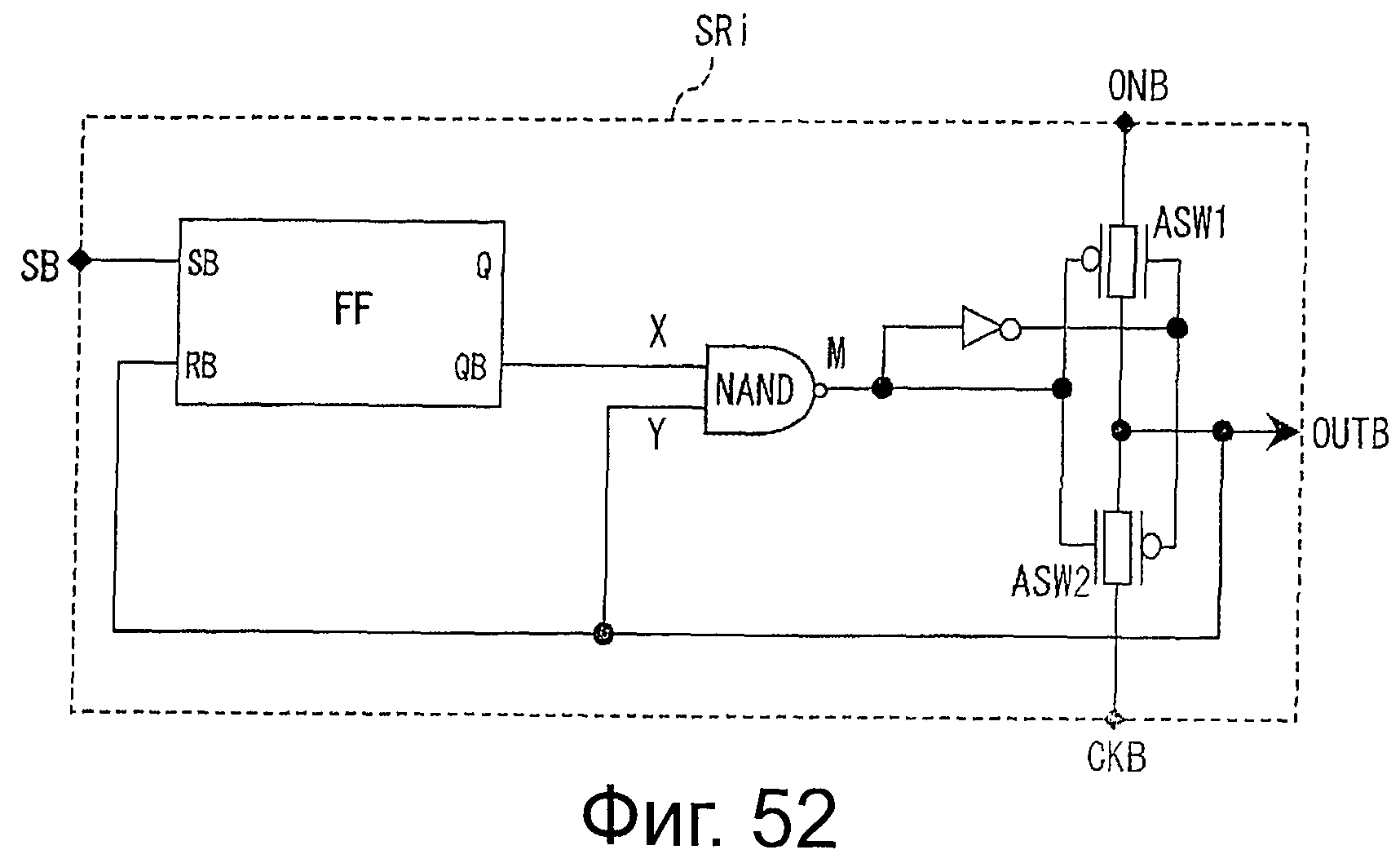

Фиг.52 представляет электрическую схему, иллюстрирующую каждый из нескольких каскадов регистра сдвига в устройстве отображения, показанном на фиг.51.

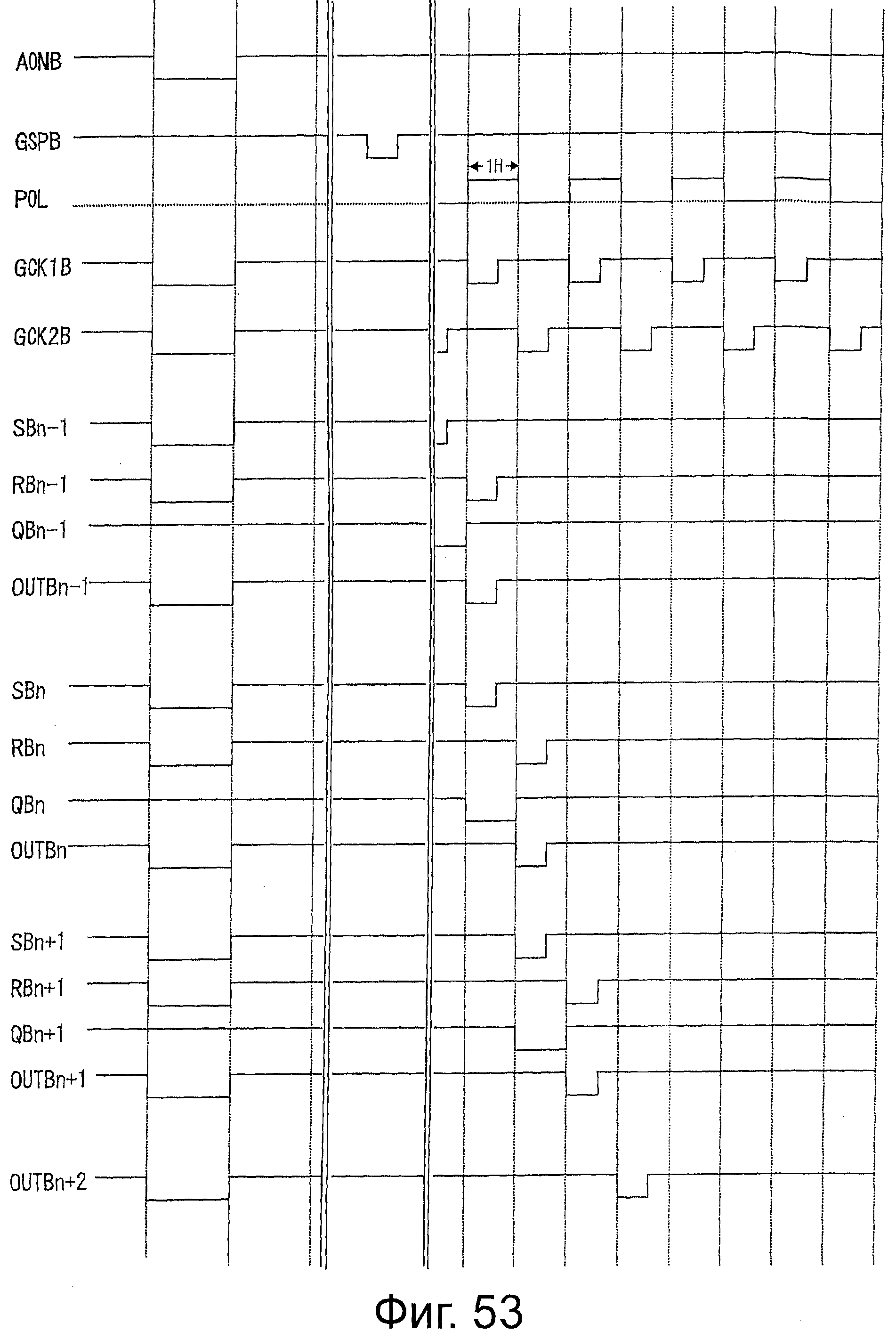

Фиг.53 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.51.

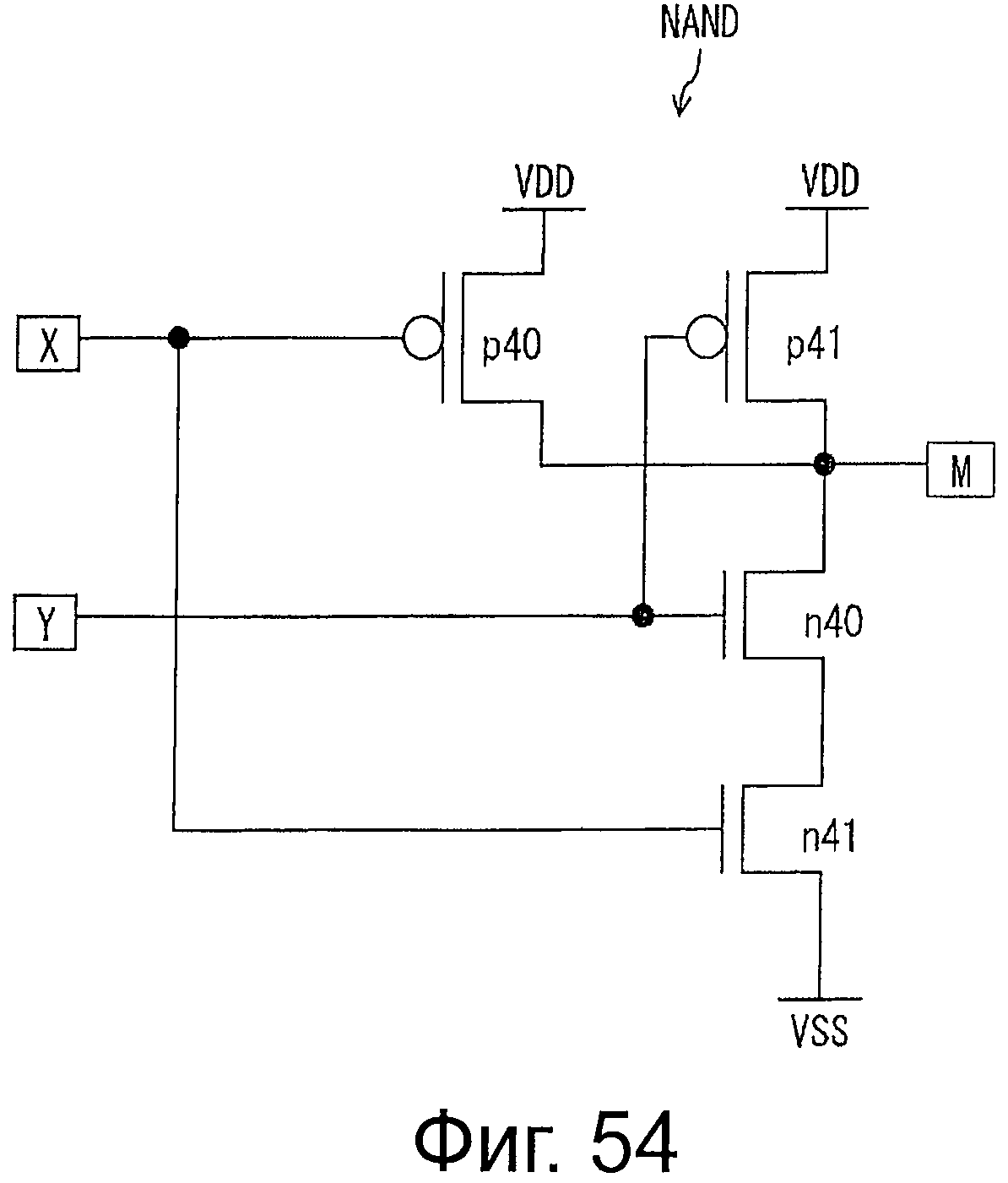

Фиг.54 представляет электрическую схему, иллюстрирующую схему И-НЕ в регистре сдвига в устройстве отображения, изображенном на фиг.51.

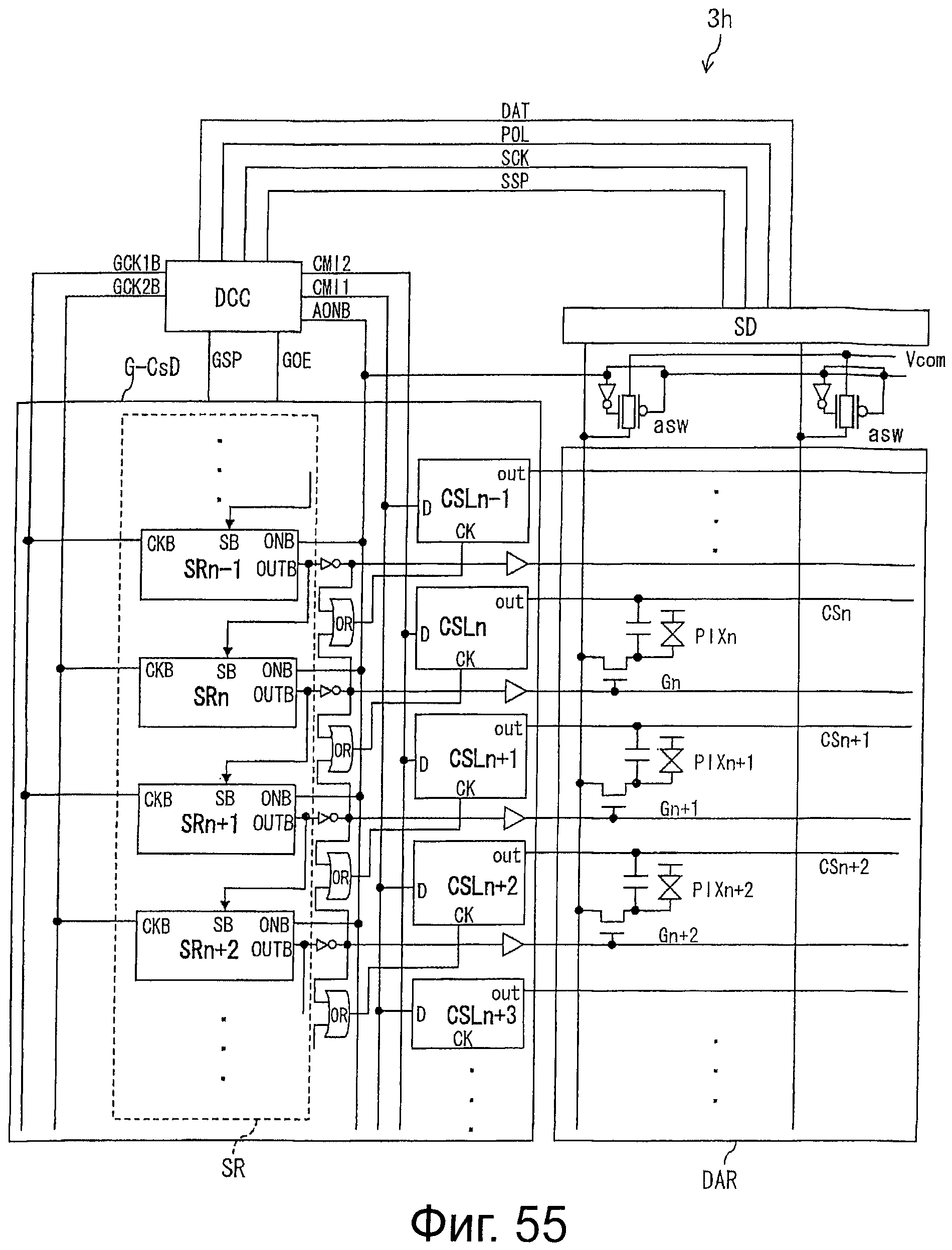

Фиг.55 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

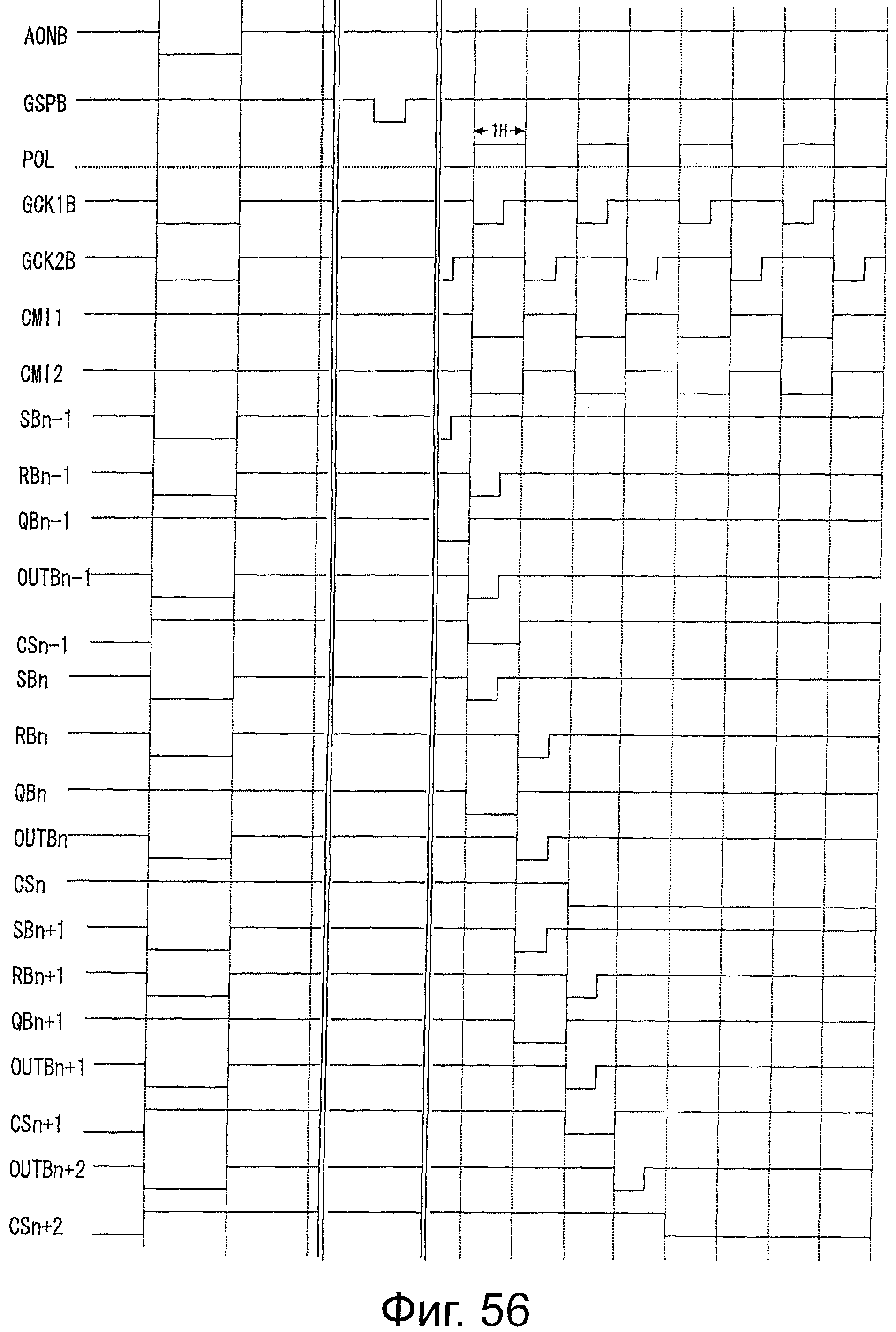

Фиг.56 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.55.

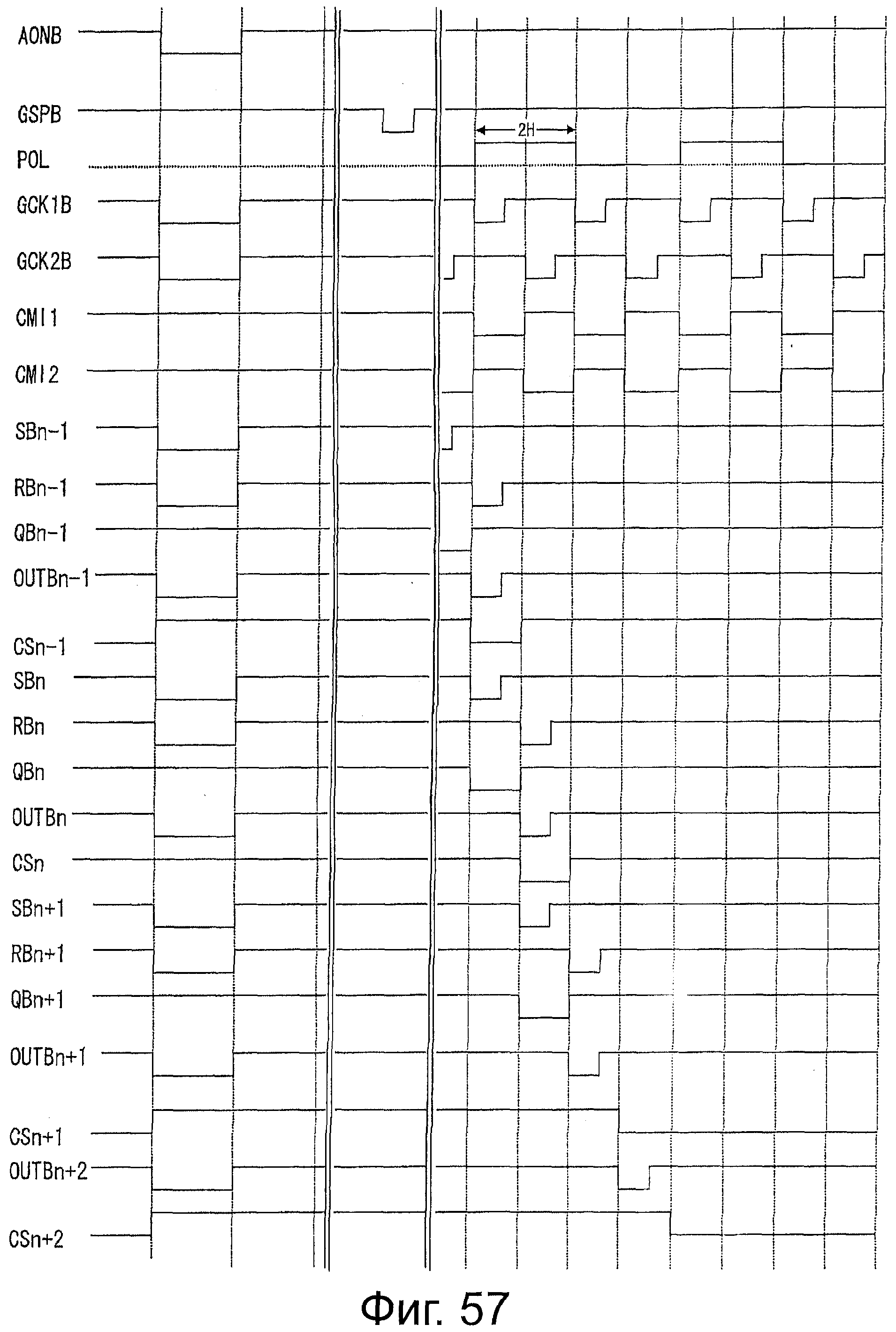

Фиг.57 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.55.

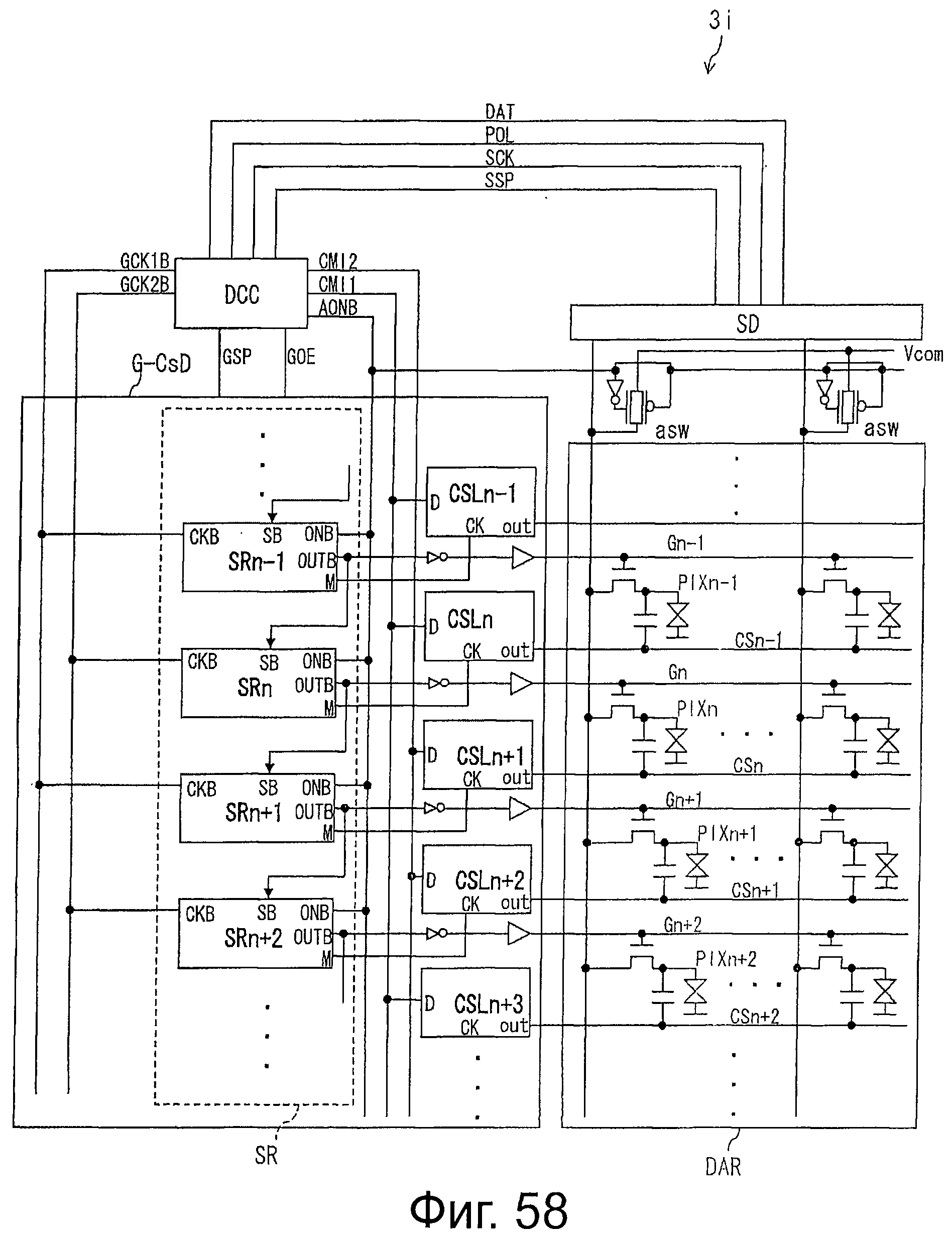

Фиг.58 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

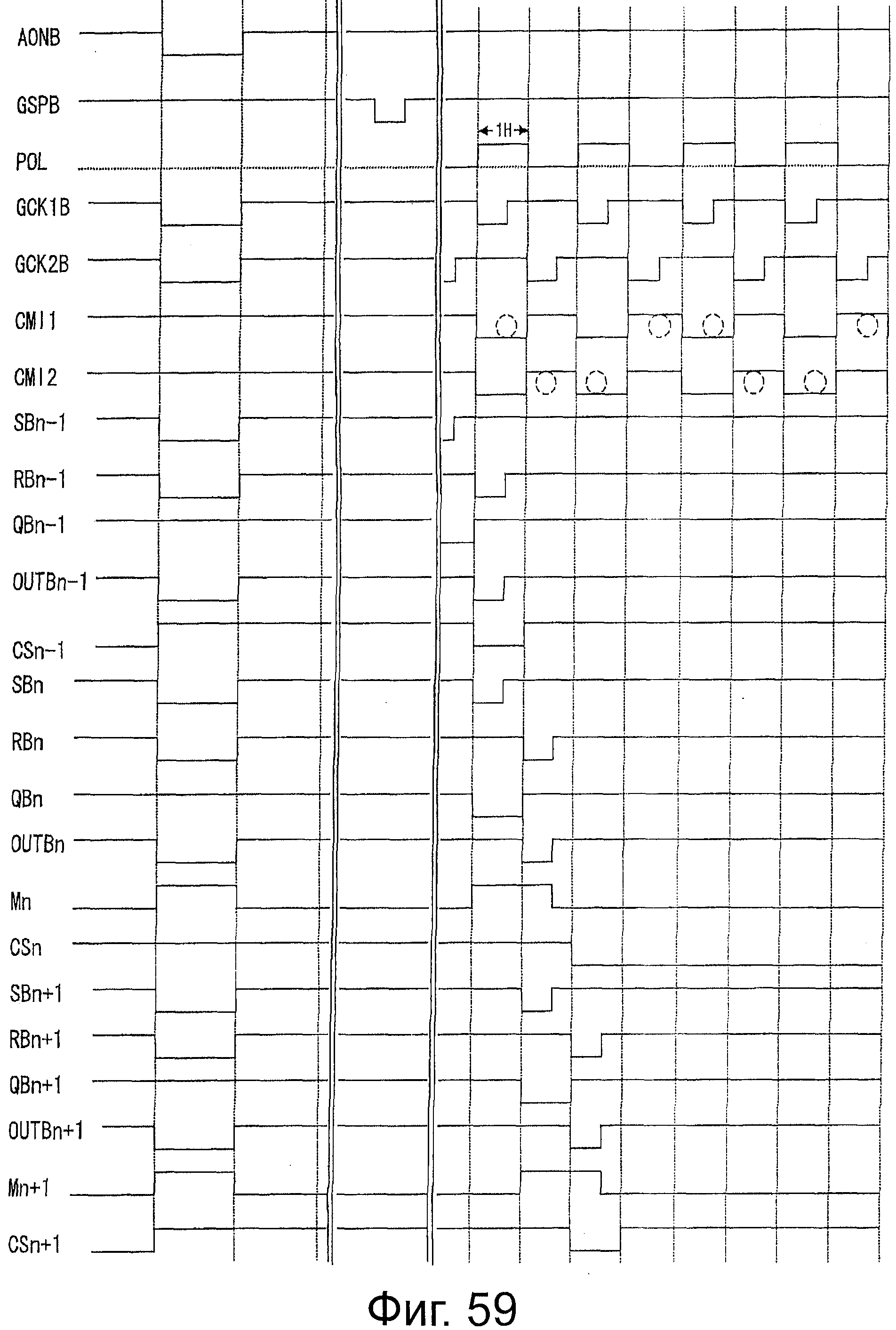

Фиг.59 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.58.

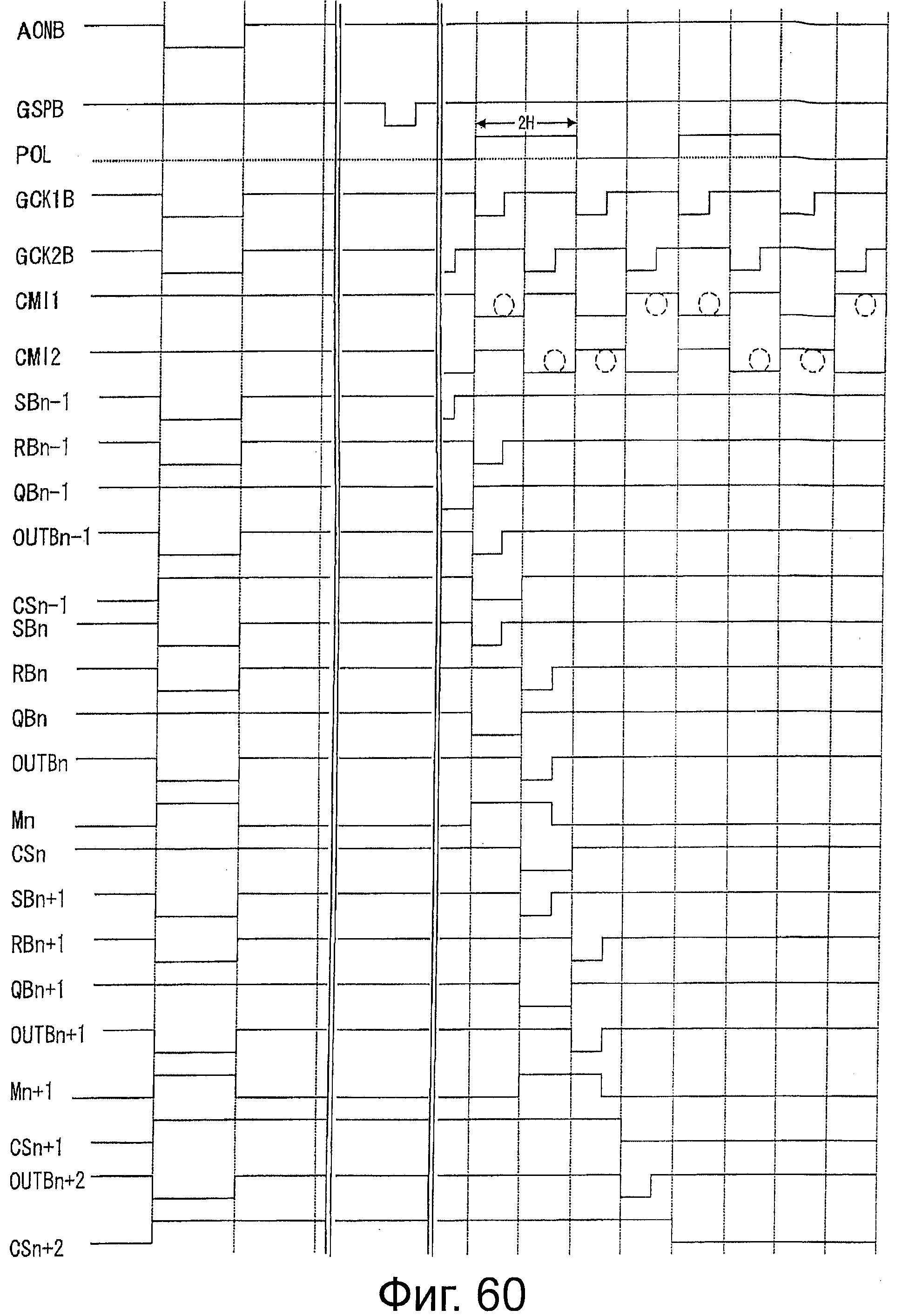

Фиг.60 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.58.

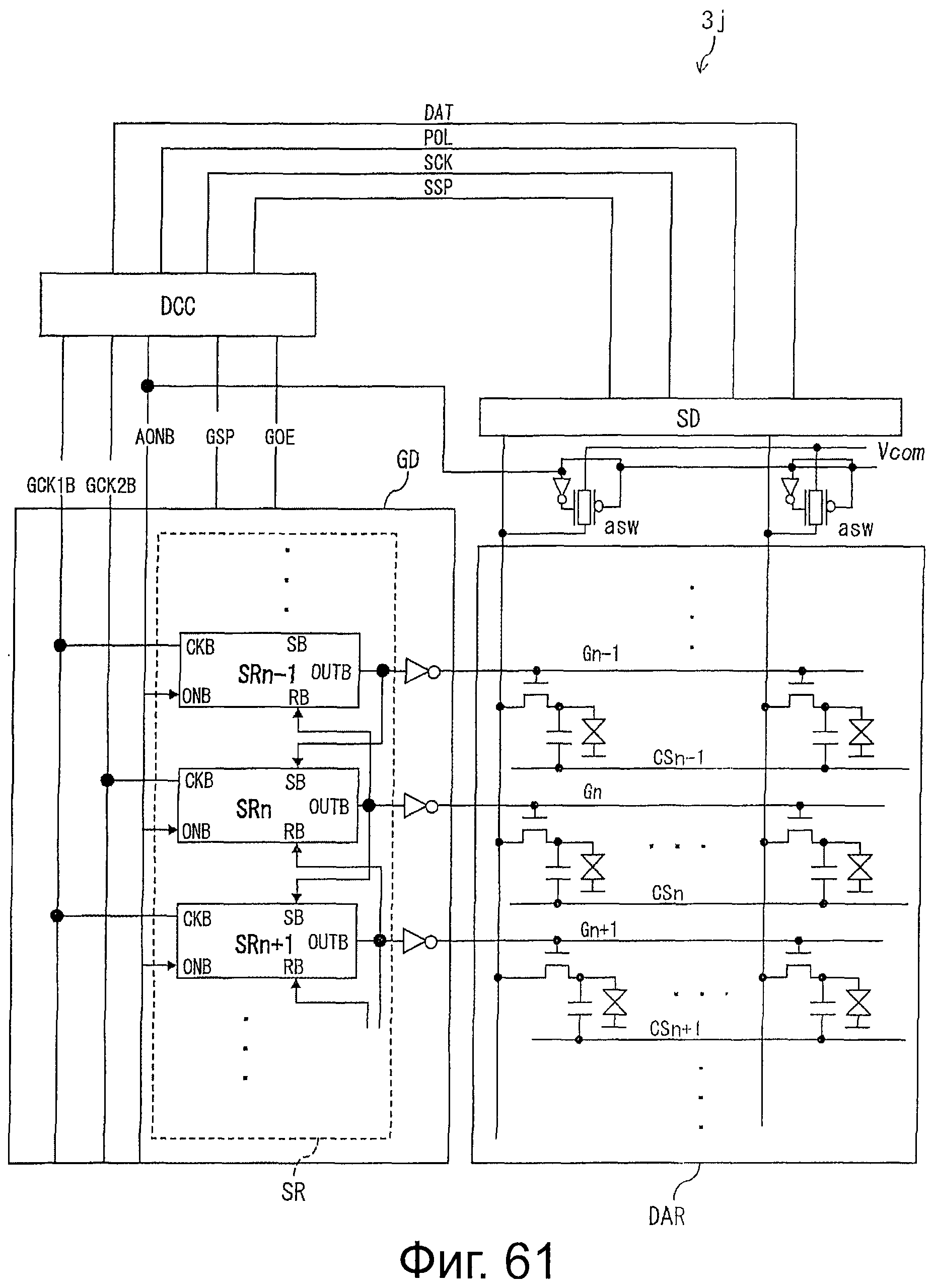

Фиг.61 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

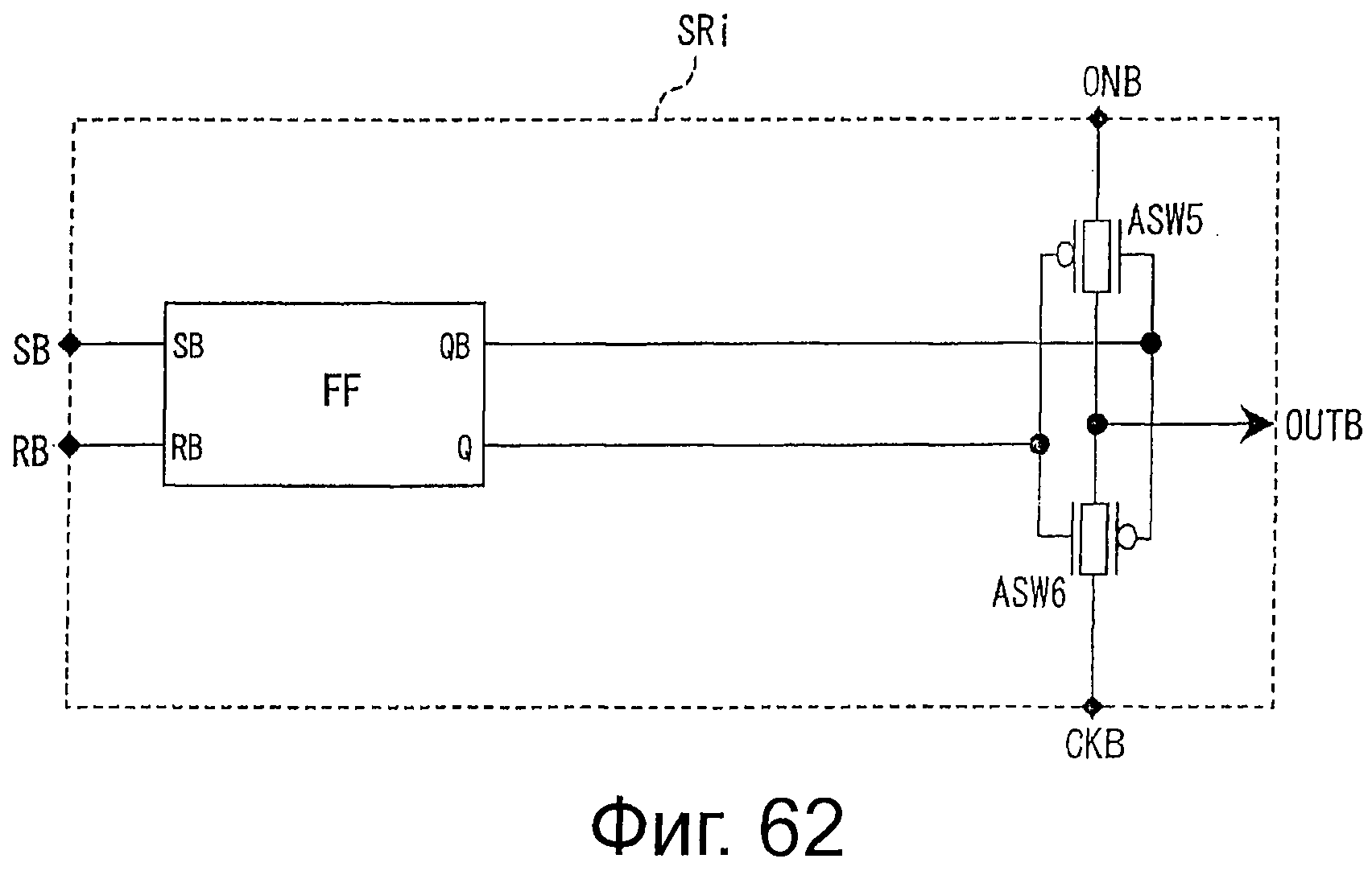

Фиг.62 представляет электрическую схему, иллюстрирующую каждый из нескольких каскадов регистра сдвига в устройстве отображения, показанном на фиг.61.

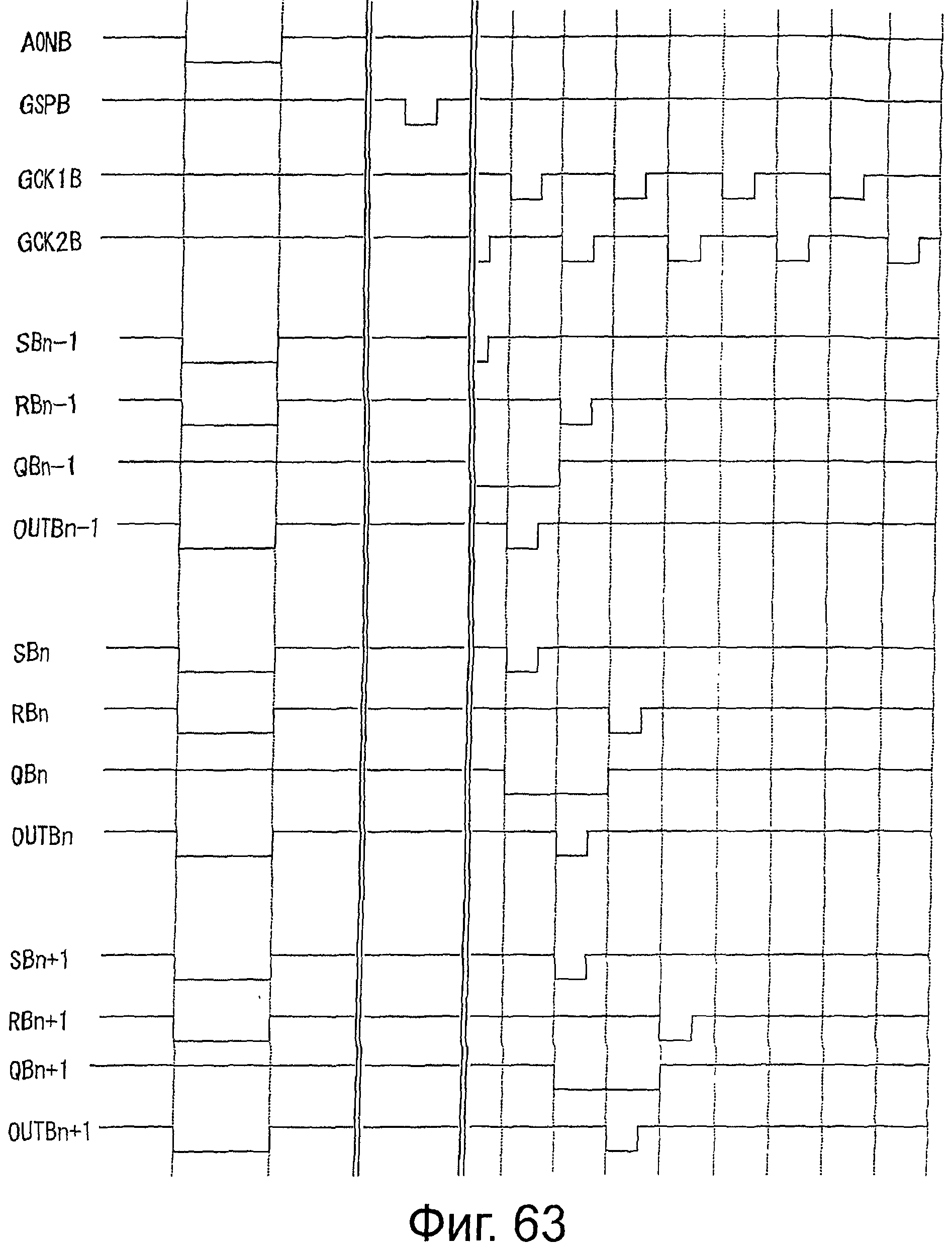

Фиг.63 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.61.

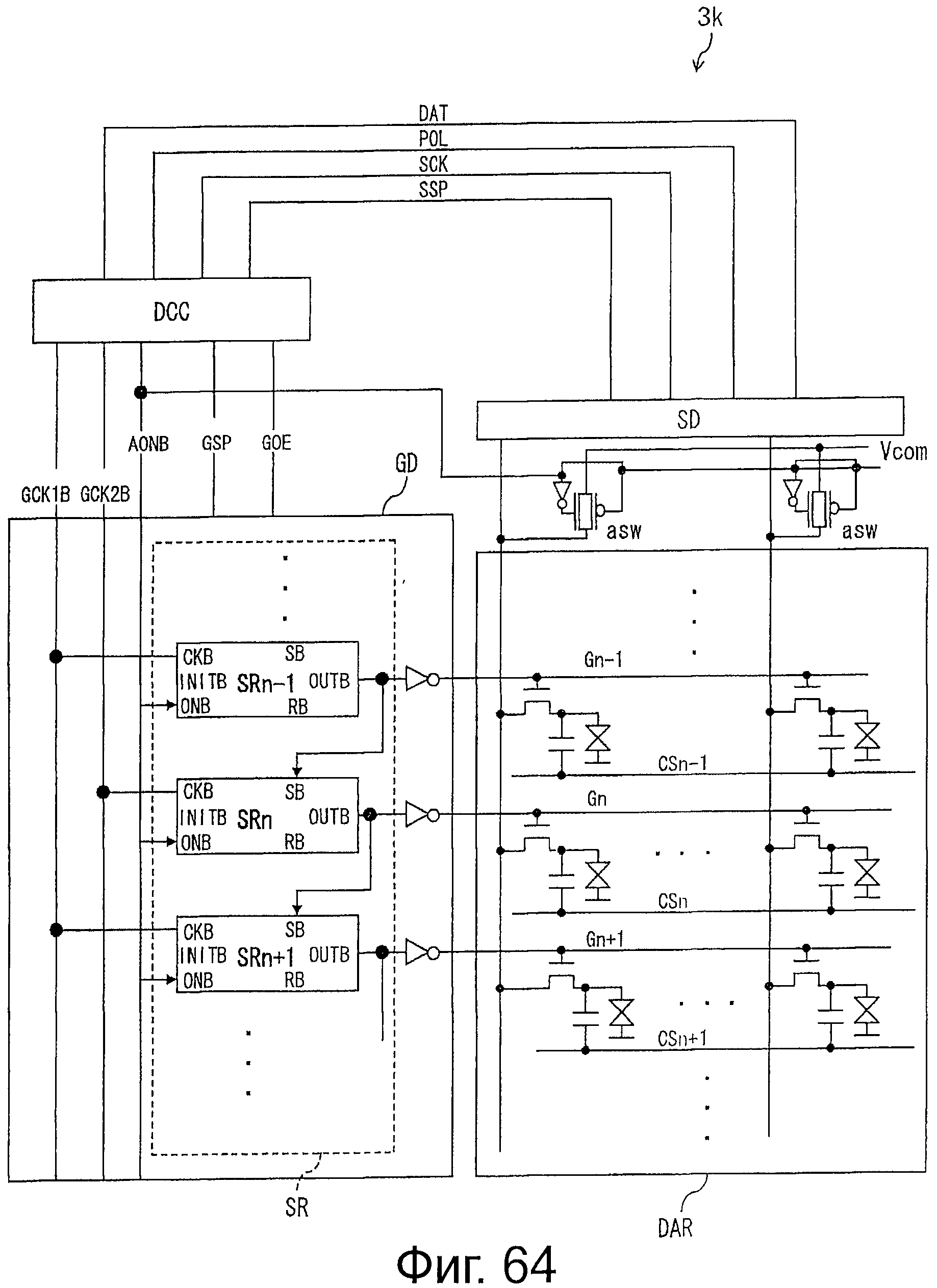

Фиг.64 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

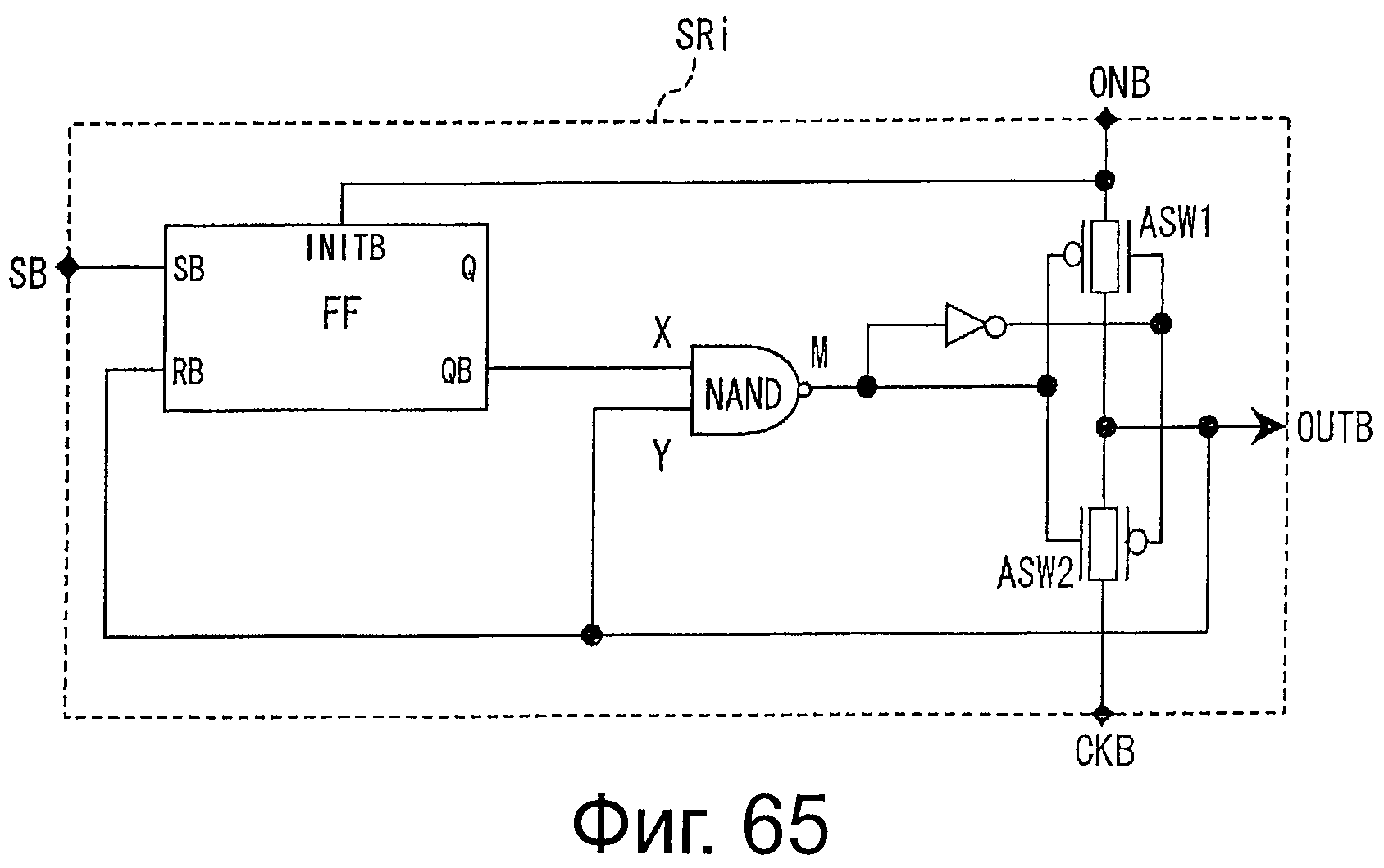

Фиг.65 представляет электрическую схему, иллюстрирующую каждый из нескольких каскадов регистра сдвига в устройстве отображения, показанном на фиг.64.

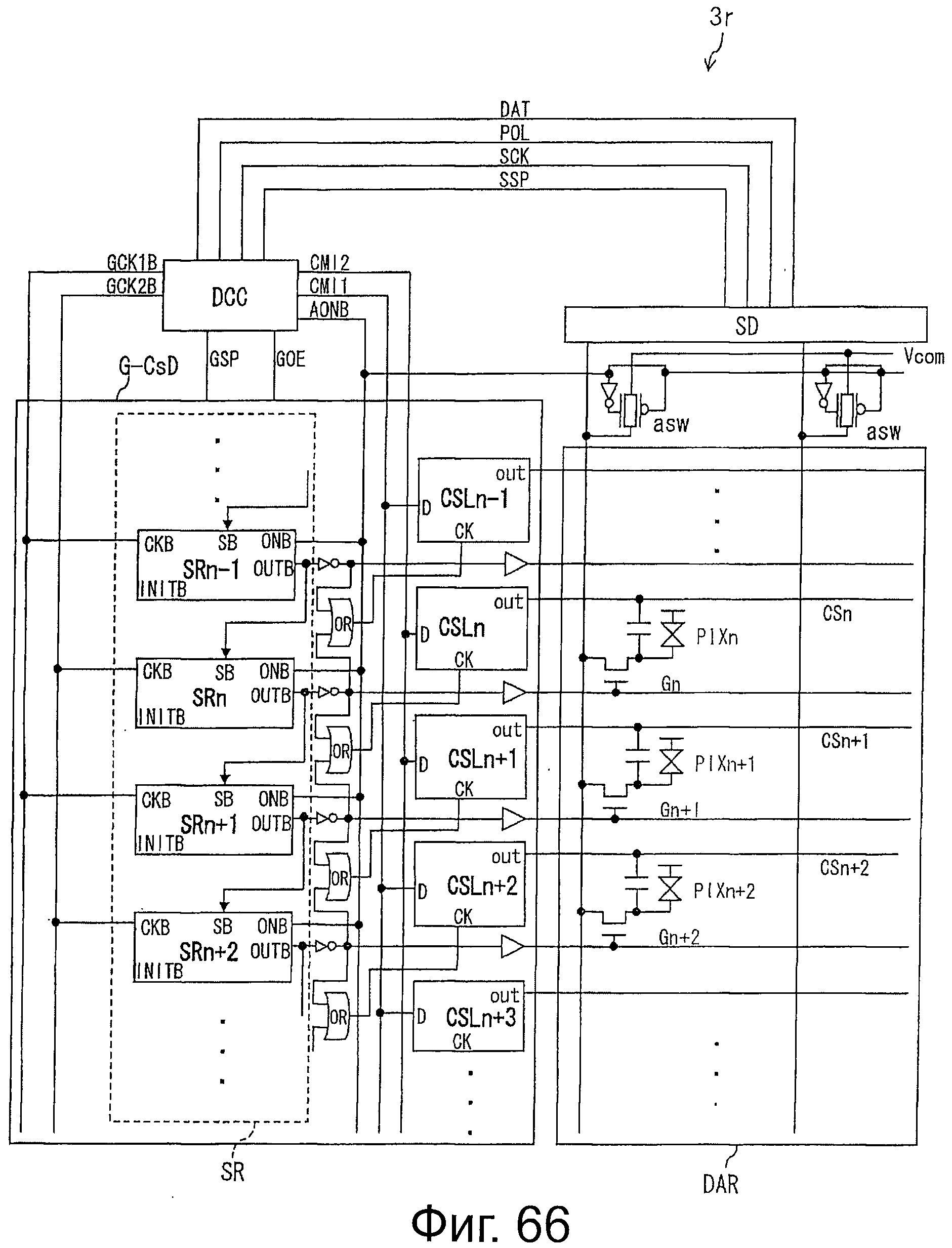

Фиг.66 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

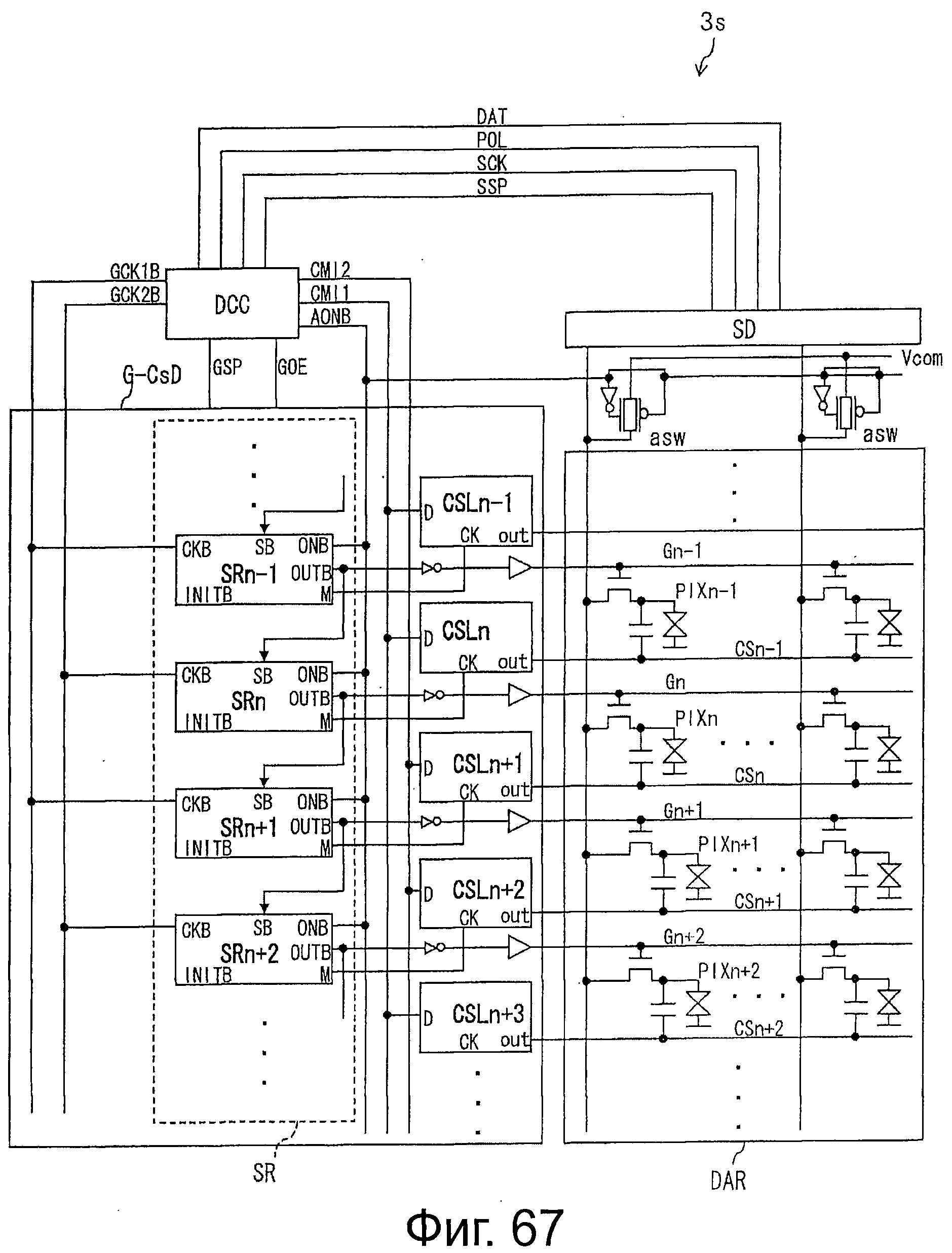

Фиг.67 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

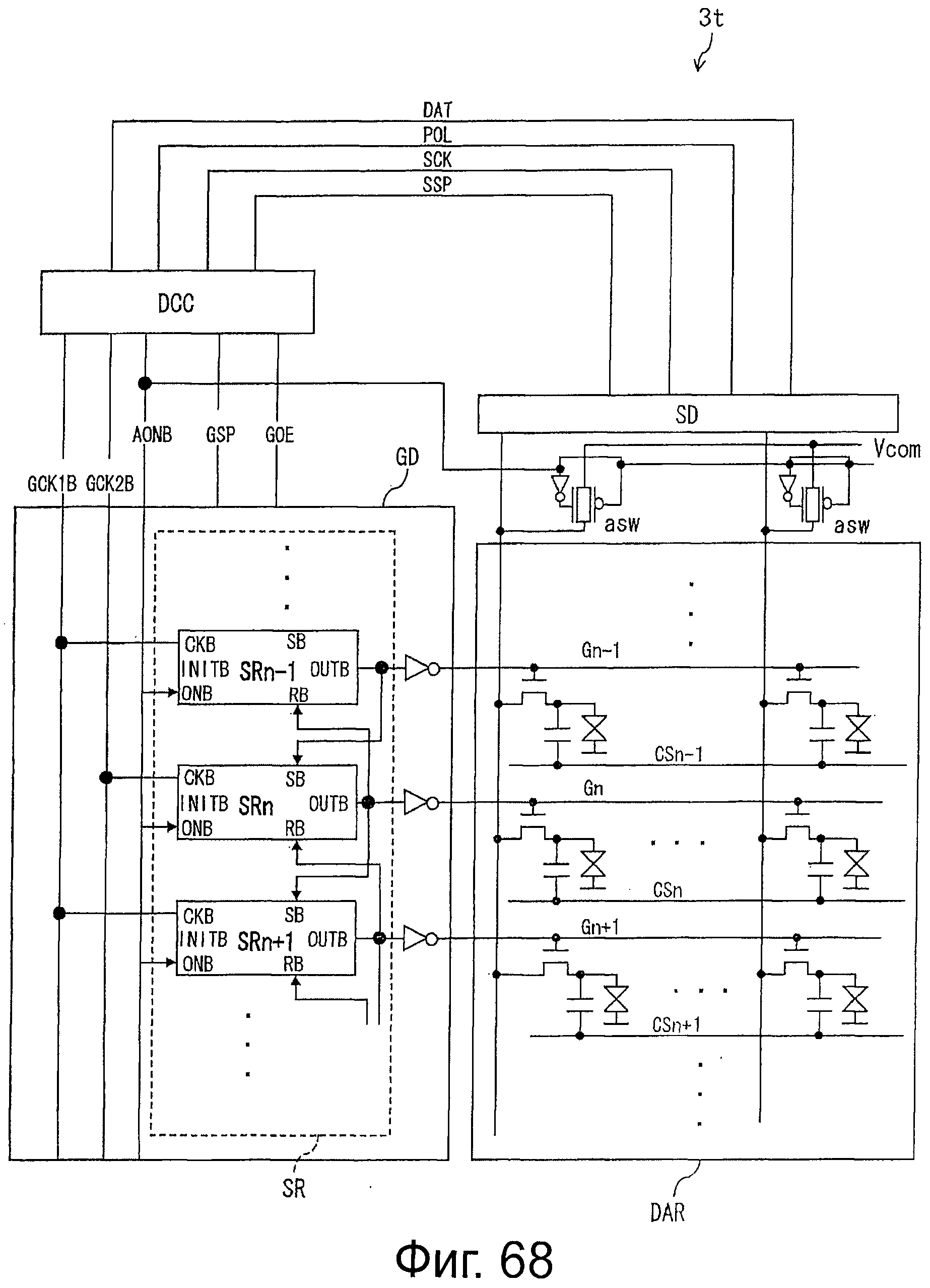

Фиг.68 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

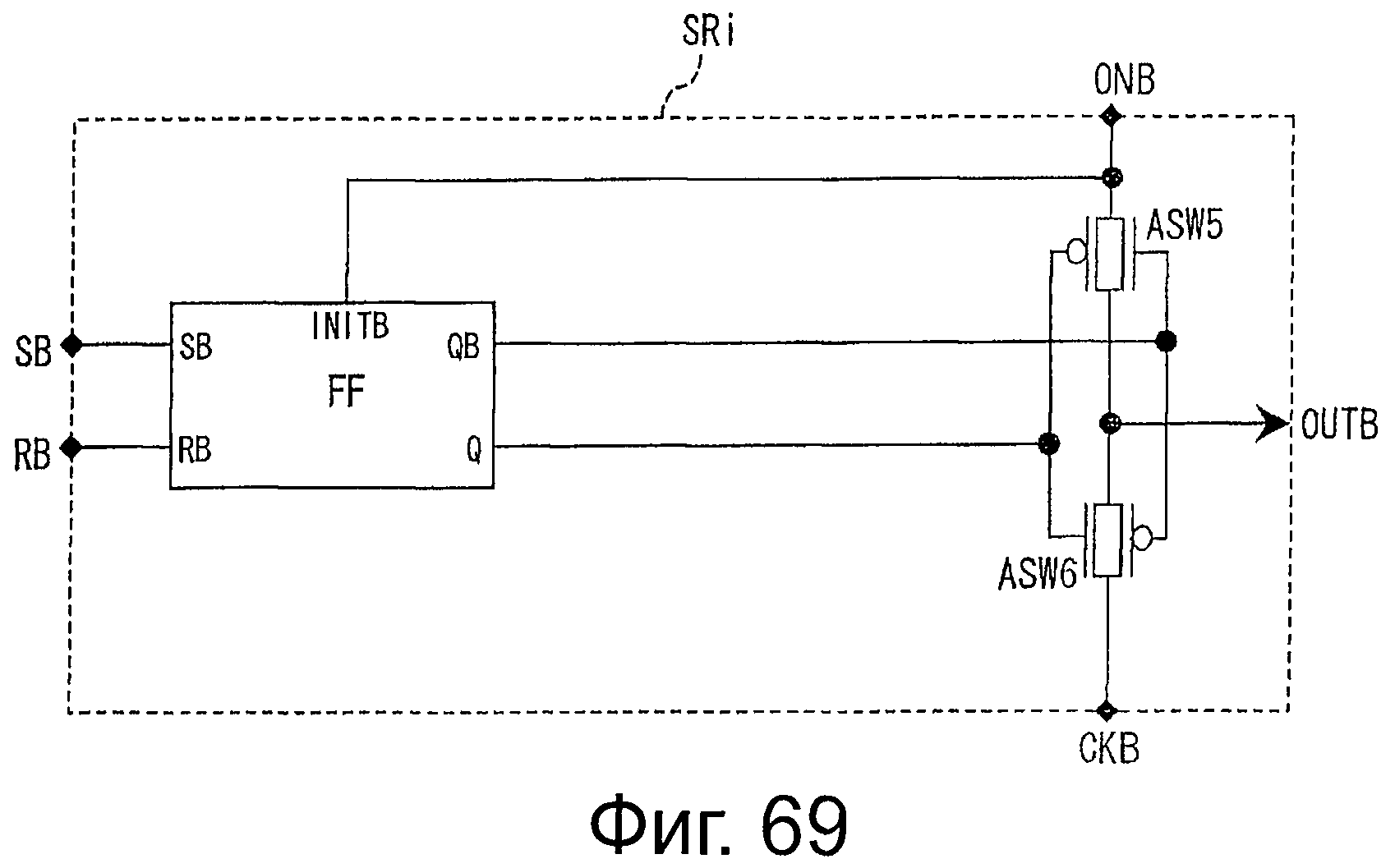

Фиг.69 представляет электрическую схему, иллюстрирующую каждый из нескольких каскадов регистра сдвига в устройстве отображения, показанном на фиг.68.

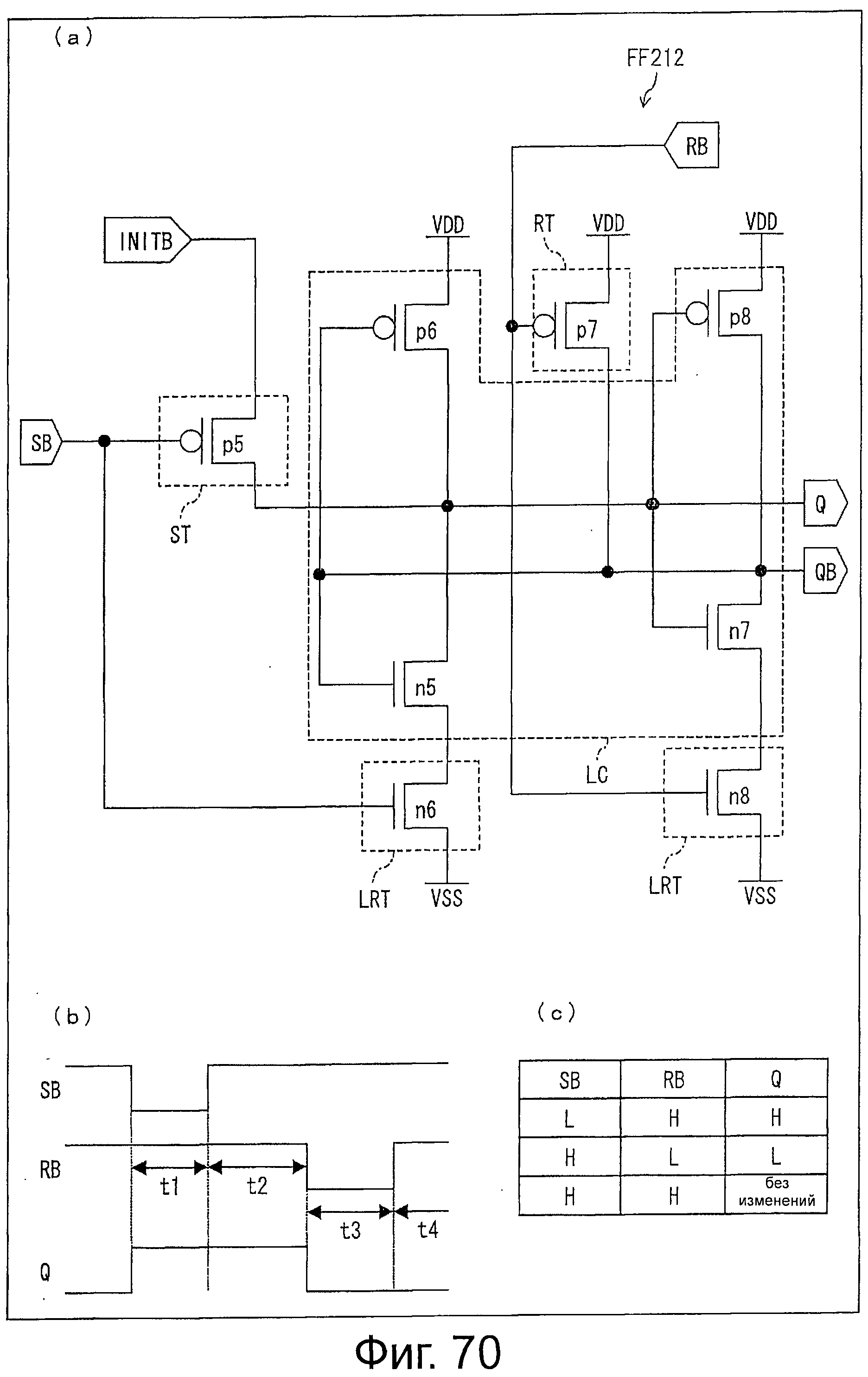

Фиг.70 представляет пояснительный вид, иллюстрирующий другой триггер, используемый в устройстве отображения согласно настоящему изобретению: фиг.70 (а) показывает электрическую схему, фиг.70 (b) показывает временную диаграмму и фиг.70 (с) показывает таблицу истинности.

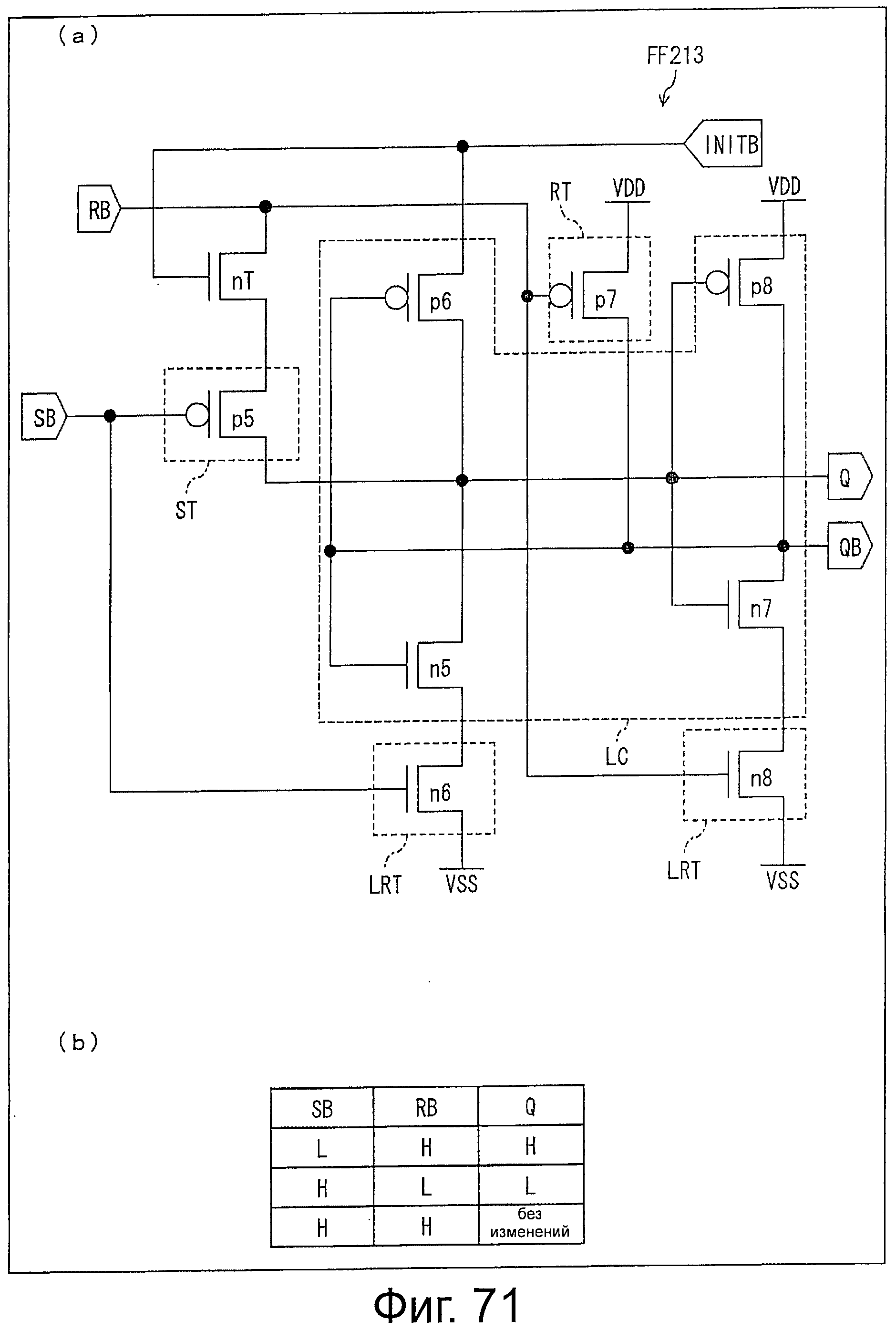

Фиг.71 представляет пояснительный вид, иллюстрирующий другой триггер, используемый в устройстве отображения согласно настоящему изобретению: фиг.71 (а) показывает электрическую схему, фиг.71 (b) показывает таблицу истинности.

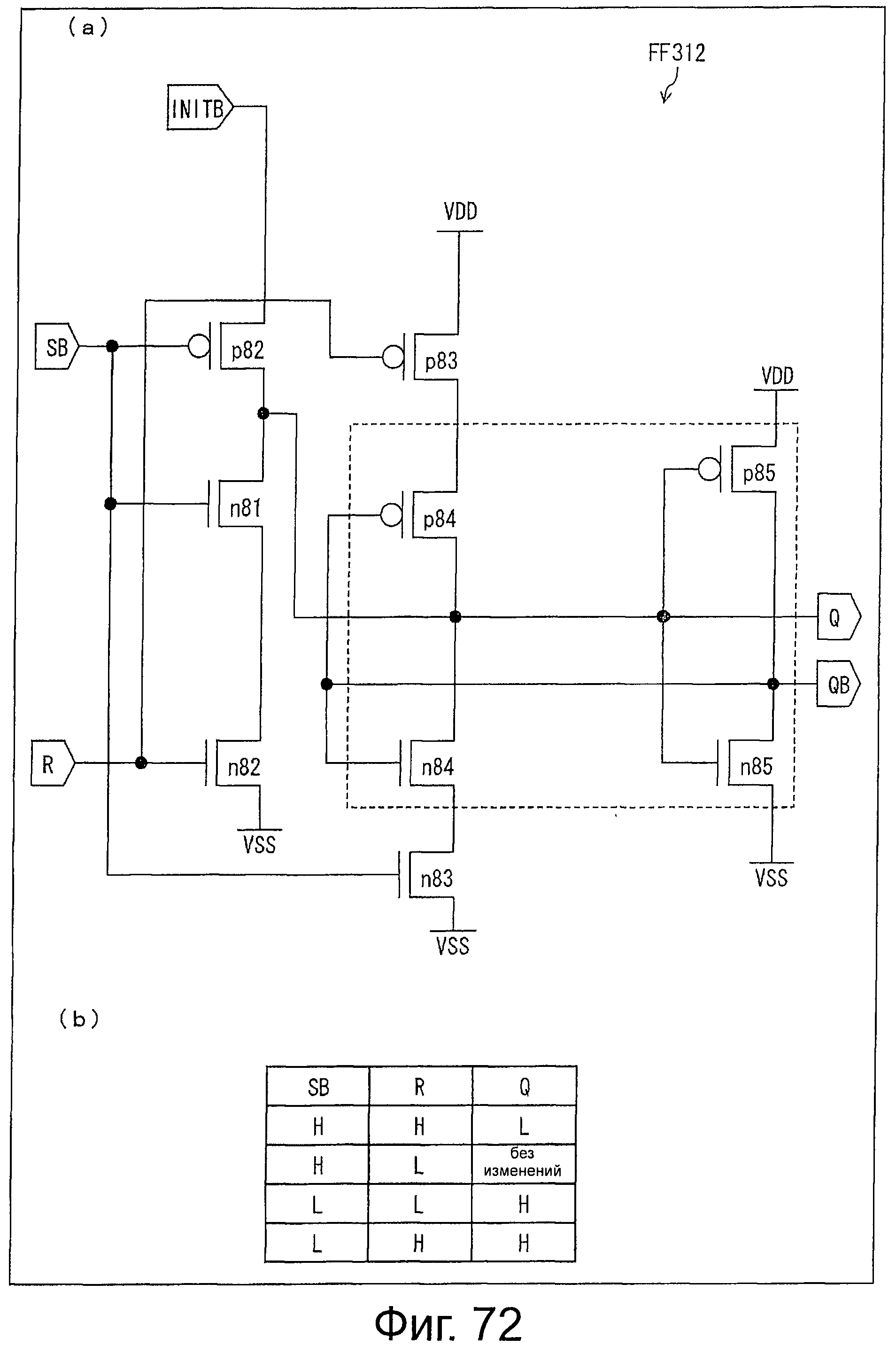

Фиг.72 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 3 настоящего изобретения: фиг.72 (а) показывает электрическую схему, фиг.72 (b) показывает таблицу истинности.

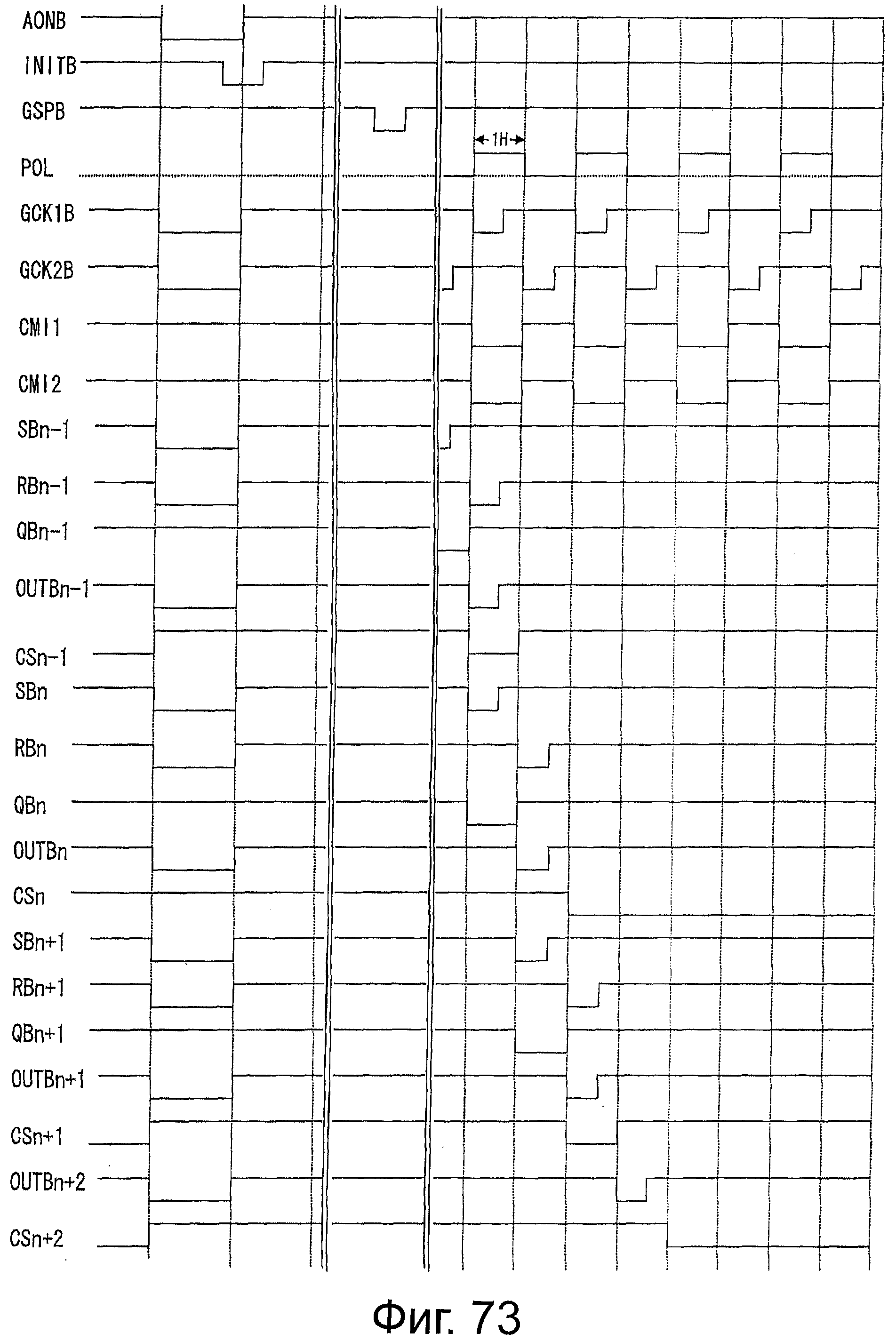

Фиг.73 представляет временную диаграмму, показывающую другой модифицированный пример временной диаграммы, изображенной на фиг.40 или фиг.44.

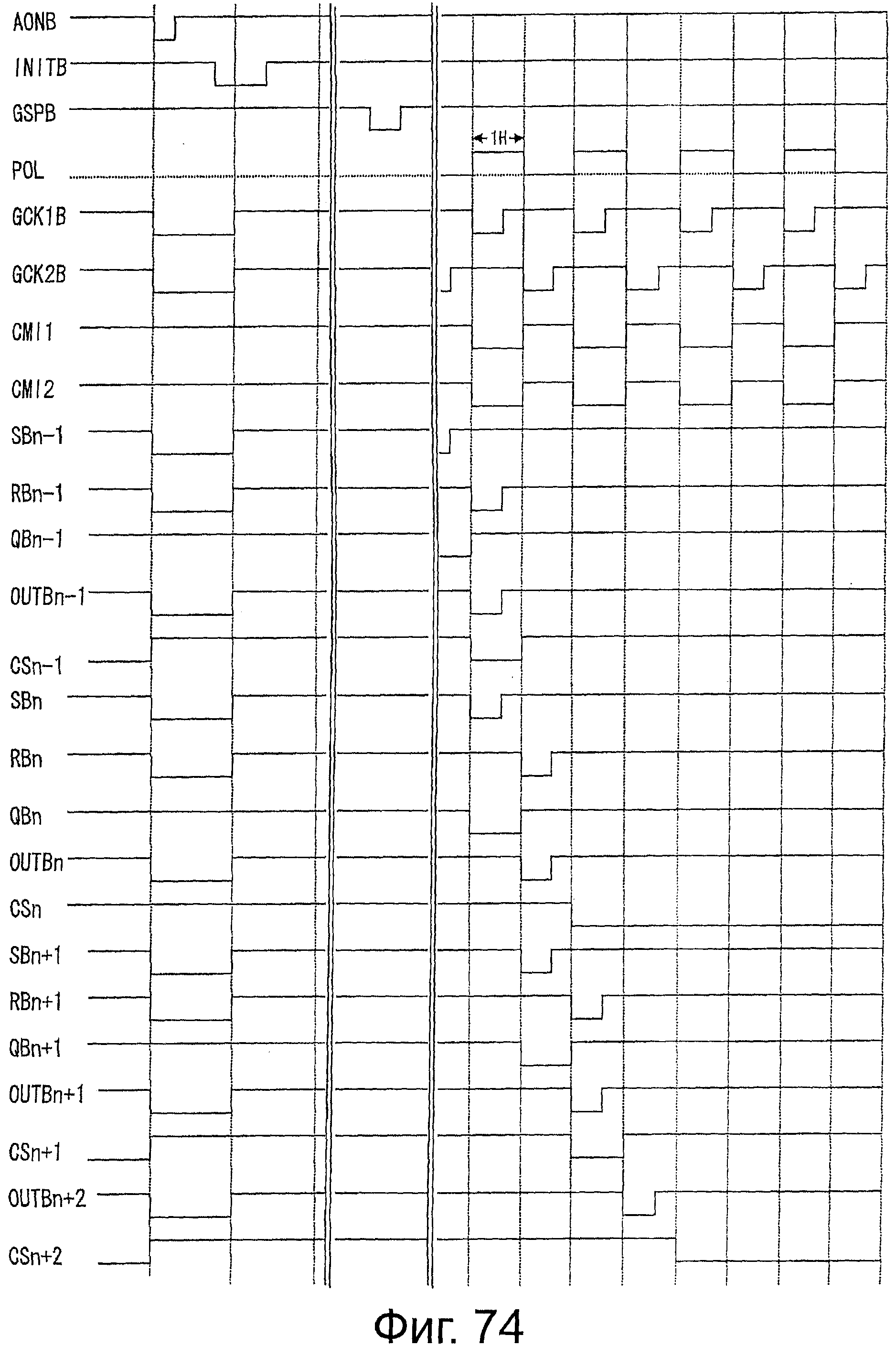

Фиг.74 представляет временную диаграмму, показывающую другой модифицированный пример временной диаграммы, изображенной на фиг.40 или фиг.44.

Фиг.75 представляет электрическую схему, иллюстрирующую известный триггер.

Подробное описание изобретения

Варианты настоящего изобретения описаны ниже со ссылками на фиг.1-74. В последующем описании RS-триггер (в дальнейшем обозначаемый триггер "FF", где это подходит) принимает (i) сигнал установки (S-сигнал или SB-сигнал) через клемму установки (клемма S или клемма SB), (ii) сигнал сброса (R-сигнал или RB-сигнал) через клемму сброса (клемма R или клемма RB) и (iii) сигнал инициализации (INIT-сигнал или INITB-сигнал) через клемму инициализации (клемма INIT или клемма INITB). Кроме того, RS-триггер передает на выход (i) Q-сигнал через выходную клемму (клемму Q) и (ii) QB-сигнал через клемму инвертированного выхода (клемма QB). Отметим, что электрическое напряжение источника питания высокого напряжения (VDD) равно Vdd (в дальнейшем именуется «высокое», где это подходит), а электрическое напряжение источника питания низкого напряжения (VSS) равно Vss (в дальнейшем именуется «низкое», где это подходит). Указанные S-сигнал (сигнал установки), R-сигнал (сигнал сброса), INIT-сигнал (сигнал инициализации) и Q-сигнал (выходной сигнал) имеют высокий уровень, когда они активны. Указанные SB-сигнал (инвертированный сигнал установки), RB-сигнал (инвертированный сигнал сброса), INITB-сигнал (инвертированный сигнал инициализации) и QB-сигнал (инвертированный выходной сигнал) имеют низкий уровень, когда они активны.

[Триггер согласно варианту 1]

Фиг.1 (а) представляет электрическую схему, иллюстрирующую конфигурацию триггера согласно варианту 1 настоящего изобретение. Триггер FF 101, показанный на фиг.1 (а), включает (i) p-канальный транзистор р1 и n-канальный транзистор n1, которые составляют КМОП-схему, (n) p-канальный транзистор р2 и n-канальный транзистор n2, которые составляют другую КМОП-схему, (iii) клемму SB, (iv) клемму RB, (v) клемму Q, (vi) клемму QB и (vii) клемму INIT. В схеме триггера FF 101 (i) затвор транзистора р1, затвор транзистора n1, сток транзистора р2, сток транзистора n2 и клемма Q соединены одно с другим, (ii) сток транзистора р1, сток транзистора n1, затвор транзистора р2, затвор транзистора n2 и клемма QB соединены одно с другим, (iii) исток транзистора р1 соединен с клеммой SB, (iv) исток транзистора р2 соединен с клеммой RB, (v) исток транзистора n1 соединен с клеммой INIT и (vi) исток транзистора n2 соединен с клеммой VSS (источник питания низкого напряжения). Здесь транзистор р1, транзистор n1, транзистор р2 и транзистор n2 составляют схему LC защелки.

Фиг.1 (b) представляет временную диаграмму, показывающую работу триггера FF 101 (когда INIT-сигнал неактивен), и фиг.1 (с) представляет таблицу истинности для триггера FF 101 (когда INIT-сигнал неактивен).

Последующее описание относится к работе триггера FF 101 в случае, когда SB-сигнал активен (=низкий уровень) и RB-сигнал неактивен (=высокий уровень) (период t1 времени). Когда выходной 0-сигнал имеет низкий уровень и выходной QB-сигнал имеет высокий уровень, транзистор р1 открыт. В таких условиях, когда SB-сигнал стал активным (=низкий уровень), электрический потенциал клеммы QB снижается до уровня Vss + Vth (пороговое напряжение). Когда электрический потенциал клеммы QB уменьшается и становится по существу равным Vss, транзистор р2 отпирается, а транзистор n2 запирается (если пороговое напряжение транзистора n2 не меньше напряжения Vth, транзистор n2 запирается полностью). Здесь, поскольку RB-сигнал неактивен (=высокий уровень =Vdd), выходной Q-сигнал перешел на высокий уровень. Клемма Q соединена с затвором транзистора р1 и с затвором транзистора n1. Соответственно, когда клемма Q переходит на высокий уровень, транзистор р1 запирается, а транзистор n1 отпирается. В течение периода времени, отличного от периода времени инициализации, INIT-сигнал имеет низкий уровень (Vss). Соответственно, когда транзистор n1 отпирается, выходной QB-сигнал тоже переходит на низкий уровень (Vss). Когда QB-сигнал имеет низкий уровень, транзистор р2 открыт, а транзистор n2 заперт. В этом случае клемма Q оказывается отсоединена электрически от клеммы VSS и передает на выход RB-сигнал (=высокий уровень =Vdd). Как описано выше, выходной QB-сигнал начинает сразу же смещаться к уровню напряжения Vss + Vth, но выходной Q-сигнал поступает по цепи обратной связи назад через схему LC защелки. В результате выходной QB-сигнал устойчиво остается на низком (Vss) уровне. Отметим, что когда SB-сигнал сдвигается от состояния высокого уровня к состоянию низкого уровня, сток транзистора р1 не имеет электрического соединения с каким-либо открытым транзистором. Соответственно, схема освобождения защелки не нужна.

Последующее описание относится к работе триггера FF 101 в случае, когда SB-сигнал неактивен (=высокий уровень) и RB-сигнал неактивен (=высокий уровень) (период t2 времени). Указанный INIT-сигнал имеет низкий уровень (Vss) в течение периода времени, отличного от периода времени инициализации. Вследствие этого, когда SB-сигнал и RB-сигнал имеют высокий уровень, схема LC защелки оказывается включена. Соответственно, состояние, в котором SB-сигнал не изменялся, сохраняется. Иными словами, состояние, имевшее место в периоде t1 (выходной Q-сигнал имеет высокий уровень, и выходной QB-сигнал имеет низкий уровень) сохраняется в периоде t2.

Последующее описание относится к работе триггера FF 101 в случае, когда SB-сигнал неактивен (=высокий уровень) и RB-сигнал активен (=низкий уровень) (период t3 времени). Когда выходной Q-сигнал имеет высокий уровень и выходной QB-сигнал имеет низкий уровень, транзистор р2 открыт. В такой ситуации, когда RB-сигнал стал активным (=низкий уровень), электрический потенциал клеммы Q уменьшается до уровня Vss + Vth (пороговое напряжение). Когда электрический потенциал клеммы Q уменьшился и стал по существу равным напряжению Vss, транзистор р1 открывается, а транзистор n1 запирается (если пороговое напряжение транзистора n1 не меньше напряжения Vth, транзистор n1 запирается полностью). Здесь SB-сигнал неактивен (=высокий уровень =Vdd), так что выходной QB-сигнал переходит на высокий уровень. Клемма QB соединена с затвором транзистора р2 и с затвором транзистора n2. Соответственно, когда выходной QB-сигнал переходит на высокий уровень, транзистор р2 запирается, а транзистор n2 открывается. Когда транзистор n2 открыт, клемма Q оказывается электрически соединена с клеммой VSS, вследствие чего Q-сигнал переходит на низкий уровень (Vss). Когда клемма Q имеет низкий уровень, транзистор р1 открыт, а транзистор n1 заперт. Соответственно, клемма QB отсоединена электрически от клеммы EMIT и передает на выход SB-сигнал (высокий уровень =Vdd). Как описано выше, выходной Q-сигнал сразу же начинает смещаться к уровню напряжения Vss + Vth, но выходной QB-сигнал поступает по цепи обратной связи назад через схему LC защелки, вследствие чего выходной Q-сигнал устойчиво остается на низком уровне (Vss). Отметим, что сток транзистора р2 не имеет электрического соединения с каким-либо открытым транзистором, когда RB-сигнал сдвигается от состояния с высоким уровнем к состоянию с низким уровнем. Соответственно, схема освобождения защелки не нужна.

Последующее описание относится к работе триггера FF 101 в случае, когда SB-сигнал неактивен (=высокий уровень) и RB-сигнал неактивен (=высокий уровень) (период t4 времени). Указанный INIT-сигнал имеет низкий уровень (Vss) в течение периода времени, отличного от периода времени инициализации. Вследствие этого, когда SB-сигнал имеет высокий уровень и RB-сигнал имеет высокий уровень, схема LC защелки оказывается включена. Соответственно, состояние, в котором SB-сигнал не изменялся, сохраняется. Иными словами, состояние, имевшее место в периоде t3 (выходной Q-сигнал имеет низкий уровень, и выходной QB-сигнал имеет высокий уровень) сохраняется в периоде t4.

Последующее описание относится к работе триггера FF 101, когда INIT-сигнал активен (=высокий уровень) (инициализация). Когда выходной Q-сигнал имеет низкий уровень и выходной QB-сигнал имеет высокий уровень, транзистор n1 заперт. В такой ситуации, когда INIT-сигнал перешел на высокий уровень, нет никакого влияния на выходные сигналы триггера (Q-сигнал имеет низкий уровень, и QB-сигнал имеет высокий уровень). Когда выходной Q-сигнал имеет высокий уровень и выходной QB-сигнал имеет низкий уровень, транзистор n1 открыт. В такой ситуации, когда INIT-сигнал перешел на высокий уровень, электрический потенциал клеммы QB увеличивается до уровня Vdd-Vth (пороговое напряжение). Когда электрический потенциал клеммы QB увеличивается и становится по существу равен Vdd, транзистор n2 отпирается и транзистор р2 запирается (когда пороговое напряжение транзистора р2 не меньше Vth, транзистор р2 полностью запирается). В этом случае клемма Q оказывается электрически соединена с клеммой VSS, так что выходной Q-сигнал переходит на низкий уровень (=Vss). Клемма Q соединена с затвором транзистора р1 и затвором транзистора n1. Соответственно, когда выходной Q-сигнал переходит на низкий уровень, транзистор n1 запирается, а транзистор р1 отпирается. Здесь SB-сигнал неактивен (=высокий уровень =Vdd), так что выходной QB-сигнал переходит на высокий уровень. Когда выходной QB-сигнал имеет высокий уровень, транзистор n2 открыт, а транзистор р2 заперт. Соответственно, клемма Q оказывается электрически отделена от клеммы RB и передает на выход низкий уровень (Vss). Как описано выше, выходной QB-сигнал сразу же начинает сдвигаться к уровню потенциала Vdd-Vth, но выходной Q-сигнал поступает по цепи обратной связи назад через схему LC защелки. Соответственно, выходной QB-сигнал устойчиво остается на высоком уровне (Vdd). Применение описанного выше способа позволяет осуществлять инициализацию без использования схемы инициализации.

Когда оба сигнала, SB-сигнал и RB-сигнал, активны (=низкий уровень), транзистор р1, транзистор р2, транзистор n1 и транзистор n2 оказываются заперты (плавающее состояние), когда потенциалы обеих клемм, клеммы Q и клеммы QB, становятся равны напряжению Vss + Vth. В этом случае выходные сигналы (Q-сигнал и QB-сигнал) находятся в неопределенном состоянии.

Как описано выше, в схеме триггера FF 101 (i) транзистор р1, транзистор n1, транзистор р2 и транзистор n2 (две CMOS-схемы) составляют схему защелки, (ii) исток транзистора р1 соединен с клеммой SB, (iii) исток транзистора р2 соединен с клеммой RB и (iv) исток транзистора n1 соединен с клеммой INIT. В такой схеме можно выполнять операцию установки, операцию защелкивания, операцию сброса и операцию инициализации без использования схемы установки, схемы сброса, схемы освобождения защелки и схемы инициализации, каждая из которых была необходима в известном триггере (см. фиг.70).

Можно модифицировать схему, представленную на фиг.1 (а), чтобы соединить исток транзистора n1 с клеммой VSS, как это сделано в триггере FF 105, показанном на фиг.21 (а). На фиг.21 (b) представлена таблица истинности для триггера FF 105.

Фиг.2 (а) представляет электрическую схему, иллюстрирующую конфигурацию триггера FF 102, который представляет собой модифицированный пример триггера, показанного на фиг.1 (а). Триггер FF 102, показанный на фиг.2 (а), включает (i) p-канальный транзистор р3 и n-канальный транзистор n3, которые составляют КМОП-схему, (ii) p-канальный транзистор р4 и n-канальный транзистор n4, которые составляют другую КМОП-схему, (iii) клемму S, (iv) клемму R, (v) клемму Q, (vi) клемму QB и (vii) клемму INITB. В схеме триггера FF 102 (i) затвор транзистора р3, затвор транзистора n3, сток транзистора р4, сток транзистора n4 и клемма Q соединены одно с другим, (ii) сток транзистора р3, сток транзистора n3, затвор транзистора р4, затвор транзистора n4 и клемма QB соединены одно с другим, (iii) исток транзистора n4 соединен с клеммой S, (iv) исток транзистора n3 соединен с клеммой R, (v) исток транзистора р4 соединен с клеммой INITB и (vi) исток транзистора р3 соединен с клеммой VDD (источник питания высокого напряжения). Здесь транзистор p3, транзистор n3, транзистор р4 и транзистор n4 составляют схему LC защелки.

Фиг.2 (b) представляет временную диаграмму, показывающую работу триггера FF 102 (когда INITB-сигнал неактивен), а фиг.2 (с) представляет таблицу истинности для триггера FF 102 (когда INITB-сигнал неактивен). Выходной Q-сигнал триггера FF 102 является таковым, что (i) он находится в состоянии удержания в течение периода времени, когда S-сигнал имеет низкий уровень (неактивен) и R-сигнал имеет низкий уровень (неактивен), (ii) он имеет низкий уровень (неактивен) в течение периода времени, когда S-сигнал имеет низкий уровень (неактивен) и R-сигнал имеет высокий уровень (активен), (iii) он имеет высокий уровень (активен) в течение периода времени, когда S-сигнал имеет высокий уровень (активен) и R-сигнал имеет низкий уровень (неактивен), и (iv) он находится в неопределенном состоянии в течение периода времени, когда S-сигнал имеет высокий уровень (активен) и R-сигнал имеет высокий уровень (активен) (см. фиг.2 (b) и (с)).

Фиг.19 (а) представляет электрическую схему, иллюстрирующую другую конфигурацию триггера согласно варианту 1 настоящего изобретения. Триггер FF 103, показанный на фиг.19 (а), включает (i) p-канальный транзистор Р1 и n-канальный транзистор N1, которые составляют КМОП-схему, (ii) p-канальный транзистор Р2 и n-канальный транзистор N2, которые составляют другую КМОП-схему, (iii) клемму SB, (iv) клемму R, (v) клемму INITB, (vi) клемму Q и (vii) клемму QB. В схеме триггера FF 103 (i) затвор транзистора Р1, затвор транзистора N1, сток транзистора Р2, сток транзистора N2, и клемма Q соединены одно с другим, (ii) сток транзистора Р1, сток транзистора N1, затвор транзистора Р2, и затвор транзистора N2 соединены одно с другим, (iii) исток транзистора Р1 соединен с клеммой SB, (iv) исток транзистора N1 соединен с клеммой R, (v) исток транзистора Р2 соединен с клеммой INITB и (vi) исток транзистора N2 соединен с клеммой VSS. Здесь, транзистор Р1, транзистор N1, транзистор Р2 и транзистор N2 составляют схему LC защелки.

Фиг.19 (b) представляет таблицу истинности для триггера FF 103 (когда INITB-сигнал неактивен). Выходной Q-сигнал триггера FF 103 является таковым, что (i) он имеет низкий уровень (неактивен) в течение периода времени, в котором SB-сигнал имеет высокий уровень (неактивен) и R-сигнал имеет высокий уровень (активен), (ii) он находится в состоянии удержания в течение периода времени, когда SB-сигнал имеет высокий уровень (неактивен) и R-сигнал имеет низкий уровень (неактивен), (iii) он находится в неопределенном состоянии в течение периода времени, когда SB-сигнал имеет низкий уровень (активен) и R-сигнал is имеет высокий уровень (активен), и (iv) он имеет высокий уровень (активен) в течение периода времени, когда SB-сигнал is имеет низкий уровень (активен) и R-сигнал имеет низкий уровень (неактивен) (см. фиг.19 (b)).

Фиг.20 (а) представляет электрическую схему, иллюстрирующую конфигурацию триггера FF 104, являющегося модифицированным примером триггера, показанного на фиг.19 (а). Триггер FF 104, изображенный на фиг.20 (а), включает (i) p-канальный транзистор Р3 и n-канальный транзистор N3, которые составляют КМОП-схему, (ii) p-канальный транзистор Р4 и n-канальный транзистор N4, которые составляют другую КМОП-схему, (iii) клемму S, (iv) клемму RB, (v) клемму INIT, (vi) клемму Q и (vii) клемму QB. В схеме триггера FF 104 (i) затвор транзистора Р3, затвор транзистора N3, сток транзистора Р4, сток транзистора N4 и клемма Q соединены одно с другим, (ii) сток транзистора Р3, сток транзистора N3, затвор транзистора Р4 и затвор транзистора N4 соединены одно с другим, (iii) исток транзистора N4 соединен с клеммой S, (iv) исток транзистора Р4 соединен с клеммой RB, (v) исток транзистора N3 соединен с клеммой INIT и (vi) исток транзистора Р3 соединен с клеммой VDD. Здесь, транзистор Р3, транзистор N3, транзистор Р4 и транзистор N4 составляют схему LC защелки.

Фиг.20 (b) представляет таблицу истинности для триггера FF 104 (когда INITB-сигнал неактивен). Выходной Q-сигнал триггера FF 104 является таковым, что (i) он имеет высокий уровень (активен) в течение периода времени, в котором S-сигнал имеет высокий уровень (активен) и RB-сигнал имеет высокий уровень (неактивен), (ii) он находится в неопределенном состоянии в течение периода времени, в котором S-сигнал имеет высокий уровень (активен) и RB-сигнал имеет низкий уровень (активен), (iii) он находится в состоянии удержания в течение периода времени, в котором S-сигнал имеет низкий уровень (неактивен) и RB-сигнал имеет высокий уровень (неактивен), и (iv) он имеет низкий уровень (неактивен) в течение периода времени, в котором S-сигнал имеет низкий уровень (неактивен) и RB-сигнал имеет низкий уровень (активен) (см. фиг.20 (b)).

[Триггер согласно варианту 2]

Фиг.3 (а) представляет электрическую схему, иллюстрирующую конфигурацию триггера согласно варианту 2 настоящего изобретения. Триггер FF 201, показанный на фиг.3 (а), включает (i) p-канальный транзистор р6 и n-канальный транзистор n5, которые составляют КМОП-схему, (ii) p-канальный транзистор р8 и n-канальный транзистор n7, которые составляют другую КМОП-схему, (iii) p-канальные транзисторы р5 и р7, (iv) n-канальные транзисторы n6 и n8, (v) клемму SB, (vi) клемму RB, (vii) клемму INITB, (viii) клемму Q и (ix) клемму QB. В схеме триггера FF 201 (i) затвор транзистора р6, затвор транзистора n5, сток транзистора р7, сток транзистора р8, сток транзистора n7 и клемма QB соединены одно с другим, (ii) сток транзистора р6, сток транзистора n5, сток транзистора р5, затвор транзистора р8, затвор транзистора n7 и клемма Q соединены одно с другим, (iii) исток транзистора n5 и сток транзистора n6 соединены один с другим, (iv) исток транзистора n7 и сток транзистора n8 соединены один с другим, (v) затвор транзистора р5 и затвор транзистора n6 соединены с клеммой SB, (vi) исток транзистора р5, затвор транзистора р7 и затвор транзистора n8 соединены с клеммой RB, (vii) исток транзистора р6 соединен с клеммой INITB, (viii) исток транзистора р7 и исток транзистора р8 соединены с клеммой VDD и (ix) исток транзистора n6 и исток транзистора n8 соединены с клеммой VSS. Здесь, транзистор р6, транзистор n5, транзистор р8 и транзистор n7 составляют схему LC защелки. Транзистор р5 служит транзистором ST установки. Транзистор р7 служит транзистором RT сброса. Транзистор n6 служит транзистором LRT освобождения защелки (освобождающий транзистор). Транзистор n8 служит транзистором LRT освобождения защелки (освобождающий транзистор).

Фиг.3 (b) представляет временную диаграмму, показывающую работу триггера FF 201 (когда INITB-сигнал неактивен), и фиг.3 (с) представляет таблицу истинности для триггера FF 201 (когда INITB-сигнал неактивен). Выходной Q-сигнал триггера FF 201 является таковым, что (i) он имеет низкий уровень (неактивен) в течение периода времени, в котором SB-сигнал имеет низкий уровень (активен) и RB-сигнал имеет низкий уровень (активен), (ii) он имеет высокий уровень (активен) в течение периода времени, в котором SB-сигнал имеет низкий уровень (активен) и RB-сигнал имеет высокий уровень (неактивен), (iii) он имеет низкий уровень (неактивен) в течение периода времени, в котором SB-сигнал имеет высокий уровень (неактивен) и RB-сигнал имеет низкий уровень (активен), и (iv) он находится в состоянии удержания в течение периода времени, в котором SB-сигнал имеет высокий уровень (неактивен) и RB-сигнал имеет высокий уровень (неактивен) (см. фиг.3 (b) и (с)).

Например, в течение периода t1 времени, показанного на фиг.3 (b), клемма Q получает напряжение Vdd от клеммы RB. Это отпирает транзистор n7. Соответственно, клемма QB получает напряжение Vss (низкий уровень). При этом в течение периода t2 времени SB-сигнал находится на высоком уровне. Это вызывает запирание транзистора р5 и отпирание транзистора n6. Соответственно, состояние, имевшее место в период t1, сохраняется в течение периода t2. В течение периода t3 времени RB-сигнал находится на низком уровне. Это вызывает отпирание транзистора р7. Соответственно, клемма QB получает напряжение Vdd (высокий уровень). Далее, транзистор n5 отпирается, так что клемма Q получает напряжение Vss. Когда оба сигнала - SB-сигнал и RB-сигнал, перешли на низкий уровень (активен), (i) транзистор р7 отпирается и клемма QB получает напряжение Vdd (высокий уровень) и (ii) клемма Q получает напряжение Vss + Vth (пороговое напряжение транзистора р5) через транзистор р5.

Более того, когда оба сигнала, SB-сигнал и RB-сигнал, становятся неактивными в период времени, в котором INITB-сигнал активен, оба выходных сигнала, Q-сигнал и QB-сигнал, триггера FF 201 становятся неактивными.

Например, если в период времени, в котором INITB-сигнал имеет низкий уровень (активен), оба сигнала, SB-сигнал и RB-сигнал, переходят из состояния А, в котором оба эти сигнала, SB-сигнал и RB-сигнал, имеют низкий уровень (активен), в состояние X, в котором оба эти сигнала, SB-сигнал и RB-сигнал, имеют высокий уровень (неактивен), выходные сигналы на соответствующих клемме Q и клемме QB остаются такими же, как и в состоянии А. Это происходит потому, что (i) в состоянии А транзистор р7 открыт, а транзистор р6 заперт, так что клемма QB получает напряжение Vdd (высокий уровень), а клемма Q получает напряжение Vss, и также (ii) транзистор р6 остается заперт в состоянии X. Далее, если в период времени, в котором INITB-сигнал имеет низкий уровень (активен), SB-сигнал и RB-сигнал переходят из состояния В, в котором SB-сигнал имеет высокий уровень (неактивен) и RB-сигнал имеет низкий уровень (активен), в состояние X, в котором оба сигнала, SB-сигнал и RB-сигнал, имеют высокий уровень (неактивен), выходные сигналы на соответствующих клемме Q и клемме QB остаются такими же, как и в состоянии В. Это происходит потому, что (i) в состоянии В транзистор р7 и транзистор р5 - оба открыты, так что клемма QB получает напряжение Vdd (высокий уровень) и клемма Q получает напряжение Vss (низкий уровень), а также (ii) транзистор р6 в состоянии Х остается заперт. Более того, если в период времени, в котором INITB-сигнал имеет низкий уровень (активен), SB-сигнал и RB-сигнал переходят из состояния С, в котором SB-сигнал имеет низкий уровень (активен) и RB-сигнал имеет высокий уровень (неактивен), в состояние X, в котором оба сигнала, SB-сигнал и RB-сигнал, имеют высокий уровень (неактивен), клемма Q получает напряжение Vss (низкий уровень), и клемма QB получает напряжение Vdd (высокий уровень). Иными словами, выходные сигналы на соответствующих клемме Q и клемме QB в состоянии С находятся в неопределенном состоянии. Когда транзистор р6 отпирается непосредственно перед тем, как SB-сигнал и RB-сигнал изменят свое состояние в соответствии с переходом от состояния С в состояние X, потенциал клеммы Q сразу же становится равным Vss + Vth (пороговое напряжение транзистора р6). Это вызывает отпирание транзистора р8, так что клемма QB получает напряжение Vdd (высокий уровень). В этом случае транзистор n5, с которым соединена клемма QB, отпирается, так что клемма Q получает напряжение Vss (низкий уровень). Далее, если транзистор р6 запирается непосредственно перед тем, как SB-сигнал и RB-сигнал перешли из состояния С в состояние X, т.е. в ситуации, когда транзистор р6, составляющий схему LC защелки, заперт, а транзистор n5, составляющий инвертор, открыт, клемма Q получает напряжение Vss (низкий уровень). Это вызывает отпирание транзистора р8, затвор которого соединен с клеммой Q. Соответственно, клемма QB получает напряжение Vdd (высокий уровень). Как описано выше, клемма Q получает напряжение Vss (низкий уровень), и клемма QB получает напряжение Vdd (высокий уровень) в состоянии X, независимо от того, каким неопределенным состоянием является состояние С.

Как описано выше, в схеме триггера FF 201 (i) транзистор р6, транзистор n5, транзистор р8 и транзистор n7 (две КМОП-схемы) составляют схему защелки, (ii) клемма RB соединена с (а) затвором транзистора р7, который служит транзистором RT сброса, и (b) истоком транзистора р5, который служит транзистором ST установки, и (iii) исток транзистора р6 соединен с клеммой INITB. В такой конфигурации можно выполнять операцию установки, операцию защелкивания, операцию сброса, операцию определения приоритета (когда оба сигнала - SB-сигнал и RB-сигнал, стали активным одновременно), и инициализации без применения схемы определения приоритета и схемы инициализации, каждая из которых была нужна в обычном триггере (см. фиг.70). Как описано выше, в триггере FF 201, когда SB-сигнал и RB-сигнал стали активными одновременно, RB-сигнал (сброс) имеет приоритет, так что выходной сигнал на клемме QB становится неактивным.

Отметим, что триггер FF 201, показанный на фиг.3 (а), может быть модифицирован таким образом, что исток транзистора р6 будет соединен с клеммой VDD, как в триггере FF 209, изображенном на фиг.22 (а). Фиг.22 (b) представляет таблицу истинности для триггера FF 209.

Фиг.4 (а) представляет электрическую схему, иллюстрирующую конфигурацию триггера FF 202, который является модифицированным примером триггера, показанного на фиг.3 (а). Триггер FF 202, изображенный на фиг.4 (а), включает (i) p-канальный транзистор р10 и n-канальный транзистор n10, которые составляют КМОП-схему, (ii) p-канальный транзистор р12 и n-канальный транзистор n12, которые составляют другую КМОП-схему, (iii) p-канальные транзисторы р9 и p11, (iv) n-канальные транзисторы n9 и n12, (v) клемму S, (vi) клемму R, (vii) клемму INIT, (viii) клемму Q и (ix) клемму QB. В схеме триггера FF 202 (i) затвор транзистора р10, затвор транзистора n10, сток транзистора р12, сток транзистора n12, сток транзистора n9 и клемма QB соединены одно с другим, (ii) сток транзистора р10, сток транзистора n10, сток транзистора n10, затвор транзистора р12, затвор транзистора n12, сток транзистора n11 и клемма Q соединены одно с другим, (iii) исток транзистора р10 и сток транзистора n9 соединены один с другим, (iv) исток транзистора р12 и сток транзистора p11 соединены один с другим, (v) затвор транзистора n9 и затвор транзистора n11 соединены с клеммой S, (vi) исток транзистора n9, затвор транзистора р9 и затвор транзистора n11 соединены с клеммой R, (vii) исток транзистора n12 соединен с клеммой INIT, (viii) исток транзистора р9 и исток транзистора р11 соединены с клеммой VDD и (ix) исток транзистора n10 и исток транзистора n11 соединены с клеммой VSS. Здесь, транзистор р10, транзистор n10, транзистор р12 и транзистор n12 составляют схему LC защелки. Транзистор n9 служит транзистором ST установки. Транзистор nil служит транзистором RT сброса. Транзистор р9 служит транзистором LRT освобождения защелки, и транзистор р11 также служит транзистором LRT освобождения защелки.

Фиг.4 (b) представляет временную диаграмму, показывающую работу триггера FF 202 (когда INIT-сигнал неактивен), и фиг.4 (с) представляет таблицу истинности для триггера FF 202 (когда INIT-сигнал неактивен). Выходной Q-сигнал триггера FF 202 является таковым, что (i) он находится в состоянии удержания в течение периода времени, в котором S-сигнал имеет низкий уровень (неактивен) и R-сигнал имеет низкий уровень (неактивен), (n) он имеет низкий уровень (неактивен) в течение периода времени, в котором S-сигнал имеет низкий уровень (неактивен) и R-сигнал имеет высокий уровень (активен), (iii) он имеет высокий уровень (активен) в течение периода времени, в котором S-сигнал имеет высокий уровень (активен) и R-сигнал имеет низкий уровень (неактивен), и (iv) он имеет низкий уровень (неактивен) в течение периода времени, в котором S-сигнал имеет высокий уровень (активен) и R-сигнал is имеет высокий уровень (активен) (см. фиг.4 (b) и (с)).

Далее, если оба сигнала, S-сигнал и R-сигнал, стали неактивными в период времени, в котором INIT-сигнал активен, оба выходных сигнала, Q-сигнал и QB-сигнал, триггера FF 202 становятся неактивными.

Фиг.7 (а) представляет электрическую схему, иллюстрирующую другую конфигурацию триггера согласно варианту 2 настоящего изобретения. Триггер FF 203, показанный на фиг.7 (а), включает (i) p-канальный транзистор р22 и n-канальный транзистор n21, которые составляют КМОП-схему, (ii) p-канальный транзистор р23 и n-канальный транзистор n22, которые составляют другую КМОП-схему, (iii) p-канальный транзистор р21, (iv) клемму SB, (v) клемму RB, (vi) клемму INIT, (vii) клемму Q и (viii) клемму QB. В схеме триггера FF 203 (i) затвор транзистора р22, затвор транзистора n21, сток транзистора р23, сток транзистора n22, сток транзистора р21 и клемма Q соединены одно с другим, (ii) сток транзистора р22, сток транзистора n21, затвор транзистора р23, затвор транзистора n22 и клемма QB соединены одно с другим, (iii) затвор транзистора р21 соединен с клеммой SB, (iv) исток транзистора р21 и исток транзистора р23 соединены с клеммой RB, (v) исток транзистора n21 соединен с клеммой INIT, и (vi) исток транзистора n22 соединен с клеммой VSS. Здесь, транзистор р22, транзистор n21, транзистор р23 и транзистор n22 составляют схему LC защелки, а транзистор р21 служит транзистором ST установки.

Фиг.7 (b) представляет временную диаграмму, показывающую работу триггера FF 203 (когда INIT-сигнал неактивен), и фиг.7 (с) представляет таблицу истинности для триггера FF 203 (когда INIT-сигнал неактивен). Выходной Q-сигнал триггера FF 203 являются таковым, что (i) он имеет низкий уровень (неактивен) в течение периода времени, в котором SB-сигнал имеет низкий уровень (активен) и RB-сигнал имеет низкий уровень (активен), (ii) он имеет высокий уровень (активен) в течение периода времени, в котором SB-сигнал имеет низкий уровень (активен) и RB-сигнал имеет высокий уровень (неактивен), (hi) он имеет низкий уровень (неактивен) в течение периода времени, в котором SB-сигнал имеет высокий уровень (неактивен) и RB-сигнал имеет низкий уровень (активен), и (iv) он находится в состоянии удержания в течение периода времени, в котором SB-сигнал имеет высокий уровень (неактивен) и RB-сигнал имеет высокий уровень (неактивен) (см. фиг.7 (b) и (с)).

Например, в течение периода t1 времени, показанного на фиг.7 (b), клемма Q получает напряжение Vdd (высокий уровень) от клеммы RB. Соответственно, транзистор n21 открыт, так что клемма QB получает напряжение Vss (низкий уровень). Затем, в течение периода t2 времени SB-сигнал находится на высоком уровне, так что транзистор р21 заперт. Соответственно, сохраняется состояние, имевшее место в периоде t1. В течение периода t3 времени RB-сигнал находится на низком уровне. Соответственно, клемма Q временно получает напряжение Vss + Vth (пороговое напряжение транзистора р23) через транзистор р23. Это вызывает отпирание транзистора р22, так что клемма QB получает напряжение Vdd (высокий уровень). Далее, поскольку клемма QB получает напряжение Vdd, транзистор n22 открыт. Соответственно, клемма Q получает напряжение Vss. Отметим, что когда оба сигнала, SB-сигнал и RB-сигнал, имеют низкий уровень (активен), клемма Q временно получает напряжение Vss + Vth через транзистор р21. Это вызывает отпирание транзистора р22, так что клемма QB получает напряжение Vdd (высокий уровень). Далее, поскольку клемма QB получает напряжение Vdd, транзистор n22 открыт. Соответственно, клемма Q получает напряжение Vss.

Как описано выше, в схеме триггера FF 203 (i) транзистор р22, транзистор n21, транзистор р23 и транзистор n22 (две КМОП-схемы) составляют схему защелки, (ii) клемма RB соединена с (а) истоком транзистора р21, который служит транзистором ST установки, и (b) истоком транзистора р23, и (iii) исток транзистора n21 соединен с клеммой INIT. В такой конфигурации можно выполнять операцию установки, операцию защелкивания, операцию сброса, операцию определения приоритета (когда SB-сигнал и RB-сигнал стали активными одновременно) и операцию инициализации без применения схемы сброса, схемы освобождения защелки, схемы определения приоритета и схемы инициализации, каждая из которых была нужна в известном триггере (см. фиг.70). Как описано выше, когда SB-сигнал и RB-сигнал триггера FF 203 стали активными одновременно, RB-сигнал (сброса) имеет приоритет, так что выходные сигнала на соответствующих клемме Q и клемме QB становятся неактивными.

Фиг.8 (а) представляет электрическую схему, иллюстрирующую конфигурацию триггера FF 204, представляющего собой модифицированный пример триггера, показанного на фиг.7 (а). Триггер FF 204, изображенный на фиг.8 (а), включает (i) p-канальный транзистор р24 и n-канальный транзистор n24, которые составляют КМОП-схему, (ii) p-канальный транзистор р25 и n-канальный транзистор n25, которые составляют другую КМОП-схему, (hi) n-канальный транзистор n23, (iv) клемму S, (v) клемму R, (vi) клемму INITB, (vii) клемму Q и (viii) клемму QB. В схеме триггера FF 204 (i) затвор транзистора р24, затвор транзистора n24, сток транзистора р25, сток транзистора n25, сток транзистора n23 и клемма QB соединены одно с другим, (ii) сток транзистора р24, сток транзистора n24, затвор транзистора р25, затвор транзистора n25 и клемма Q соединены одно с другим, (iii) затвор транзистора n23 соединен с клеммой S, (iv) исток транзистора n23 и исток транзистора n25 соединены с клеммой R, (v) исток транзистора р24 соединен с клеммой INITB, (vi) исток транзистора р25 соединен с клеммой VDD и (vii) исток транзистора n24 соединен с клеммой VSS. Здесь, транзистор р24, транзистор n24, транзистор р25 и транзистор n25 составляют схему LC защелки, а транзистор n23 служит транзистором ST установки.

Фиг.8 (b) представляет временную диаграмму, показывающую работу триггера FF 204 (когда INITB-сигнал неактивен), и фиг.8 (с) представляет таблицу истинности для триггера FF 204 (когда INITB-сигнал неактивен). Выходной Q-сигнал триггера FF 204 является таковым, что (i) он находится в состоянии удержания в течение периода времени, в котором S-сигнал имеет низкий уровень (неактивен) и R-сигнал имеет низкий уровень (неактивен), (ii) он имеет низкий уровень (неактивен) в течение периода времени, в котором S-сигнал имеет низкий уровень (неактивен) и R-сигнал имеет высокий уровень (активен), (iii) он имеет высокий уровень (активен) в течение периода времени, в котором S-сигнал имеет высокий уровень (активен) и R-сигнал имеет низкий уровень (неактивен), и (iv) он имеет низкий уровень (неактивен) в течение периода времени, в котором S-сигнал имеет высокий уровень (активен) и R-сигнал имеет высокий уровень (активен) (см. фиг.8 (b) и (с)).

Фиг.11 (а) представляет схему, иллюстрирующую другую конфигурацию триггера согласно варианту 2 настоящего изобретения. Триггер FF 205, показанный на фиг.11 (а), включает (i) p-канальный транзистор р32 и n-канальный транзистор n31, которые составляют КМОП-схему, (ii) p-канальный транзистор р34 и n-канальный транзистор n32, которые составляют другую КМОП-схему, (iii) p-канальные транзисторы р31 и p33, (iv) клемму SB, (v) клемму RB, (vi) клемму INITB, (vii) клемму Q и (viii) клемму QB. В схеме триггера FF 205 (i) затвор транзистора р32, затвор транзистора n31, сток транзистора р34, сток транзистора n32, сток транзистора p33 и клемма QB соединены одно с другим, (ii) сток транзистора р32, сток транзистора n31, затвор транзистора р34, затвор транзистора n32, сток транзистора р31 и клемма Q соединены одно с другим, (iii) затвор транзистора р31 соединен с клеммой SB, (iv) исток транзистора р31 и затвор транзистора p33 соединены с клеммой RB, (v) исток транзистора р32 соединен с клеммой INITB, (vi) исток транзистора p33 и исток транзистора р34 соединены с клеммой VDD, и (vii) исток транзистора n31 и исток транзистора n32 соединены с клеммой VSS. Здесь, транзистор р32, транзистор n31, транзистор р34 и транзистор n32 составляют схему LC защелки, транзистор р31 служит транзистором ST установки, а транзистор p33 служит транзистором RT сброса.

Фиг.11 (b) представляет таблицу истинности для триггера FF 205 (когда INIT-сигнал неактивен). Выходной Q-сигнал триггера FF 205 является таковым, что (i) он имеет низкий уровень (неактивен) в течение периода времени, в котором SB-сигнал имеет низкий уровень (активен) и RB-сигнал имеет низкий уровень (активен), (ii) он имеет высокий уровень (активен) в течение периода времени, в котором SB-сигнал имеет низкий уровень (активен) и RB-сигнал имеет высокий уровень (неактивен), (iii) он имеет низкий уровень (неактивен) в течение периода времени, в котором SB-сигнал имеет высокий уровень (неактивен) и RB-сигнал имеет низкий уровень (активен), и (iv) он находится в состоянии удержания в течение периода времени, в котором SB-сигнал имеет высокий уровень (неактивен) и RB-сигнал имеет высокий уровень (неактивен) (см. фиг.11 (b)).

Фиг.12 (а) представляет электрическую схему, иллюстрирующую конфигурацию триггера FF 206, который является модифицированным примером триггера, изображенного на фиг.11 (а). Триггер FF 206, показанный на фиг.12 (а), включает (i) p-канальный транзистор р35 и n-канальный транзистор n34, которые составляют КМОП-схему, (ii) p-канальный транзистор р36 и n-канальный транзистор n36, которые составляют другую КМОП-схему, (iii) n-канальные транзисторы n33 и n35, (iv) клемму S, (v) клемму R, (vi) клемму INITB, (vii) клемму Q и (viii) клемму QB. В схеме триггера FF 206 (i) затвор транзистора р35, затвор транзистора n34, сток транзистора р36, сток транзистора n36, сток транзистора n33 и клемма QB соединены одно с другим, (ii) сток транзистора р35, сток транзистора n34, затвор транзистора р36, затвор транзистора n36, сток транзистора n35 и клемма Q соединены одно с другим, (iii) затвор транзистора n33 соединен с клеммой S, (iv) исток транзистора n33 и затвор транзистора n35 соединены с клеммой R, (v) исток транзистора р35 соединен с клеммой INITB, (vi) исток транзистора р36 соединен с клеммой VDD и (vii) исток транзистора n35 соединен с клеммой VSS. Здесь, транзистор р35, транзистор n34, транзистор р36 и транзистор n36 составляют схему LC защелки. Транзистор n33 служит транзистором ST установки. Транзистор n35 служит транзистором RT сброса.

Фиг.12 (b) представляет таблицу истинности для триггера FF 206 (когда INITB-сигнал неактивен). Выходной Q-сигнал триггера FF 206 является таковым, что (i) он находится в состоянии удержания в течение периода времени, в котором S-сигнал имеет низкий уровень (неактивен) и R-сигнал имеет низкий уровень (неактивен), (ii) он имеет низкий уровень (неактивен) в течение периода времени, в котором S-сигнал имеет низкий уровень (неактивен) и R-сигнал имеет высокий уровень (активен), (iii) он имеет высокий уровень (активен) в течение периода времени, в котором S-сигнал имеет высокий уровень (активен) и R-сигнал имеет низкий уровень (неактивен), и (iv) он имеет низкий уровень (неактивен) в течение периода времени, в котором S-сигнал имеет высокий уровень (активен) и R-сигнал имеет высокий уровень (активен) (см. фиг.12 (b) и (с)).

Фиг.15 (а) представляет схему, иллюстрирующую другую конфигурацию триггера согласно варианту 2 настоящего изобретения. Триггер FF 207, показанный на фиг.15 (а), включает (i) p-канальный транзистор р44 и n-канальный транзистор n43, которые составляют КМОП-схему, (ii) p-канальный транзистор р45 и n-канальный транзистор n44, которые составляют другую КМОП-схему, (iii) p-канальный транзистор р43, (iv) n-канальный транзистор n45, (v) клемму SB, (vi) клемму RB, (vii) клемму INIT, (viii) клемму Q и (ix) клемму QB. В схеме триггера FF 207 (i) затвор транзистора р44, затвор транзистора n43, сток транзистора р45, сток транзистора n44, сток транзистора р43 и клемма Q соединены одно с другим, (ii) сток транзистора р44, сток транзистора n43, затвор транзистора р45, затвор транзистора n44 и клемма QB соединены одно с другим, (iii) исток транзистора n44 и сток транзистора n45 соединены одно с другим, (iv) затвор транзистора р43 и затвор транзистора n45 соединены с клеммой SB, (v) исток транзистора р43 и исток транзистора р45 соединены с клеммой RB, (vi) исток транзистора n43 соединен с клеммой INIT, (vii) исток транзистора р44 соединен с клеммой VDD, и (viii) исток транзистора n45 соединен с клеммой VSS. Здесь, транзистор р44, транзистор n43, транзистор р45 и транзистор n44 составляют схему LC защелки. Транзистор р43 служит транзистором ST установки. Транзистор n45 служит транзистором LRT схемы освобождения защелки.

Фиг.15 (b) представляет таблицу истинности (когда INIT-сигнал неактивен). Выходной Q-сигнал триггера FF 207 является таковым, что (i) он имеет низкий уровень (неактивен) в течение периода времени, в котором SB-сигнал имеет низкий уровень (активен) и RB-сигнал имеет низкий уровень (активен), (ii) он имеет высокий уровень (активен) в течение периода времени, в котором SB-сигнал имеет низкий уровень (активен) и RB-сигнал имеет высокий уровень (неактивен), (iii) он имеет низкий уровень (неактивен) в течение периода времени, в котором SB-сигнал имеет высокий уровень (неактивен) и RB-сигнал имеет низкий уровень (активен), и (iv) он находится в состоянии удержания в течение периода времени, в котором SB-сигнал имеет высокий уровень (неактивен) и RB-сигнал имеет высокий уровень (неактивен) (см. фиг.15 (b)).

Фиг.16 (а) 16 представляет электрическую схему, иллюстрирующую конфигурацию триггера FF 208, который является модифицированным примером триггера, показанного на фиг.15 (а). Триггер FF 208, показанный на фиг.16 (а), включает (i) p-канальный транзистор р46 и n-канальный транзистор n47, которые составляют КМОП-схему, (ii) p-канальный транзистор р48 и n-канальный транзистор n48, которые составляют другую КМОП-схему, (iii) n-канальный транзистор n46, (iv) p-канальный транзистор р47, (v) клемму S, (vi) клемму R, (vii) клемму INITB, (viii) клемму Q и (ix) клемму QB. В схеме триггера FF 208 (i) затвор транзистора р46, затвор транзистора n47, сток транзистора р48, сток транзистора n48, сток транзистора n46 и клемма QB соединены одно с другим, (ii) сток транзистора р46, сток транзистора n47, затвор транзистора р48, затвор транзистора n48 и клемма Q соединены одно с другим, (iii) сток транзистора р47 и исток транзистора р48 соединены одно с другим, (iv) затвор транзистора n46 и затвор транзистора р47 соединены с клеммой S, (v) исток транзистора n46 и исток транзистора n48 соединены с клеммой R, (vi) исток транзистора р46 соединен с клеммой INITB, (vii) исток транзистора р47 соединен с клеммой VDD, и (viii) исток транзистора n47 соединен с клеммой VSS. Здесь, транзистор р46, транзистор n47, транзистор р48 и транзистор n48 составляют схему LC защелки. Транзистор n46 служит транзистором ST установки. Транзистор р47 служит транзистором LRT освобождения защелки.

Фиг.16 (b) представляет таблицу истинности для триггера FF 208 (когда INITB-сигнал неактивен). Выходной Q-сигнал триггера FF 208 является таковым, что (i) он находится в состоянии удержания в течение периода времени, в котором S-сигнал имеет низкий уровень (неактивен) и R-сигнал имеет низкий уровень (неактивен), (ii) он имеет низкий уровень (неактивен) в течение периода времени, в котором S-сигнал имеет низкий уровень (неактивен) и R-сигнал имеет высокий уровень (активен), (iii) он имеет высокий уровень (активен) в течение периода времени, в котором S-сигнал имеет высокий уровень (активен) и R-сигнал имеет низкий уровень (неактивен), и (iv) он имеет низкий уровень (неактивен) в течение периода времени, в котором S-сигнал имеет высокий уровень (активен) и R-сигнал имеет высокий уровень (активен) (см. фиг.16 (b)).

Фиг.25 (а) представляет электрическую схему, иллюстрирующую конфигурацию триггера FF 210. Триггер FF 210, показанный на фиг.25 (а), включает (i) p-канальный транзистор р84 и n-канальный транзистор n84, которые составляют КМОП-схему, (ii) p-канальный транзистор р85 и n-канальный транзистор n85, которые составляют другую КМОП-схему, (iii) p-канальные транзисторы р81, р82 и р83, (iv) n-канальные транзисторы n82 и n83, (v) клемму SB, (vi) клемму R, (vii) клемму INIT, (viii) клемму Q и (ix) клемму QB. В схеме триггера FF 210 (i) затвор транзистора р84, затвор транзистора n84, сток транзистора р85, сток транзистора n85 и клемма QB соединены одно с другим, (ii) сток транзистора р84, сток транзистора n84, сток транзистора р81, сток транзистора n82, затвор транзистора р85, затвор транзистора n85 и клемма Q соединены одно с другим, (iii) исток транзистора р84 и сток транзистора р83 соединены один с другим, (iv) исток транзистора р81 и сток транзистора р82 соединены один с другим, (v) затвор транзистора р81 и затвор транзистора n83 соединены с клеммой SB, (vi) затвор транзистора n82, затвор транзистора р82 и затвор транзистора р83 соединены с клеммой R, (vii) исток транзистора n85 соединен с клеммой INIT, (viii) исток транзистора р82, исток транзистора р83 и исток транзистора р85 соединены с клеммой VDD, и (ix) исток транзистора n82 и исток транзистора n83 соединены с клеммой VSS. Здесь, транзистор р84, транзистор n84, транзистор р85 и транзистор n85 составляют схему LC защелки. Транзистор р81 служит транзистором ST установки. Транзистор n82 служит транзистором RT сброса. Транзистор р83 служит транзистором LRT освобождения защелки. Транзистор n83 служит транзистором LRT освобождения защелки. Транзистор р82 служит транзистором PDT определения приоритета.

Фиг.25 (b) представляет таблицу истинности для триггера FF 210 (когда INIT-сигнал неактивен). Выходной Q-сигнал триггера FF 210 является таковым, что (i) он имеет низкий уровень (неактивен) в течение периода времени, в котором SB-сигнал имеет высокий уровень (неактивен) и R-сигнал имеет высокий уровень (активен), (ii) он находится в состоянии удержания в течение периода времени, в котором SB-сигнал имеет высокий уровень (неактивен) и R-сигнал имеет низкий уровень (неактивен), (iii) он имеет низкий уровень (неактивен) в течение периода времени, в котором SB-сигнал имеет низкий уровень (активен) и R-сигнал имеет высокий уровень (активен), и (iv) он имеет высокий уровень (активен) в течение периода времени, в котором SB-сигнал имеет низкий уровень (активен) и R-сигнал имеет низкий уровень (неактивен) (см. фиг.25 (b)).

Отметим, что можно модифицировать триггер FF 210, показанный на фиг.25 (а), таким образом, что исток транзистора р85 будет соединен с клеммой INITB, а исток транзистора n85 соединен с клеммой VSS, как в триггере FF 211, изображенном на фиг.27 (а). Фиг.27 (b) представляет таблицу истинности для триггера FF 211.

[Триггер согласно варианту 3]

Фиг.5 (а) представляет электрическую схему, иллюстрирующую конфигурацию триггера согласно варианту 3 настоящего изобретения. Триггер FF 301, показанный на фиг.5 (а) включает (i) p-канальный транзистор р14 и n-канальный транзистор n13, которые составляют КМОП-схему, (ii) p-канальный транзистор р16 и n-канальный транзистор n15, которые составляют другую КМОП-схему, (iii) p-канальные транзисторы р13 и р15, (iv) n-канальные транзисторы n14 и n16, (v) клемму SB, (vi) клемму RB, (vii) клемму INITB, (viii) клемму Q и (ix) клемму QB. В схеме триггера FF 301 (i) затвор транзистора р14, затвор транзистора n13, сток транзистора р16, сток транзистора р15, сток транзистора р15 и клемма Q соединены одно с другим, (ii) сток транзистора р14, сток транзистора n13, затвор транзистора р16, затвор транзистора n15, сток транзистора р13 и клемма QB соединены одно с другим, (iii) исток транзистора n13 и сток транзистора n14 соединены одно с другим, (iv) исток транзистора n15 и сток транзистора n16 соединены одно с другим, (v) исток транзистора р13, затвор транзистора р15 и затвор транзистора n16 соединены с клеммой SB, (vi) затвор транзистора р13 и затвор транзистора n14 соединены с клеммой RB, (vii) исток транзистора р16 соединен с клеммой INITB, (viii) исток транзистора р14 и исток транзистора р15 соединены с клеммой VDD, и (ix) исток транзистора n14 и исток транзистора n16 соединены с клеммой VSS. Здесь, транзистор р14, транзистор n13, транзистор р16 и транзистор n15 составляют схему LC защелки. Транзистор р15 служит транзистором ST установки. Транзистор р13 служит транзистором RT сброса. Транзистор n14 служит транзистором LRT освобождения защелки. Транзистор n16 служит транзистором LRT освобождения защелки.

Фиг.5 (b) представляет временную диаграмму, показывающую работу триггера FF 301 (когда INITB-сигнал неактивен), и фиг.5 (с) представляет таблицу истинности для триггера FF 301 (когда INITB-сигнал неактивен). Выходной Q-сигнал триггера FF 301 является таковым, что (i) он имеет высокий уровень (активен) в течение периода времени, в котором SB-сигнал имеет низкий уровень (активен) и RB-сигнал имеет низкий уровень (активен), (ii) он имеет высокий уровень (активен) в течение периода времени, в котором SB-сигнал имеет низкий уровень (активен) и RB-сигнал имеет высокий уровень (неактивен), (iii) он имеет низкий уровень (неактивен) в течение периода времени, в котором SB-сигнал имеет высокий уровень (неактивен) и RB-сигнал имеет низкий уровень (активен), и (iv) он находится в состоянии удержания в течение периода времени, в котором SB-сигнал имеет высокий уровень (неактивен) и RB-сигнал имеет высокий уровень (неактивен) (см. фиг.5 (b) и (с)).

Например, в течение периода t1 времени, показанного на фиг.15 (b), транзистор р15 открыт, так что клемма Q получает напряжение Vdd (высокий уровень). Это вызывает отпирание транзистора n13, так что клемма QB получает напряжение Vss (низкий уровень). Затем, в течение периода t2 времени SB-сигнал находится на высоком уровне, так что транзистор р15 заперт, а транзисторы n14 и n16 открыты. Соответственно, состояние, имевшее место в периоде t1, сохраняется в течение периода t2 времени. В течение периода t3 времени RB-сигнал находится на низком уровне, так что клемма QB получает напряжение Vdd (высокий уровень) от клеммы SB. Это вызывает отпирание транзистора n15, так что клемма Q получает напряжение Vss (низкий уровень). Отметим, что когда оба сигнала, SB-сигнал и RB-сигнал, перешли на низкий уровень (активен), (i) транзистор р15 открыт, так что клемма Q получает напряжение Vdd (высокий уровень) и (ii) клемма QB получает напряжение Vss + Vth (пороговое напряжение транзистора р13) через транзистор р13.

Далее, когда оба сигнала, SB-сигнал и RB-сигнал, стали неактивными в период времени, в котором INITB-сигнал активен, выходные сигналы, Q-сигнал и QB-сигнал, триггера FF 301 стали неактивными.

Например, если в период времени, в котором INITB-сигнал имеет низкий уровень (активен), SB-сигнал и RB-сигнал изменили состояния от состояния А, в котором SB-сигнал имеет низкий уровень (активен) и RB-сигнал имеет низкий уровень (активен), к состоянию X, в котором оба сигнала, SB-сигнал и RB-сигнал, имеют высокий уровень (неактивен), клемма Q получает напряжение Vss (низкий уровень), а клемма QB получает напряжение Vdd (высокий уровень). Иными словами, в состоянии А выходные сигналы на соответствующих клеммах, клемме Q и клемме QB, находятся в не определенном состоянии. Если транзистор р16 открылся непосредственно перед тем, как SB-сигнал и RB-сигнал перешли из состояния А в состояние X, потенциал клеммы Q сразу же становится равным Vss + Vth (пороговое напряжение транзистора р16). Это вызывает отпирание транзистора р14, так что клемма QB получает напряжение Vdd (высокий уровень). Далее, поскольку транзистор n15, с которым соединена клемма QB, открыт, клемма Q получает напряжение Vss (низкий уровень). При этом если транзистор р16 запирается непосредственно перед тем, как SB-сигнал и RB-сигнал перешли из состояния А в состояние X, иными словами, если транзистор р16, составляющий схему LC защелки, заперт, а транзистор n15, составляющий инвертор, открыт клемма Q получает напряжение Vss (низкий уровень). Это вызывает отпирание транзистора р14, затвор которого соединен с клеммой Q. Соответственно, клемма QB получает напряжение Vdd (высокий уровень). Иными словами, клемма Q получает напряжение Vss (низкий уровень) и клемма QB получает напряжение Vdd (высокий уровень) в состоянии X, независимо от того, какова неопределенность состояния А. Далее, если в период времени, в котором INITB-сигнал имеет низкий уровень (активен), SB-сигнал и RB-сигнал изменились от состояния В, в котором SB-сигнал имеет низкий уровень (активен) и RB-сигнал имеет высокий уровень (неактивен), в состояние X, в котором оба сигнала, SB-сигнал и RB-сигнал, имеют высокий уровень (неактивен), клемма Q получает напряжение Vss (низкий уровень) и клемма QB получает напряжение Vdd (высокий уровень). Иными словами, в состоянии В выходные сигналы на соответствующих клеммах - клемме Q и клемме QB, находятся в неопределенном состоянии. Если транзистор р16 отпирается непосредственно перед тем, как SB-сигнал и RB-сигнал изменяются от состояния В к состоянию X, потенциал клеммы Q сразу же становится равным Vss + Vth (пороговое напряжение транзистора р16). Это вызывает отпирание транзистора р14, так что клемма QB получает напряжение Vdd (высокий уровень). Далее, транзистор n15, с которым соединена клемма QB, отпирается, так что клемма Q получает напряжение Vss (низкий уровень). Если транзистор р16 запирается непосредственно перед тем, как SB-сигнал и RB-сигнал изменяются от состояния В к состоянию X, иными словами, если транзистор р16, составляющий схему LC защелки, заперт, а транзистор n15, составляющий инвертор, открыт, клемма Q получает напряжение Vss (низкий уровень). Это вызывает отпирание транзистора р14, затвор которого соединен с клеммой Q. Соответственно, клемма QB получает напряжение Vdd (высокий уровень). Иными словами, клемма Q получает напряжение Vss (низкий уровень), а клемма QB получает напряжение Vdd (высокий уровень) в состоянии X, независимо от того, какова неопределенность состояния В.