Сдвиговый регистр - RU2116678C1

Код документа: RU2116678C1

Чертежи

Описание

Изобретение относится к сдвиговым регистрам, в частности к ступени сдвигового регистра, пригодной для использования в качестве сканнера шин выборки для жидкокристаллических дисплеев.

Жидкокристаллические телевизионные и компьютерные дисплеи (ЖКД) известны в данной области техники (см., например, патенты США N 4742346 и 4766430, выданные на имя G.G.Gillette и др.) Дисплеи, описанные в патентах Gillette, включают в себя матрицу жидкокристаллических ячеек, которые расположены на пересечениях шин данных и шин выборки. Шины выборки выбираются последовательно сканнером шин выборки для создания на дисплее горизонтальных строк. Когда шины выборки последовательно выбираются, шины данных выдают яркостные сигналы (в серой градации) на колонки жидкокристаллических ячеек.

Предпочтительно, чтобы управляющая схема, которая осуществляет управление сканнером, выбирающим горизонтальные строки, которые должны показываться на дисплее, изготавливалась непосредственно на одной и той же подложке и в одно и то же время с изготовлением жидкокристаллических ячеек. Кроме того, поскольку для телевизионного или компьютерного дисплея требуется большое число шин данных и шин выборки и поскольку малый шаг элементов изображения (пикселов) ограничивает пространство, оставшееся для размещения управляющей схемы, существенно сохранять схему насколько это возможно простой.

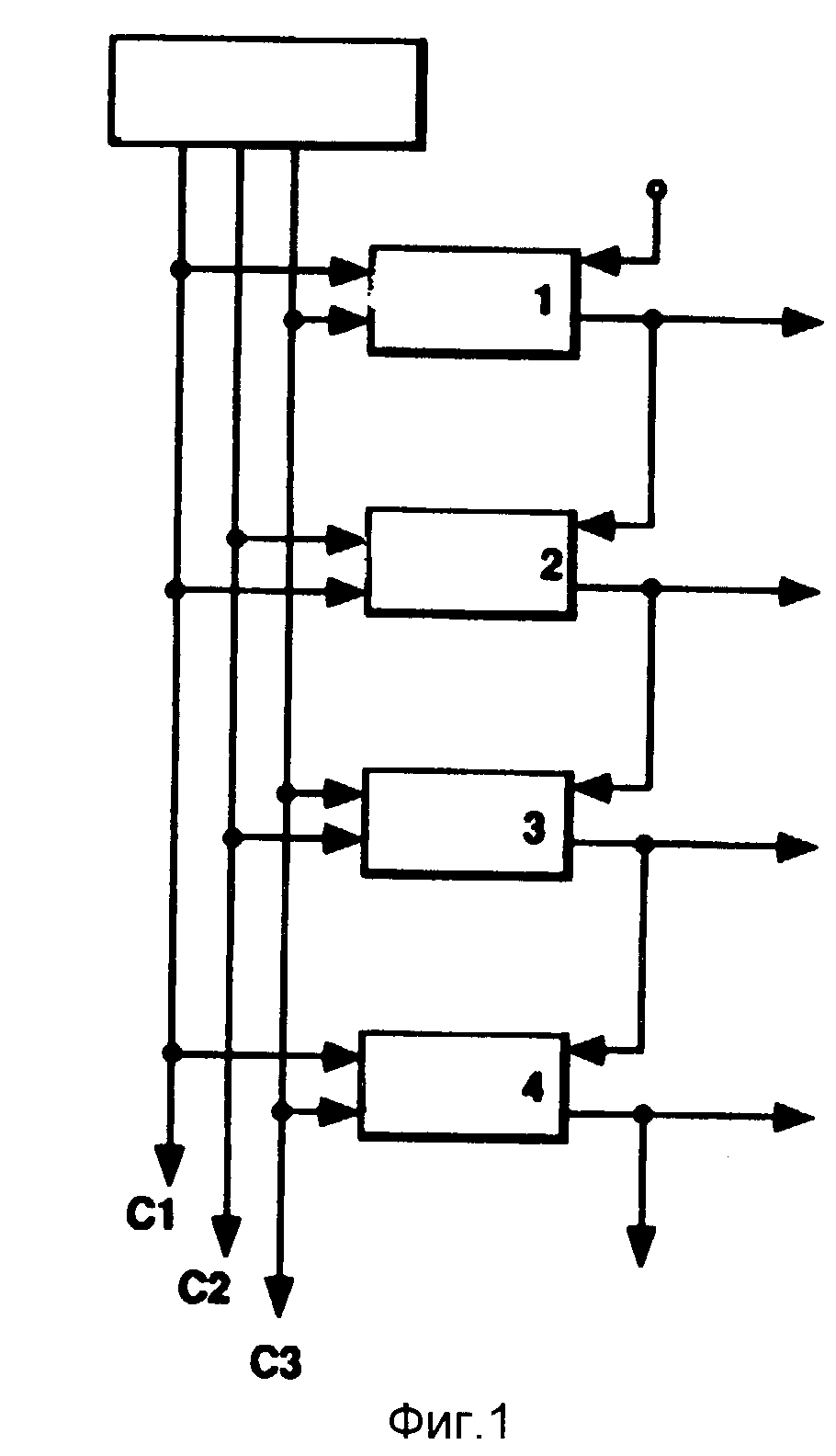

Фиг 1. иллюстрирует пример известного сканирующего регистра (регистра развертки), описанного в патенте США N 5222082, который может быть объединен с жидкокристаллическим дисплейным устройством. Регистр управляется многофазными синхронизирующими сигналами C1, C2, C3 при различных временных фазах, подаваемых на разные ступени 11 сканирующего регистра.

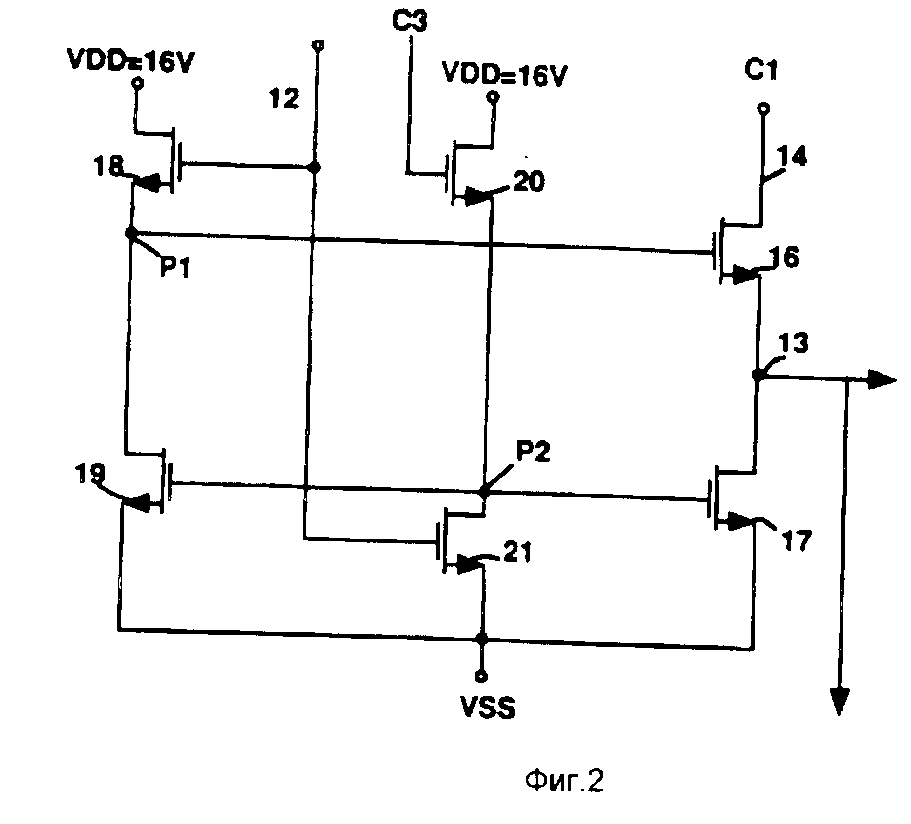

Фиг. 2 подробно иллюстрирует одну из ступеней сканирующего регистра. Ступень сканирующего регистра включает в себя входную секцию, содержащую транзисторы 18 и 19, промежуточную секцию, содержащую транзисторы 20 и 21, и выходную секцию, содержащую транзисторы 16 и 17.

Выходная секция выполнена в виде двухтактного (пушпульного) усилителя с синхронизируемым потенциалом питания, подключенным к ее выводу 14 питания. Выход выбирается на месте соединения транзисторов 16 и 17.

Выходная секция выполнена в виде коммутируемого усилителя для подачи заданного потенциала в течение фазы синхронизации, поданной на вывод питания выходной секции. Выходной сигнал P1 входной ступени подключен для управления выходным транзистором 16. В частности, выход P1 следует после входного сигнала, приложенного к электроду затвора транзистора 18. Выход входной секции будет высоким, когда фаза синхронизации, приложенная к выводу 14, становится высокой, и высокий уровень передается на выходной вывод 13. Когда входной сигнал низкий, высокий уровень в узле (узловой точке пересечения электрической схемы P1) сохраняется до появления фазы C3 синхронизации. Таким образом, затвор выходного транзистора 16 будет иметь высокий уровень, когда C1 синхронизации становится высоким, обеспечивая путь заряда к выходу 13, и когда C1 синхронизации становится низким, обеспечивая путь для разряда выходного узла 13.

Промежуточная секция выполнена в виде синхронизированного инвертирующего усилителя, чувствительного к входному сигналу. Выход промежуточной степени соединен с электродом затвора понижающего транзистора 17 выходной ступени. Промежуточная ступень включает в себя повышающий и понижающий транзисторы 20 и 21 соответственно. Проводимость транзистора 21 больше, чем транзистора 20, так, что, если оба транзистора 20 и 21 проводят совместно, выходной потенциал в узле P2 останется низким. Таким образом, если синхронизация, поданная на транзистор 20, имеет высокий уровень, когда входной сигнал имеет высокий уровень, выходной сигнал будет находиться в непроводящем состоянии. Однако, поскольку приложением ступени является регистр развертки, импульсы входного сигнала появляются относительно нечасто. В результате узел P2 будет нормально заряжен до высокого уровня для каждого импульса синхронизации фазы C3 синхронизации, и выходной транзистор 17 будет нормально проводящим.

Стоки транзисторов 18 и 20 принимают относительно положительное напряжение VDD смещения около 16 В. Таким образом, узел P2 будет иметь нормальное смещение около 16 В. Это создает чрезвычайную нагрузку на электроды затвора транзисторов 19 и 17, которая с течением времени стремится вызвать значительное повышение соответствующих пороговых напряжений. Когда порог транзистора 19 возрастает, его способность к разряду узла P1 уменьшается, и требуется большее время для выключения транзистора 16. В результате некоторое напряжение C1 синхронизации может шунтироваться на выходной узел 13 и нежелательно воздействовать на последующие ступени регистра, а также привести к ошибочной адресации рядов пикселов ЖКД.

Изобретение связано с этими проблемами и предлагает ступень сдвигового регистра, которая не только предотвращает ложные выходные значения, но также потребляет меньше энергии.

Изобретение представляет собой ступень сдвигового регистра для включения в каскадное соединение подобных ступеней и для запитывания сигналами многофазной синхронизации. Смежные ступени такого каскадного соединения запитываются разными комбинациями многофазных сигналов синхронизации. Каскад сдвигового регистра включает в себя входную схему и выходную ступень. Выходная ступень включает в себя усилитель, содержащий последовательно соединенные повышающий и понижающий транзисторы, каждый из которых имеет соответствующий управляющий электрод. Стык последовательно соединенных транзисторов является выходным выводом для каскада сдвигового регистра. Входная схема реагирует на импульс развертки, подаваемой на ее входной вывод для генерирования управляющего сигнала, который соединяется с управляющим электродом повышающего транзистора для управления состоянием выходной ступени в целях обеспечения выходных импульсов развертки. Главный проводящий путь фиксирующего транзистора образован между управляющим электродом повышающего транзистора и истоком с потенциалом, достаточным для выключения повышающего транзистора. Управляющий электрод фиксирующего транзистора соединен с выходным выводом последующей ступени указанного каскадного соединения или альтернативно - с источником синхросигналов, с фазой, отличной от фазы синхроимпульсов, запитывающих указанную выходную ступень.

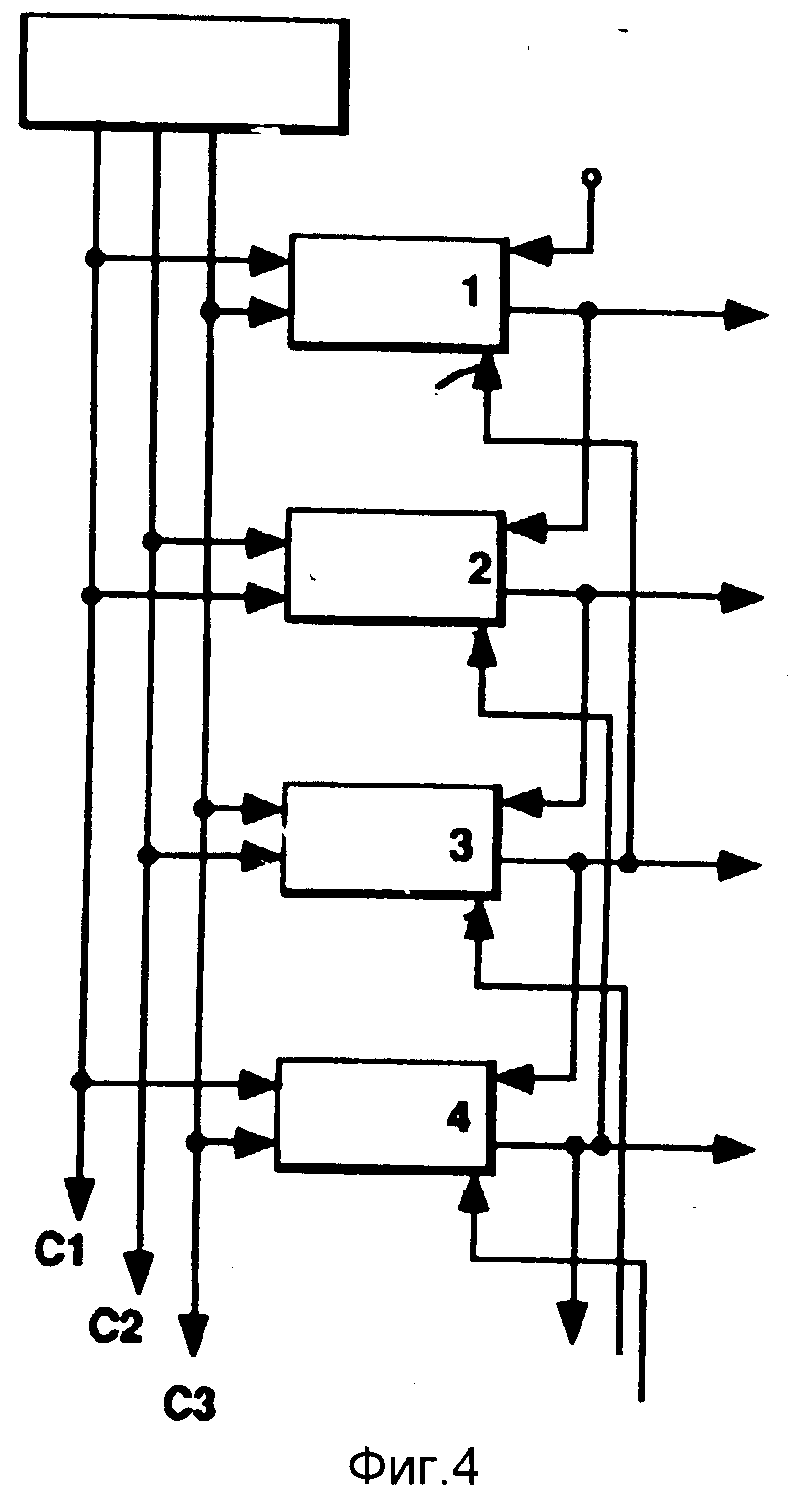

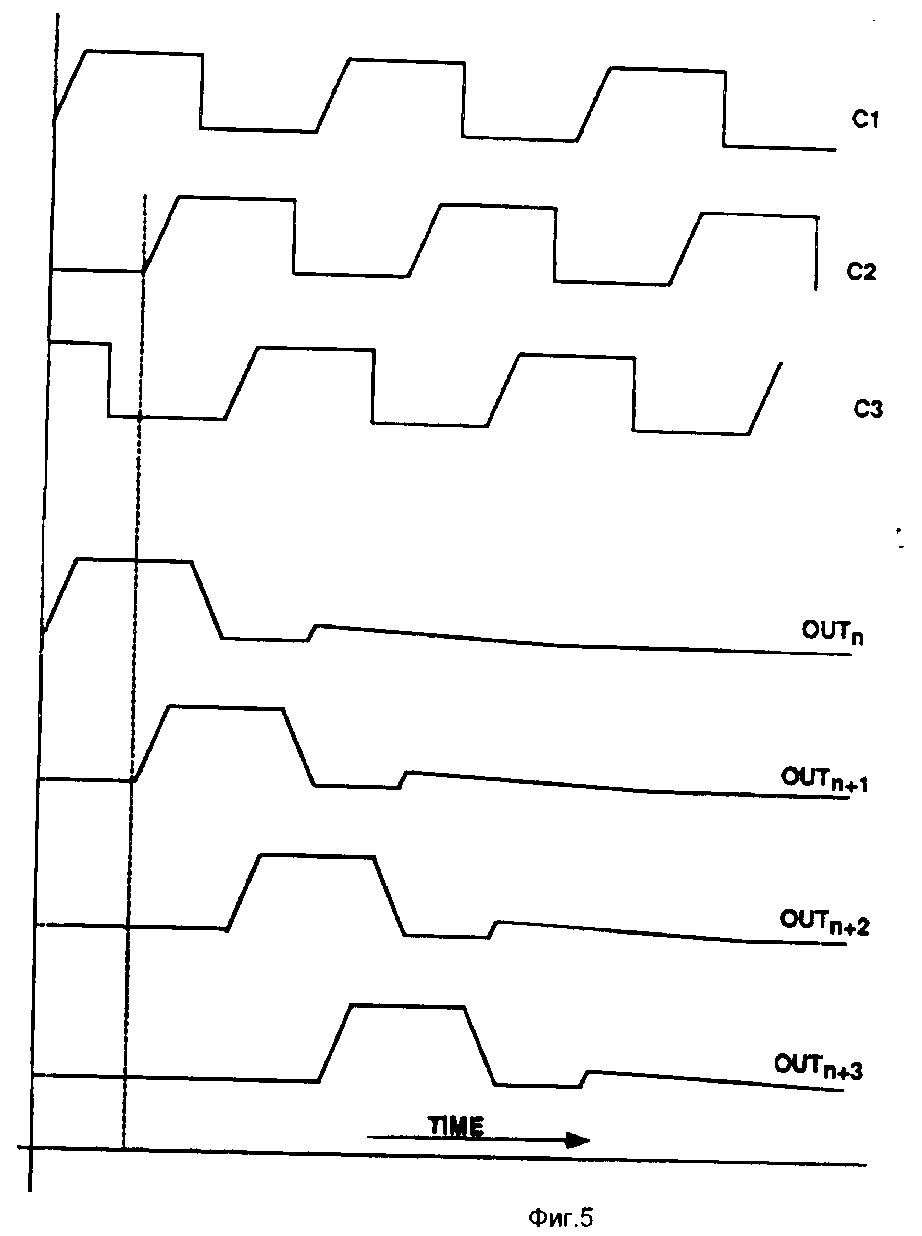

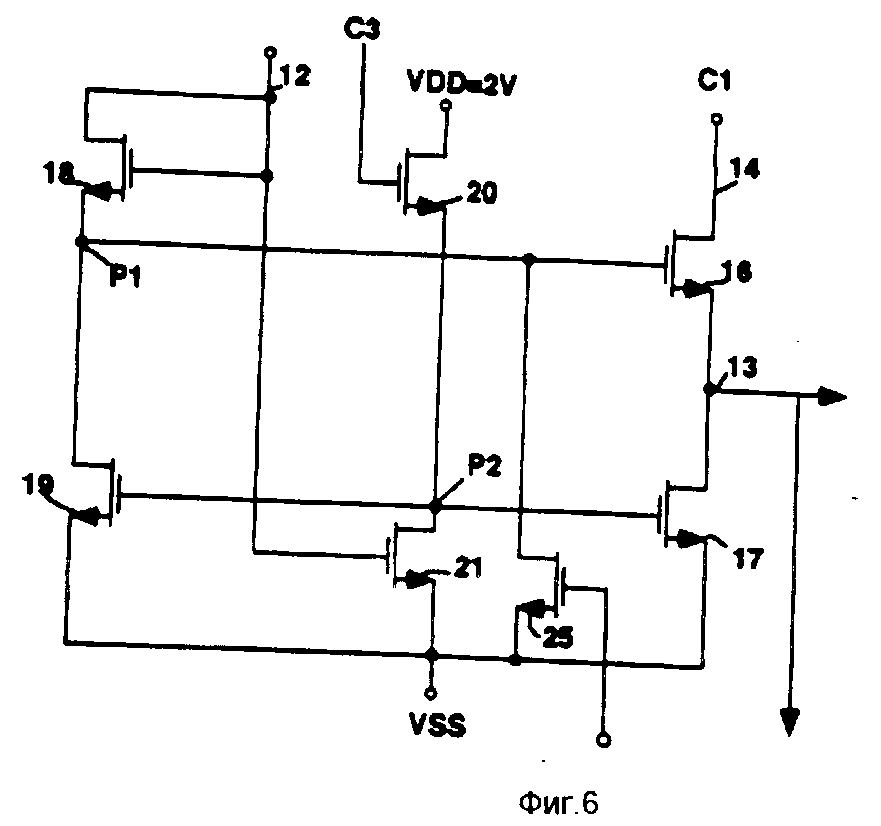

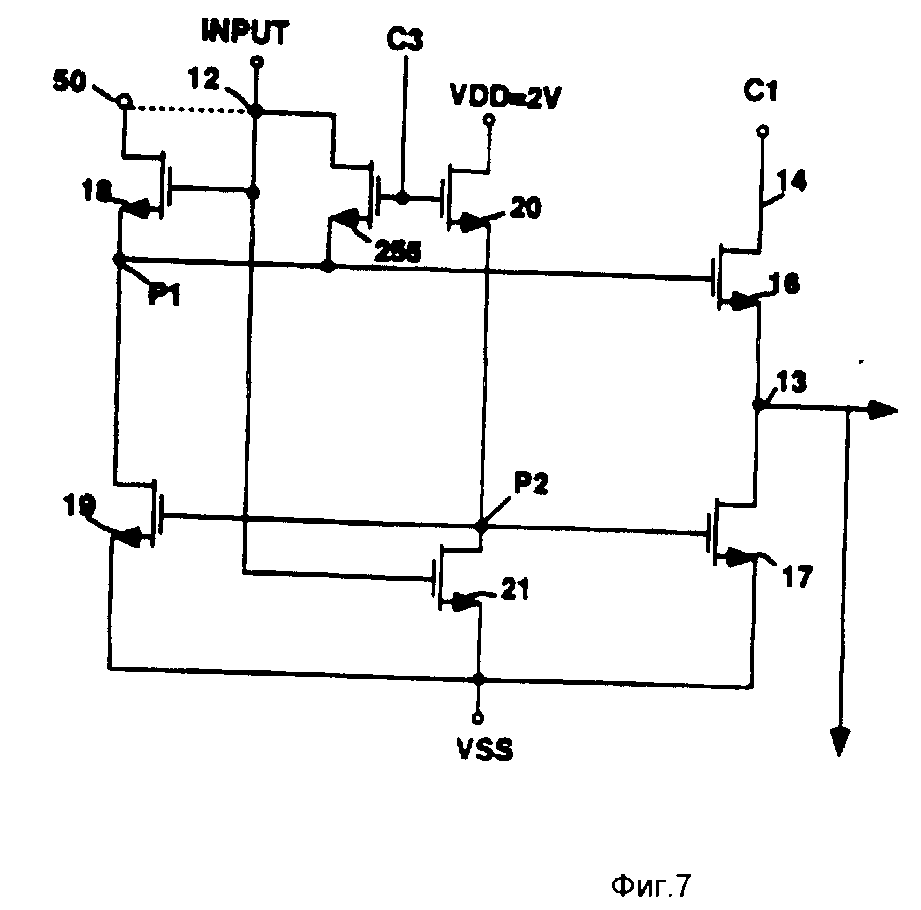

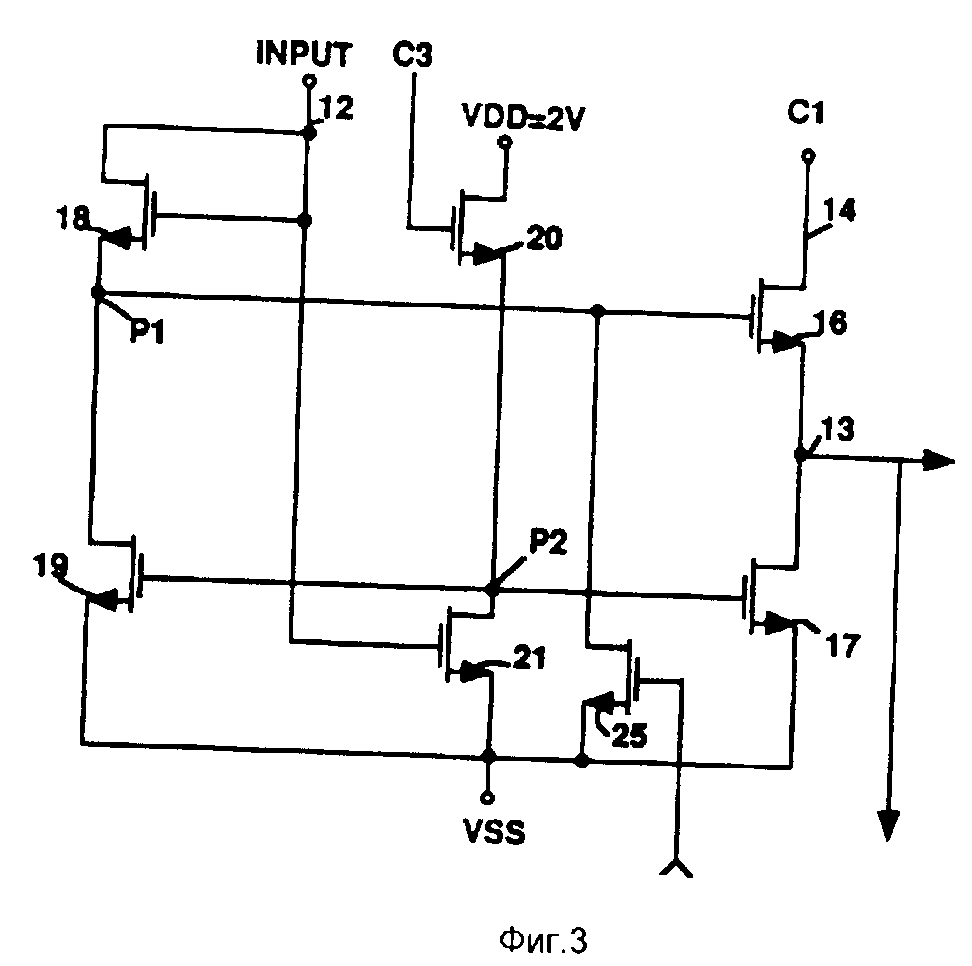

На фиг. 1 приведена блок-схема известного сдвигового регистра, включающего в себя множество каскадированных ступеней; на фиг. 2 - схема ступени известного сдвигового регистра, которая может использоваться в сдвиговом регистре по фиг. 1; на фиг. 3 - схема ступени сдвигового регистра, реализующего изобретение; на фиг. 4 - блок-схема сдвигового регистра, включающего в себя каскадное соединение нескольких ступеней, иллюстрируемых на фиг. 3; на фиг. 5 - временная диаграмма выходных сигналов и соответствующих сигналов синхронизации, появляющихся в соответствующих узлах сдвигового регистра по фиг. 4, использующего ступени, иллюстрируемые на фиг. 3; на фиг. 6 и 7 - схемы альтернативных ступеней сдвигового регистра, реализующих изобретение.

Фиг. 3 иллюстрирует ступень сдвигового регистра в соответствии с первым вариантом осуществления изобретения. Ступень подобна ступени на фиг. 2, но имеет несколько важных отличий. Во-первых, в улучшенную степень включен дополнительный транзистор 25. Проходящий путь сток-исток транзистора 25 подключен между узлом P1 и точкой опорного потенциала, достаточного для выключения повышающего транзистора 16. Затвор транзистора 25 соединен с выходным выводом последующей ступени. Если данная ступень имеет номер n в каскадном соединении ступеней с порядковой нумерацией, затвор транзистора 25 предпочтительно соединяют с выходом ступеней n + 2. Однако затвор транзистора 25 может быть соединен с другой ступенью, например ступенью n + 3, с полезным результатом. Транзистор 25 способствует понижению напряжения в узле P1, что позволяет транзистору 19 быть конструктивно меньше. Фактически понижение напряжения в узле P1 под управлением транзистора 25 может быть почти полным, так что функция транзистора 19 может состоять просто в поддержании низкого уровня в узле P1, когда напряжение в нем уже понизилось.

Транзистор 19, регулируемый для выполнения понижающей функции, может управляться низким напряжением затвора. Потенциал питания, приложенный к промежуточной ступени, следовательно, можно уменьшить, например, с 16 В в ступени регистра по фиг. 2 до примерно 2 В в ступени регистра по фиг. 3. Это уменьшение напряжения питания и последующее уменьшение напряжения затвора, приложенного к транзисторам 19 и 17, ведет к полезному уменьшению величины дрейфа порогового напряжения в транзисторах 19 и 17. В результате ступень становится более надежной и увеличивается срок ее эксплуатации.

Размеры транзистора 17 можно также уменьшить, поскольку с включением транзистора 25 можно быть уверенным, что а) узел P1 будет сохранять низкий уровень, предохраняющий транзистор 16 от параллельной работы в конкурирующем режиме с транзистором 17, и б) фактор безопасности надлежащей работы увеличивается благодаря стабилизации порогового напряжения транзистора 17. Заметим, что поскольку транзисторы 19 и 17 могут быть уменьшены в размерах, транзистор 25 можно включать без увеличения площади ступени (в интегральной форме).

Дополнительным изменением является устранение питания, подаваемого на стоковый электрод транзистора 18 на ступени фиг. 2. Питание заменяется соединением стокового электрода транзистора 18 с входным выводом. Поскольку транзистор 18 по существу не отбирает ток стока источника, это соединение незначительно нагружает выход предыдущей ступени каскада. Вдобавок к устранению питания это изменение имеет полезный эффект, приводящий к большей нечувствительности входной ступени к шуму на входе.

При взаимном соединении электродов затвора и стока транзистора 18 последний работает как диод. Таким образом, фактически транзистор 18 можно заменить диодом. Транзистор 18 в диодном соединении заряжает узел P1 до амплитуды входного импульса (минус пороговое значение), а транзисторы 25 и 19 впоследствии разряжают узел P1. Поскольку проводимость транзистора в диодном включении нелинейная, потенциал в узле P1 может быть повышен до более высоких значений, когда синхросигнал, приложенный к выводу питания выходного усилителя, становится высоким, т.е. емкости затвор-сток и затвор-исток повышающего транзистора 16 будут ответвлять существенную часть синхронизирующего напряжения на выводах 14 и 13 к узлу P1, тем самым увеличивая возможность управления транзистора 16.

Фиг. 4 иллюстрирует каскадное соединение множества ступеней типа, показанного на фиг. 3. В показанном устройстве последовательные ступени регистра управляются тремя различными фазами синхронизации C1, C2, C3. Выходной вывод каждой последовательной ступени регистра соединен с входным выводом последующей ступени регистра. Электрод затвора соответствующего транзистора 25 ступени n соединен с выходным выводом ступени n + 2. Следует повторить, однако, что электрод затвора соответствующего транзистора 25 можно соединить с выходными выводами других ступеней, т.е. электрод затвора транзистора 25 ступени n можно соединить с выходным выводом ступени n + 3 и т.д.

Фиг. 5 иллюстрирует формы сигналов по напряжению и во времени для соответствующих фаз синхронизации и выбранных выводов ступени регистра. Напомним, что выходной сигнал одной ступени является входной сигналом для следующей ступени, следовательно, нет необходимости показывать единичный входной сигнал. Иллюстрируемый сдвиговый регистр фиг. 4 показан с использованием 3-фазной синхронизации, следовательно, 3-фазная синхронизация включена в фиг. 5. Можно видеть, что после того, как каждый выходной вывод выдает импульс развертки, имеется небольшой выступ в выходном потенциале, только следующий непосредственно после импульса развертки. Это происходит, поскольку транзистор 19, сделанный меньшим, не полностью снижает потенциал узла P1, и часть фазы синхронизации, поданной на вывод питания выходной ступени, имеет утечку через транзистор 16. Когда транзистор 25 включен в проводящее состояние, узел P1 полностью переводится в низкий уровень, предотвращая дальнейшую утечку импульсов синхронизации через соответствующий транзистор 16. Заметим, что формы сигналов фиг. 5 генерируются для электродов затвора соответствующих транзисторов 25 соответствующих ступеней n, соединенных с выходными выводами соответствующих ступеней n + 3.

Выходные импульсы показаны перекрывающимися. Величина перекрытия является функцией величины, на которую перекрываются фазы синхронизации. Таким образом, желаемое перекрытие выходных импульсов регулируется для конкретного приложения путем регулировки перекрытия фаз синхронизации.

Фиг. 6 иллюстрирует альтернативную ступень сдвигового регистра, где управляющий электрод фиксирующего транзистора 25 подключен к фазам синхронизации, отличающимся от фазы, подключенной к стоковому электроду транзистора 16. В трехфазной неперекрывающейся системе синхронизации транзистор 25 может быть подключен к фазе синхронизации, не подключенный к транзисторам 20 и 16. В системе с более чем тремя фазами управляющий электрод транзистора 25 может быть подключен к одной из альтернативных фаз синхронизации из подключенных к транзисторам 20 и 16. Ограничение на фазу синхронизации, которая подключена к управляющему электроду фиксирующего транзистора 25 таково, что его импульсы приходят после фазы входного сигнального импульса и фазы синхронизации, подключенной к стоку транзистора 16. Подключение транзистора 25 к фазе синхронизации, а не к выходному соединению последующей ступени регистра дает конструктору схем альтернативы в размещении по отношению к топологии интегральных схем.

Фиг. 7 иллюстрирует дополнительную альтернативную ступень регистра. В этом варианте осуществления путь исток-сток фиксирующего транзистора 255 выполнен между узлом P1 и входным выводом 12, а его управляющий электрод подключен к фазе C3 синхронизации. Входной вывод 12 N-ступенчатого регистра находится под низким потенциалом (по существу VSS), по меньшей мере (N-1)/N-ную часть времени регистр управляем, следовательно, фиксирующий транзистор 255 при включении будет фиксировать узел P1 в состоянии низкого уровня для закрывания транзистора 16. На затвор транзистора 255 подаются импульсы каждый тактовый цикл, обеспечивая регулярную и частую фиксацию узла P1 в низком состоянии.

Рассмотрим многофазную систему синхронизации, где синхросигналы, поданные на транзисторы 21 и 20, имеют последовательные фазы: например, фазы C1 и C3, как показано на фиг. 5. Входной импульс на вывод 12 будет приходить одновременно с фазой C3 синхронизации. В этом примере на транзистор 255 подаются импульсы, когда входной сигнал на выводе 12 имеет высокий уровень. Транзистор 255 будет, следовательно, помогать в установлении высокого уровня в узле P1, позволяя тем самым транзистору 18 иметь меньшие размеры. В течение всего цикла синхронизации, когда входной импульс приложен к выводу 12, узел P1 будет в состоянии высокого уровня. Однако это не окажет воздействия на требуемую работу сдвигового регистра. Узел P1 будет зафиксирован в состоянии низкого уровня синхронизации C3 в течение следующего цикла синхронизации.

Стоковый электрод транзистора 18 может быть соединен или с источником постоянного потенциала питания, например VDD, или альтернативно, с входным выводом 12, как показано на фиг. 3.

Реферат

Изобретение относится к сдвиговым регистрам, включающим в себя множество каскадированных ступеней, каждая из которых имеет входной вывод и выходной вывод. Каждая ступень включает в себя синхронизированную выходную схему, содержащую последовательно соединенные повышающий и понижающий транзисторы. Дополнительный транзистор имеет проводящий путь, подключенный между управляющим электродом повышающего транзистора и точкой с потенциалом, достаточным для выключения повышающего транзистора. Управляющий электрод дополнительного транзистора подключен к выходу последующей из каскадированных ступеней или альтернативно - к источнику синхросигналов с фазой, отличающейся от фазы синхросигналов, поданных на указанную выходную схему, для гарантирования того, что выход соответствующей ступени не сможет дрейфовать к включенному состоянию. 4 с. и 14 з.п. ф-лы, 7 ил.

Формула

13. Регистр по п.10, отличающийся тем, что входная секция содержит первый и второй транзисторы, причем сток и затвор первого транзистора соединены с входом ступени, а его исток соединен со стоком второго транзистора и с управляющим выходом секции, затвор второго транзистора соединен с вторым управляющим выходом секции, исток второго транзистора подключен к отрицательному полюсу источника питания.

Комментарии