Устройство для коррекции порядка при нормализации чисел - RU2638724C1

Код документа: RU2638724C1

Чертежи

Описание

ОБЛАСТЬ ТЕХНИКИ

Изобретение относится к области вычислительной техники, в частности к устройствам обработки данных, и может быть использовано для построения средств автоматики и функциональных узлов систем управления, а также в устройствах обработки чисел с плавающей запятой при нормализации данных.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

При выполнении операций в арифметико-логических устройствах с числами с плавающей запятой результаты операций могут быть представлены в ненормализованном виде. Для сохранения данных в формате с плавающей запятой и для дальнейшей обработки проводится нормализация данных. Для нормализации чисел определяется количество старших нулевых (незначащих) разрядов в зависимости от знака числа, представленного в дополнительном или обратном коде. На величину нулевых разрядов проводится коррекция (декремент) порядка числа и осуществляется сдвиг данных перед записью значения в мантиссу числа.

В соответствии со стандартом IEEE754-2008 для операций с плавающей запятой установлены форматы одинарной (32-разрядные), двойной (64 разрядные) и учетверенной (128-разрядные) точности. Для выполнения постбинарных вычислений требуется увеличение разрядности мантиссы, вводится 256-разрядный формат (октоточность) (например, при выполнении операций умножения, возведения в степень). При этом разрядность результатов операций составляет более 200 разрядов.

Известно устройство для определения количества единиц (нулей) в двоичном числе (RU №2446442, МПК G06F 7/50, Н03K 21/00, заявлено 11.04.2011, опубликовано 27.03.2012, Бюл. №9), содержащее блок управляемой инверсии, состоящий из n-элементов «ИСКЛЮЧАЮЩЕЕ ИЛИ» (n - количество разрядов входного числа), элементы ИЛИ и модули, состоящие из элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента И, которые объединены в группы, состоящие из ярусов, и объединены в k-каскадов (k=]log2n[), так, что каждый i-й каскад содержит g(i) = n/2i групп (i = 1, …, k), каждая группа i-го каскада разделена на j ярусов (j = 1 ,…, i), при этом первый ярус каждой группы i-го каскада содержит i модулей, а каждый j-й ярус каждой группы i-го каскада (j = 2, …, i,) содержит (i-j) модулей и элемент «ИЛИ».

Недостатком данного устройства является определение количества единиц (нулей) в двоичном числе, а не старших единиц (нулей).

К причинам, препятствующим достижению указанного ниже технического результата, относится отсутствие средств для формирования кода числа старших единиц (нулей) в двоичном числе.

Известно устройство для определения количества единиц в упорядоченном двоичном числе (RU №2522875, МПК Н03K 21/12, заявлено 24.05.2012, опубликовано 20.07.2014, Бюл. №20), содержащее буферы с тремя состояниями с прямым и инверсным входами разрешения, n разрядов входного двоичного числа, (k + 1) разрядов выходного двоичного кода (k=[log2n] меньшее целое), причем буферы с тремя состояниями объединены в пирамидальную структуру, состоящую из (m-1) ступеней (m=]log2n[ большее целое), и в выходной блок, содержащий к буферов с тремя состояниями с инверсным входом разрешения и к буферов с тремя состояниями с прямым входом разрешения, при этом каждая i-я ступень (i = 1,…, (m-1)) содержит 2i-1 буферов с тремя состояниями с инверсным входом разрешения и 2i-1 буферов с тремя состояниями с прямым входом разрешения.

Недостатком данного устройства является определение количества единиц в упорядоченном двоичном числе, а не старших единиц (нулей) в произвольном двоичном числе со знаком.

К причинам, препятствующим достижению указанного ниже технического результата, относится отсутствие средств для формирования кода числа старших единиц (нулей) в двоичном числе.

Известны способ и устройство для определения количества старших нулей (Optimized method and apparatus for parallel leading zero/one detection US 6697828 B1, МПК G06F 7/00, G06F 7/74, заявлено 01.06.2000, опубликовано 24.02.2004), в котором 32-разрядные входные данные разбиваются на четырехразрядные полубайты для которых параллельно вычисляется количество нулевых разрядов. Устройство содержит анализаторы полубайтов, которые вычисляют трехразрядный двоичный код для каждого полубайта, пирамидальную структуру двухвходовых мультиплексоров, содержащую три каскада, и группу элементов И для формирования сигналов управления входами выборки мультиплексорами.

Недостатками данного устройства являются большие аппаратные затраты и низкое быстродействие, так как при увеличении разрядности входных данных увеличивается количество последовательно включенных каскадов мультиплексоров, а также отсутствие средств для определения старших нулей в зависимости от знака числа.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятое за прототип, устройство для подсчета количества незначащих нулей (Redundancy-free circuits for zero counters US 8180815 B2, МПК G06F 15/00, G06F 3/00, G06F 7/74, заявлено 12.08.2008, опубликовано 15.05.2012), в котором генерируется трехразрядный код соответствующий количеству старших незначащих нулей для четырехразрядных полубайтов входных данных. Устройство реализовано как 16-битовый двоичный счетчик, состоящий из четырех 4-х битовых декодеров преобразования в трехразрядный код, выходы двух младших бит которых объединены на четырех двухразрядных мультиплексорах, пятый 4-х битовый декодер преобразует в двухразрядный код, соответствующий номеру полубайта, старшие разряды соответствующие сгенерированным трехразрядным кодам, когда все входные биты входных полубайт равны нулю, а также содержит выходной блок, который состоит из четырех элементов 2И-2ИЛИ, для объединения с выходами младшего 16-битового двоичного счетчика нулей.

Недостатками данного устройства являются большие аппаратные затраты и низкое быстродействие, так как для управления мультиплексорами и для формирования номера полубайтов применяются отдельные схемы, при увеличении разрядности входных данных увеличивается количество последовательно включенных каскадов выходных блоков, а также отсутствие средств для определения старших нулей в зависимости от знака числа.

ЗАДАЧА ИЗОБРЕТЕНИЯ

Задачей изобретения является разработка устройства для определения старших нулей в многоразрядных входных данных со знаком, заданных в дополнительном или обратном коде.

Техническим результатом изобретения является уменьшение аппаратных затрат, увеличение быстродействия устройства, расширение функциональных возможностей в части возможности определения старших нулевых разрядов для двоичных чисел со знаком, а также упрощение увеличения разрядности входных данных.

КРАТКОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Указанный технический результат при осуществлении изобретения достигается тем, что в устройство для коррекции порядка при нормализации чисел содержащее

вход знака Sign и N разрядов D1, D2, …, DN входного двоичного числа (D1 - старший разряд, DN - младший разряд), N разрядов X1, Х2, …, XN внутренней шины, (K + 1) разрядов В0, В1, …, BK выходного двоичного кода (K=[log2N] меньшее целое, В0 - младший разряд, ВК - старший разряд), (М + 1) каскадов блоков пирамидальной структуры (М=]log4(N/16)[ (большее целое)), при этом каждый i-й каскад (i = 1, …, (М+1)) содержит ]N/16/4(i-1)[ блоков, выходной блок 4, состоящий из (К-2) элементов ИЛИ, входной блок 5 управляемой инверсии, состоящий из N-элементов «ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ», группу из L элементов И 61, 62, …, 6L (L количество блоков 1-го каскада, где L=]N/16[ (большее целое)),

при этом в 1-ом каскаде каждый блок содержит

преобразователь в двухразрядный двоичный код 7, состоящий из четырех групп, каждая из которых содержит первый элемент 2И с инверсным входом, второй элемент 2И, элемент 2ИЛИ и третий элемент 2И,

двухразрядный коммутатор 8, состоящий из двух элементов 2И-2И-2И-2И-4ИЛИ, модуль проверки полубайтов 9, состоящий из четырех элементов 4И, первый модуль указателя младшего нуля 10, состоящий из четырех элементов И с одним инверсным входом и пятого элемента 4И,

двухразрядный двоичный шифратор 11, состоящий из двух элементов 2ИЛИ, при этом каждый блок второго, третьего, …, (М+1)-го каскадов содержит второй модуль указателя младшего нуля 12, состоящий из трех элементов И с одним инверсным входом и четвертый элемент 4И, и двухразрядный двоичный шифратор 11, состоящий из двух элементов 2ИЛИ,

причем N разрядов D1, D2, …, DN входного двоичного числа соединены с первыми входами соответствующих одноименных элементов «ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ» входного блока 5, вторые входы которых подключены к входу знака Sign двоичного числа, а выходы элементов входного блока 5 являются соответствующими N разрядами X1, Х2, …, XN внутренней шины (при этом X1 - младший разряд, XN - старший разряд),

входами каждого j-го блока 1-го каскада (j = 1, 2, …, L) являются 16 разрядов внутренней шины X, с (1+16(j-l))-го по (16+16(j-1))-й разряды, разделенные на четыре группы полубайт по четыре разряда каждая, причем все полубайты шины X нумеруются, начиная с младших разрядов,

в каждом j-м блоке 1-го каскада в каждой группе преобразователя 7 младший первый разряд входа соответствующего полубайта соединен с первым входом первого элемента 2И с инверсным входом, первым входом второго элемента 2И и первым входом третьего элемента 2И, второй разряд входа полубайта соединен со вторым инверсным входом первого элемента 2И и вторым входом третьего элемента 2И, а третий разряд входа полубайта соединен со вторым входом второго элемента 2И, при этом выходы первого элемента 2И с инверсным входом и второго элемента 2И соединены с входами элемента 2ИЛИ, выход g0 которого является первым выходом каждой группы преобразователя 7, а выход g1 третьего элемента 2И является вторым выходом каждой группы преобразователя 7,

а также в каждом j-м блоке 1-го каскада четыре разряда входа каждого полубайта соединены с четырьмя входами соответствующего элемента 4И модуля проверки полубайтов 9, причем выход g2_0 первого элемента 4И модуля проверки полубайтов 9 соединен со вторым инверсным входом первого элемента И, вторыми входами второго, третьего и четвертого элементов И и первым входом пятого элемента И первого модуля указателя младшего нуля 10, выход g2_1 второго элемента 4И модуля проверки полубайтов 9 соединен с третьим инверсным входом второго элемента И, третьими входами третьего и четвертого элементов И и вторым входом пятого элемента И первого модуля указателя младшего нуля 10, выход g2_2 третьего элемента 4И модуля проверки полубайтов 9 соединен с четвертым инверсным входом третьего элемента И, четвертым входом четвертого элементов И и третьим входом пятого элемента И первого модуля указателя младшего нуля 10, выход g2_3 четвертого элемента 4И модуля проверки полубайтов 9 соединен с пятым инверсным входом четвертого элемента И и четвертым входом пятого элементов И первого модуля указателя младшего нуля 10, причем первые входы первого, второго, третьего и четвертого элементов И первого модуля указателя младшего нуля 10 соединены с входом переноса блока CI «все единицы» j-го блока, а выход пятого элемента И первого модуля указателя младшего нуля 10 является выходом переноса блока СО «все единицы» j-го блока,

в каждом j-м блоке 1-го каскада первые выходы g0 каждой группы преобразователя в двухразрядный двоичный код 7 соединены с соответствующими первыми входами элементов 2И первого элемента 2И-2И-2И-2И-4ИЛИ, а вторые выходы g1 каждой группы преобразователя в двухразрядный двоичный код 7 соединены с соответствующими первыми входами элементов 2И второго элемента 2И-2И-2И-2И-4ИЛИ, при этом вторые входы соответствующих одноименных элементов 2И первого и второго элементов 2И-2И-2И-2И-4ИЛИ соединены между собой и подключены к соответствующим выходам u_0, u_1, u_2, u_3 с первого по четвертый элементы И с инверсным входом первого модуля указателя младшего нуля 10, а также выходы второго u_1 и третьего u_2 элементов И с инверсным входом модуля указателя младшего нуля 10, соединены с первыми входами соответственно первого и второго элементов ИЛИ двухразрядного двоичного шифратора 11, вторые входы которых соединены с выходом u_3 четвертого элемента И с инверсным входом модуля указателя младшего нуля 10,

выходы первого b0 и второго b1 элементов 2И-2И-2И-2И-4ИЛИ двухразрядного коммутатора 8 и выходы первого b2 и второго b3 элементов ИЛИ двухразрядного двоичного шифратора 11 являются соответственно первым, вторым, третьим и четвертым выходами каждого j-го блока 1-го каскада,

в группе из L элементов И 61, 62, …, 6L первые входы j-го элемента И 6j (j = 1, 2, …, L) соединены с выходом переноса СО «все единицы» j-го блока, а выходы элементов И, начиная с первого 61 до предпоследнего 6L-1 элементов, соединены с соответствующими входами переноса CI «все единицы» блоков, начиная со второго l2 до последнего 1L блока, вторые входы (1+4*Z)-го, (2+4*Z)-го, (3+4*Z)-го и (4+4*Z)-го элементов из группы из L элементов И 61, 62,…, 6L (Z = 0, 1, …, (L/4-1)) подключены к входу переноса CI «все единицы» (1+4*Z)-го блока, третьи входы (2+4*Z)-го, (3+4*Z)-го и (4+4*Z)-го элементов И подключены к выходу переноса СО «все единицы» (1+4*Z)-го блока, четвертые входы (3+4*Z)-го и (4+4*Z)-го элементов И подключены к выходу переноса СО «все единицы» (2+4*Z)-го блока, пятый вход (4+4*Z)-го элемента И подключен к входу переноса CI «все единицы» (3+4*Z)-го блока, кроме того, вход переноса CI «все единицы» первого блока l1 соединен с логической единицей,

в каждом v-ом блоке i-го каскада, начиная со второго каскада 2 до (М + 1)-го каскада (i=2, …, (М + 1), v = 1, …, N/16/4(i-1)), выход переноса СО «все единицы» (1+4(v-1)) блока (i-1)-го каскада соединен с первыми входами первого, второго и третьего элементов И с инверсным входом и первым входом четвертого элемента И второго указателя младшего нуля 12, выход переноса СО «все единицы» (2+4(v-1)) блока (i-1)-го каскада соединен со вторым инверсным входом первого элемента И с инверсным входом и вторыми входами второго и третьего элементов И с инверсным входом и вторым входом четвертого элемента И второго указателя младшего нуля 12, выход переноса СО ««все единицы» (3+4(v-1)) блока (i-1)-го каскада соединен с третьим инверсным входом второго элемента И с инверсным входом, третьим входом третьего элемента И с инверсным входом и третьим входом четвертого элемента И второго указателя младшего нуля 12, выход переноса СО «все единицы» (4+4(v-1)) блока (i-1)-го каскада соединен со четвертым инверсным входом третьего элемента И с инверсным входом и четвертым входом четвертого элемента И второго указателя младшего нуля 12, а также выходы первого и второго элементов И с инверсным входом второго указателя младшего нуля 12 соединены с первыми входами соответственно первого и второго элементов ИЛИ двухразрядного двоичного шифратора 11, вторые входы которых соединены с выходом третьего элемента И с инверсным входом второго указателя младшего нуля 12, при этом выход четвертого элемента И второго модуля указателя младшего нуля 12 является выходом переноса СО «все единицы» каждого v-го блока, а выходы первого и второго элементов ИЛИ двухразрядного двоичного шифратора 11 являются соответственно первым и вторым, выходами каждого v-го блока,

первый b0, второй b1, третий b2 и четвертый b3 выходы всех L блоков первого каскада 1 соединены с соответствующими входами одноименных элементов ИЛИ выходного блока 4, первый и второй выходы всех блоков в i-м каскаде (i=2, …, М) соединены с соответствующими входами соответственно (2i + 1)-го и (2i + 2)-го элементов ИЛИ выходного блока 4,

выходы (К-2) элементов ИЛИ выходного блока 4, первый и второй выходы блока последнего (М + 1)-го каскада и выход последнего элемента 6L из группы из L элементов И являются соответственно (K + 1) разрядами В0, В1, …, BK выходного двоичного кода.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

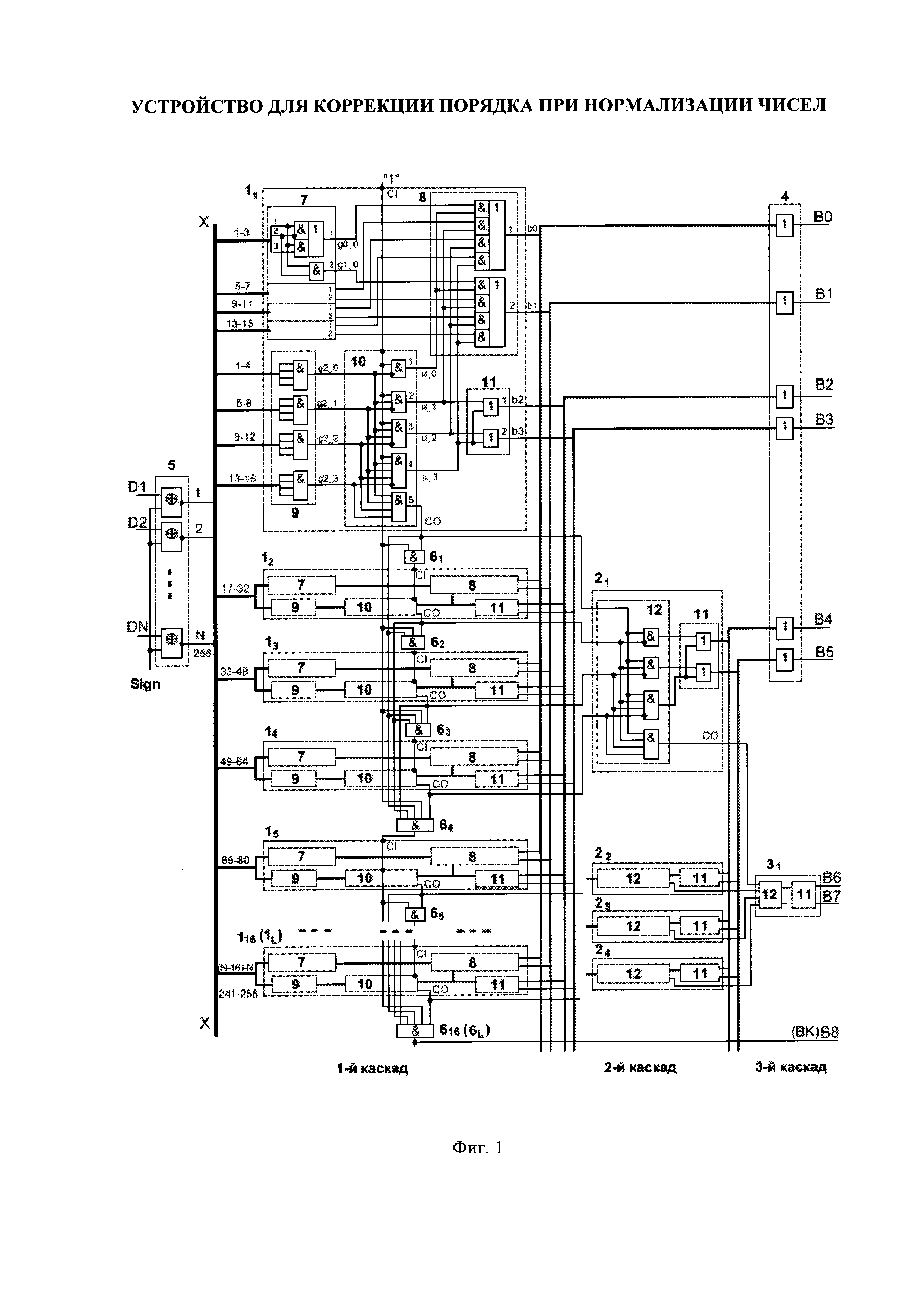

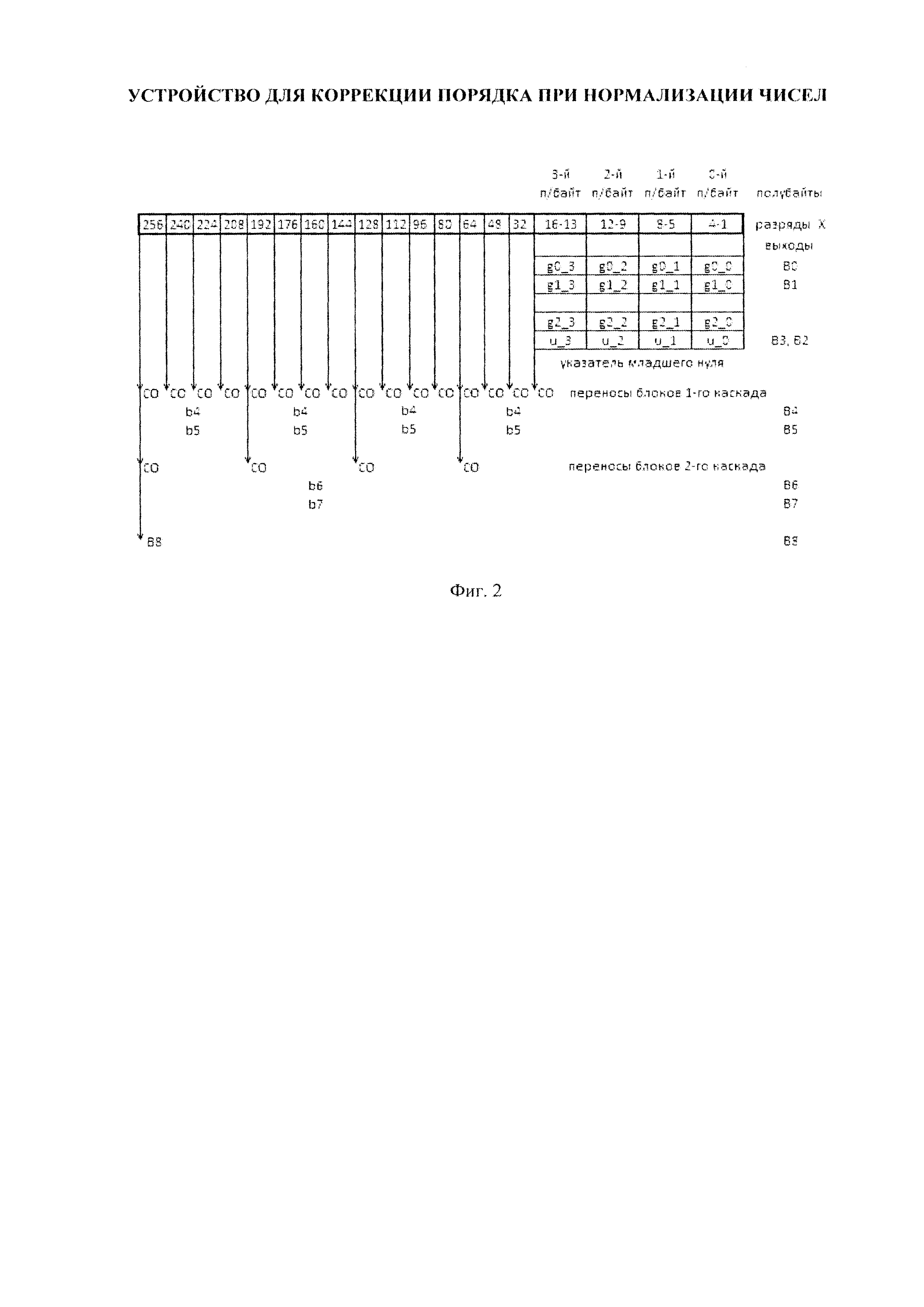

На фиг. 1 представлена схема предлагаемого устройства для коррекции порядка при нормализации чисел при N=256. На фиг. 2 представлены формат данных шины X и схема формирования значений разрядов выходного кода В при N=256.

На фиг. 1 приняты следующие обозначения:

D1, D2, …, D256 (DN) - N разрядов входного двоичного числа (при N=256),

Sign - знак входного числа,

X1, Х2, …, Х256 (XN) - N разрядов внутренней шины,

В0, В1, …, В8 (BK + 1) - (K + 1) разрядов выходного двоичного кода (при К=8) (K=[log2N] меньшее целое),

CI - вход переноса блока «все единицы»,

СО - выход переноса блока «все единицы»,

L - количество блоков 1-го каскада, где L=]N/16[ (большее целое), L=16 при N=256,

(М + 1) - количество каскадов (М=]log4(N/16)[ (большее целое)), (М + 1) = 3 при N=256),

g2, g1, g0 - трехразрядный двоичный код соответствующий количеству единиц в полубайте (g0 - младший разряд),

u_3, u_2, u_1, u_0 - выходы модуля указателя младшего нуля в унитарном коде,

b1, b0 - младшие разряды количества единиц в полубайте,

b3, b2 - разряды номера полубайта внутри каждого блока первого каскада,

b5, b4 - разряды указывающие номер блока 1 в группах из четырех блоков 1 первого каскада,

l1, l2, …, l16(L) - блоки первого каскада,

21, 22, 23, 24 - блоки второго каскада,

31 - блок третьего каскада,

4 - выходной блок содержащий (К-2) элементов ИЛИ,

5 - входной блок управляемой инверсии, состоящий из N-элементов

«ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ» (XNOR),

61, 62,…, 616(L) - группа из L элементов И,

7 - преобразователь в двухразрядный двоичный код, содержащий четыре группы,

каждая из которых состоит из первого элемента 2И с инверсным входом,

второго элемента 2И, элемента 2ИЛИ и третьего элемента 2И,

8 - двухразрядный коммутатор, состоящий из двух элементов 2И-2И-2И-2И-4ИЛИ,

9 - модуль проверки полубайтов, содержащий четыре элемента 4И,

10 - первый модуль указателя младшего нуля, содержащий четыре элемента И с

одним инверсным входом и пятый элемент 4И,

11 - двухразрядный двоичный шифратор, содержащий два элемента 2ИЛИ,

12 - второй модуль указателя младшего нуля, содержащий три элемента И с одним

инверсным входом и четвертый элемент 4И.

Предлагаемое устройство содержит вход знака Sign и N разрядов D1, D2, …, DN входного двоичного числа (D1 - старший разряд, DN - младший разряд), N разрядов X1, Х2, …, XN внутренней шины, (K + 1) разрядов В0, В1, …, BK выходного двоичного кода (K=[log2N] меньшее целое, В0 - младший разряд, ВК - старший разряд), (М + 1) каскадов блоков пирамидальной структуры (М=]log4(N/16)[ (большее целое)), при этом каждый i-й каскад (i=1, …, (М+1)) содержит ]N/16/4(i-1)[ блоков, выходной блок 4, состоящий из (К-2) элементов ИЛИ, входной блок 5 управляемой инверсии, состоящий из N-элементов «ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ», группу из L элементов И 61, 62, …, 6L (L количество блоков 1-го каскада, где L=]N/16[ (большее целое)).

При этом в 1-ом каскаде каждый блок содержит преобразователь в двухразрядный двоичный код 7, состоящий из четырех групп, каждая из которых содержит первый элемент 2И с инверсным входом, второй элемент 2И, элемент 2ИЛИ и третий элемент 2И, двухразрядный коммутатор 8, состоящий из двух элементов 2И-2И-2И-2И-4ИЛИ, модуль проверки полубайтов 9, состоящий из четырех элементов 4И, первый модуль указателя младшего нуля 10, состоящий из четырех элементов И с одним инверсным входом и пятого элемента 4И, двухразрядный двоичный шифратор 11, состоящий из двух элементов 2ИЛИ.

При этом каждый блок второго, третьего, (М + 1)-го каскадов содержит второй модуль указателя младшего нуля 12, состоящий из трех элементов И с одним инверсным входом и четвертый элемент 4И, и двухразрядный двоичный шифратор 11, состоящий из двух элементов 2ИЛИ.

Причем N разрядов D1, D2, …, DN входного двоичного числа соединены с первыми входами соответствующих одноименных элементов «ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ» входного блока 5, вторые входы которых подключены к входу знака Sign двоичного числа, а выходы элементов входного блока 5 являются соответствующими N разрядами X1, Х2, …, XN внутренней шины (при этом X1 - младший разряд, XN - старший разряд).

Входами каждого j-го блока 1-го каскада (j=1, 2, …, L) являются 16 разрядов внутренней шины X, с (1+16(j-1))-го по (16+16(j-1))-й разряды, разделенные на четыре группы полубайт по четыре разряда каждая, причем все полубайты шины X нумеруются, начиная с младших разрядов.

В каждом j-м блоке 1-го каскада в каждой группе преобразователя 7 младший первый разряд входа соответствующего полубайта соединен с первым входом первого элемента 2И с инверсным входом, первым входом второго элемента 2И и первым входом третьего элемента 2И, второй разряд входа полубайта соединен со вторым инверсным входом первого элемента 2И и вторым входом третьего элемента 2И, а третий разряд входа полубайта соединен со вторым входом второго элемента 2И, при этом выходы первого элемента 2И с инверсным входом и второго элемента 2И соединены с входами элемента 2ИЛИ, выход g0 которого является первым выходом каждой группы преобразователя 7 соответствующим нечетному количеству единиц в полубайте, а выход g1 третьего элемента 2И является вторым выходом каждой группы преобразователя 7 соответствующим двум старшим единицам в полубайте.

Также в каждом j-м блоке 1-го каскада четыре разряда входа каждого полубайта соединены с четырьмя входами соответствующего элемента 4И модуля проверки полубайтов 9, при этом выход g2_0 первого элемента 4И соответствует значению четырех единиц в нулевом полубайте, выход g2_l второго элемента 4И - в первом полубайте, выход g2_2 третьего элемента 4И - во втором полубайте, а выход g2_3 четвертого элемента 4И - в третьем полубайте. Причем выход g2_0 первого элемента 4И модуля проверки полубайтов 9 соединен со вторым инверсным входом первого элемента И, вторыми входами второго, третьего и четвертого элементов И и первым входом пятого элемента И первого модуля указателя младшего нуля 10, выход g2_1 второго элемента 4И модуля проверки полубайтов 9 соединен с третьим инверсным входом второго элемента И, третьими входами третьего и четвертого элементов И и вторым входом пятого элемента И первого модуля указателя младшего нуля 10, выход g2_2 третьего элемента 4И модуля проверки полубайтов 9 соединен с четвертым инверсным входом третьего элемента И, четвертым входом четвертого элементов И и третьим входом пятого элемента И первого модуля указателя младшего нуля 10, выход g2_3 четвертого элемента 4И модуля проверки полубайтов 9 соединен с пятым инверсным входом четвертого элемента И и четвертым входом пятого элементов И первого модуля указателя младшего нуля 10. Причем первые входы первого, второго, третьего и четвертого элементов И первого модуля указателя младшего нуля 10 соединены с входом переноса блока CI «все единицы» j-го блока, а выход пятого элемента И первого модуля указателя младшего нуля 10 является выходом переноса блока СО «все единицы» j-го блока.

В каждом j-м блоке 1-го каскада первые выходы g0 каждой группы преобразователя в двухразрядный двоичный код 7 соединены с соответствующими первыми входами элементов 2И первого элемента 2И-2И-2И-2И-4ИЛИ, а вторые выходы g1 каждой группы преобразователя в двухразрядный двоичный код 7 соединены с соответствующими первыми входами элементов 2И второго элемента 2И-2И-2И-2И-4ИЛИ. При этом вторые входы соответствующих одноименных элементов 2И первого и второго элементов 2И-2И-2И-2И-4ИЛИ соединены между собой и подключены к соответствующим выходам u_0, u_1, u_2, u_3 с первого по четвертый элементы И с инверсным входом первого модуля указателя младшего нуля 10, а также выходы второго u_1 и третьего u_2 элементов И с инверсным входом модуля указателя младшего нуля 10, соединены с первыми входами соответственно первого и второго элементов ИЛИ двухразрядного двоичного шифратора 11, вторые входы которых соединены с выходом u_3 четвертого элемента И с инверсным входом модуля указателя младшего нуля 10.

Выходы первого b0 и второго b1 элементов 2И-2И-2И-2И-4ИЛИ двухразрядного коммутатора 8 и выходы первого b2 и второго b3 элементов ИЛИ двухразрядного двоичного шифратора 11 являются соответственно первым, вторым, третьим и четвертым выходами каждого j-го блока 1-го каскада.

В группе из L элементов И 61, 62, …, 6L первые входы j-го элемента И 6j (j = 1, 2, …, L) соединены с выходом переноса СО «все единицы» j-го блока, а выходы элементов И, начиная с первого 61 до предпоследнего 6L-1 элементов, соединены с соответствующими входами переноса CI «все единицы» блоков, начиная со второго l2 до последнего lL блока, вторые входы (1+4*Z)-го, (2+4*Z)-го, (3+4*Z)-го и (4+4*Z)-го элементов из группы из L элементов И 61, 62, …, 6L (Z = 0, 1, …, (L/4-1)) подключены к входу переноса CI «все единицы» (1+4*Z)-го блока, третьи входы (2+4*Z)-го, (3+4*Z)-го и (4+4*Z)-го элементов И подключены к выходу переноса СО «все единицы» (1+4*Z)-го блока, четвертые входы (3+4*Z)-го и (4+4*Z)-го элементов И подключены к выходу переноса СО «все единицы» (2+4*Z)-го блока, пятый вход (4+4*Z)-го элемента И подключен к входу переноса CI «все единицы» (3+4*Z)-го блока, кроме того, вход переноса CI «все единицы» первого блока l1 соединен с логической единицей.

В каждом v-м блоке i-го каскада, начиная со второго каскада 2 до (М + 1)-го каскада (i=2, …, (М + 1), v=1, …, N/16/4(i-1)), выход переноса СО «все единицы» (1+4(v-1)) блока (i-1)-го каскада соединен с первыми входами первого, второго и третьего элементов И с инверсным входом и первым входом четвертого элемента И второго указателя младшего нуля 12. Выход переноса СО «все единицы» (2+4(v-1)) блока (i-1)-го каскада соединен со вторым инверсным входом первого элемента И с инверсным входом и вторыми входами второго и третьего элементов И с инверсным входом и вторым входом четвертого элемента И второго указателя младшего нуля 12. Выход переноса СО ««все единицы» (3+4(v-1)) блока (i-1)-го каскада соединен с третьим инверсным входом второго элемента И с инверсным входом, третьим входом третьего элемента И с инверсным входом и третьим входом четвертого элемента И второго указателя младшего нуля 12. Выход переноса СО «все единицы» (4+4(v-1)) блока (i-1)-го каскада соединен со четвертым инверсным входом третьего элемента И с инверсным входом и четвертым входом четвертого элемента И второго указателя младшего нуля 12, а также выходы первого и второго элементов И с инверсным входом второго указателя младшего нуля 12 соединены с первыми входами соответственно первого и второго элементов ИЛИ двухразрядного двоичного шифратора 11, вторые входы которых соединены с выходом третьего элемента И с инверсным входом второго указателя младшего нуля 12. При этом выход четвертого элемента И второго модуля указателя младшего нуля 12 является выходом переноса СО «все единицы» каждого v-го блока, а выходы первого и второго элементов ИЛИ двухразрядного двоичного шифратора 11 являются соответственно первым и вторым, выходами каждого v-го блока.

Первый b0, второй b1, третий b2 и четвертый b3 выходы всех L блоков первого каскада 1 соединены с соответствующими входами одноименных элементов ИЛИ выходного блока 4, первый и второй выходы всех блоков в i-м каскаде (i=2, …, М) соединены с соответствующими входами соответственно (2i + 1)-го и (2i + 2)-го элементов ИЛИ выходного блока 4.

Выходы (К-2) элементов ИЛИ выходного блока 4, первый и второй выходы блока последнего (М + 1)-го каскада и выход последнего элемента 6L из группы из L элементов И являются соответственно (K + 1) разрядами В0, В1, …, BK выходного двоичного кода.

ПОДРОБНОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Предлагаемое устройство для коррекции порядка при нормализации чисел работает следующим образом.

На входы устройства поступает N разрядов входного двоичного числа D1, …, D256 (DN) и знак числа Sign, представленные в дополнительном или обратном коде. Для положительных чисел значение знака Sign = 0, а для отрицательных Sign = 1. Младший разряд D1 является старшим разрядом входного двоичного числа.

Во входном блоке управляемой инверсии 5 разряды входного числа D1, …, D16 (Dn) не изменяются для отрицательных чисел при значении знака Sign = l, или все разряды инвертируются для положительных чисел при значении знака Sign = 0. Таким образом в младших разрядах на внутренней шине X1, Х2, …, Х256 (XN) (при этом X1 - младший разряд, XN - старший разряд) будут сформированы единичные значения, соответствующие старшим нулевым (незначащим) разрядам во входном двоичном числе в зависимости от знака числа Sign.

Далее определяется количество единиц в младших разрядах шины X.

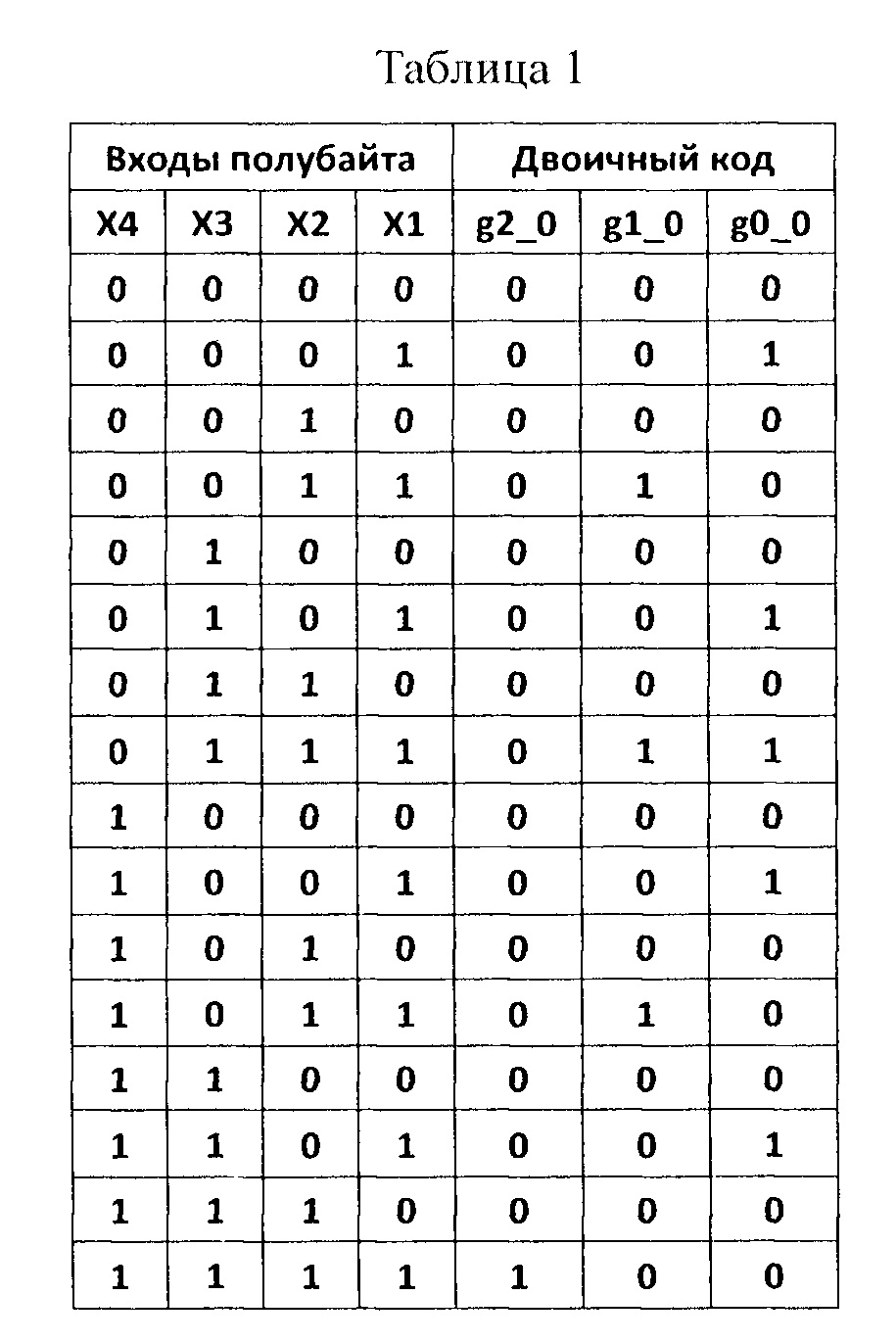

Для определения количества единиц разряды внутренней шины X делятся на группы по четыре разряда соответствующие полубайтам числа, начиная с младшего разряда X1. Для каждого полубайта четыре входных разряда одновременно параллельно преобразуются в трехразрядный двоичный код g2, g1, g0 (g0 - младший разряд) соответствующий количеству единиц в полубайте. Пример таблицы истинности для преобразования разрядов Х4, Х3, Х2, X1 младшего нулевого полубайта в двоичный код g2_0, g1_0, g0_0 приведен в таблице 1. На основе таблицы 1 составлена сокращенная таблица истинности (таблица 2) для формирования трехразрядного двоичного кода, в которой введено обозначение X - любое значение. Для минимизации схемы учитывается, что при всех единичных значениях на входах Х4, ХЗ, Х2, XI (нижняя строка в таблице 2) формируется старший третий бит g2_0 = 1, при котором на выход блока не передаются значения двух младших бит g1_0, g0_0. На основе таблицы 2 для разрядов двоичного кода получены следующие выражения:

g0_0 = X1 and not Х2 or X1 and Х3,

g1_0 = X1 and X2,

g2_0 = X1 and X2 and X3 and X4.

Единичное значение разряда g0_0 указывает на нечетное количество единиц (одна единица в младшем разряде X1 или три единицы в разрядах X1, Х2 и Х3), единичное значение разряда g1_0 указывает на две единицы в младших разрядах X1 и Х2, единичное значение разряда g2_0 указывает на наличие всех четырех единиц в разрядах X1, Х2, Х3 и Х4. В соответствии с данными выражениями реализованы группы преобразователей в двухразрядный двоичный код 7 и модули проверки полубайтов 9.

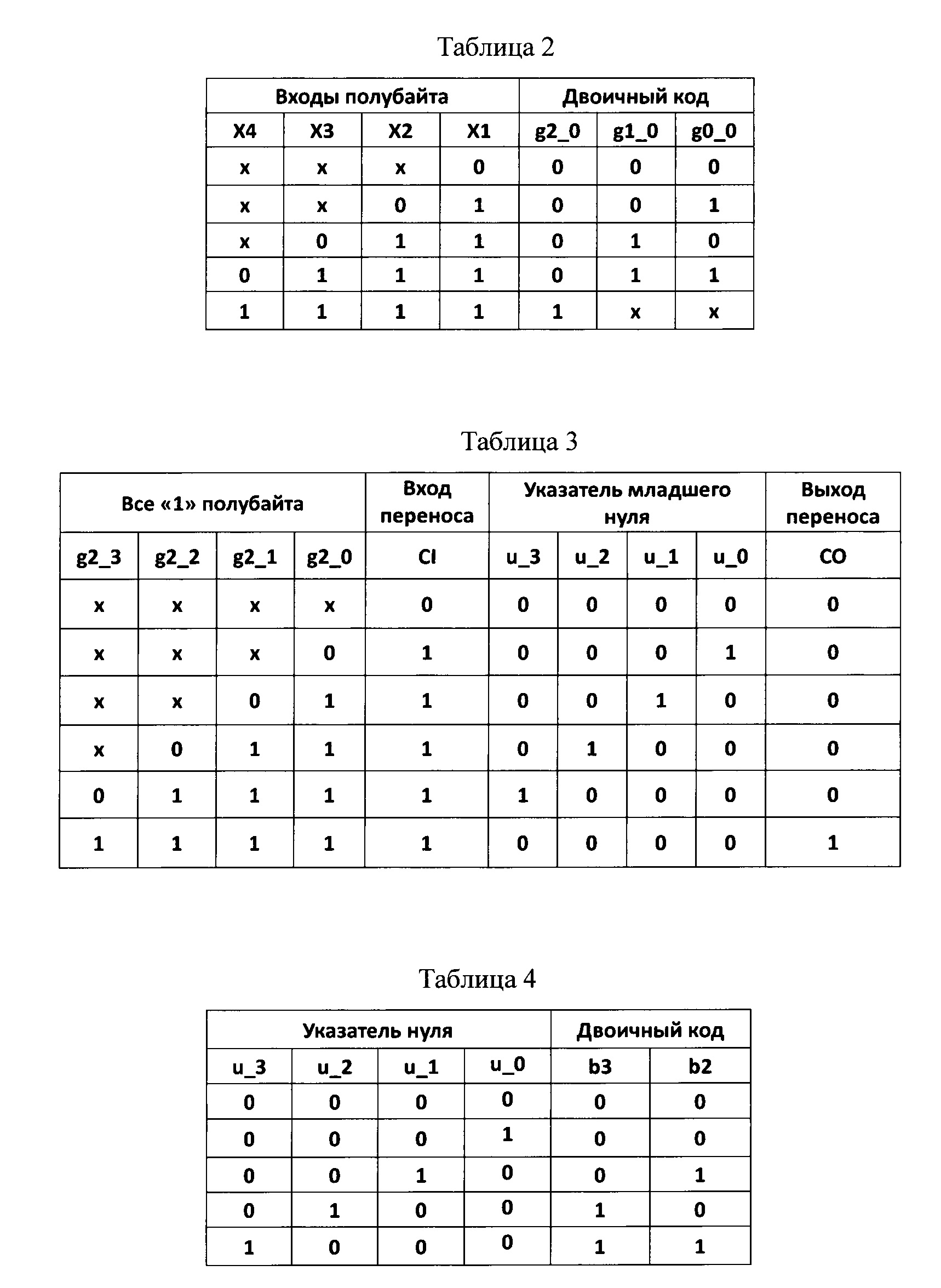

Передача на выход двух младших разрядов g1 и g0 двоичного кода соответствующих полубайтов выполняется двухразрядными коммутаторами 8. На выходы коммутаторов 8 передаются значения разрядов g1 и g0 только от одного полубайта из всех полубайтов, которые являются значениями разрядов b1 и b0 выходного двоичного кода для полубайта. Управление коммутаторами 8 выполняется модулями указателей младшего нуля 10, на выходах u_3, u_2, u_1, u_0 которых формируется унитарный код «1 из N», при котором только на одном выходе формируется единичное значение, а на остальных выходах формируются нулевые значения, или на всех выходах формируются нулевые значения. Таблица истинности для формирования значений выходов указателей младших нулей 10 и сигнала выхода переноса блока СО «все единицы» в зависимости от значений старших разрядов g2 двоичного кода полубайтов, которые соответствуют значениям «все единицы» полубайта, и входа переноса блока CI «все единицы» приведены в таблице 3. Единичное значение на соответствующем выходе и указателя младшего нуля 10 формируется при единичном значении на входе переноса блока CI «все единицы», единичных значениях в разрядах g2 для младших полубайт и нулевом значении соответствующего входа g2.

Для повышения быстродействия в устройство введена схема ускоренного переноса значений «все единицы» между блоками 1 первого каскада. Ускоренный перенос между блоками 1 реализуется группой из L элементов И 61, 62, …, 616(L). Перенос внутри групп из четырех блоков 1 проводится параллельно, а между группами из четырех блоков 1 по следовательно.

Значения выходов u_3, u_2, u_1, u_0 указателей младшего нуля 10 используются также для формирования номера полубайта в блоках 1. Номер полубайта (разряды b3 и b2) внутри каждого блока 1 первого каскада формируется двухразрядными двоичными шифраторами 11 в соответствии с таблицей истинности приведенной в таблице 4. Двоичные шифраторы преобразуют унитарный код в двоичный код b3, b2. В таблице 4 приведено только пять строк, так как на входе не может быть других комбинаций. На основе таблицы 4 получены следующие выражения для разрядов b3 и b2 номера полубайта в каждом блоке:

b2 = u_1 or u_3,

b3 = u_2 or u_3.

При этом, так как единичное значение устанавливается только на одном выходе всех указателей младшего нуля 10 всех блоков 1 первого каскада, то значения разрядов g1 и g0 полубайтов передаются только на одном двухразрядном коммутаторе 8 и значения разрядов b3 и b2 формируются только на одном двухразрядном двоичном шифраторе 11, а на выходах остальных двухразрядных коммутаторов 8 и двухразрядных двоичных шифраторах 11 будут установлены нулевые значения. Одноименные выходы разрядов b3, b2, b1 и b0 блоков первого каскада соединены с входами одноименных элементах ИЛИ выходного блока 4, выходы которого являются соответствующими разрядами В3, В2, В1, В0 выходного двоичного кода В.

Во втором каскаде формируются значения разрядов b5 и b4 указывающие номер блока 1 в группах из четырех блоков 1 первого каскада. Формирование разрядов b5 и b4 выполняется аналогично как в таблице 4 на вторых указателях младшего нуля 12 и двоичных шифраторах 11, при этом входными данными для вторых указателей младшего нуля 12 являются выходы переноса блоков СО «все единицы» первого каскада, на всех выходах которых также формируется унитарный код «1 из N». Одноименные выходы b5 и b4 блоков 2 второго каскада соединены с входами одноименных элементах ИЛИ выходного блока 4, выходы которого являются соответствующими разрядами В5 и В4 выходного двоичного кода В. Кроме того в каждом блоке 2 второго каскада также формируются сигналы выхода переноса блока СО «все единицы».

Выходы переноса блока СО «все единицы» второго каскада являются входными сигналами для третьего каскада, далее выходы переноса блока СО «все единицы» третьего каскада являются входами для четвертого каскада и т.д. На фиг. 2 представлены формат данных шины X и схема формирования значений разрядов выходного кода В при N=256.

Таким образом, на (K + 1) разрядах В0, В1, …, В8 (BK + 1) выходного двоичного кода будет сформировано значение, соответствующее количеству старших нулей в соответствии со знаком числа для коррекции порядка при нормализации чисел. Если количество N разрядов входного двоичного числа D не кратно 4, то младшие разряды дополняются единичными значениями в соответствующем коде или нулевыми значениями на внутренней шине X.

Блоки каскадов предлагаемого устройства могут быть преобразованы для реализации в базисах штрих Шеффера (И-НЕ) или стрелка Пирса (ИЛИ-НЕ). Также блоки могут быть описаны на языках VHDL или Verilog для реализации на ПЛИС.

Предлагаемое устройство для коррекции порядка при нормализации чисел в сравнении с устройством прототипом обладает более высоким быстродействием, так как при увеличении разрядности входных данных в предлагаемом устройстве введены схемы для ускоренного переноса между блоками, а в прототипе применяется последовательная передача выходных разрядов количества нулей между 16-ти разрядными блоками. Также в предлагаемом устройстве уменьшаются аппаратные средства, так как для управления коммутаторами 8 передачи разрядов полубайтов и для формирования номеров полубайтов в двоичных шифраторах 11 используются одни и те же схемы указателей младших нулей 10, а в прототипе реализованы раздельно.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство для коррекции порядка при нормализации чисел решает поставленную задачу определение количества старших нулевых разрядов в многоразрядных входных данных, обладает регулярностью узлов и связей, при этом упрощается конструкция и, следовательно, устройство соответствует заявляемому техническому результату - сокращение аппаратных затрат, увеличение быстродействия, расширение функциональных возможностей в части возможности определения старших нулевых разрядов для двоичных чисел со знаком, а также упрощение увеличения разрядности входных данных.

Реферат

Изобретение относится к области вычислительной техники, в частности к устройствам обработки данных, и может быть использовано для построения средств автоматики и функциональных узлов систем управления, а также в устройствах обработки чисел с плавающей запятой при нормализации данных. Техническим результатом является уменьшение аппаратных затрат, увеличение быстродействия устройства, обеспечение возможности определения старших нулевых разрядов для двоичных чисел со знаком, а также упрощение увеличения разрядности входных данных. Устройство содержит (М + 1) каскадов блоков пирамидальной структуры, выходной блок, входной блок управляемой инверсии, группу элементов И, при этом в 1-м каскаде каждый блок содержит преобразователь в двухразрядный двоичный код, двухразрядный коммутатор, модуль проверки полубайтов, первый модуль указателя младшего нуля, двухразрядный двоичный шифратор, а каждый блок со второго по (М + 1)-го каскада содержит второй модуль указателя младшего нуля и двухразрядный двоичный шифратор. 2 ил., 4 табл.

Формула

Документы, цитированные в отчёте о поиске

Система и способ подсчета начальных нулевых разрядов и подсчета начальных единичных разрядов в цифровом процессоре сигналов

Комментарии