Система и способ подсчета начальных нулевых разрядов и подсчета начальных единичных разрядов в цифровом процессоре сигналов - RU2409837C2

Код документа: RU2409837C2

Чертежи

Описание

УРОВЕНЬ ТЕХНИКИ

I. ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее раскрытие в целом относится к цифровым процессорам сигналов и устройствам, которые используют такие процессоры. Более конкретно раскрытие относится к компонентам внутренней части цифрового процессора сигналов, которые выполняют подсчет нулевых начальных разрядов или подсчет единичных начальных разрядов в словах данных.

II. ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Усовершенствования в технологии привели к более малым и более мощным персональным вычислительным устройствам. Например, в настоящее время имеются разнообразные портативные персональные вычислительные устройства, включающие в состав вычислительные устройства беспроводной связи, такие как портативные беспроводные телефоны, персональные цифровые ассистенты (ПЦА, PDA), и устройства персонального вызова, которые являются небольшими, легкими и без труда носимыми пользователями. Более конкретно, портативные беспроводные телефоны, такие как телефоны сотовой связи и поддерживающие Интернет-протокол (ИП, IP) телефоны, могут передавать речь и пакеты данных по сетям беспроводной связи. Кроме того, многие такие беспроводные телефоны включают в себя устройства других типов, которые встроены в них. Например, беспроводной телефон может также включать в себя цифровую фотокамеру, цифровую видеокамеру, устройство цифровой записи и устройство воспроизведения аудиофайла. К тому же, такие беспроводные телефоны могут включать в себя web-интерфейс, который может использоваться для осуществления доступа к Интернету. Как таковые, эти беспроводные телефоны включают в себя значительные вычислительные возможности.

Некоторые из программ, которые обеспечивают функциональность различных устройств, встроенных во внутреннюю часть беспроводного телефона, включают в себя команды, которые требуют счета нулевых начальных разрядов или счета единичных начальных разрядов для конкретных слов данных. Обычно используются множество размеров слов данных в зависимости от различных программ. Как таковые, могут использоваться многие компоненты аппаратных средств для выполнения счета нулевых начальных разрядов и единичных начальных разрядов в пределах различных слов данных.

Таким образом будет полезно обеспечить в рамках цифрового процессора сигналов усовершенствованную систему и способ выполнения счета нулевых начальных разрядов и выполнения счета единичных начальных разрядов.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Раскрывается способ обработки слова данных и включает в себя этапы приема слова данных и определения, является ли слово данных тридцатидвухразрядным словом данных или шестидесятичетырехразрядным словом данных. Кроме того, способ включает в себя этап расширения за счет знака тридцатидвухразрядного слова данных, чтобы создавать временное шестидесятичетырехразрядное слово данных после определения, что слово данных является тридцатидвухразрядным словом данных.

В конкретном варианте осуществления способ может включать в себя этап определения, должно ли определяться количество нулевых начальных разрядов или количество единичных начальных разрядов. Также в конкретном варианте осуществления способ может включать в себя этап передачи временного шестидесятичетырехразрядного слова данных на двоичный счетчик, имеющий разрядность шестьдесят четыре двоичных разряда, после определения, что должно быть определено количество нулевых начальных разрядов. Дополнительно, в конкретном варианте осуществления, способ может включать в себя этапы выполнения счета нулевых начальных разрядов во временном шестидесятичетырехразрядном слове данных, чтобы формировать расширенное за счет знака значение подсчета нулевых начальных разрядов, вычитания постоянного значения тридцать два из расширенного за счет знака значения подсчета нулевых начальных разрядов, если число не является нулем, чтобы сформировать определяемое значение подсчета нулевых начальных разрядов, и записи в регистр определенного значения подсчета нулевых начальных разрядов.

В другом конкретном варианте осуществления способ может включать в себя этап инвертирования временного шестидесятичетырехразрядного слова данных, чтобы создавать инвертированное шестидесятичетырехразрядное слово данных, если должно определяться число единичных начальных разрядов. Также в конкретном варианте осуществления способ может включать в себя этапы передачи инвертированного временного шестидесятичетырехразрядного слова данных на двоичный счетчик разрядностью шестьдесят четыре двоичных разряда, выполняющий подсчет нулевых начальных разрядов в инвертированном временном шестидесятичетырехразрядном слове данных, чтобы сформировать расширенное за счет знака значение подсчета единичных начальных разрядов, вычитания постоянного значения тридцать два из расширенного за счет знака значения подсчета единичных начальных разрядов, если значение подсчета не является нулем, чтобы сформировать определенное значение подсчета единичных начальных разрядов, и записи в регистр определенного значения подсчета единичных начальных разрядов.

В следующем конкретном варианте осуществления способ может дополнительно включать в себя этап определения, должно ли использоваться количество нулевых начальных разрядов или количество единичных начальных разрядов после определения, что слово данных является шестидесятичетырехразрядным словом данных. Дополнительно, в конкретном варианте осуществления способ может включать в себя этап передачи шестидесятичетырехразрядного слова данных на двоичный счетчик разрядностью шестьдесят четыре разряда после определения, что должно использоваться количество нулевых начальных разрядов, этап выполнения подсчета нулевых начальных разрядов в шестидесятичетырехразрядном слове данных, чтобы сформировать определенное значение подсчета нулевых начальных разрядов, и этап записи в регистр определенного значения подсчета нулевых начальных разрядов.

В очередном конкретном варианте осуществления способ может включать в себя этап инвертирования шестидесятичетырехразрядного слова данных, чтобы создавать инвертированное шестидесятичетырехразрядное слово данных, если должно использоваться количество единичных начальных разрядов, этап передачи инвертированного шестидесятичетырехразрядного слова данных на шестидесятичетырехразрядный счетчик, этап выполнения подсчета нулевых начальных разрядов в инвертированном шестидесятичетырехразрядном слове данных, чтобы сформировать определенное значение подсчета единичных начальных разрядов, и этап записи в регистр определенного значения подсчета единичных начальных разрядов.

В другом варианте осуществления раскрыт способ и может включать в себя этап использования двоичного счетчика разрядностью шестьдесят четыре разряда, чтобы выполнять подсчет одного или нескольких нулевых начальных разрядов в тридцатидвухразрядном слове.

В следующем варианте осуществления раскрыто устройство исполнения команд для цифрового процессора сигналов и может включать в себя блок управления, расширитель знака, связанный с блоком управления, инвертор, связанный с блоком управления, и двоичный счетчик разрядностью шестьдесят четыре разряда, связанный с блоком управления. В этом варианте осуществления блок управления может включать в себя логику (логическую схему), чтобы давать команды двоичному счетчику выполнить подсчет нулевых начальных разрядов в одном или нескольких тридцатидвухразрядных словах, принятых в устройстве исполнения команд, и логику, чтобы давать команды шестидесятичетырехразрядному логическому счетчику выполнить счет нулевых начальных разрядов в одном или нескольких шестидесятичетырехразрядных словах данных, принятых в устройстве исполнения команд.

В очередном варианте осуществления обеспечивается цифровой процессор сигналов и включает в себя запоминающее устройство, контроллер последовательности исполнения команд (планировщик), который реагирует (действует в зависимости от содержимого) на запоминающее устройство, блок регистров, который является связанным с запоминающим устройством, и устройство исполнения команд, которое реагирует на контроллер последовательности. В этом варианте осуществления устройство исполнения команд может включать в себя блок управления, расширитель знака, который связан с блоком управления, инвертор, который связан с блоком управления, и двоичный счетчик разрядностью шестьдесят четыре разряда, который связан с блоком управления. В этом варианте осуществления блок управления может включать в себя логику для управления шестидесятичетырехразрядным логическим счетчиком, чтобы выполнять счет нулевых начальных разрядов в одном или нескольких тридцатидвухразрядных словах, и логику, чтобы управлять двоичным счетчиком разрядностью шестьдесят четыре разряда для выполнения счета нулевых начальных разрядов в одном или нескольких шестидесятичетырехразрядных словах данных.

В очередном варианте осуществления раскрыто портативное устройство связи и включает в себя цифровой процессор сигналов. В этом варианте осуществления цифровой процессор сигналов может включать в себя запоминающее устройство, контроллер последовательности, который реагирует на запоминающее устройство, блок регистров, который связан с запоминающим устройством, и устройство исполнения команд, которое реагирует на контроллер последовательности. В этом варианте осуществления устройство исполнения команд может включать в себя блок управления, расширитель знака, связанный с блоком управления, инвертор, связанный с блоком управления, и двоичный счетчик разрядностью шестьдесят четыре разряда, который является связанным с блоком управления. В этом варианте осуществления блок управления может включать в себя логику, чтобы управлять шестидесятичетырехразрядным логическим счетчиком для выполнения счета нулевых начальных разрядов в одном или нескольких тридцатидвухразрядных словах, и логику, чтобы управлять шестидесятичетырехразрядным логическим счетчиком для выполнения счета нулевых начальных разрядов в одном или нескольких шестидесятичетырехразрядных словах данных.

В очередном варианте осуществления раскрыто процессорное устройство и включает в себя средство для приема тридцатидвухразрядного слова данных, средство для расширения за счет знака тридцатидвухразрядного слова данных, чтобы создавать временное шестидесятичетырехразрядное слово данных, средство для выполнения подсчета нулевых начальных разрядов во временном шестидесятичетырехразрядном слове данных, чтобы получать промежуточное значение подсчета нулевых начальных разрядов, и средство для вычитания значения из промежуточного значения подсчета нулевых начальных разрядов, если значение подсчета не является нулем, чтобы получать окончательное значение подсчета нулевых начальных разрядов.

В другом варианте осуществления раскрыто процессорное устройство и включает в себя средство для приема тридцатидвухразрядного слова данных, средство для расширения за счет знака тридцатидвухразрядного слова данных, чтобы создавать временное шестидесятичетырехразрядное слово данных, средство для инвертирования временного шестидесятичетырехразрядного слова данных, чтобы создавать инвертированное временное шестидесятичетырехразрядное слово данных, средство для выполнения счета нулевых начальных разрядов во временном шестидесяти-четырех-разрядном слове данных, чтобы получать промежуточное значение подсчета единичных начальных разрядов, и средство для вычитания значения из промежуточного значения подсчета единичных начальных разрядов, если значение подсчета не является нулем, чтобы получать окончательное значение подсчета нулевых начальных разрядов.

В следующем варианте осуществления раскрыто процессорное устройство и включает в себя средство для приема слова данных, средство для определения, является ли слово данных тридцатидвухразрядным словом данных или шестидесятичетырехразрядным словом данных, и средство для расширения за счет знака тридцатидвухразрядного слова данных, чтобы создавать временное шестидесятичетырехразрядное слово данных.

В очередном варианте осуществления раскрыт способ обработки слова данных и включает в себя этап приема слова данных, имеющего разрядность 2 в N-й степени. Способ дополнительно включает в себя этап расширения за счет знака слова данных до временного слова данных, имеющего разрядность 2 в М-й степени, и ввода временного слова данных на счетчик, имеющий разрядность 2 в М-й степени.

В очередном варианте осуществления раскрыто процессорное устройство и включает в себя средство для приема слова данных, имеющего разрядность 2 в N-й степени, средство для расширения за счет знака слова данных до временного слова данных, имеющего разрядность 2 в М-й степени, и средство для ввода временного слова данных в счетчик, имеющий разрядность 2 в М-й степени.

В другом варианте осуществления раскрыто устройство для воспроизведения аудиофайла и включает в себя цифровой процессор сигналов, кодер/декодер (кодек, CODEC) аудио, который связан с цифровым процессором сигналов, мультимедийную плату, которая соединена с цифровым процессором сигналов, и порт универсальной последовательной шины (УПШ, USB), который связан с цифровым процессором сигналов. В этом варианте осуществления цифровой процессор сигналов включает в себя запоминающее устройство, контроллер последовательности, который реагирует на запоминающее устройство, блок регистров, который связан с запоминающим устройством, и устройство исполнения команд, которое реагирует на контроллер последовательности. Устройство исполнения команд может включать в себя блок управления, расширитель знака, который связан с блоком управления, инвертор, который связан с блоком управления, и двоичный счетчик с разрядностью шестьдесят четыре разряда, который также связан с блоком управления. В этом варианте осуществления блок управления включает в себя логику, чтобы управлять шестидесятичетырехразрядным двоичным счетчиком для выполнения счета нулевых начальных разрядов в одном или в нескольких тридцатидвухразрядных словах. Также блок управления может включать в себя логику для управления шестидесятичетырехразрядным двоичным счетчиком для выполнения счета нулевых начальных разрядов в одном или нескольких шестидесятичетырехразрядных словах данных.

Преимущество одного или нескольких раскрытых в документе вариантов осуществления может включать использование одних и тех же ресурсов для подсчета нулевых начальных разрядов для различных размеров слов данных.

Другое преимущество может включать использование одних и тех же ресурсов для подсчета единичных начальных разрядов для различных размеров слов данных.

Следующее преимущество может включать значительное сокращение аппаратных средств, необходимых для подсчета нулевых начальных разрядов и для подсчета единичных начальных разрядов.

Другие аспекты, преимущества и признаки настоящего раскрытия станут очевидными после рассмотрения всей заявки, включающей нижеследующие разделы: краткое описание чертежей, подробное описание и формулу изобретения.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Аспекты и преимущества описанных в документе вариантов осуществления станут очевидными при чтении нижеследующего подробного описания при рассмотрении вместе с сопроводительными чертежами, на которых:

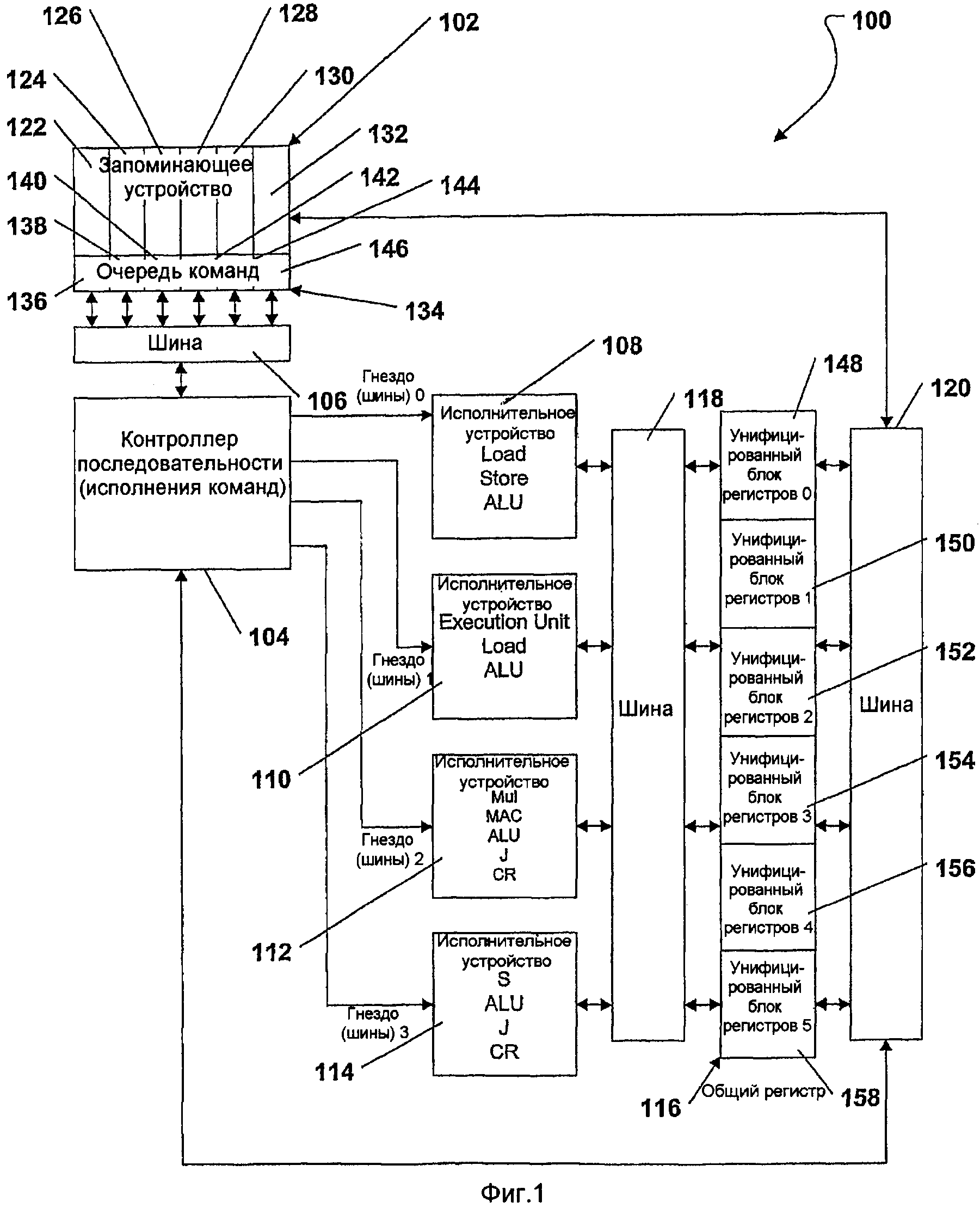

Фиг.1 - общая схема примерного цифрового процессора сигналов;

Фиг.2 - схема, иллюстрирующая примерное устройство исполнения команд;

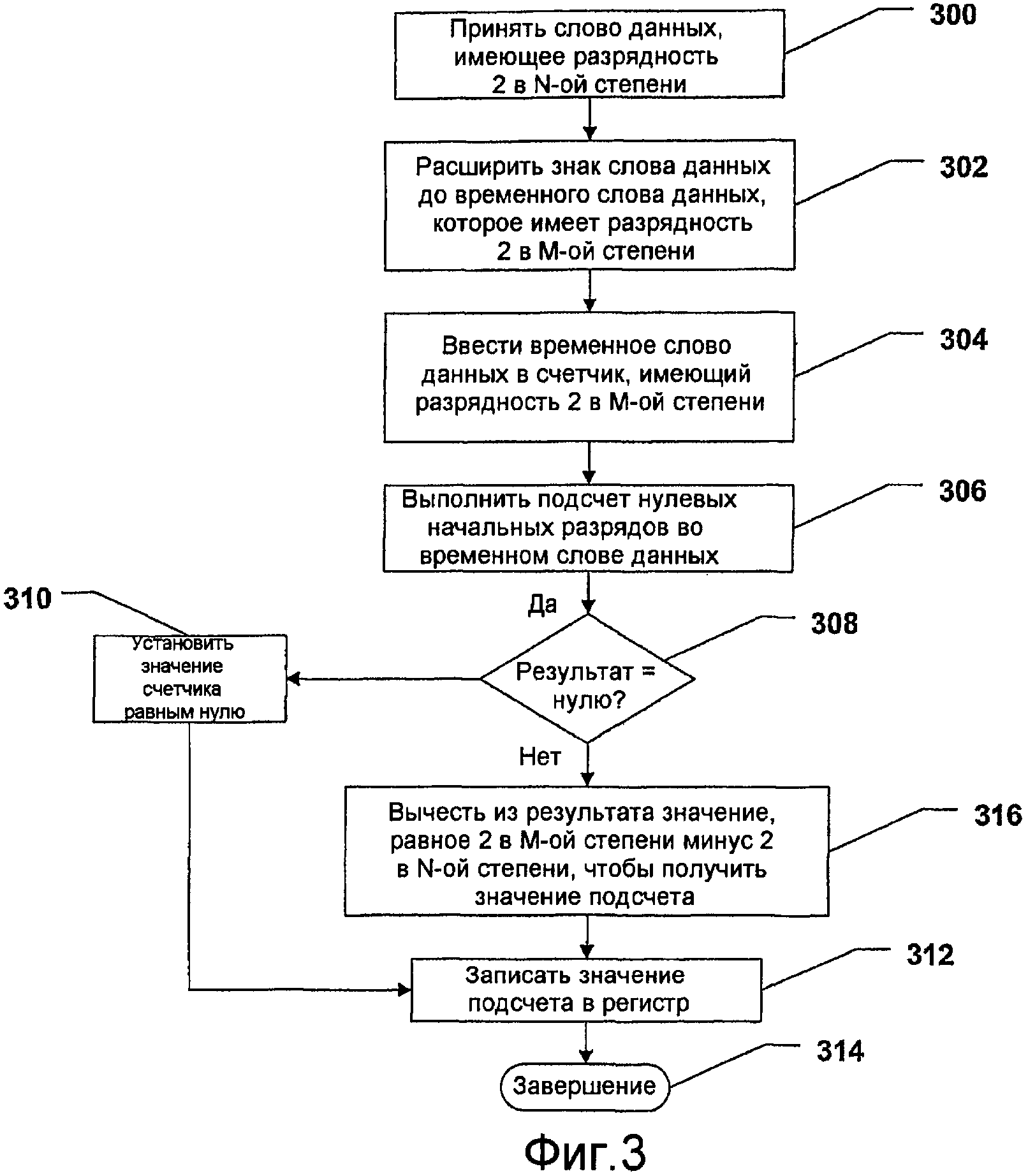

Фиг.3 - схема последовательности действий, иллюстрирующая способ выполнения счета нулевых начальных разрядов в слове данных;

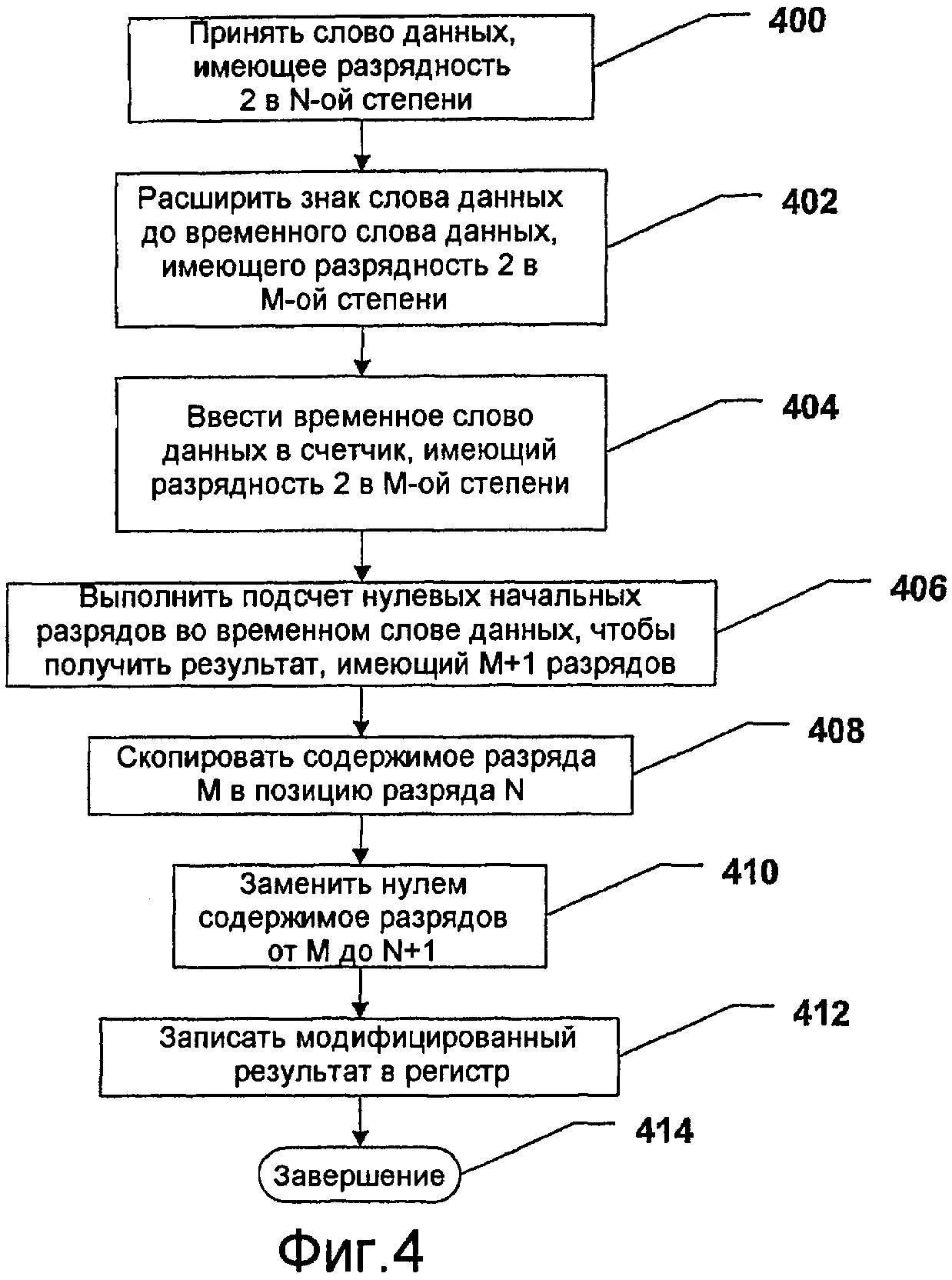

Фиг.4 - схема последовательности действий, иллюстрирующая другой способ выполнения счета нулевых начальных разрядов в слове данных;

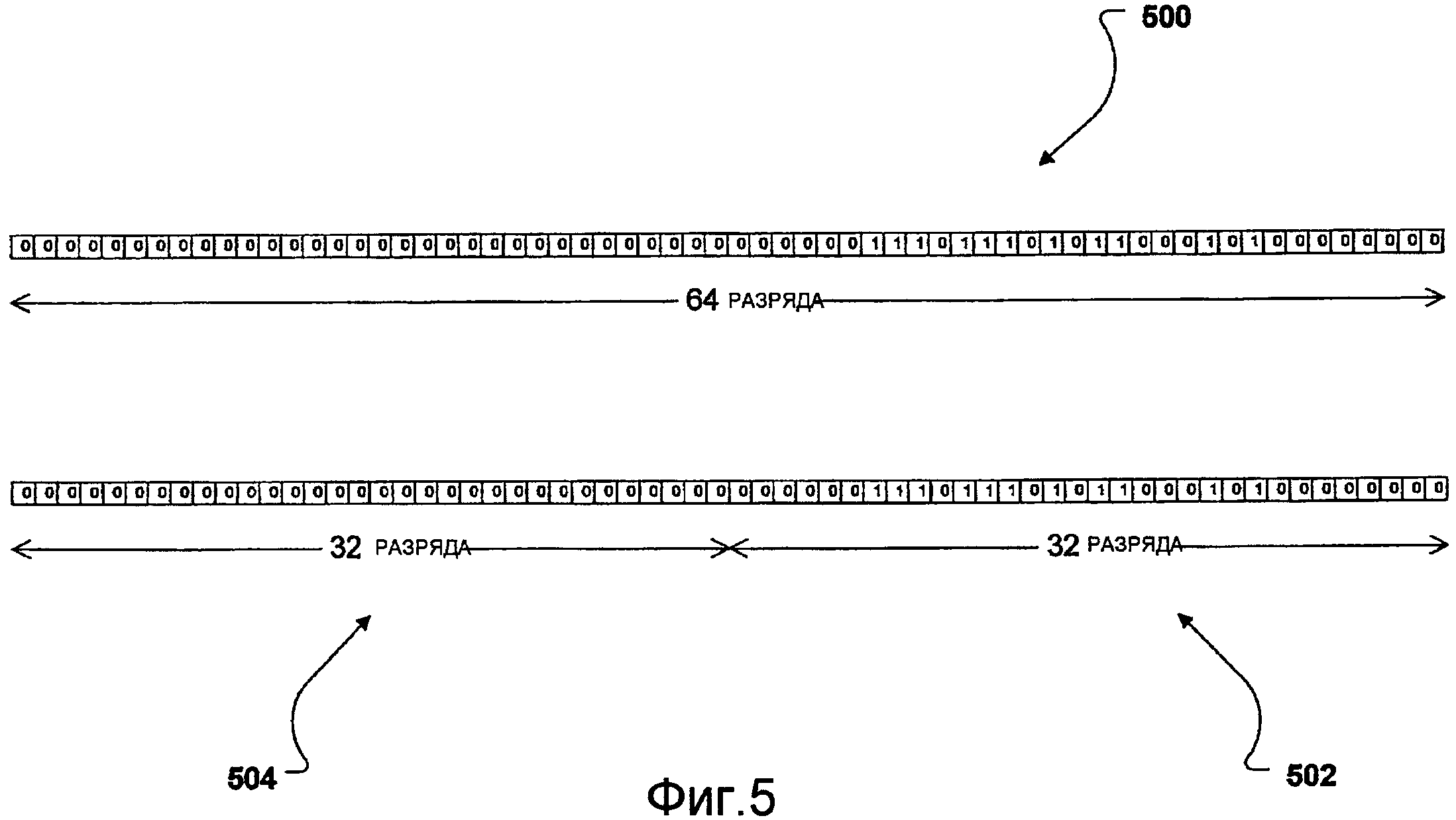

Фиг.5 - схема, иллюстрирующая примерное шестидесятичетырехразрядное слово данных и примерное тридцатидвухразрядное слово данных, которое расширено за счет знака на тридцать два разряда;

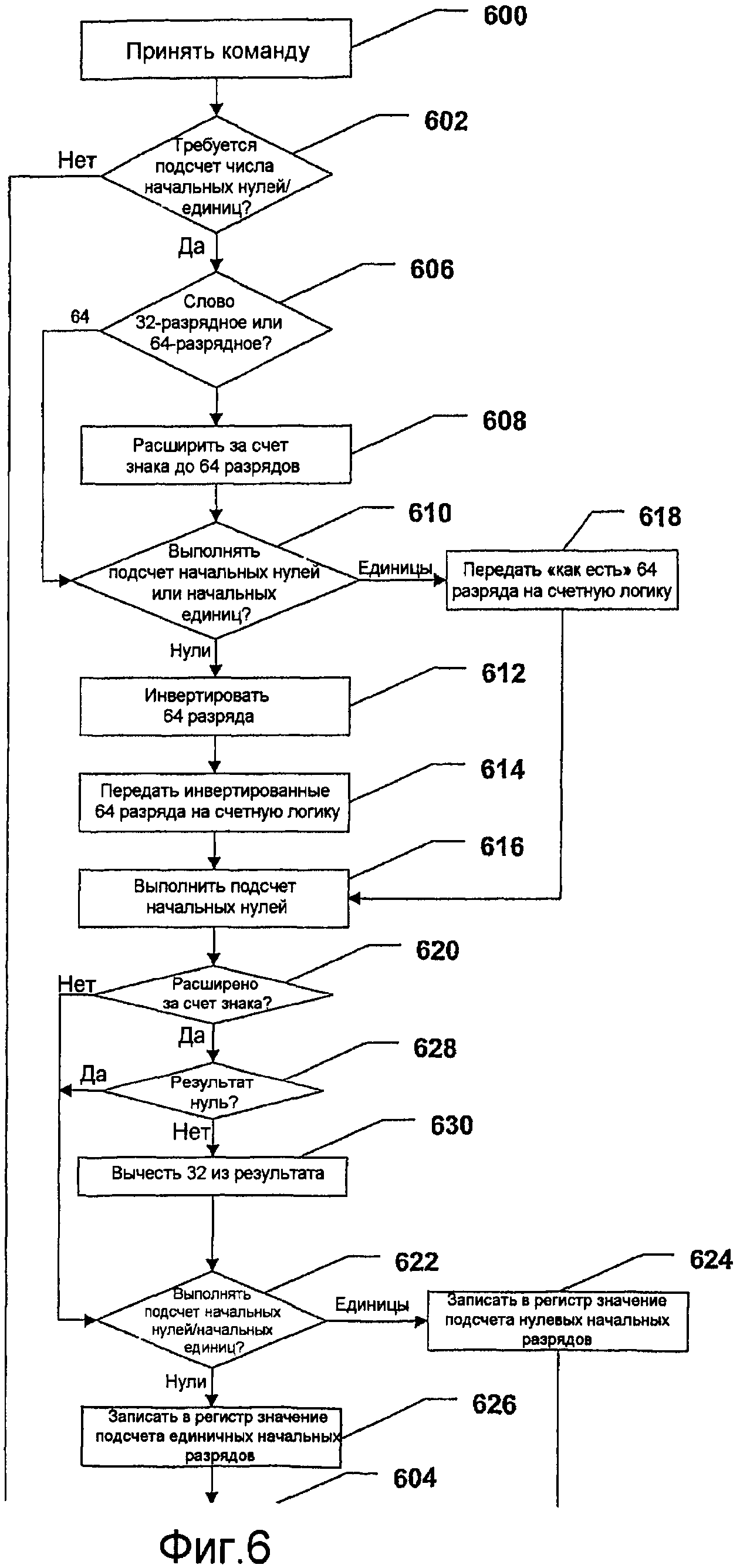

Фиг.6 - схема последовательности действий, иллюстрирующая способ выполнения счета нулевых начальных разрядов и выполнения счета единичных начальных разрядов в шестидесятичетырехразрядном слове данных и тридцатидвухразрядном слове данных;

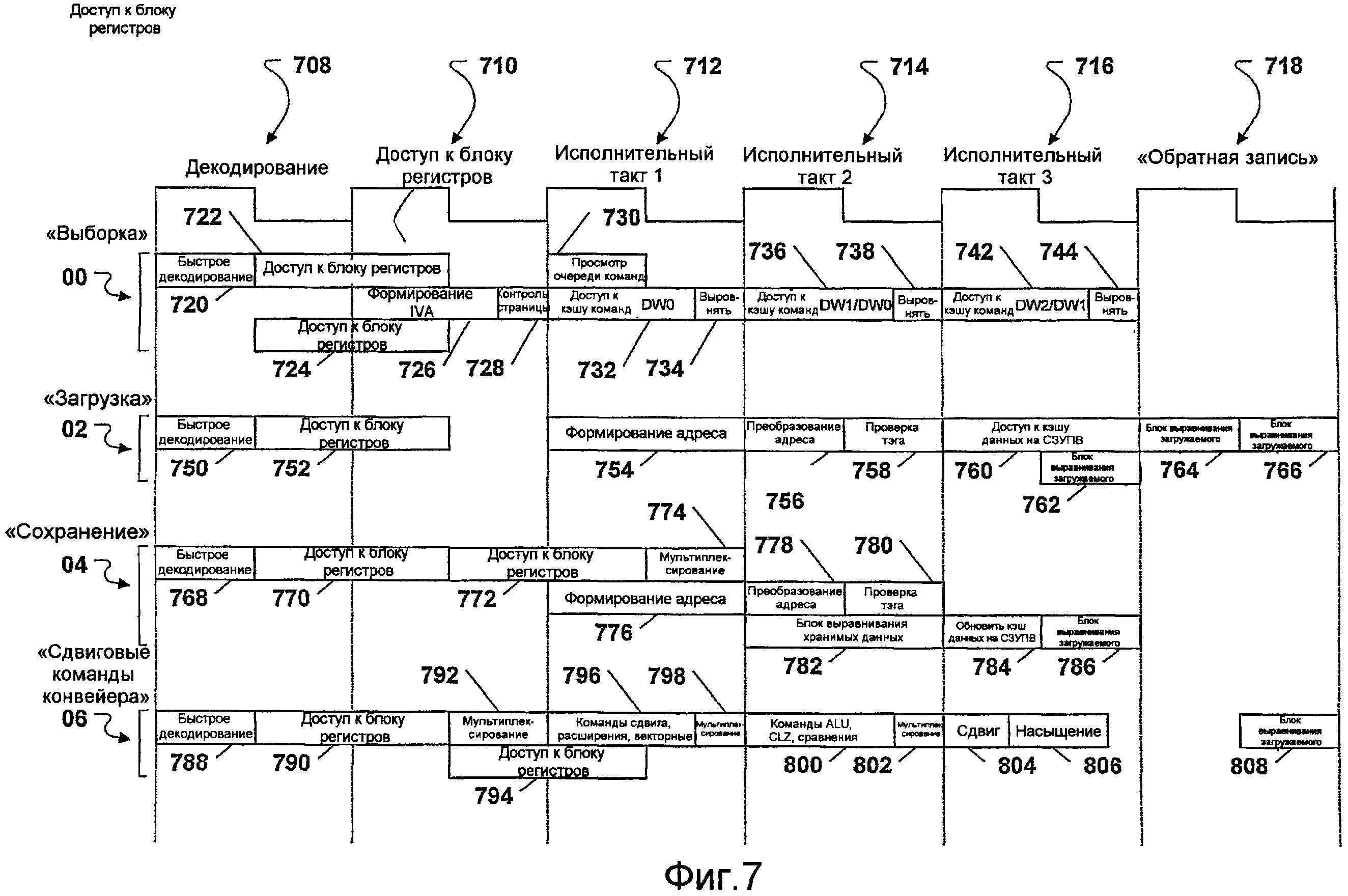

Фиг.7 - схема, иллюстрирующая подробно многопотоковую операцию с чередованием для цифрового процессора сигналов, показанного на Фиг.1;

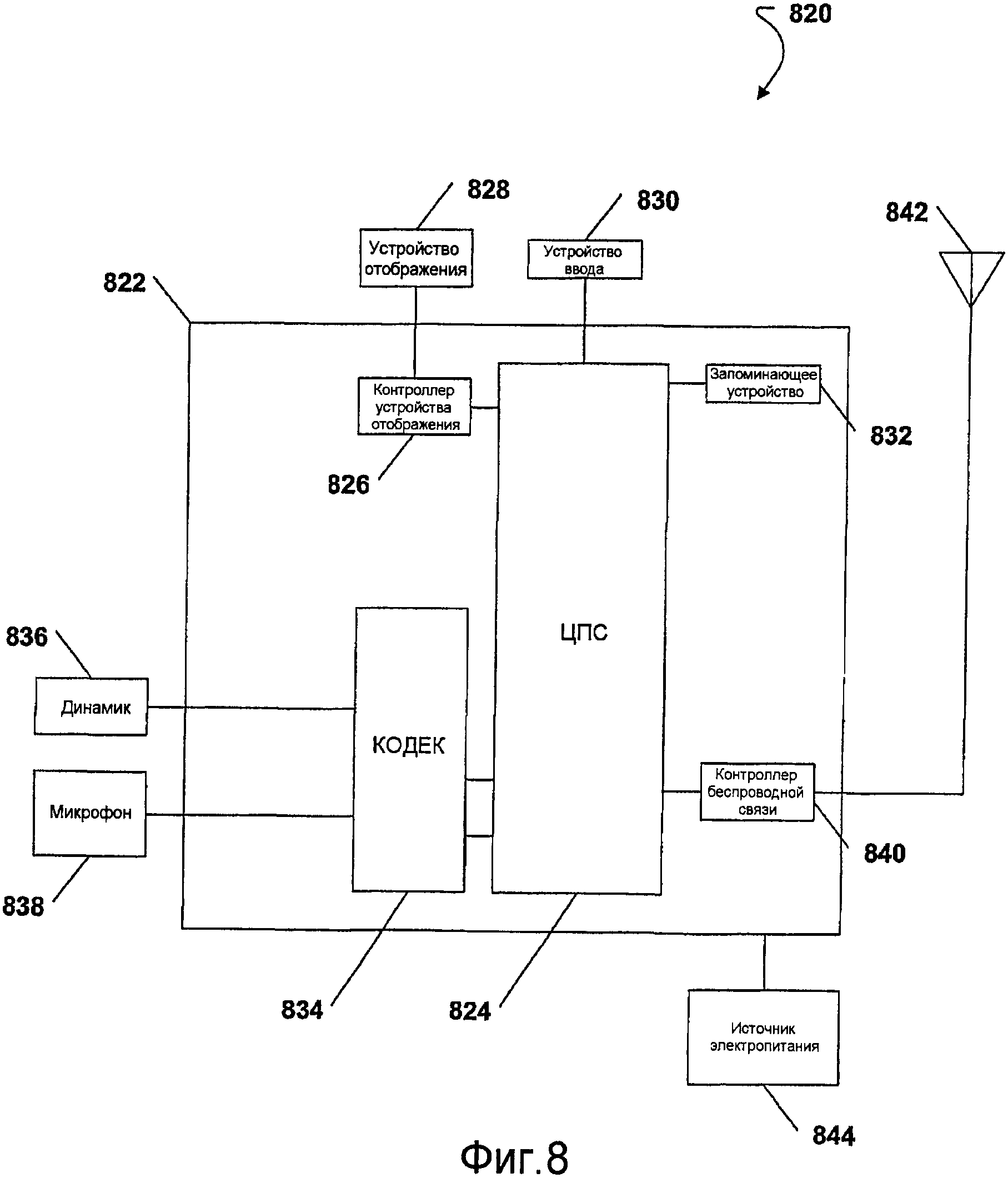

Фиг.8 - общая схема портативного устройства связи, включающего в себя цифровой процессор сигналов;

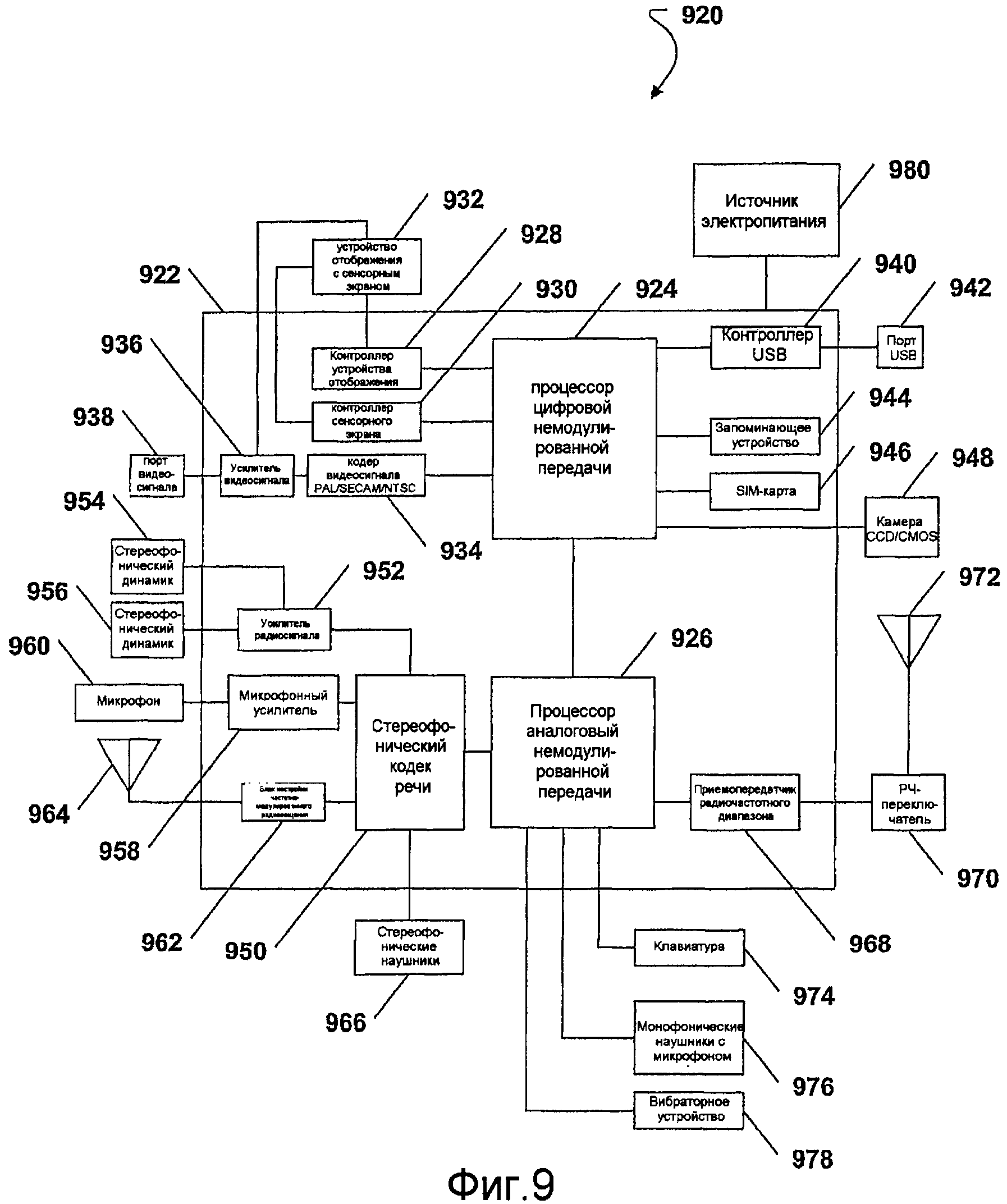

Фиг.9 - общая схема примерного телефона сотовой связи, включающего в себя цифровой процессор сигналов;

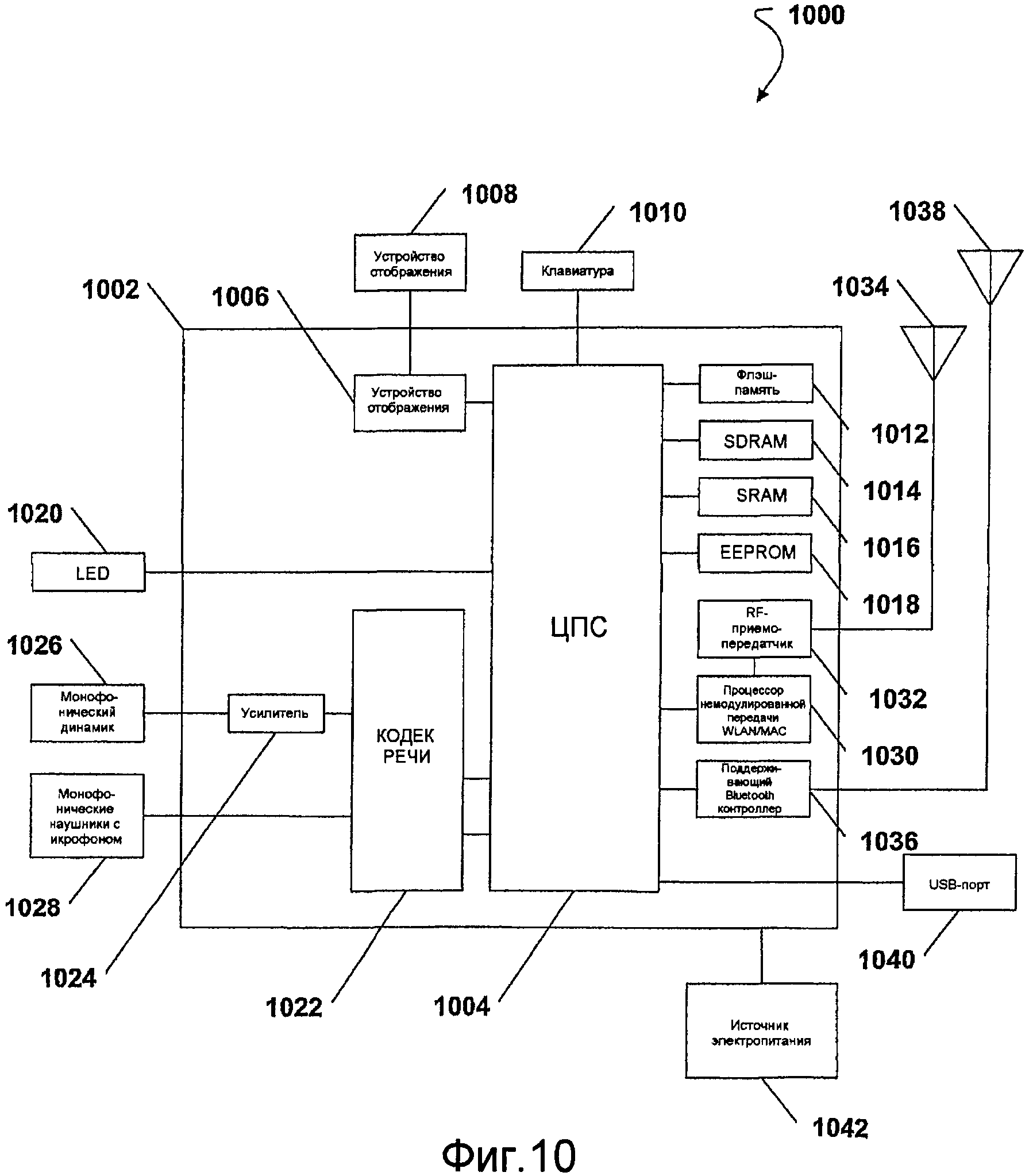

Фиг.10 - общая схема примерного беспроводного, поддерживающего Интернет-протокол телефона, включающего в себя цифровой процессор сигналов;

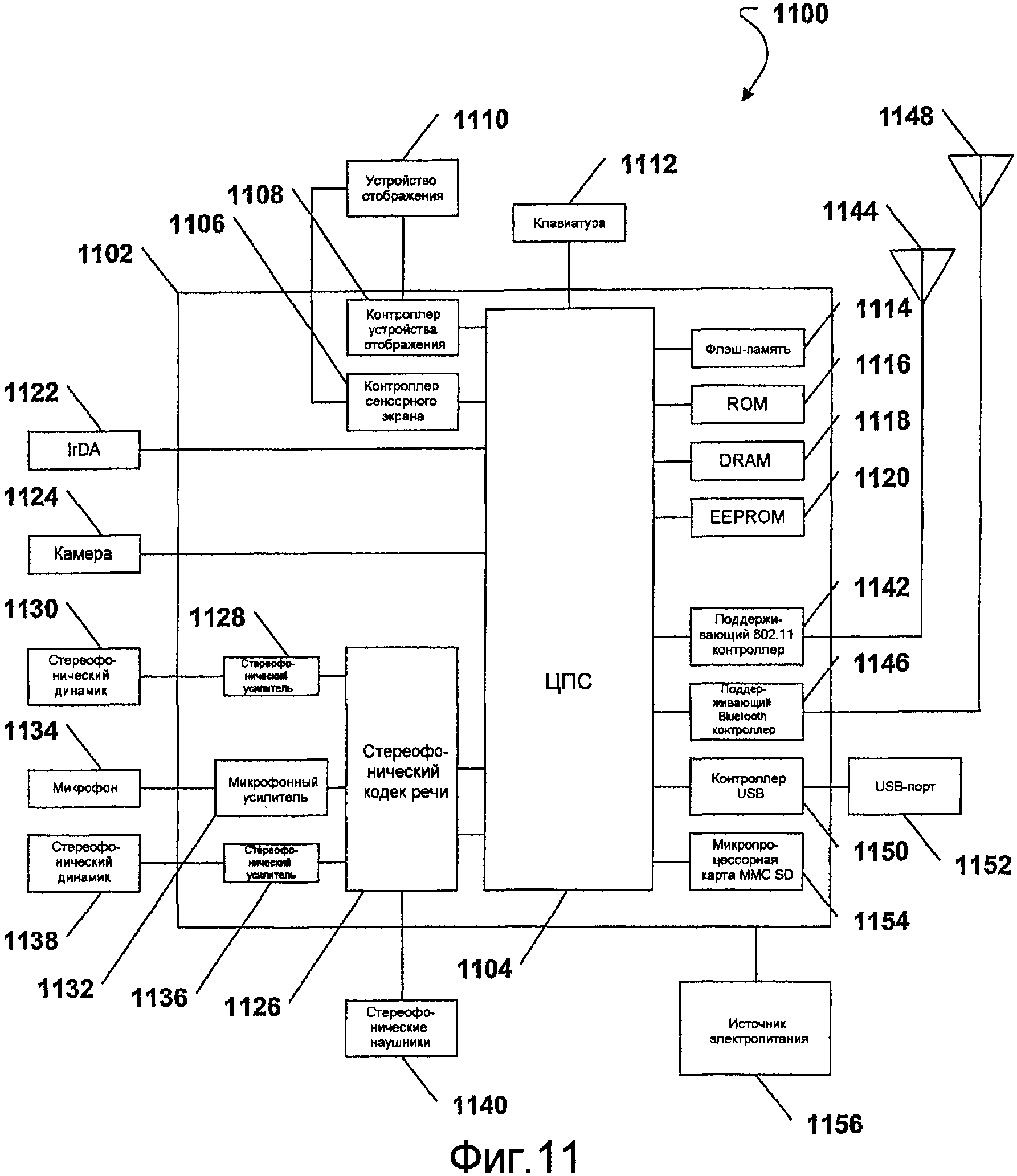

Фиг.11 - общая схема примерного портативного цифрового ассистента, включающего в себя цифровой процессор сигналов; и

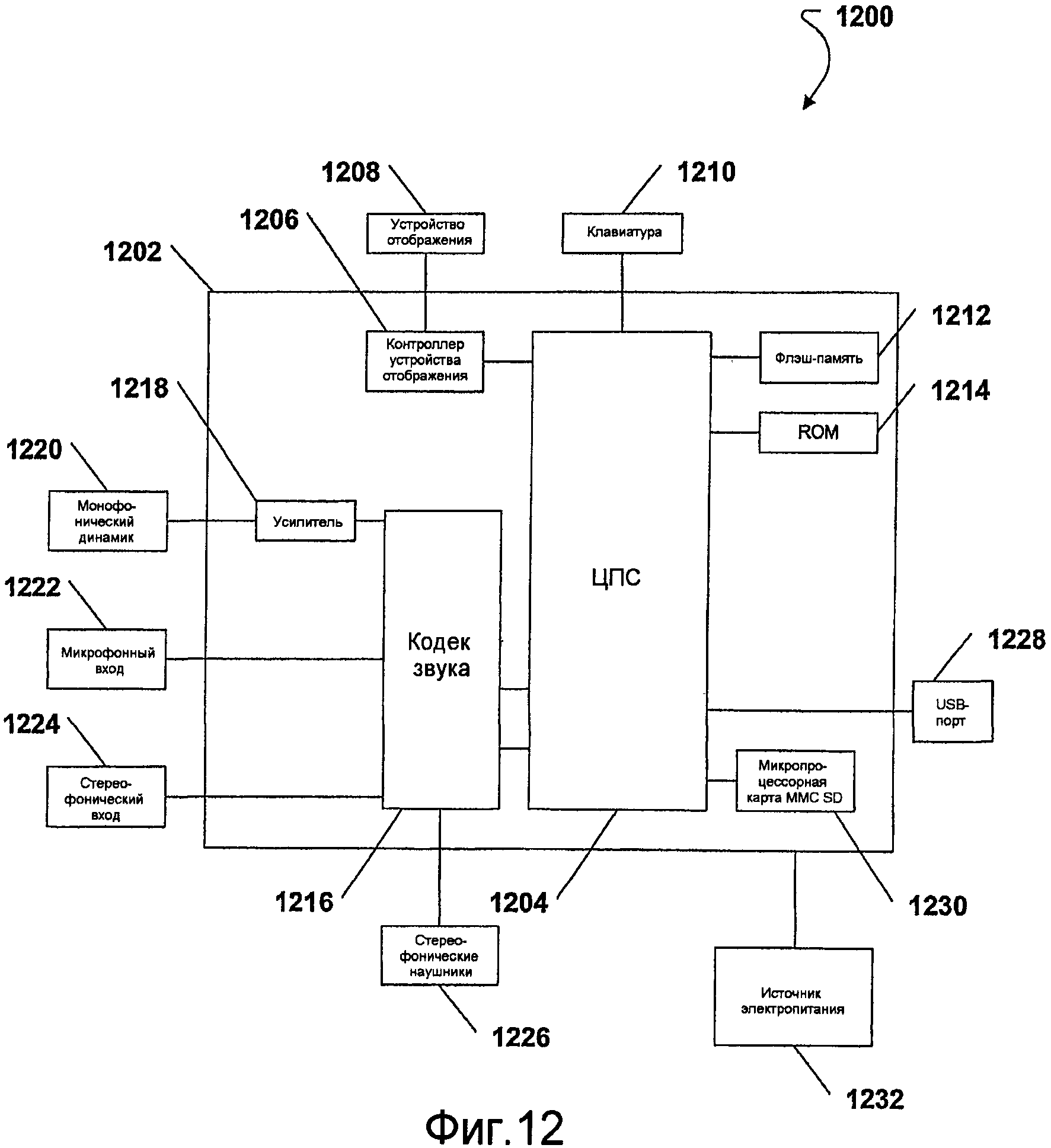

Фиг.12 - общая схема примерного устройства воспроизведения аудиофайла, включающего в себя цифровой процессор сигналов.

ПОДРОБНОЕ ОПИСАНИЕ

На Фиг.1 иллюстрируется блок-схема примерного, неограничительного варианта осуществления цифрового процессора 100 сигналов (ЦПС, DSP). Как проиллюстрировано на Фиг.1, DSP 100 включает в себя запоминающее устройство 102, которое является связанным с контроллером 104 последовательности (исполнения команд) через первую шину 106. Как используется в документе, термин «связанный» может обозначать, что два или несколько компонентов являются компонентами с непосредственной связью или с косвенной связью. В конкретном варианте осуществления первая шина 106 является шестидесятичетырехразрядной (64) шиной, и контроллер 104 последовательности выполнен с возможностью извлекать из запоминающего устройства 102 команды, имеющие размер тридцать два (32) бита или шестьдесят четыре (64) бита. Первая шина 106 является связанной с первым устройством 108 исполнения команд, вторым устройством 110 исполнения команд, третьим устройством 112 исполнения команд и четвертым устройством 114 исполнения команд. На Фиг.1 показано, что каждое устройство 108, 110, 112, 114 исполнения команд может быть связано с общим блоком 116 регистров через вторую шину 118. Общий блок 116 регистров также может быть связан с контроллером 104 последовательности и запоминающим устройством 102 через третью шину 120.

В конкретном варианте осуществления запоминающее устройство 102 включает в себя первый кэш 122 команд, второй кэш 124 команд, третий кэш 126 команд, четвертый кэш 128 команд, пятый кэш 130 команд и шестой кэш 132 команд. Во время работы к кэшам 122, 124, 126, 128, 130, 132 команд можно осуществлять доступ независимо друг от друга посредством контроллера 104 последовательности. Кроме того, в конкретном варианте осуществления каждый кэш 122, 124, 126, 128, 130, 132 команд включает в себя множество команд.

Как проиллюстрировано на Фиг.1, запоминающее устройство 102 может включать в себя очередь 134 команд, которая включает в себя очереди команд для каждого кэша 122, 124, 126, 128, 130, 132 команд. В частности, очередь 134 команд включает в себя первую очередь 136 команд, которая соотнесена (ассоциирована) с первым кэшем 122 команд, вторую очередь 138 команд, которая соотнесена со вторым кэшем 124 команд, третью очередь команд 140, которая соотнесена с третьим кэшем 126 команд, четвертую очередь команд 142, которая соотнесена с четвертым кэшем 128 команд, пятую очередь команд 144, которая соотнесена с пятым кэшем 130 команд, и шестую очередь команд 146, которая соотнесена с шестым кэшем 132 команд.

Во время работы контроллер 104 последовательности может осуществлять выборку команд из каждого кэша 122, 124, 126, 128, 130, 132 команд через очередь 134 команд. В конкретном варианте осуществления контроллер 104 последовательности выбирает команды из очередей 136, 138, 140, 142, 144, 146 команд в порядке от первой очереди 136 команд к шестой очереди команд 146. После выборки команды из шестой очереди команд 146 контроллер 104 последовательности возвращается на первую очередь 136 команд и продолжает выборку команд из очередей 136, 138, 140, 142, 144, 146 команд по порядку.

В конкретном варианте осуществления контроллер 104 последовательности в первом режиме действует в качестве 2-канального суперскалярного контроллера последовательности, который поддерживает суперскалярные команды. Кроме того, в конкретном варианте осуществления контроллер последовательности действует также во втором режиме, который поддерживает команды с командными словами (СБКС, VLIW) сверхбольшой длины. В частности, контроллер последовательности может действовать в качестве 4-канального VLIW-контроллера последовательности. В конкретном варианте осуществления первое устройство 108 исполнения команд может исполнять команду загрузки, команду сохранения и команду арифметико-логического устройства (АЛУ, ALU). Второе устройство 110 исполнения команд может исполнять команду загрузки и команду ALU. К тому же, третье устройство исполнения команд может исполнять команду умножения, команду (MAC) умножения с накоплением, команду ALU, конструкцию переадресации в программе и команду передачи управления по содержимому регистра (CR). На Фиг.1 дополнительно показано, что четвертое устройство 114 исполнения команд может исполнять команду сдвига (S), команду ALU, конструкцию переадресации в программе и команду CR. На Фиг.2 подробно показаны компоненты, которые могут быть включены в состав четвертого блока 114 исполнения команд. В конкретном варианте осуществления конструкцией переадресации в программе могут быть цикл с контролем завершения по нулю (ZOL), команда ветвления, команда перехода (J) и т.д.

Как изображено на Фиг.1, общий регистр 116 включает в себя первый унифицированный блок регистров 148, второй унифицированный блок регистров 150, третий унифицированный блок регистров 152, четвертый унифицированный блок регистров 154, пятый унифицированный блок регистров 156 и шестой унифицированный блок регистров 158. Каждый унифицированный блок регистров 148, 150, 152, 154, 156, 158 соответствует кэшам 122, 124, 126, 128, 130, 132 команд в составе запоминающего устройства 102. Кроме того, в конкретном варианте осуществления каждый унифицированный блок регистров 148, 150, 152, 154, 156, 158 имеет одинаковую структуру и включает в себя ряд операндов-данных и ряд адресных операндов.

Во время работы цифрового процессора 100 сигналов команды могут выбираться из запоминающего устройства 102 посредством контроллера 104 последовательности, и операнды могут выбираться из унифицированных блоков 148, 150, 152, 154, 156, 158 регистров. Кроме того, команды и операнды могут быть посланы на намеченные устройства 108, 110, 112, 114 исполнения команд и исполнены в устройствах 108, 110, 112, 114 исполнения команд. Затем один или несколько операндов извлекаются из общего регистра 116, например, одного из унифицированных блоков 148, 150, 152, 154, 156, 158 регистров и используются во время исполнения команды. Результаты в каждом устройстве 108, 110, 112, 114 исполнения команд могут записываться в общий регистр 116, то есть в один из унифицированных регистровых файлов (блоков) 148, 150, 152, 154, 156, 158.

Что касается Фиг.2, на ней показан примерный, неограничительный вариант осуществления устройства исполнения команд и в целом обозначенного позицией 200. В конкретном варианте осуществления устройство 200 исполнения команд может быть включено в состав системы 100, показанной на Фиг.1. Например, устройство 200 исполнения команд может заменить четвертое устройство 114 исполнения команд, показанное на Фиг.1. Как изображено на Фиг.2, устройство 200 исполнения команд включает в себя расширитель 202 знака. Кроме того, как показано, инвертор 204 может быть связан с расширителем 202 знака. Также с инвертором 204 может быть связан счетный блок 206. В конкретном варианте осуществления счетный блок 206 включает в себя шестидесятичетырехразрядный счетчик.

На Фиг.2 также показано, что блок 208 управления может быть связан с расширителем 202 знака, инвертором 204 и счетным блоком 206. В конкретном варианте осуществления устройство 200 исполнения команд может принимать множество команд 210, например, шестидесятичетырехразрядные команды и тридцатидвухразрядные команды. Также в иллюстративном варианте осуществления команды 210 могут храниться в одной из очередей 136, 138, 140, 142, 144, 144, 146 команд (Фиг.1) и направляться на исполнительное устройство 200 через контроллер 104 последовательности (Фиг.1). Дополнительно устройство 200 исполнения команд может записывать в регистр 212 результат операции счета, выполненной счетным блоком 206. В конкретном варианте осуществления блок 208 управления может включать в себя логику, чтобы выполнять один или несколько этапов описанного в документе способа.

Что касается Фиг.3, на ней показан способ подсчета нулевых начальных разрядов для слова данных, и он начинается на этапе 300. На этапе 300 устройство исполнения команд принимает слово данных, которое имеет разрядность 2 в N-й степени. Затем на этапе 302 расширитель знака расширяет знак слова данных до временного слова данных, которое имеет разрядность 2 в М-й степени. В конкретном варианте осуществления N и М являются целыми числами. Кроме того, в конкретном варианте осуществления М больше N. Переходя на этап 304, расширитель знака вводит, или иначе передает, временное слово данных в (на) счетчик, который имеет разрядность 2 в М-й степени. На этапе 306 счетчик выполняет подсчет нулевых начальных разрядов во временном слове данных.

Переходя на этап 308 принятия решения, контроллер определяет, является ли нулевым результат счетчика. Если это так, способ продолжается на этапе 310, и контроллер устанавливает значение счета равным нулю. Затем на этапе 312 блок управления записывает значение счета в регистр. Способ затем завершается на этапе 314. Возвращаясь к этапу 308 принятия решения, если значение счета не является нулевым, способ продолжается на этапе 316, и из результата вычитают значение, равное 2 в М-й степени минус 2 в N-й степени, чтобы получить значение счета. Переходя к этапу 312, блок управления записывает значение счета в регистр. Способ затем завершается в состоянии 314.

На Фиг.4 показан другой способ выполнения счета нулевых начальных разрядов для слова данных. Начиная на этапе 400, устройство исполнения команд принимает слово данных, которое имеет разрядность 2 в N-й степени. На этапе 402 расширитель знака расширяет знак слова данных до временного слова данных, которое имеет разрядность 2 в М-й степени. В конкретном варианте осуществления N и М являются целыми числами и М больше N. Переходя на этап 404, расширитель знака передает, или иначе вводит, временное слово данных на счетчик, который имеет разрядность 2 в М-й степени. На этапе 406 счетчик выполняет подсчет нулевых начальных разрядов во временном слове данных, чтобы получить результат, который включает в себя M+1 разрядов. В конкретном варианте осуществления младшим значащим битом в результате является нулевой (0) разряд, и старшим значащим битом в результате является разряд М. Дополнительно, разряд N находится между самым младшим значащим битом и самым старшим значащим битом. Продолжая на этапе 408, содержимое разряда М копируют в позицию разряда N. На этапе 410 содержимое разрядов от М до N+1 заменяют нулем. Затем на этапе 412 блок управления записывает модифицированный результат в регистр. Способ затем завершается на этапе 414.

На Фиг.5 иллюстрируется шестидесятичетырехразрядное слово 500 данных и тридцати-двух-разрядное слово 502 данных. В конкретном варианте осуществления шестидесятичетырехразрядное слово 500 данных может быть входным для счетного блока, например, счетного блока 206, описанного со ссылками на Фиг.2. Счетный блок 206 может подсчитать число (количество) нулевых начальных разрядов в шестидесятичетырехразрядном слове 500 данных. Дополнительно, если команда требует значения подсчета единичных начальных разрядов в шестидесятичетырехразрядном слове данных, то шестидесятичетырехразрядное слово данных инвертируют и посредством счетного блока подсчитывают результирующие нулевые начальные разряды инвертированного шестидесятичетырехразрядного слова данных.

В другом варианте осуществления, если команда требует значения числа нулевых начальных разрядов или единичных начальных разрядов для тридцатидвухразрядного слова данных, то тридцатидвухразрядное слово 502 данных может быть расширено знаком (за счет знака) на тридцать два разряда, чтобы создать расширенное за счет знака временное шестидесятичетырехразрядное слово 504 данных. Временное шестидесятичетырехразрядное слово 504 данных может быть входным для счетного блока, чтобы получать значение подсчета нулевых начальных разрядов или подсчета единичных начальных разрядов, как описано в настоящем документе.

На Фиг.6 иллюстрируется примерный неограничительный способ выполнения подсчета нулевых начальных разрядов и подсчета единичных начальных разрядов. Начиная с этапа 600, устройство исполнения команд принимает слово, соответствующее команде. На этапе 602 устройство исполнения команд, например блок управления в составе устройства исполнения команд, определяет, требуется ли согласно соответствующей команде подсчет числа нулевых начальных разрядов или числа единичных начальных разрядов в составе слова. Если подсчет числа нулевых начальных разрядов или единичных начальных разрядов не требуется, способ завершается в состоянии 604. С другой стороны, если требуется подсчет числа нулевых начальных разрядов или подсчет единичных начальных разрядов, способ переходит на этап 606 принятия решения.

На этапе 606 принятия решения блок управления определяет, имеет ли слово размерность тридцать два разряда или размерность шестьдесят четыре разряда. Если слово имеет размерность тридцать два разряда, способ продолжается на этапе 608, и расширитель знака расширяет за счет знака тридцатидвухразрядное слово данных, чтобы создать временное шестидесятичетырехразрядное слово данных. После этого способ переходит на этап 610 принятия решения. Возвращаясь к этапу 604 принятия решения, если слово имеет шестьдесят четыре разряда, способ продолжается непосредственно на этапе 610 принятия решения.

На этапе 610 принятия решения блок управления определяет, требуется ли подсчет числа нулевых начальных разрядов или подсчет числа единичных начальных разрядов для шестидесятичетырехразрядного слова данных или временного шестидесятичетырехразрядного слова данных. Если требуется счет числа единичных начальных разрядов, способ продолжается на этапе 612, и инвертор инвертирует шестидесятичетырехразрядное слово данных или временное шестидесятичетырехразрядное слово данных, чтобы создать инвертированное шестидесятичетырехразрядное слово данных или инвертированное временное шестидесятичетырехразрядное слово данных. Переходя на этап 614, инвертор передает инвертированное шестидесятичетырехразрядное слово данных или инвертированное временное шестидесятичетырехразрядное слово данных на счетный блок. На этапе 616 счетный блок выполняет подсчет нулевых начальных разрядов инвертированного шестидесятичетырехразрядного слова данных или инвертированного временного шестидесятичетырехразрядного слова данных, чтобы получить временный результат.

Возвращаясь к этапу принятия решения 610, если требуется подсчет числа нулевых начальных разрядов, способ продолжается на этапе 618, и блок управления передает шестидесятичетырехразрядное слово данных или временное шестидесятичетырехразрядное слово данных на счетный блок. После этого способ переходит на этап 616, и счетный блок выполняет подсчет нулевых начальных разрядов шестидесятичетырехразрядного слова данных или временного шестидесятичетырехразрядного слова данных, чтобы получить временный результат. От этапа 616 способ продолжается на этапе 620 принятия решения, и блок управления определяет, было ли шестидесятичетырехразрядное слово данных, которое является предметом счета, предварительно расширено за счет знака. Если не было, способ продолжается на этапе принятия решения 622, и блок управления определяет, является ли значение счета числом нулевых начальных разрядов или числом единичных начальных разрядов. Если значение счета является числом нулевых начальных разрядов, способ продолжается на этапе 624, и блок управления записывает значение подсчета нулевых начальных разрядов в регистр. Способ затем завершается на этапе 604. Напротив, на этапе 622 принятия решения, если значение счета является числом единичных начальных разрядов, способ продолжается на этапе 626, и блок управления записывает значение подсчета единичных начальных разрядов в регистр. Способ затем завершается на этапе 604.

Возвращаясь к этапу принятия решения 620, если шестидесятичетырехразрядное слово данных, которое является предметом счета, было предварительно расширено за счет знака, способ продолжается на этапе принятия решения 628. На этапе принятия решения 628 блок управления определяет, является ли результат счета нулем. Если это так, способ переходит на этап 622 принятия решения и продолжается, как описано в настоящем документе. С другой стороны, если результат не является нулем, способ продолжается на этапе 630, и постоянное значение тридцать два вычитают из временного результата, чтобы выдать окончательный результат. После этого способ продолжается на этапе 622 принятия решения и продолжается, как описано в настоящем документе.

Что касается Фиг.7, на ней показан подробно способ многопотоковой обработки с чередованием для цифрового процессора сигналов. На Фиг.7 показано, что способ включает в себя процедуру 700 обработки ветвления, процедуру 702 обработки загрузки, процедуру 704 обработки сохранения и процедуру 706 обработки s-pipe. Каждая процедура (программа) 700, 702, 704, 706 включает в себя множество этапов, которые выполняются в течение шести тактов для каждой команды, выбираемой контроллером последовательности из очереди команд. В конкретном варианте осуществления такты включают в себя такт 708 декодирования (дешифрирования), такт 710 доступа к блоку регистров, первый исполнительный такт 712, второй исполнительный такт 714, третий исполнительный такт 716 и такт 718 обратной записи. Кроме того, каждый такт включает в себя первую часть и вторую часть.

На Фиг.7 показано, что в течение процедуры 700 обработки ветвления на этапе 720 для команды выполняется быстрое декодирование в контроллере последовательности в течение первой части такта декодирования. На этапе 722 в течение второй части такта быстрого декодирования контроллер последовательности обращается к блоку регистров, например, начинает доступ к блоку регистров для первого операнда. Доступ к регистру для этапа 722 завершается в пределах такта 710 доступа к блоку регистров, и первый операнд извлекается из блока регистров. В конкретном варианте осуществления контроллер последовательности осуществляет доступ к блоку регистров через первый порт считывания данных. Как показано, доступ к блоку регистров на этапе 722 происходит в течение второй части такта 708 декодирования и первой части такта 710 доступа к блоку регистров. Как таковой, доступ к блоку регистров охватывает такт 708 декодирования и такт 710 доступа к блоку регистров.

На этапе 724, а также в течение такта 708 декодирования контроллер последовательности начинает для команды полное декодирование. Полное декодирование, выполняемое посредством контроллера последовательности, происходит в пределах второй части такта 708 декодирования и первой части такта 710 доступа к блоку регистров.

В течение такта 710 доступа к блоку регистров, на этапе 726 контроллер последовательности формирует виртуальный адрес (ВАК, IVA) команды. После этого на этапе 728 контроллер последовательности исполняет проверку страницы, чтобы определять физический адрес страницы, соответствующий номеру страницы виртуальной адресации. Переходя к первому такту 712 исполнения, на этапе 730 контроллер последовательности выполняет просмотр очереди команд. На этапе 732 контроллер последовательности обращается к кэшу команд первый раз и извлекает первое двойное слово для команды. В конкретном варианте осуществления каждая команда включает в себя три двойных слова, например, первое двойное слово, второе двойное слово и третье двойное слово. На этапе 734 в течение первого исполнительного такта 712 контроллер последовательности выравнивает двойное слово, поступающее из кэша команд.

Продолжая на втором исполнительном такте 714, контроллер последовательности обращается к кэшу команд второй раз, чтобы на этапе 736 извлечь для команды второе двойное слово. Затем на этапе 738 контроллер последовательности выравнивает двойное слово, извлеченное из кэша команд.

Приступая к третьему исполнительному такту 716, контроллер последовательности обращается к кэшу команд третий раз, чтобы на этапе 742 извлечь третье двойное слово. После того как контроллер последовательности обращается к кэшу команд третий раз, контроллер последовательности на этапе 744 выравнивает третье двойное слово.

Как проиллюстрировано на Фиг.7, в течение процедуры 702 обработки загрузки на этапе 750 контроллер последовательности исполняет для команды быстрое декодирование в течение первой части такта 708 декодирования. На этапе 752 в течение второй части такта 708 декодирования контроллер последовательности начинает доступ к блоку регистров. Как показано, второй доступ к регистру посредством контроллера последовательности занимает два такта, то есть включая вторую часть такта 708 декодирования и первую часть такта 710 доступа к блоку регистров. Как таковой, доступ к блоку регистров завершается в пределах такта 710 доступа к блоку регистров, и может извлекаться второй операнд. Затем в течение первого исполнительного такта 712, на этапе 754, блок формирования адреса в первом устройстве исполнения команд формирует для команды первый виртуальный адрес на основании предварительно считанного содержимого блока регистров.

На этапе 756 в течение второго исполнительного такта 714 буфер (БППД, DTLB) хранения предыстории (процесса) преобразования данных выполняет преобразование адреса для первого виртуального адреса, чтобы сформировать первый физический адрес. Еще в пределах второго исполнительного такта 714, на этапе 758, контроллер последовательности выполняет проверку тэга.

Переходя к третьему исполнительному такту 716, контроллер последовательности на этапе 760 осуществляет доступ к кэшу данных, поддерживаемому на статическом запоминающем устройстве (СЗУПВ, SRAM) с произвольной выборкой, чтобы считать данные из SRAM. Также в пределах третьего цикла исполнения на этапе 762 контроллер последовательности обновляет связанный с командой блок регистров, первый раз через первый порт записи данных. В конкретном варианте осуществления контроллер последовательности обновляет блок регистров результатами значения адреса с последующим приращением. Затем в течение такта 718 обратной записи на этапе 764 блок выравнивания загружаемого осуществляет сдвиг, чтобы выровнять данные внутри двойного слова. На этапе 766, также в пределах такта 718 обратной записи, контроллер последовательности обновляет блок регистров для команды загруженными из кэша данными, второй раз через первый порт записи данных.

На Фиг.7 показано, что в течение процедуры 704 обработки сохранения на этапе 768 контроллер последовательности выполняет для команды быстрое декодирование в течение такта 708 декодирования. Далее в течение такта 708 декодирования на этапе 770 контроллер последовательности осуществляет доступ к блоку регистров, соотнесенному с командой, третий раз через третий порт считывания данных. Доступ к регистру на этапе 770 происходит в пределах последней части такта 708 декодирования и первой части такта 710 доступа к блоку регистров. Как таковой, доступ к блоку регистров начинается в пределах такта 708 декодирования и завершается в пределах такта 710 доступа к блоку регистров. В конкретном варианте осуществления третий операнд извлекается из блока регистров в течение такта 710 доступа к блоку регистров.

Как изображено на Фиг.7, в течение второй части такта 710 доступа к блоку регистров контроллер последовательности на этапе 772 осуществляет доступ к блоку регистров для команды четвертый раз через третий порт считывания данных. Четвертый доступ к блоку регистров начинается в пределах такта 710 доступа к блоку регистров и завершается в пределах первого исполнительного такта 712, в котором четвертый операнд извлекается из регистра. В конкретном варианте осуществления используется третий порт считывания данных, чтобы осуществлять доступ к регистру для извлечения третьего операнда и четвертого операнда. На этапе 774 часть данных от контроллера последовательности мультиплексируется в мультиплексоре. Также в течение первого исполнительного такта 712, на этапе 776, второй блок формирования адреса во втором устройстве исполнения команд формирует для команды виртуальный адрес на основании предварительно считанных данных из блока регистров.

Приступая на этапе 778 ко второму исполнительному такту 714 в течение процедуры сохранения, буфер предыстории преобразования данных (DTLB) преобразует в физический адрес предварительно сформированный для команды виртуальный адрес. На этапе 780 во втором исполнительном такте 714 контроллер последовательности исполняет проверку тэга. Также в течение второго исполнительного такта 714, на этапе 782, блок выравнивания хранимого выравнивает хранимые данные к соответствующей границе байта, полуслова или слова внутри двойного слова перед записью данных в кэш данных. Переходя к третьему исполнительному такту 716, на этапе 784, контроллер последовательности обновляет кэш данных, поддерживаемый на статическом запоминающем устройство с произвольной выборкой. Затем на этапе 786 контроллер последовательности обновляет блок регистров для команды результатами исполнения команды в течение третьего исполнительного такта 716, третий раз через второй порт записи данных.

Как проиллюстрировано на Фиг.7, процедура s-pipe 706 начинается в течение такта 708 декодирования на этапе 788, где для команды выполняется быстрое декодирование. На этапе 790 контроллер последовательности осуществляет доступ к блоку регистров для команды пятый раз через четвертый порт считывания данных. Пятый доступ к блоку регистров также занимает два такта, начинается в пределах второй части такта 708 декодирования и завершается в пределах первой части такта 710 доступа к блоку регистров, в котором извлекается пятый операнд. Еще в течение такта 710 доступа к блоку регистров часть данных из блока регистров для команды мультиплексируется в мультиплексоре. Также в течение такта 710 доступа к блоку регистров контроллер последовательности на этапе 794 осуществляет доступ к блоку регистров для команды шестой раз через четвертый порт считывания данных. Шестой доступ к блоку регистров начинается в пределах второй части такта 710 доступа к блоку регистров и завершается в пределах первой части первого исполнительного такта 712. Шестой операнд извлекается в течение первого исполнительного такта 712.

Приступая ко второму исполнительному такту 714, на этапе 796, данные, извлеченные в течение пятого доступа к блоку регистров и шестого доступа к блоку регистров, посылают на 64-разрядный сдвиговый регистр, блок обработки векторов и расширитель знака/нуля. Также в течение первого исполнительного такта на этапе 798 мультиплексируются данные из сдвигового регистра, блока обработки векторов и расширителя знака/нуля.

Переходя на второй исполнительный такт 714, мультиплексированные данные из сдвигового регистра, блока обработки векторов и расширителя знака/нуля на этапе 800 посылают на арифметико-логическое устройство, блок счета нулевых начальных разрядов или компаратор. На этапе 802 данные от арифметико-логического устройства, блока счета нулевых начальных разрядов и компаратора мультиплексируют в одном мультиплексоре. После того как данные мультиплексированы, сдвиговый регистр осуществляет сдвиг мультиплексированных данных, чтобы умножать данные на 2, 4, 8 и т.д. на этапе 804 в течение третьего исполнительного такта 716. Затем на этапе 806 насыщают выходные данные сдвигового регистра. В течение такта обратной записи 718, на этапе 808, блок регистров для команды обновляется четвертый раз через третий порт записи данных.

В конкретном варианте осуществления, как проиллюстрировано на Фиг.7, способ организации многопотоковой обработки с чередованием для цифрового процессора сигналов использует четыре порта считывания для каждого регистра и три порта записи для каждого регистра. Вследствие повторного использования портов считывания и портов записи могут извлекаться шесть операндов через четыре порта данных считывания. Дополнительно могут быть обновлены четыре результата в блок регистров через три порта записи данных.

На Фиг.8 иллюстрируется примерный неограничительный вариант осуществления портативного устройства связи, которое в целом обозначено (позицией) 820. Как проиллюстрировано на Фиг.8, портативное устройство связи включает в себя внутрикристальную (встроенную в кристалл) систему 822, которая включает в себя цифровой процессор 824 сигналов. В конкретном варианте осуществления цифровым процессором 824 сигналов является цифровой процессор сигналов, показанный на Фиг.1 и описанный в настоящем документе. На Фиг.8 также показан контроллер 826 устройства отображения, который связан с цифровым процессором 824 сигналов и устройством 828 отображения. Кроме того, с цифровым процессором 824 сигналов связано устройство 830 ввода. Как показано, запоминающее устройство 832 связано с цифровым процессором 824 сигналов. Дополнительно кодер/декодер (кодек) 834 может быть связан с цифровым процессором 824 сигналов. С кодеком 834 могут быть связаны динамик 836 и микрофон 838.

На Фиг.8 также изображено, что контроллер 840 беспроводной связи может быть связан с цифровым процессором 824 сигналов и антенной 842 беспроводной связи. В конкретном варианте осуществления источник 844 электропитания связан с внутрикристальной системой 822. Кроме того, в конкретном варианте осуществления, как проиллюстрировано на Фиг.8, устройство 828 отображения, устройство 830 ввода, динамик 836, микрофон 838, антенна 842 беспроводной связи и источник 844 электропитания являются внешними по отношению к внутрикристальной системе 822. Однако каждый связан с компонентом внутрикристальной системы 822.

В конкретном варианте осуществления цифровой процессор 824 сигналов использует организацию многопоточной обработки с чередованием, чтобы обрабатывать команды, связанные с потоками программы, необходимыми для выполнения функциональных возможностей и операций, требуемых различными компонентами портативного устройства 820 связи. Например, когда сеанс беспроводной связи установлен через антенну беспроводной связи, пользователь может говорить в микрофон 838. Электронные сигналы, представляющие речь пользователя, могут посылаться на кодек 834 для кодирования. Цифровой процессор 824 сигналов может выполнять обработку данных для кодека 834, чтобы кодировать электронные сигналы от микрофона. Дополнительно поступающие сигналы, принятые через антенну 842 беспроводной связи, посредством беспроводного контроллера 840 могут посылаться на кодек 834 для декодирования и посылки на динамик 836. Цифровой процессор 824 сигналов может также исполнять обработку данных для кодека 834 при декодировании сигнала, принятого через антенну 842 беспроводной связи.

Кроме того, прежде в течение или после сеанса беспроводной связи цифровой процессор 824 сигналов может обрабатывать входные данные, которые приняты от устройства ввода 830. Например, в течение сеанса беспроводной связи пользователь может использовать устройство 830 ввода и устройство 828 отображения, чтобы переходить по сайтам в Интернет посредством web-браузера, который встроен в запоминающее устройство 832 портативного устройства 820 связи. Цифровой процессор 824 сигналов может чередовать различные потоки программ, которые используются устройством ввода данных 830, контроллером устройства отображения 826, устройством отображения 828, кодеком 834 и контроллером 840 беспроводной связи, как описано в документе, чтобы эффективно управлять работой портативного устройства 820 связи и различных компонентов в нем. Многие из команд, связанных с различными потоками программ, выполняются одновременно в течение одного или нескольких тактов. Как таковое, потребление мощности и энергии из-за неиспользуемых тактов значительно снижается.

Что касается Фиг.9, на ней показан примерный неограничительный вариант осуществления телефона сотовой связи, обозначенного в целом позицией 920. Как показано, телефон 920 сотовой связи включает в себя внутрикристальную систему 922, которая включает в себя связанные вместе процессор 924 цифровой немодулированной передачи и процессор 926 аналоговой немодулированной передачи. В конкретном варианте осуществления процессор 924 цифровой немодулированной передачи является цифровым процессором сигналов, например, цифровым процессором сигналов, показанным на Фиг.1 и описанным в документе. Дополнительно в конкретном варианте осуществления процессором 926 аналоговой немодулированной передачи также может быть цифровой процессор сигналов, например, цифровой процессор сигналов, показанный на Фиг.1. Как проиллюстрировано на Фиг.9, контроллер 928 устройства отображения и контроллер 930 сенсорного экрана связаны с процессором 924 цифровой немодулированной передачи. В свою очередь устройство отображения 932 с сенсорным экраном, являющееся внешним по отношению к внутрикристальной системе 922, связано с контроллером 928 устройства отображения и контроллером 930 сенсорного экрана.

На Фиг.9, кроме того, указано, что кодер 934 видео, например кодер, поддерживающий построчное изменение фазы (PAL), кодер, поддерживающий последовательное воспроизведение цветов с их запоминанием (SECAM), или кодер, поддерживающий стандарт Национального комитета по телевизионным системам (NTSC), связаны с процессором 924 цифровой немодулированной передачи. Дополнительно усилитель 936 видеосигнала связан с кодером 934 видеосигнала и устройством 932 отображения с сенсорным экраном. Также порт 938 видеосигнала связан с усилителем 936 видеосигнала. Как изображено на Фиг.9, контроллер 940 универсальной последовательной шины (УПШ, USB) связан с процессором 924 цифровой немодулированной передачи. Также USB-порт 942 связан с контроллером 940 USB. Запоминающее устройство 944 и карта модуля 946 идентификации абонента (МИА, SIM) также могут быть связаны с процессором 924 цифровой немодулированной передачи. Далее, как показано на Фиг.9, цифровая камера 948 может быть связана с процессором 924 цифровой немодулированной передачи. В примерном варианте осуществления цифровая камера 948 является камерой на приборе с зарядовой связью (ПЗС-камерой, CCD) или камерой на комплементарных структурах металл-оксид-полупроводник (КМОП, CMOS).

Как дополнительно проиллюстрировано на Фиг.9, стереофонический кодек 950 аудио может быть связан с процессором 926 аналоговой немодулированной передачи. Кроме того, усилитель 952 звука может быть связан со стереофоническим кодеком 950 аудио. В примерном варианте осуществления первый стереофонический динамик 954 и второй стереофонический динамик 956 связаны с усилителем 952 звука. На Фиг.9 показано, что микрофонный усилитель 958 также может быть связан со стереофоническим кодеком 950 аудио. Кроме того, микрофон 960 может быть связан с микрофонным усилителем 958. В конкретном варианте осуществления блок 962 настройки (тюнер) частотно-модулированного (ЧМ, FM) радиовещания может быть связан со стереофоническим кодеком 950 аудио. Также FM-антенна 964 связана с блоком 962 настройки FM-приемника. Кроме того, стереонаушники 966 могут быть связаны со стереофоническим кодеком 950 аудио.

На Фиг.9 дополнительно указано, что приемопередатчик 968 диапазона радиочастот (РЧ, RF) может быть связан с процессором 926 аналоговой немодулированной передачи. Переключатель 970 может быть связан с RF-приемопередатчиком 968 и RF-антенной 972. Как показано на Фиг.9, вспомогательная клавиатура 974 может быть связана с процессором 926 аналоговой немодулированной передачи. Также монофонические наушники 976 с микрофоном могут быть связаны с процессором 926 аналоговой немодулированной передачи. Кроме того, вибраторное устройство 978 может быть связано с процессором 926 аналоговой немодулированной передачи. На Фиг.9 также показано, что источник 980 электропитания может быть связан с внутрикристальной системой 922. В конкретном варианте осуществления источником 980 электропитания является источник электропитания постоянного тока (ПТ, DC), который подает электропитание на различные требующие энергии компоненты телефона 920 сотовой связи. Дополнительно в конкретном варианте осуществления источник электропитания является перезаряжаемым. DC-аккумулятор или DC-источник электропитания, которое получают от преобразователя переменного тока (ПТ, AC) в постоянный ток, соединенного с AC-источником питания.

В конкретном варианте осуществления, как изображено на Фиг.9, устройство 932 отображения с сенсорным экраном, порт 938 видеосигнала, USB-порт 942, камера 948, первый стереофонический динамик 954, второй стереофонический динамик 956, микрофон 960, FM-антенна 964, стереонаушники 966, RF-переключатель 970, RF-антенна 972, вспомогательная клавиатура 974, монофонические наушники 976, вибратор 978 и источник электропитания 980 являются внешними по отношению к внутрикристальной системе 922. Кроме того, в конкретном варианте осуществления процессор 924 цифровой немодулированной передачи и процессор аналоговой немодулированной передачи могут использовать описанную в документе многопотоковую обработку с чередованием, чтобы обрабатывать различные потоки программ, связанные с одним или несколькими различными компонентами, относящимися к сотовому телефону 920.

Что относится к Фиг.10, на ней показан примерный, неограничительный вариант осуществления поддерживающего Интернет-протокол (IP) беспроводного телефона и обозначенного в целом позицией 1000. Как показано, беспроводный IP-телефон 1000 включает в себя внутрикристальную систему 1002, которая включает в себя цифровой процессор (DSP) 1004 сигналов. В конкретном варианте осуществления DSP 1004 является цифровым процессором сигналов, показанным на Фиг.1 и описанным в документе. Как проиллюстрировано на Фиг.10, контроллер 1006 устройства отображения связан с DSP 1004, и устройство 1008 отображения связано с контроллером 1006 устройства отображения. В примерном варианте осуществления устройством 1008 отображения является жидкокристаллический дисплей (ЖКД, LCD). На Фиг.10 дополнительно показана вспомогательная клавиатура 1010, которая может быть связана с DSP 1004.

Как дополнительно изображено на Фиг.10, с DSP 1004 может быть связана флэш-память 1012. Синхронное динамическое запоминающее устройство (СДОЗУ, SDRAM) с произвольной выборкой 1014, статическое запоминающее устройство (SRAM) 1016 с произвольной выборкой и электрически стираемое программируемое постоянное запоминающее устройство (ЭСППЗУ, EEPROM) 1018 также могут быть связаны с DSP 1004. На Фиг.10 также показано, что с DSP 1004 может быть связан светоизлучающий диод (СИД, LED) 1020. Кроме того, в конкретном варианте осуществления с DSP 1004 может быть связан кодек 1022 речи. С кодеком 1022 речи может быть связан усилитель 1024, и с усилителем 1024 может быть связан монофонический динамик 1026. На Фиг.10 дополнительно указано, что монофонические наушники 1028 также могут быть связаны с кодеком 1022 речи. В конкретном варианте осуществления монофонические наушники 1028 включают в состав микрофон.

На Фиг.10 также иллюстрируется, что процессор 1030 немодулированной передачи в беспроводной локальной сети (БЛВС, WLAN) может быть связан с DSP 1004. RF-приемопередатчик 1032 может быть связан с процессором 1030 немодулированной передачи в составе WLAN, и RF-антенна 1034 может быть связана с RF-приемопередатчиком 1032. В конкретном варианте осуществления поддерживающий технологию Bluetooth контроллер 1036 также может быть связан с DSP 1004, и поддерживающая технологию Bluetooth антенна 1038 может быть связана с контроллером 1036. На Фиг.10 также показано, что USB-порт 1040 также может быть связан с DSP 1004. Кроме того, источник 1042 электропитания связан с внутрикристальной системой 1002 и подает электропитание на различные компоненты беспроводного IP-телефона 1000 через внутрикристальную систему 1002.

В конкретном варианте осуществления, как указано на Фиг.10, устройство 1008 отображения, вспомогательная клавиатура 1010, LED 1020, монофонический динамик 1026, монофонические наушники 1028, RF-антенна 1034, Bluetooth-антенна 1038, USB-порт 1040 и источник 1042 электропитания являются внешними по отношению к внутрикристальной системе 1002. Однако каждый из этих компонентов связан с одним или несколькими компонентами внутрикристальной системы. Кроме того, в конкретном варианте осуществления цифровой процессор 1004 сигналов может использовать многопотоковую обработку с чередованием, как описано в настоящем документе, чтобы обрабатывать различные потоки программ, связанные с одним или несколькими различными компонентами, относящимися к IP-телефону 1000.

На Фиг.11 иллюстрируется примерный неограничительный вариант осуществления портативного цифрового ассистента (PDA), обозначенного в целом позицией 1100. Как показано, PDA 1100 включает в себя внутрикристальную систему 1102, которая включает в себя цифровой процессор 1104 сигналов (DSP). В конкретном варианте осуществления DSP 1104 является цифровым процессором сигналов, показанным на Фиг.1 и описанным в настоящем документе. Как изображено на Фиг.11, контроллер 1106 сенсорного экрана и контроллер 1108 устройства отображения связаны с DSP 1104. Кроме того, устройство отображения с сенсорным экраном связано с контроллером 1106 сенсорного экрана и контроллером 1108 устройства отображения. На Фиг.11 также указано, что с DSP 1104 может быть связана вспомогательная клавиатура 1112.

Как дополнительно изображено на Фиг.11, флэш-память 1114 может быть связана с DSP 1104. Также постоянное запоминающее устройство (ПЗУ, ROM) 1116, динамическое запоминающее устройство с произвольной выборкой (DRAM) 1118 и электрически стираемое программируемое постоянное запоминающее устройство (ЭСППЗУ, EEPROM) 1120 могут быть связаны с DSP 1104. На Фиг.11 также показано, что порт 1122 стандарта Ассоциации по средствам передачи данных в инфракрасном диапазоне (IrDA) может быть связан с DSP 1104. Кроме того, в конкретном варианте осуществления с DSP 1104 может быть связана цифровая камера 1124.

Как показано на Фиг.11, в конкретном варианте осуществления с DSP 1104 может быть связан стереофонический кодек 1126 аудио. Первый стереоусилитель 1128 может быть связан со стереофоническим кодеком 1126 аудио, и первый стереофонический динамик 1130 может быть связан с первым стереоусилителем 1128. Дополнительно, микрофонный усилитель 1132 может быть связан со стереофоническим кодеком 1126 аудио, и микрофон 1134 может быть связан с микрофонным усилителем 1132. На Фиг.11, кроме того, показано, что второй стереоусилитель 1136 может быть связан со стереофоническим кодеком 1126 аудио и второй стереофонический динамик 1138 может быть связан со вторым стереоусилителем 1136. В конкретном варианте осуществления стереонаушники 1140 также могут быть связаны со стереофоническим кодеком 1126 аудио.

На Фиг.11 также иллюстрируется, что поддерживающий стандарт 802.11 контроллер 1142 может быть связан с DSP 1104 и поддерживающая стандарт 802.11 антенна 1144 может быть связана с поддерживающим стандарт 802.11 контроллером 1142. Кроме того, поддерживающий технологию Bluetooth контроллер 1146 может быть связан с DSP 1104, и Bluetooth-антенна 1148 может быть связана с Bluetooth-контроллером 1146. Как изображено на Фиг.11, контроллер 1150 USB может быть связан с DSP 1104, и USB-порт 1152 может быть связан с контроллером 1150 USB. Дополнительно, микропроцессорная карта 1154, например, мультимедийная карта (ММК, MMC) или защищенная цифровая карта (формата Secure Digital, SD) может быть связана с DSP 1104. Кроме того, как показано на Фиг.11, источник 1156 электропитания может быть связан с внутрикристальной системой 1102 и может подавать электропитание на различные компоненты PDA 1100 через внутрикристальную систему 1102.

Как указано на Фиг.11, в конкретном варианте осуществления устройство 1110 отображения, вспомогательная клавиатура 1112, порт 1122 IrDA, цифровая камера 1124, первый стереофонический динамик 1130, микрофон 1134, второй стереофонический динамик 1138, стереонаушники 1140, антенна 1144 по стандарту 802.11, Bluetooth-антенна 1148, USB-порт 1152, и источник 1150 электропитания являются внешними по отношению к внутрикристальной системе 1102. Однако каждый из этих компонентов связан с одним или несколькими компонентами во внутрикристальной системе. Дополнительно, в конкретном варианте осуществления цифровой процессор 1104 сигналов может использовать описанную в документе многопотоковую обработку с чередованием, чтобы обрабатывать различные потоки программ, связанные с одним или несколькими различными компонентами, относящимися к портативному цифровому ассистенту 1100.

Что касается Фиг.12, на ней показан примерный неограничительный вариант осуществления устройства воспроизведения аудиофайла, такого как устройство воспроизведения формата уровня 3 (MP3) Экспертной группы по вопросам движущегося изображения, которое обозначено в целом позицией 1200. Как показано, устройство 1200 воспроизведения аудиофайла включает в себя внутрикристальную систему 1202, которая включает в себя цифровой процессор сигналов (DSP) 1204. В конкретном варианте осуществления DSP 1204 является цифровым процессором сигналов, показанным на Фиг.1 и описанным в документе. Как проиллюстрировано на Фиг.12, контроллер 1206 устройства отображения связан с DSP 1204, и устройство 1208 отображения связано с контроллером 1206 устройства отображения. В примерном варианте осуществления устройством 1208 отображения является жидкокристаллический дисплей (LCD). На Фиг.12 дополнительно показано, что с DSP 1204 может быть связана вспомогательная клавиатура 1210.

Как дополнительно изображено на Фиг.12, с DSP 1204 могут быть связаны флэш-память 1212 и постоянное запоминающее устройство (ROM) 1214. Дополнительно, в конкретном варианте осуществления с DSP 1204 может быть связан кодек 1216 аудио. С кодеком 1216 может быть связан усилитель 1218 звука, и с усилителем 1218 может быть связан монофонический динамик 1220. На Фиг.12 дополнительно указано, что вход 1222 микрофона и вход 1224 стереовещания также могут быть связаны с кодеком 1216 аудио. В конкретном варианте осуществления стереонаушники 1226 также могут быть связаны с кодеком 1216 аудио.

На Фиг.12 также указано, что с DSP 1204 могут быть связаны порт 1228 USB и микропроцессорная карта 1230. Дополнительно, источник 1232 электропитания может быть связан с внутрикристальной системой 1202 и может подавать электропитание на различные компоненты устройства 1200 воспроизведения аудиофайла через внутрикристальную систему 1202.

В конкретном варианте осуществления, как обозначено на Фиг.12, устройство 1208 отображения, вспомогательная клавиатура 1210, монофонический динамик 1220, вход 1222 микрофона, вход 1224 стереовещания, стереофонические наушники 1226, USB-порт 1228 и источник электропитания 1232 являются внешними по отношению к внутрикристальной системе 1202. Однако каждый из этих компонентов связан с одним или несколькими компонентами во внутрикристальной системе. Также в конкретном варианте осуществления цифровой процессор сигналов 1204 может использовать описанную в настоящем документе многопотоковую обработку режим с чередованием, чтобы обрабатывать различные потоки программ, относящиеся к одному или нескольким различным компонентам, относящимся к устройству 1200 воспроизведения аудиофайла.

С помощью раскрытой в документе конфигурации устройства описанные в документе система и способ обеспечивают способ выполнения счета нулевых начальных разрядов и счета единичных начальных разрядов в шестидесяти-четырех-разрядных словах данных и тридцати-двух-разрядных словах данных с использованием одних и тех же аппаратных средств в рамках цифрового процессора сигналов. Как таковая устраняется необходимость различных наборов аппаратных средств для выполнения счета нулевых начальных разрядов и единичных начальных разрядов в словах данных различного размера.

Специалисты в данной области техники дополнительно оценят, что различные иллюстративные логические блоки, конфигурации, модули, схемы и этапы алгоритмов, описанные в связи с раскрытыми в документе вариантами осуществления, могут быть реализованы в виде электронных аппаратных средств, программного обеспечения или их комбинации. Чтобы явно проиллюстрировать эту взаимозаменяемость аппаратных средств и программного обеспечения, различные иллюстративные компоненты, блоки, конфигурации, модули, схемы и этапы были описаны выше обобщенно в терминах их функциональных возможностей. Осуществлены ли такие функциональные возможности в виде аппаратного средства или программного обеспечения, зависит от конкретного применения и проектных ограничений, наложенных на полную систему. Специалисты в данной области техники могут реализовывать описанные функциональные возможности различными способами для каждого конкретного применения, но такие решения по реализации не следует интерпретировать в качестве выходящих за рамки объема настоящего раскрытия.

Этапы способа или алгоритм, описанный в связи с раскрытыми в документе вариантами осуществления, могут быть реализованы непосредственно в виде аппаратных средств, в виде исполняемого процессором программного модуля или в виде комбинации обоих. Программный модуль может постоянно находиться в оперативном запоминающем устройстве (RAM), флэш-памяти, постоянном запоминающем устройстве (ROM), программируемом постоянном запоминающем устройстве (ППЗУ, PROM), стираемом программируемом постоянном запоминающем устройстве (EPROM), электрически стираемом программируемом постоянном запоминающем устройстве (ЭСППЗУ, EEPROM), регистрах, накопителе на жестком диске, на съемном диске, предназначенном только для чтения компакт-диске (CD-ROM), или любой другой форме носителя данных, известного в области техники. Иллюстративный носитель данных связан с процессором, так что процессор может считывать информацию с носителя данных и записывать информацию на него. В качестве альтернативы носитель данных может быть встроенным в процессор. Процессор и носитель данных могут быть резидентными в проблемно-ориентированной интегральной микросхеме (ПОИМ, ASIC). ASIC может постоянно находиться в вычислительном устройстве или пользовательском терминале. В качестве альтернативы, процессор и носитель данных могут постоянно находиться в качестве дискретных компонентов в вычислительном устройстве или пользовательском терминале. Предшествующее описание раскрытых вариантов осуществления представлено, чтобы дать возможность любому специалисту в области техники создавать или использовать настоящее раскрытие. Различные модификации этих вариантов осуществления будут без труда очевидными специалистам в данной области техники, и определенные в документе общие принципы могут применяться к другим вариантам осуществления без выхода за рамки существа или объема раскрытия. Таким образом, настоящее раскрытие не подразумевает ограничения вариантами осуществления, показанными в документе, а должно толковаться расширительно, в соответствии с принципами и признаками новизны, как определено согласно нижеследующей формуле изобретения.

Реферат

Изобретения относятся к цифровым процессорам сигналов и компонентам внутренней части цифровых процессоров сигналов, которые выполняют подсчет нулевых начальных разрядов или подсчет единичных начальных разрядов в словах данных. Техническим результатом является расширение функциональных возможностей устройств за счет выполнения подсчета нулевых или единичных начальных разрядов для различных размеров слов данных, а также сокращение аппаратных средств, необходимых для подсчета нулевых или единичных начальных разрядов. Способ обработки слова данных, содержащий этапы, на которых принимают слово данных, определяют, имеет ли слово данных первую разрядность или вторую разрядность, причем вторая разрядность больше, чем первая разрядность, после определения, что слово данных имеет первую разрядность, осуществляют расширение за счет знака слова данных для создания слова данных, имеющего вторую разрядность, и вычитают значение из промежуточного значения подсчета начальных бит данных слова данных, имеющего вторую разрядность, для определения окончательного значения подсчета начальных бит данных. 9 н. и 30 н.п. ф-лы, 12 ил.

Формула

принимают слово данных;

определяют, имеет ли слово данных первую разрядность или вторую разрядность, причем вторая разрядность больше, чем первая разрядность;

после определения, что слово данных имеет первую разрядность, осуществляют расширение за счет знака слова данных для создания слова данных, имеющего вторую разрядность; и вычитают значение из промежуточного значения подсчета начальных бит данных слова данных, имеющего вторую разрядность, для определения окончательного значения подсчета начальных бит данных.

инвертируют слово данных, имеющее вторую разрядность, для создания инвертированного слова данных, когда должно использоваться значение единичных начальных разрядов; и

передают инвертированное слово данных на шестидесяти четырех разрядный счетчик битов.

используют шестидесяти четырех разрядный логический счетчик для осуществления подсчета нуля или более нулевых начальных разрядов в тридцати двух разрядном слове данных;

осуществляют расширение за счет знака тридцати двух разрядного слова данных для создания шестидесяти четырех разрядного слова данных;

осуществляют подсчет нулевых начальных разрядов в шестидесяти четырех разрядном слове данных для получения промежуточного результата и

вычитают постоянное значение из промежуточного результата, если значение подсчета нулевых начальных значений не равно нулю, для получения окончательного результата.

принимают второе тридцати двух разрядное слово данных;

осуществляют расширение за счет знака второго тридцати двух разрядного слова данных для создания второго шестидесяти четырех разрядного слова данных и

инвертируют второе шестидесяти четырех разрядное слово данных для формирования инвертированного шестидесяти четырех разрядного слова данных.

блок управления;

расширитель знака, соединенный с блоком управления;

по меньшей мере, один инвертор, соединенный с блоком управления; и

шестидесяти четырех разрядный счетчик битов, соединенный с блоком управления, при этом блок управления включает в себя:

логику для инструктирования шестидесяти четырех разрядного счетчика битов осуществлять подсчет нулевых начальных разрядов в одном или более тридцати двух разрядных словах данных, принятых на устройстве исполнения команд;

логику для инструктирования шестидесяти четырех разрядного счетчика битов осуществлять подсчет нулевых начальных разрядов в одном или более шестидесяти четырех разрядных словах данных, принятых на устройстве исполнения команд;

логику для управления расширителем знака с целью расширения за счет знака одного или более тридцати двух разрядных слов данных для создания временного шестидесяти четырех разрядного слова данных;

логику для инструктирования шестидесяти четырех разрядного счетчика битов осуществлять подсчет нулевых начальных разрядов во временном шестидесяти четырех разрядном слове данных с целью получения промежуточного значения подсчета нулевых начальных разрядов;

логику для вычитания постоянного значения из промежуточного значения подсчета нулевых начальных разрядов, если промежуточное значение подсчета нулевых начальных разрядов не равно нулю, с целью получения окончательного значения подсчета нулевых начальных разрядов.

цифровой процессор сигналов, содержащий:

запоминающее устройство;

контроллер последовательности, реагирующий на запоминающее устройство;

блок регистров, соединенный с запоминающим устройством;

устройство исполнения команд, реагирующее на контроллер последовательности, при этом устройство исполнения команд содержит:

блок управления;

расширитель знака, соединенный с блоком управления;

инвертор, соединенный с блоком управления; и

шестидесяти четырех разрядный счетчик битов, соединенный с блоком управления, при этом блок управления включает в себя:

логику для управления шестидесяти четырех разрядным счетчиком битов с целью осуществления подсчета нулевых начальных разрядов в одном или более тридцати двух разрядных словах данных; и

логику для управления шестидесяти четырех разрядным счетчиком битов с целью осуществления подсчета нулевых начальных разрядов в одном или более шестидесяти четырех разрядных словах данных;

процессор основной полосы частот, соединенный с цифровым процессором сигналов;

кодер/декодер (кодек), соединенный с процессором основной полосы частот;

приемопередатчик радиочастотного (RF) диапазона, соединенный с процессором основной полосы частот; и

антенну, соединенную с приемопередатчиком RF диапазона.

контроллер Bluetooth, соединенный с цифровым процессором сигналов; и антенну Bluetooth, связанную с контроллером Bluetooth.

контроллер 802.11, соединенный с цифровым процессором сигналов;

антенну 802.11, соединенную с контроллером 802.11;

контроллер Bluetooth, соединенный с цифровым процессором сигналов;

антенну Bluetooth, соединенную с контроллером Bluetooth;

контроллер универсальной последовательной шины (USB), соединенный с цифровым процессором сигналов; и USB-порт, соединенный с контроллером USB.

средство для приема тридцати двух разрядного слова данных;

средство для расширения за счет знака тридцати двух разрядного слова данных с целью создания временного шестидесяти четырех разрядного слова данных;

средство для осуществления подсчета нулевых начальных разрядов во временном шестидесяти четырех разрядном слове данных с целью получения промежуточного значения подсчета нулевых начальных разрядов и

средство для вычитания значения из промежуточного значения подсчета нулевых начальных разрядов, если значение подсчета не равно нулю, с целью получения окончательного значения подсчета нулевых начальных разрядов.

средство для приема тридцати двух разрядного слова данных;

средство для расширения за счет знака тридцати двух разрядного слова данных с целью создания временного шестидесяти четырех разрядного слова данных;

средство для инвертирования временного шестидесяти четырех разрядного слова данных с целью создания инвертированного временного шестидесяти четырех разрядного слова данных;

средство для осуществления подсчета нулевых начальных разрядов во временном шестидесяти четырех разрядном слове данных с целью получения промежуточного значения подсчета единичных начальных разрядов; и

средство для вычитания значения из промежуточного значения подсчета единичных начальных разрядов, если значение подсчета не равно нулю, с целью получения окончательного значения подсчета единичных начальных разрядов.

прнимают слово данных, имеющее разрядность 2 в N-й степени;

выполняют расширение за счет знака слова данных до временного слова данных, имеющего разрядность 2 в М-й степени;

вводят временное слово данных на счетчик, имеющий разрядность 2 в М-й степени;

осуществляют подсчет нулевых начальных разрядов во временном слове данных для получения временного результата; и вычитают значение, равное 2 в М-й степени минус 2 в N-й степени, из временного результата для определения значения подсчета.

копируют содержимое разряда М в позицию разряда N и заменяют нулем содержимое разрядов от М до N+1.

средство для приема слова данных, имеющего разрядность 2 в N-й степени;

средство для расширения за счет знака слова данных до временного слова данных, имеющего разрядность 2 в М-й степени;

средство для ввода временного слова данных в счетчик, имеющий разрядность 2 в М-й степени;

средство для осуществления подсчета нулевых начальных разрядов во временном слове данных с целью получения временного результата;

средство для вычитания значения, равного 2 в М-й степени минус 2 в N-й степени, из временного результата с целью получения значения подсчета.

средство для копирования содержимого разряда М в позицию разряда N и средство для замены нулем содержимого разрядов от М до разряда N+1.

цифровой процессор сигналов;

кодер/декодер (CODEC, кодек) аудио, соединенный с цифровым процессором сигналов;

мультимедийную плату, соединенную с цифровым процессором сигналов;

порт универсальной последовательной шины (USB), соединенный с цифровым процессором сигналов; и

при этом цифровой процессор сигналов включает в себя:

запоминающее устройство;

контроллер последовательности, реагирующий на запоминающее устройство;

блок регистров, соединенный с запоминающим устройством;

устройство исполнения команд, реагирующее на контроллер последовательности, причем устройство исполнения команд включает в себя:

блок управления;

расширитель знака, соединенный с блоком управления;

инвертор, соединенный с блоком управления; и

шестидесяти четырех разрядный счетчик битов, соединенный с блоком управления, при этом блок управления включает в себя:

логику для управления шестидесяти четырех разрядным двоичным счетчиком с целью осуществления подсчета нулевых начальных разрядов в одном или более тридцати двух разрядных словах данных и

логику для управления шестидесяти четырех разрядным двоичным счетчиком с целью осуществления подсчета нулевых начальных разрядов в одном или более шестидесяти четырех разрядных словах данных.

Документы, цитированные в отчёте о поиске

Обработка с использованием одного потока команд и множества потоков данных

Комментарии