Способ и устройство для реконфигурируемого процессора - RU2283507C2

Код документа: RU2283507C2

Чертежи

Описание

Область к которой относится изобретение

Изобретение в целом относится к изменению пропускной способности между устройством и процессором. Более точно изобретение относится к устройству и способу изменения пропускной способности между устройством и процессором без изменения разводки физических компонентов в процессоре.

Предшествующий уровень техники

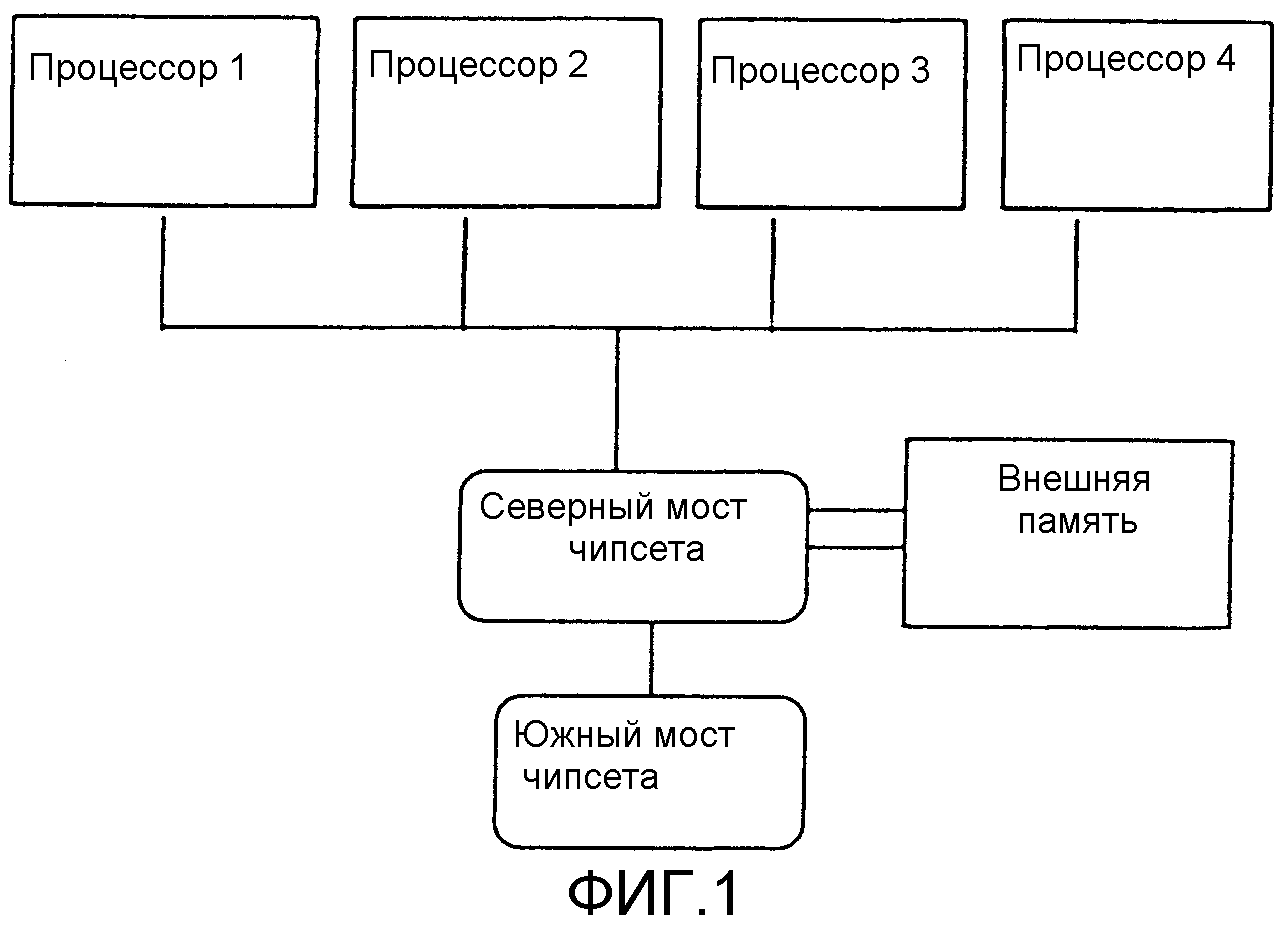

Параллельное объединение нескольких процессоров увеличивает производительность обработки данных. Обычно любое количество процессоров от двух до восьми может быть объединено параллельно. В общем случае набор параллельных процессоров объединяется через общую шину. Фиг.1 показывает четырехпроцессорную (4Р) архитектуру, используемую совместно с общей шиной. Четыре процессора: процессор 1, процессор 2, процессор 3 и процессор 4, подсоединены к общей шине, которая, в свою очередь, соединяется с микросхемой «северный мост» чипсета (набора микросхем). Северный мост чипсета дополнительно соединяется с микросхемой «южный мост» чипсета и внешней памятью. Например, Pentium™ процессор может использовать архитектуру общей шины, приведенную на Фиг.1. Тем не менее, двухточечная архитектура шины обычно обеспечивает более высокую пропускную способность, чем архитектура с общей шиной.

В случае архитектуры с общей шиной одну и ту же шину совместно использует набор устройств, обязанных соблюдать определенный порядок и следовать определенному протоколу при использовании шины. Напротив, двухточечная архитектура шины обеспечивает непрерываемое соединение между двумя отдельными устройствами. Таким образом, двухточечная шина обеспечивает более высокую пропускную способность между двумя отдельными устройствами. Более высокая пропускная способность может иметь положительный эффект в виде повышения производительности одного процессора или группы процессоров. Например, если между двумя устройствами существует 48-битное соединение, то скорость транзакций между двумя устройствами в три раза выше, чем в случае наличия только 16-битного соединения между двумя данными устройствами. Однако из-за того, что данная архитектура обеспечивает непрерываемую связь между двумя отдельными устройствами, двухточечная архитектура шины может обладать некоторыми недостатками. Так, если в любой момент времени между двумя устройствами имеет место небольшой поток информации, избыточная пропускная способность гарантированно не используется.

Например, если заказчик использует свою компьютерную систему как для исполнения приложений рабочей станции, так и для исполнения серверных приложений, то пользователь может не добиться пиковой производительности аппаратного обеспечения его компьютерной системы. В серверном приложении идет интенсивный обмен информацией между процессорами. Соответственно между каждым процессором в системе производитель организует соединения с высокой пропускной способностью. Однако если, например, заказчик желает использовать в приложениях, которые подразумевают интенсивный обмен информацией между процессорами и чипсетом, такие, как приложения для рабочей станции, его компьютерную систему, тогда производитель организует соединения с высокой пропускной способностью между каждым процессором и микросхемой в системе. Тем не менее, если заказчик обладает компьютерной системой, в которой реализованы соединения с высокой пропускной способностью между процессором(ми) и чипсетом, но решил в данный момент запустить серверное приложение на этой системе, он может получить низкую производительность серверного приложения и недоиспользование избыточной пропускной способности между чипсетом и процессором(ми).

Краткое описание чертежей

Чертежи относятся к изобретению и содержат:

Фиг.1 иллюстрирует четырехпроцессорную (4Р) архитектуру, применяемую совместно с общей шиной.

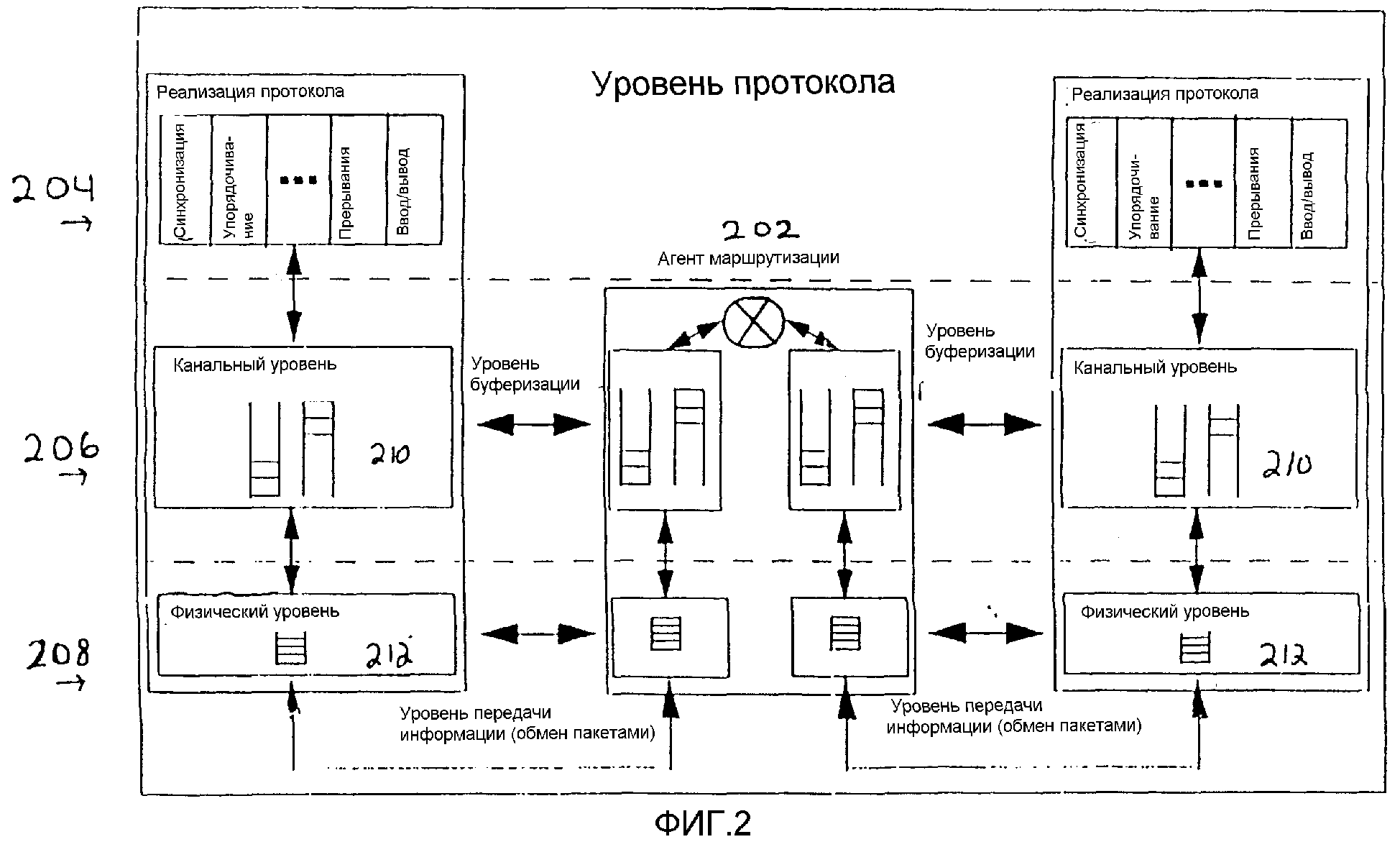

Фиг.2 иллюстрирует вариант осуществления процессора, включающего агент маршрутизации, уровень протокола, уровень буферизации и уровень передачи информации.

Фиг.3 иллюстрирует двухпроцессорную двухточечную архитектуру с 16-битным двухточечным соединением между: 1) компонентом ввода-вывода и первым процессором; так же как и 2) компонентом ввода-вывода и вторым процессором;

Фиг.4 иллюстрирует двухпроцессорную двухточечную архитектуру с 32-битным двухточечным соединением между: 1) компонентом ввода-вывода и первым процессором; так же, как и 2) компонентом ввода-вывода и вторым процессором;

Фиг.5 иллюстрирует четырехпроцессорную двухточечную архитектуру с 16-битным двухточечным соединением между компонентом ввода-вывода и каждым из четырех процессоров;

Фиг.6 иллюстрирует вариант осуществления агента маршрутизации, управляющего входящими линиями связи в варианте осуществления уровня передачи информации;

Фиг.7 иллюстрирует вариант осуществления агента маршрутизации, управляющего входящими линиями связи в варианте осуществления уровня буферизации.

Фиг.8 иллюстрирует вариант осуществления агента маршрутизации, управляющего исходящими линиями связи в варианте осуществления уровня буферизации.

Фиг.9 иллюстрирует вариант реализации агента маршрутизации, управляющего выходящими линиями связи в варианте реализации уровня передачи информации.

Хотя данное изобретение может быть модифицировано и реализовано в различных формах, на чертежах показаны конкретные варианты реализации изобретения, и они будут подробно описаны ниже. Необходимо понимать, что данное изобретение не ограничивается непосредственно раскрываемыми формами реализации, напротив, существует стремление охватить все модификации, эквиваленты и альтернативы, соответствующие духу и объему изобретения.

Подробное описание изобретения

Специалисты в данной области техники признают, что возможны разнообразные отклонения от описываемых вариантов реализации изобретения и что может быть сделано большое количество модификаций и усовершенствований, не выходя за рамки формы и объема изобретения. Например, в нескольких описанных вариантах реализации для иллюстрации используются определенные значения тактовой частоты, числа бит данных, определенное количество уровней, конкретное число компонентов и т.д. Тем не менее, специалист в данной области техники признает, что варианты реализации этого изобретения включают также варианты с отличиями от определенных величин, используемых в частном варианте реализации изобретения, приводимом здесь с целью иллюстрации.

Для того чтобы позволить заказчику изменять пропускную способность, или количество линий шины и тактовую частоту, между двумя устройствами в двухточечной архитектуре, с процессором может быть использован агент маршрутизации. Двухточечная архитектура шины обеспечивает непрерываемое соединение между двумя отдельными устройствами. В общем случае при двухточечной архитектуре шины передача информации осуществляется при помощи пакетного протокола. Агент маршрутизации может изменять эффективную пропускную способность между процессором и устройством, внешним по отношению к процессору путем изменения одной или более линий связи в процессоре, без изменения разводки для физических компонентов процессора. Пропускная способность представляет собой общее количество информации, которое может быть передано за данный период времени между двумя устройствами. В варианте реализации изобретения производитель или заказчик могут изменять количество портов, подключаемых между двумя устройствами, для увеличения пропускной способности между двумя устройствами. В варианте реализации изобретения производитель или заказчик могут добавлять дополнительные процессоры, соединенные с устройством, изменяя количество портов, подключаемых между первым процессором и устройством, внешним по отношению к первому процессору.

Фиг.2 иллюстрирует вариант осуществления процессора 200, имеющего агент 202 маршрутизации, уровень 204 протокола, уровень 206 буферизации и уровень 208 передачи информации. В одном варианте осуществления изобретения процессор 200 имеет агент 202 маршрутизации и три уровня: уровень 204 протокола, уровень 206 буферизации, например один или более канальных уровней 210, и уровень передачи информации, например один или более физических уровней 212. Агент 202 маршрутизации изменяет линии связи на физическом уровне 212 и канальном уровне 210 без изменения разводки для физических компонентов в процессоре 200. Физический уровень 212 выполняет физическую передачу информации в другие устройства и из них. Канальный уровень 210 реализует функции связи между функциями уровня 204 протокола и физическим уровнем 212. Уровень 204 протокола выполняет запросы, ответы и передачу данных.

В варианте осуществления изобретения агент 202 маршрутизации может быть внутренним или внешним по отношению к процессору 200. В варианте осуществления изобретения один агент 202 маршрутизации управляет линиями связи на всех уровнях процессора 200. В альтернативном варианте реализации изобретения для управления линиями связи существует множество агентов 202 маршрутизации. Агент 202 маршрутизации может быть комбинацией аппаратного и программного обеспечения. Агент 202 маршрутизации может реализовывать несколько функций, например посылку сигнала запрета/разрешения одному или более устройствам переключения линий связи и посылку сигнала изменения различных тактовых частот. Уровень 206 буферизации может содержать один или более входящих линий связи. Уровень 206 буферизации может содержать одну или более выходящих линий связи. Уровень 208 передачи информации может содержать одну или более входящих линий связи. Уровень 208 передачи информации может содержать одну или более выходящих линий связи.

Фиг.3 иллюстрирует двухпроцессорную двухточечную архитектуру 300, имеющую 16-битное двухточечное соединение между: 1) компонентом 302 ввода-вывода и первым процессором 304; так же как и 2) компонентом 302 ввода-вывода и вторым процессором 306. Первый процессор 304, имея четыре 16-битных порта 308, 310, 312, 314, соединенных с процессором, может иметь три 16-битных порта 308, 310, 312, подсоединенных ко второму процессору 306, и один 16-битный порт 314, подсоединенный к компоненту 302 ввода-вывода. В варианте реализации изобретения компонент ввода-вывода может быть мостом, памятью, чипсетом (набором микросхем) либо подобным компонентом. Таким образом, между первым процессором 304 и вторым процессором 306 существует 48-битное соединение. Помимо этого первый процессор 304 и второй процессор 306 имеют 16-битное соединение с компонентом 302 ввода-вывода. Агент маршрутизации может изменять линии связи в первом процессоре 304 таким образом, что процессор будет иметь два 16-битных двухточечных (32 бита) соединения со вторым процессором 306 и 32-битное соединение с компонентом 302 ввода-вывода.

Фиг.4 иллюстрирует двухпроцессорную двухточечную архитектуру 400, имеющую 32-битное двухточечное соединение между: 1) компонентом 402 ввода-вывода и первым процессором 404; так же как и 2) компонентом 402 ввода-вывода и вторым процессором 406. Первый процессор 404, имея четыре 16-битных порта 408, 410, 412, 414, соединенные с процессором, может иметь два 16-битных порта, подсоединенных ко второму процессору 406, и два 16-битных порта, подсоединенных к компоненту 402 ввода-вывода, например чипсету. Таким образом, между первым процессором 404 и вторым процессором 406 существует 32-битное соединение. Помимо этого первый процессор 404 и второй процессор 406 имеют 32-битное соединение с компонентом 402 ввода-вывода. В 32-битном режиме по сравнению с 16-битным режимом пропускная способность между компонентом 402 ввода-вывода и первым процессором 404 так же как и между компонентом 402 ввода-вывода и вторым процессором 406 эффективно удваивается. В 16-битном режиме требуется восемь тактовых циклов для передачи восьми 16-битных пакетов(128 бит) информации между каждым процессором и компонентом ввода-вывода. В 32-битном режиме требуется четыре тактовых цикла для передачи четырех 32-битных пакетов(128 бит) информации между каждым процессором и компонентом ввода-вывода.

Фиг.5 иллюстрирует вариант осуществления четырехпроцессорной двухточечной архитектуры 500, содержащей 16-битное соединение между компонентом 502 ввода-вывода и каждым из четырех процессоров 504, 506, 508, 510. Четыре процессора представлены процессором 1 504, процессором 2 506, процессором 3 508, процессором 4 510. В варианте реализации изобретения каждый из четырех процессоров 504, 506, 508, 510 использует вариант осуществления арбитра. Процессоры 504, 506, 508, 510 обладают гибкой архитектурой, которая координируется с арбитром с целью разнообразного использования процессоров 504, 506, 508, 510. Например, четырехпроцессорная архитектура 500 может быть заменена двухпроцессорной архитектурой с использованием 32-битного соединения с компонентом 502 ввода-вывода. Таким образом, вычислительная мощность такой конфигурации будет эффективно удвоена, т.к. данные, приходящие от компонента 502 ввода-вывода, будут обрабатываться четырьмя процессорами. Следовательно, реализация арбитра позволяет одному компоненту 502 ввода-вывода работать либо с двухпроцессорной архитектурой, либо с четырехпроцессорной архитектурой 500, или с другой подобной мультипроцессорной архитектурой.

Программируемые установки управления в конфигурационном регистре предписывают агенту маршрутизации установить конфигурацию, требуемую в настоящее время заказчиком, например 16-битное, 32-битное или 48-битное двухточечное соединение между процессором и устройством, внешним по отношению к процессору. В варианте реализации изобретения устройством, внешним по отношению к процессору, может быть другой процессор, устройство ввода-вывода, мост либо другое подобное устройство. В варианте реализации изобретения заказчик программирует установки управления для определения пропускной способности соединений между процессором и устройствами, внешними по отношению к процессору. Основываясь на установках управления в конфигурационном регистре, агент маршрутизации разрешает или блокирует линии связи на уровне передачи информации и уровне буферизации. Агент маршрутизации может изменять линии связи, увеличивая или уменьшая количество портов процессора и, следовательно, эффективную пропускную способность между процессором и другим устройством.

Обычно на сервере происходит интенсивный обмен данными между первым и вторым процессорами. Следовательно, наличие 48-битного двухточечного соединения между двумя данными устройствами значительно сокращает время выполнения каждой транзакции между данными устройствами. В случае рабочей станции обычно происходит интенсивный обмен данными между каждым процессором и компонентом ввода-вывода. Следовательно, наличие 32-битного или 48-битного двухточечного соединения между этими устройствами значительно сокращает время выполнения каждой транзакции между данными устройствами. Специалисты в данной области техники должны признать, что определенные компоненты, описанные в следующем варианте реализации изобретения, могут отличаться или находиться в объеме изобретения.

Фиг.6 иллюстрирует вариант осуществления агента 602 маршрутизации, управляющего входящими линиями связи в варианте осуществления уровня 600 передачи информации. Первый физический уровень (SPX0 - упорядоченный обмен пакетами) 604 имеет первый порт 606; девять 16-битных регистров, первый регистр 608, второй регистр 610, третий регистр 612, четвертый регистр 614, пятый регистр 616, шестой регистр 618, седьмой регистр 620, восьмой регистр 622 и девятый регистр 624; первый 64-битный регистр 626; устройство 628 переключения линий связи такое, как мультиплексор; вариант осуществления агента 602 маршрутизации; первый элемент 609 временной задержки и первую триггерную схему 630. Второй физический уровень (SPX1- упорядоченный обмен пакетами) 632 имеет второй порт 634; девять 16-битных регистров, десятый регистр 636, одиннадцатый регистр 638, двенадцатый регистр 640, тринадцатый регистр 642, четырнадцатый регистр 644, пятнадцатый регистр 646, шестнадцатый регистр 648, семнадцатый регистр 650 и восемнадцатый регистр 652; второй 64-битный регистр 653; второй элемент 637 временной задержки и вторую триггерную схему 656. Мультиплексор представляет собой устройство, объединяющее несколько низкоскоростных каналов передачи в один высокоскоростной и наоборот. Регистр 645 конфигурации указывает агенту маршрутизации, должен ли быть определенный компонент, внешний по отношению к процессору, подсоединен через 16-битное, 32-битное или 48-битное соединение.

Если регистр 654 конфигурации запрограммирован для 16-битного двухточечного соединения с компонентом ввода-вывода, агент 602 маршрутизации предписывает каждому физическому уровню действовать независимо от других физических уровней. Например, в четырехпроцессорном варианте осуществления изобретения первый порт 606 соединяется со вторым процессором, и второй порт 634 устанавливает связь с компонентом ввода-вывода. Первый регистр 608 принимает входящий 16-битный пакет информации через первый порт 606. Этот 16-битный пакет информации посылается из первого регистра 608 через элемент 609 временной задержки для запоминания во втором регистре 610. Первый регистр 608 принимает следующий входящий 16-битный пакет информации через первый порт 606. Первый регистр 608 посылает второй 16-битный пакет информации для запоминания в третьем регистре 612. Первый физический уровень 604 повторяет данную операцию до тех пор, пока каждый из регистров со второго 610 по девятый 624 не будет содержать 16-битный пакет информации. Первое устройство 628 переключения линий связи определяет, что восемь по 16 бит (или 128 бит) информации готовы для передачи на первый канальный уровень через первую триггерную схему 630. На следующем тактовом цикле 128 бит информации передаются на первый канальный уровень через первую триггерную схему 630. Похожим образом, но используя компоненты второго физического уровня 632, второй физический уровень 632 передает 128 бит на второй уровень связи. Однако 128 бит информации, передаваемые на первый канальный уровень, не зависимы от 128 бит информации, передаваемых на второй канальный уровень. Таким образом, в нашем примере первые 128 бит информации приходят через первый порт 606 от второго процессора. Таким же образом, вторые 128 бит информации приходят через второй порт 634 от компонента ввода-вывода. Агент 602 маршрутизации разрешает 128-битную линию в первом устройстве 628 переключения линий связи. Агент 602 маршрутизации блокирует двойную 64-битную линию в первом устройстве 628 переключения линий связи. Агент 602 маршрутизации разрешает первую триггерную схему 630 и вторую триггерную схему 656.

Если регистр конфигурации запрограммирован для 32-битного двухточечного соединения, агент маршрутизации объединяет два физических уровня для совместной работы. Агент 602 маршрутизации запрещает 128-битную линию в первом устройстве 628 переключения линий связи. Агент 602 маршрутизации разрешает двойную 64-битную линию в первом устройстве 628 переключения линий связи. Агент 602 маршрутизации разрешает первую триггерную схему 630, но блокирует вторую триггерную схему 656. Агент 602 маршрутизации увеличивает тактовую частоту для каждого регистра с первого 608 по восемнадцатый 652 на коэффициент два. Первый физический уровень 604 получает четыре 16-битных пакета информации и запоминает пакеты информации в регистрах со второго 610 по четвертый 616. Второй физический уровень 632 принимает четыре 16-битных пакета информации и запоминает пакеты информации в регистрах с одиннадцатого 638 по четырнадцатый 644. Первое устройство 628 переключения линий связи определяет, что первый 64-битный регистр содержит четыре 16-битных пакета информации в регистрах со второго 610 по четвертый 616. Первое устройство 628 переключения линий связи определяет, что второй 64-битный регистр содержит четыре 16-битных пакета информации в регистрах с одиннадцатого 638 по четвертый 644. В следующем тактовом цикле 64 бит информации из первого 64-битного регистра и 64 бит информации из второго 64-битного регистра передаются до первого устройства 628 переключения линий связи через двойную 64-битную линию. Первое устройство 628 переключения линий связи передает восемь связанных 16-битных пакетов информации на первый канальный уровень. Как устройство, внешнее по отношению к процессору, так и процессор передают восемь связанных 16-битных пакетов информации, как если бы между процессором и устройством существовало 32-битное двухточечное соединение. Второй канальный уровень не принимает сигнал, так как работа второй триггерной схемы запрещена. Таким же образом, агент маршрутизации может объединить три физических уровня для образования 48-битной линии связи между процессором и устройством.

Фиг.7 иллюстрирует вариант осуществления агента 702 маршрутизации управляющего входящими линиями связи в варианте реализации уровня 700 буферизации. Входящая линия связи первого канального уровня 704 имеет первый 128-битный регистр 706, первую очередь 708 ответов, первую очередь 710 запросов, и первое устройство 712 переключения линий связи. Входящая линия связи второго канального уровня 714 имеет второй 128-битный регистр 716, вторую очередь 711 ответов, вторую очередь 713 запросов и второе устройство 716 переключения линий связи. Состав и организация компонентов третьего канального уровня 718 и четвертого канального уровня 720 аналогичны первому канальному уровню 704. Первый канальный уровень по четвертый канальный уровень связаны с пятым устройством 722 переключения линий связи вариантом осуществления агента 702 маршрутизации, пятым 128-битным регистром 724 и буфером 726 слежения за транзакциями при локальном доступе с локальными адресами (ЛСТ), центральным буфером 728 управления данными (ЦДУ) и буфером 730 слежения за транзакциями при удаленном доступе (с адресами удаленных устройств) (УДСТ).

В варианте реализации входного уровня 700 буферизации, в случае если регистр 732 конфигурации запрограммирован для 32-битного двухточечного соединения, агент 702 маршрутизации эффективно объединяет два уровня соединения вместе. Первый канальный уровень 704 принимает восемь связанных 16-битных пакетов (128 бит) информации от устройства переключения линий связи на первом физическом уровне на удвоенной тактовой частоте. Первый канальный уровень 704 сохраняет 128-битный пакет информации в первом регистре 706. 128-битный пакет информации направляется соответственно либо в первую очередь 708 ответов, либо в первую очередь 710 запросов. Агент 702 маршрутизации посылает сигнал разрешения первому устройству 712 переключения линий связи, третьему устройству 734 переключения линий связи и пятому устройству 722 переключения линий связи. Агент 702 маршрутизации также посылает сигнал запрещения второму устройству 716 переключения линий связи и четвертому устройству 736 переключения линий связи. Агент 702 маршрутизации предписывает пятому устройству 722 переключения линий связи запрашивать данные только от первого устройства 712 переключения линий связи и третьего устройства 734 переключения линий связи. В 32-битном режиме второе устройство 716 переключения линий связи и четвертое устройство 736 переключения линий связи не получают сигналов с физического уровня, т.к. агент 702 маршрутизации блокирует вторую триггерную схему и четвертую триггерную схему физического уровня.

128-битные пакеты информации последовательно в цикле передаются на пятое устройство 722 переключения линий связи через первое устройство 712 переключения линий связи и третье устройство 734 переключения линий связи. В повторяющемся цикле пятое устройство 722 переключения линий связи запрашивает содержимое первой очереди 708 ответов, затем первой очереди 710 запросов, затем третей очереди 738 ответов, затем третей очереди 740 запросов и затем повторяет эту последовательность. Каждый пакет информации может быть либо запросом команды и/или данных, либо ответом на команду или данные. В варианте реализации изобретения непосредственно после записи пакета в очередь ответов или очередь запросов информация передается из данных очередей на тактовой частоте ядра. Пакеты информации посылаются из пятого устройства 722 переключения линий связи к одному из следующих трех компонентов. Центральный буфер 728 управления данными (ЦДУ) запоминает данные, которые должны быть использованы на уровне протокола 740. Буфер слежения 730 за транзакциями при удаленном доступе (УДСТ) запоминает команды от удаленного устройства, например запрос от удаленного процессора. ЦДУ 728 запоминает соответствующие данные, ассоциированные с этой командой, если они присутствуют. Таким же образом буфер 726 слежения за транзакциями при локальном доступе (ЛДСТ) запоминает локальные команды и ответы, выдаваемые ядром процессора. Соответствующие данные, если они присутствуют, ассоциированные с этой командой, запоминаются в ЦДУ 728.

Если регистр 732 конфигурации запрограммирован для 16-битного двухточечного соединения, тогда каждый уровень 704, 714, 718, 720 входящих связей действует независимо. Агент 702 маршрутизации предписывает пятому устройству 722 переключения линий связи запрашивать информацию от восьми возможных источников, а именно соответствующих очередей запросов 710, 713, 740, 750 или соответствующих очередей ответов 708, 711, 738, 748 в каждом из канальных уровней 704, 714, 718, 720 в виде циклической последовательности. Если конкретная очередь пуста, тогда устройство 722 переключения линий связи автоматически извлекает пакеты из следующей очереди без каких-либо штрафов. В реализации изобретения пакеты от четырех физических уровней записываются в соответствующие очереди с частотой 100 мегагерц, если регистр конфигурации запрограммирован для 16-битного соединения. Пакеты записываются в очереди с частотой 200 Мегагерц, если регистр конфигурации запрограммирован для 32-битного соединения. Если регистр конфигурации сконфигурирован для 48-битного соединения, тогда агент 702 маршрутизации объединяет три канальных уровня вместе. Как только пятое устройство 722 переключения линий связи принимает пакет информации от одного из восьми возможных источников, пакет посылается на уровень протокола 740.

Входной канальный уровень посылает ответы и запросы на уровень 740 протокола. Уровень 740 протокола чередует выбор команд из ЛДСТ 726 или УДСТ 730, сопровождаемые данными из ЦДУ 728. В одном варианте реализации изобретения данная физическая информация может быть послана в ЦПУ. Информация приходит в ЦПУ для обработки и затем посылается в выходной канальный уровень. Уровень 740 протокола обычно является обрабатывающим компонентом. Уровень 740 протокола обычно разрешает запросы от других локальных процессоров и посылает запросы через физический уровень. Уровень 740 протокола может отвечать за такие функции, как упорядочивание, регистрацию конфликтов и синхронизацию. Уровень 740 протокола может пересылать запросы данных контроллеру локальной памяти, если запрос сделан к локальной памяти. Уровень 740 протокола может посылать отслеживающие запросы удаленным узлам и другим локальным процессорам. Уровень 740 протокола также обрабатывает запросы, сделанные через канальный уровень, которые могут приходить от удаленного процессора или компонента ввода-вывода.

Фиг.8 иллюстрирует вариант осуществления агента 802 маршрутизации, управляющего выходящими линиями связи в варианте осуществления уровня 800 буферизации. Уровень 804 протокола посылает обработанные данные и команды каждому из канальных уровней 806, 808, 810, 812. Уровень 804 протокола доставляет команды, генерируемые им самим, в ЛДСТ 814 и данные, если они присутствуют, соответствующие этим командам, в ЦДУ 816. Уровень 804 протокола доставляет ответы на команды от удаленных устройств в УДСТ 818 и данные, если они присутствуют, соответствующие этим командам, в ЦДУ 816. Если регистр 820 конфигурации запрограммирован для 32-битного двухточечного соединения, агент 802 маршрутизации эффективно разрешает два из четырех выходных канальных уровня. Вдоль пути следования сигнальной линии в первом выходном канальном уровне 806 и втором выходном канальном уровне 808 происходит следующее. Агент 802 маршрутизации предписывает второму устройству 822 переключения линий связи и четвертому устройству переключения линий связи (не показано) перейти в заблокированное состояние. Агент 802 маршрутизации предписывает пятому устройству 828 переключения линий связи запрашивать данные через первое устройство 824 переключения линий связи и третье устройство 826 переключения линий связи из буферов 830 запроса или буфера 832 ответа соответственно. Пятое устройство 828 переключения линий связи поочередно запрашивает биты в повторяющемся цикле из буфера 830 запросов и буфера 832 ответов. Пятое устройство 828 переключения линий связи также принимает любые данные, если они присутствуют, соответствующие этим командам из ЦДУ 816. Пятое устройство 828 переключения линий связи направляет затем 128-битный пакет данных через первый элемент 833 временной задержки либо в очередь 836 исходящих ответов, либо в очередь 834 исходящих запросов, расположенные на выходном физическом уровне.

На выходном канальном уровне присутствуют одна или более очередей 838 повторов. В очередь 838 повторов помещается копия информации, предназначенной для передачи, на случай возникновения ошибки при передаче информации. Очередь 838 повторов присутствует, главным образом, в тех случаях, когда существует возможность возникновения ошибок связи. Очередь 838 повторов стирает дублированную информацию, помещенную в очередь 838 повторов, при получении подтверждения безошибочной передачи информации.

Если регистр 820 конфигурации запрограммирован для 16-битного двухточечного соединения, тогда агент 802 маршрутизации предписывает каждому из выходных канальных уровней 806, 808, 810, 812 действовать независимо. Агент 802 маршрутизации посылает сигнал разрешения всем устройствам переключения линий в выходных канальных уровнях и устанавливает тактовую частоту по умолчанию. Информация направляется из ЛДСТ 814, УДСТ 818 и ЦДУ 816 через соответствующий каждому выходной канальный уровень в соответствующий выходной физический уровень. Например, агент 802 маршрутизации предписывает второму устройству 822 переключения линий связи запрашивать данные через шестое устройство 840 переключения линий связи из второй очереди 842 ответов и затем запрашивать данные через седьмое устройство 844 переключения линий связи из второй очереди 846 запросов. Второе устройство 822 переключения линий связи попеременно в повторяющихся циклах запрашивает биты из второй очереди 842 ответов и второй очереди 846 запросов. Второе устройство 822 переключения линий связи также принимает любые данные, соответствующие этим командам, если они присутствуют, из ЦДУ 816. Второе устройство 822 переключения линий связи затем направляет 128-битный пакет через второй элемент 848 временной задержки либо во вторую очередь 850 исходящих ответов, либо во вторую очередь 852 исходящих запросов, расположенные на выходном физическом уровне.

Фиг.9 иллюстрирует вариант осуществления агента 902 маршрутизации, управляющего линиями связи в выходном уровне 900 передачи информации. В варианте осуществления изобретения уровень передачи информации включает один или больше физических уровней. Физический уровень выполняет реальную физическую передачу информации устройствам внешним по отношению к процессору через порты, такие как первый порт 904 и второй порт 906. Обычно один 16-битный порт есть на каждом физическом уровне, например порт 904. Через эти порты процессор осуществляет передачу информации между ним и устройством, внешним по отношению к процессору. Информационные сигналы содержат такую информацию, как запросы, ответы и данные.

Например, в варианте осуществления двухпроцессорной архитектуры три порта подключаются ко второму процессору в системе, а четвертый порт подключается к компоненту ввода-вывода, такому, как чипсет. Первое устройство 908 переключения линий связи, например мультиплексор, принимает 128-битные пакеты информации с канального уровня. Первое устройство 908 переключения линий связи считывает 128-битные пакеты информации либо из очереди 911 ответов, либо из очереди 910 запросов, например, с тактовой частотой 100 мегагерц. Сигнал с выхода первого устройства 908 переключения линий связи представляет собой два 64-битных пакета информации, первый 64-битный пакет и второй 64-битный пакет, которые сохраняются в первом регистре 912. После элемента 914 временной задержки второе устройство 918 переключения линий связи считывает первый 64-битный пакет 128-битного пакета информации через второй регистр 916 на удвоенной тактовой частоте 200 мегагерц. Сигнал с выхода второго устройства 918 переключения линий связи представляет собой два 32-битных пакета информации, первый 32-битный пакет и второй 32-битный пакет, которые сохраняются в третьем регистре 920. Тактовая частота для 32-битного пакета информации в третьем регистре еще раз удваивается до 400 мегагерц.

Агент 902 маршрутизации теперь предписывает передачу 32-битного пакета информации через 32-битную обходную линию 922 или 16-битную линию передачи в соответствующих устройствах 926, 934 переключения линий связи. Регистр 924 конфигурации указывает агенту 902 маршрутизации, должен ли быть компонент, внешний по отношению к процессору, 16-битным, 32-битным или 48-битным двухточечным соединением. В одном варианте осуществления, например, если 16-битное двухточечное соединение присутствует между процессором и компонентом ввода-вывода, тогда агент 902 маршрутизации предписывает каждому физическому уровню действовать независимо от других физических уровней. Четвертое устройство 926 переключения линий связи считывает 32-битный пакет информации с частотой 400 мегагерц из третьего регистра 920 и выводит два 16-битных пакета информации. Пятое устройство 928 переключения линий связи считывает 16-битный пакет информации на частоте 400 мегагерц из четвертого регистра 927 и выводит этот 16-битный пакет информации в первый порт 904. Агент 902 маршрутизации посылает сигнал шестому устройству 930 переключения линий связи на втором выходящем физическом уровне 932. Данный сигнал разрешает 16-битную линию в пятом устройстве переключения линий связи 928. Агент 902 маршрутизации блокирует 32-битную обходную линию 922 из четвертого устройства 926 переключения линий связи. Агент 902 маршрутизации также посылает сигнал на второй физический уровень 932, шестое устройство 930 переключения линий связи, разрешая 16-битную линию в шестом устройстве 930 переключения линий связи и запрещая/игнорируя 32-битную обходную линию 922, приходящую от третьего регистра 920. Таким образом, выходные сигналы первого порта 904 и второго порта 906 представляют собой несвязанные 16-битные пакеты информации.

Например, если в одном варианте осуществления между процессором и компонентом ввода-вывода существует 32-битное двухточечное соединение, тогда агент 902 маршрутизации объединяет выходной сигнал первого порта 904 и выходной сигнал второго порта 906. Агент 902 маршрутизации посылает сигнал на шестое устройство 930 переключения линий связи. Сигнал агента маршрутизации блокирует 16-битную линию в шестом устройстве 930 переключения линий связи и разрешает 32-битную обходную линию 922, приходящую из третьего регистра 920. Агент 902 маршрутизации также посылает сигнал на первый физический уровень 931, четвертое устройство 926 переключения линий связи, разрешая 32-битную обходную линию 922. Таким образом, выходные сигналы первого порта 904 и второго порта 906 представляют собой связанные 16-битные пакеты информации. Другими словами, выходные сигналы первого порта 904 и второго порта 906 являются 32-битным пакетом информации. Для того чтобы сохранять прежнюю скорость передачи, агент 902 маршрутизации посылает также сигнал, удваивающий тактовую частоту регистров. Например, 32-битный пакет информации в третьем регистре 920 теперь тактируется на частоте 800 мегагерц. 800 мегагерц являются удвоенной тактовой частотой по сравнению со случаем 16-битной передачи информации. Таким же образом агент 902 маршрутизации может объединить вместе три порта (не показано), образуя в выходной линии связи 48-битное соединение.

В альтернативном варианте осуществления, если три физических уровня подключены, например, ко второму процессору, тогда, не обязательно, агент маршрутизации может быть запрограммирован передавать три связанных 16-битных пакета, предназначенных для второго процессора, через соответствующие компоненты каждого канального уровня и физического уровня. Таким образом, первый 16-битный пакет проходит через компоненты первого физического уровня и первого канального уровня. Второй 16-битный пакет проходит через компоненты второго физического уровня и второго канального уровня. Третий 16-битный пакет проходит через компоненты третьего физического уровня и третьего канального уровня. Агент маршрутизации изменяет адресный заголовок в трех 16-битных пакетах для того, чтобы известить второй процессор, что данные три 16-битных пакета взаимосвязаны.

Данное изобретение может быть модифицировано и реализовано в различных формах. Конкретные варианты осуществления изобретения были приведены только для примера. Соединения между процессором и устройствами могут быть, например, от 8-битных до 64-битных или более. Тактовая частота может быть, например, от 1 мегагерца до 1 гигагерца или более. Регистры могут быть от 1-битных до 128-битных или более. Дополнительно большинство функций, реализуемых посредством электронных компонентов аппаратного обеспечения, могут быть дублированы при помощи эмуляции программными средствами. Таким же образом функциональность каждого уровня: уровня протокола, уровня буферизации и уровня передачи информации может быть скомбинирована, например, в один уровень или перенесена в другой компонент. Должно быть понятно, что изобретение не ограничивается приведенными частными вариантами, напротив предполагается, что изобретение охватывает все модификации, эквиваленты и альтернативы, соответствующие форме и объему изобретения, как это определено прилагаемой формулой изобретения.

Реферат

Изобретение относится к способу, устройству и системе для изменения одной или более линий связи в процессоре без изменения разводки его физических компонентов. Техническим результатом является обеспечение возможности изменения пользователем пропускной способности или количества линий шины между процессором и внешним устройством без изменения разводки физических компонентов. Указанный результат достигается за счет использования агента маршрутизации для изменения одной или более линий связи в процессоре на основании вводимых пользователем установок управления, содержащего первый компонент для определения пропускной способности между внешним устройством и процессором и второй компонент для выдачи сигнала управления на одно или более устройств переключения линий связи, причем сигнал управления основан на определении пропускной способности первым компонентом. 7 н. 15 з.п. ф-лы, 9 ил.

Комментарии