Нечувствительный к задержке буфер транзакции для связи с квитированием - RU2598594C2

Код документа: RU2598594C2

Чертежи

Описание

Область техники, к которой относится изобретение

Варианты осуществления настоящего изобретения относятся в основном к интерфейсам компьютерных систем. В частности, варианты осуществления изобретения относятся к нечувствительному к задержке буферу транзакций для протоколов связи с квитированием систем система-на-кристалле.

Уровень техники

Основные микросхемы процессоров, как высокопроизводительных, так и низкоэнергетических, все чаще выполняют дополнительные функции, например, графические, функции устройств отображения, функции модулей безопасности, функции PCIe ™ портов (т.е., портов в соответствии со спецификацией взаимного соединения периферийных компонентов (PCI Express ™ (PCIe ™)) базовой спецификации версии 2.0 (опубликована в 2007 г.) (далее упоминается как PCIe ™ спецификация) и других PCIe ™ на основе периферийных устройств, предоставляя при этом унаследованную поддержку устройствам, совместимых с PCI спецификацией, такой как спецификацией взаимного соединения периферийных компонентов (PCI) спецификации локальной шины, версия 3.0 (опубликована в 2002 г.) (здесь и далее, упоминается как PCI спецификация).

Такие конструкции высоко сегментированы из-за наличия различных спецификаций сервера, настольных, мобильных, встраиваемых, ультра мобильных и мобильных интернет устройств. Различные рынки стремятся использовать единую микросхему система-на-кристалле (SoC или SOC), сочетающая, по меньшей мере, некоторые из ядро процессора, контроллеров памяти, контроллеров ввода/вывода и других элементов сегмента удельного ускорения на одной микросхеме. Тем не менее, конструкции, которые аккумулируют эти признаки, не получили широкое распространение из-за трудностей интеграции различных компонентов (IP) архитектуры, охраняемые законом об авторском праве, или агентов на одном кристалле. Это особенно проявляется в том, что IP-блоки могут иметь различные спецификации и уникальную конструкцию, и могут потребовать использования множества специализированных проводов, коммуникационных протоколов и так далее, чтобы совместить их на SoC. В результате, каждая SoC или другое передовое полупроводниковое устройство, которое было разработано, имеет более сложную конструкцию и процедуру адаптации к специфическим требованиям для инкорпорирования различных IP-блоков в одном устройстве.

При использовании протокола связи с квитированием (и тому подобное) IP агент должен быть подключен к соединению (или структуре, шине) для получения права использования или прав доступа на взаимодействие, отправив сигнал с запросом (REQ) арбитру, и приняв сигнал (GNT) разрешения от арбитра, прежде чем будет осуществлена передача транзакции в соединение. Как правило, как показано на фиг. 1, устройство временного хранения информации (здесь и далее обозначается как буфер транзакций) реализуется как буфер транзакций или транзакции, относящейся к данным (извлекаемые из устройства хранения данных транзакций, например, регистры), для которых "REQ" уже был размещен на IO структуре подсистемы в качестве примера. Когда принимается "GNT", соответствующая транзакция извлекается из буфера транзакций и поставляется в IO структуры подсистемы, как показано на фиг. 1. В результате, глубина этого буфера транзакций зависит от латентности связи с квитированием для заданной полосы пропускания и устойчивости к задержке. Когда IP агент перемещается в пределах IO структуры подсистемы или меняет свои требования к латентности, то изменяется латентность связи с квитированием, что оказывает воздействие на глубину буфера транзакций.

Краткое описание чертежей

Варианты осуществления настоящего изобретения проиллюстрированы в качестве примера, и не ограничиваются описанием, приведенным на прилагаемых чертежах, на которых одинаковые ссылочные позиции указывают одинаковые элементы.

Фиг. 1 представляет собой схему, иллюстрирующую типичные транзакции узла.

Фиг. 2 представляет собой блок-схему, иллюстрирующую базовую архитектуру межкомпонентного соединения в соответствии с вариантом осуществления.

Фиг. 3 представляет собой блок-схему алгоритма, иллюстрирующую процесс обработки протокола связи с квитированием согласно одному варианту осуществления.

Фиг. 4 представляет собой блок-схему алгоритма, иллюстрирующую механизм обработки транзакции в соответствии с другим вариантом осуществления.

Фиг. 5 представляет собой блок-схему алгоритма, иллюстрирующую способ обработки транзакции протоколов связи с квитированием согласно одному варианту осуществления.

Фиг. 6А и 6В показывают блок-схемы, иллюстрирующие систему система-на-кристалле в соответствии с одним вариантом осуществления.

Фиг. 7А иллюстрирует примерный формат команд расширения системы команд (AVX) в соответствии с одним вариантом осуществления настоящего изобретения.

Фиг. 7В иллюстрирует примерный формат команд расширения системы команд (AVX) в соответствии с другим вариантом осуществления настоящего изобретения.

Фиг. 7С иллюстрирует примерный формат команд расширения системы команд (AVX) в соответствии с другим вариантом осуществления настоящего изобретения.

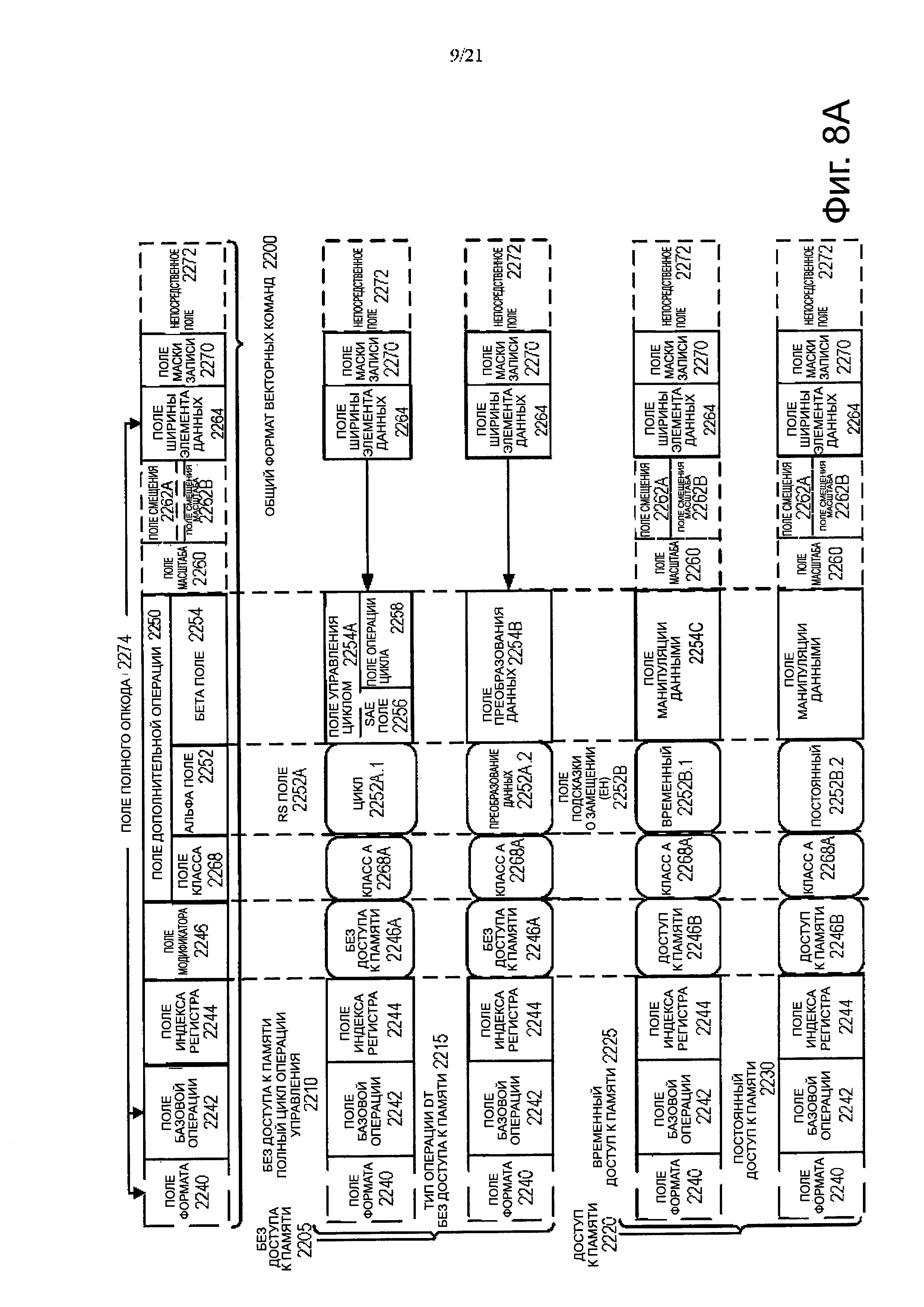

Фиг. 8А представляет собой блок-схему, иллюстрирующую общий формат векторных команд и их шаблоны команд класса А, в соответствии с вариантами осуществления изобретения.

Фиг. 8В показывает блок-схему, иллюстрирующую общий формат векторных команд и их шаблоны команд класса В, в соответствии с вариантами осуществления изобретения.

Фиг. 9А показывает блок-схему, иллюстрирующую примерный конкретный формат векторных команд, в соответствии с одним вариантом осуществления изобретения.

Фиг. 9В изображает блок-схему, иллюстрирующую общий формат векторных команд, в соответствии с другим вариантом осуществления изобретения.

Фиг. 9С показывает блок-схему, иллюстрирующую общий формат векторных команд, в соответствии с другим вариантом осуществления изобретения.

Фиг. 9D представляет собой блок-схему, иллюстрирующую общий формат векторных команд, в соответствии с другим вариантом осуществления изобретения.

Фиг. 10 представляет собой блок-схему архитектуры регистра в соответствии с одним вариантом осуществления настоящего изобретения.

Фиг. 11а представляет собой блок-схему, иллюстрирующую пример упорядоченного конвейера и пример переименования регистра конвейером с изменением последовательности выполнения команд в соответствии с вариантами осуществления изобретения.

Фиг. 11В представляет собой блок-схему, иллюстрирующую пример варианта осуществления архитектуры ядра с логикой последовательного выполнения команд и пример переименования регистра архитектурой ядра с логикой изменения последовательности выполнения команд, включенного в состав процессора, в соответствии с вариантами осуществления изобретения.

Фиг. 12А показывает блок-схему ядра процессора в соответствии с одним вариантом осуществления настоящего изобретения.

Фиг. 12В показывает блок-схему ядра процессора в соответствии с другим вариантом осуществления настоящего изобретения.

Фиг. 13 представляет собой блок-схему процессора согласно вариантам осуществления настоящего изобретения.

Фиг. 14 представляет собой блок-схему системы в соответствии с одним вариантом осуществления настоящего изобретения.

Фиг. 15 представляет собой блок-схему более конкретного примера системы в соответствии с вариантом осуществления настоящего изобретения.

Фиг. 16 показывает блок-схему более конкретного примера системы в соответствии с другим вариантом осуществления настоящего изобретения.

Фиг. 17 показывает блок-схему SoC в соответствии с вариантом осуществления настоящего изобретения.

Фиг. 18 представляет собой блок-схему, которая иллюстрирует пример контрастного использования преобразователя команд программного обеспечения для преобразования двоичных команд в наборе команд источника в двоичные команды в целевом наборе команд в соответствии с вариантами осуществления изобретения.

Описание вариантов осуществления

Различные варианты осуществления и аспекты изобретения будут описаны со ссылкой на подробное приведенное ниже описание и на прилагаемые чертежи, которые иллюстрируют различные варианты осуществления. Нижеследующее описание и чертежи иллюстрируют изобретение и не должны быть истолкованы как ограничивающие изобретение. Многочисленные конкретные подробности описаны ниже для обеспечения полного понимания различных вариантов осуществления настоящего изобретения. Тем не менее, в некоторых случаях, хорошо известные или типовые детали не описаны с целью обеспечения более краткого описания вариантов осуществления настоящего изобретения.

Ссылка в описании на "один вариант осуществления" или "вариант осуществления" означает, что конкретный признак, структура или характеристика, описанные в связи с вариантом осуществления, могут быть включены в состав, по меньшей мере, одного из вариантов осуществления изобретения. Употребление фразы "в одном из вариантов" в различных местах описания, не обязательно все относится к одному и тому же варианту осуществления.

Варианты осуществления, описанные здесь, могут быть использованы во многих различных типах систем. В качестве примеров реализации, описанные здесь, могут быть использованы с применением полупроводниковых приборов, таких как процессоры или другие полупроводниковые устройства, которые могут быть изготовлены на одном полупроводниковом кристалле. В конкретной реализации, устройство может представлять собой систему-на-кристалле (SoC) или другой усовершенствованный процессор, который включает в себя различные однородные и/или гетерогенные агенты обработки и дополнительные компоненты, такие как сетевые компоненты, например, маршрутизаторы, контроллеры, мосты, память и так далее.

Некоторые варианты реализации могут быть использованы в полупроводниковом устройстве, которое реализовано в соответствии с заданной спецификацией, такой как спецификация структуры интегрированной системы на кристалле (IOSF), разработанной Intel® Corporation, изготовленной производителем полупроводника, чтобы обеспечить стандартизированный протокол межкомпонентного соединения на кристалле для установки компонентов архитектуры (IP), защищенных авторским правом, внутри SoC или другой микросхемы. Такие ЕР блоки могут представлять собой различные компоненты, включающие в себя универсальные процессоры с логикой последовательного выполнения команд и ядро с логикой изменения последовательности выполнения команд, блоки фиксированных функций, графические процессоры, контроллеры и многих другие. Благодаря стандартизации протокола межкомпонентного взаимодействия, инфраструктура, таким образом, реализуется для широкого использования ЕР агентов в различных типах микросхем. Соответственно, изготовитель полупроводниковых устройств может не только эффективно проектировать различные типы микросхем для различных клиентов, но может также с помощью спецификации предоставлять возможность третьим сторонам разрабатывать логические устройства, такие как IP агенты, которые будут включены в структуру таких микросхем. И, кроме того, путем предоставления нескольких вариантов различных аспектов протокола межкомпонентного соединения, повторным использованием конструкций, можно добиться наличия эффективной компоновки. Хотя варианты осуществления описаны здесь с использованием IOSF спецификации, очевидно, что объем настоящего изобретения не ограничивается в этом отношении, и варианты осуществления могут быть использованы во многих различных типах систем.

Согласно некоторым вариантам осуществления, предусматривается новый подход, который полностью устраняет зависимость буфера транзакции от латентности связи с квитированием. В этом подходе, глубина буфера транзакций зависит от латентности доступа для чтения набора регистров, из которого извлекаются транзакции. Буфер транзакций используется только для хранения фиксированного числа первоначально приостановленных транзакций (например, соответствующие запросы были отправлены, но соответствующие подтверждения не были приняты от арбитра). Когда буфер транзакций заполнен, запросы (REQ) новых транзакций отправляются независимо и ведется подсчет таких приостановленных запросов. Поскольку гарантируется, что сигнал (GNT) разрешения поступит в порядке, в котором были сделаны запросы (для данного класса потока/виртуального канала (FC/VC) канал), то будет обеспечена надлежащая сохранность только первоначальных транзакции в буфере транзакций на FC/VC канале. Каждый раз, прием GNT предохраняет буфер транзакций от переполнения, если не подтвержденный REQ был отправлен без сохранения соответствующей транзакции внутри буфера транзакций, то такие транзакции извлекаются из набора регистров для пополнения буфера транзакций.

Фиг. 2 представляет собой блок-схему, иллюстрирующую базовую архитектуру межкомпонентного соединения в соответствии с вариантом осуществления. Как показано на фиг. 2, система 100 может быть частью системы-на-кристалле или другого полупроводникового устройства, и включает в себя систему 120 коммутации, которая действует в качестве межкомпонентного соединения между различными компонентами. В примере, как показано, эти компоненты включают в себя IP агенты 130 и 140, которые могут быть независимыми IP блоками для обеспечения различных функциональных возможностей, таких как вычислительных, графических и так далее. Эти IP агенты являются, таким образом, IP блоками или логическими устройствами, имеющие интерфейс, совместимый со спецификацией IOSF, в одном варианте осуществления. Как далее видно, сеть 120 также взаимодействует с мостом 150, который также может быть IP агентом. Хотя это не показано для простоты иллюстрации в варианте на фиг. 1, мост 150 может работать в качестве интерфейса с другими компонентами системы, например, на той же микросхеме или на одной или нескольких различных микросхемах. Например, мост 150 может представлять собой любое из устройств сопряжения в системе, такое как мосты 920 и 985, показанные на фиг. 6А и 6В.

Как будет описано дополнительно ниже, каждый из элементов, показанный на фиг. 2, а именно сеть 120, IP агенты 130 и 140, мост 150 могут включать в себя один или несколько интерфейсов для осуществления обработки различных коммуникационных сигналов. Эти интерфейсы могут быть определены в соответствии со спецификацией IOSF, которая определяет коммуникационные сигналы на этих интерфейсах, протоколы, используемые для обмена информацией между агентами, арбитраж и механизмы управления потоком, используемые для инициирования и организации обмена информацией, поддержанные декодированием адреса и возможностями преобразования, обмен сообщениями при полосной или внеполосной коммуникации, управление мощностью, тестирование, проверку достоверности и отладку.

Как описано выше, когда IP агент, такой как IP агент 150, пытается отправить данные в систему 120 коммутации, IP агент 150 должен послать REQ сигнал (например, устанавливая REQ линию, ассоциированную с IP агентом) арбитру 110 и ждать GNT сигнал, принятый от арбитра 110 (который одобрен арбитром 110). После приема GNT от арбитра 110, IP агент 150 должен послать транзакцию в последующем цикле в систему 120 коммутации. После того, как IP агент 150 послал REQ арбитру 110 и ожидает GNT сигнал от арбитра 110, новые данные транзакции могут быть приняты и сохранены в блоке хранения транзакций, таком как регистры, IP агентом 150. В обычной системе IP агент 150 буферизует новые данные транзакции в буфере транзакции в ожидании GNT от арбитра, что может занять длительный период времени. В результате, буфер транзакций может потребовать большей емкости хранения для удержания всех приостановленных транзакций. Данная величина емкости хранения напрямую зависит от латентности связи с квитированием.

Согласно одному варианту осуществления, по меньшей мере, один из ЕР агентов 130, 140 и 150, в этом примере, IP агент 150 включает в себя буфер 162 транзакций фиксированного размера, который хранит только фиксированное количество данных приостановленных транзакций, в то время как остальные данные транзакций могут по-прежнему удерживаться в блоке 161 хранения данных транзакций. В одном варианте осуществления, со ссылкой на фиг. 2 и фиг. 3, в качестве примера, когда IP агент 150 принимает новые данные транзакции, которые становятся доступными в блоке 162 хранения данных транзакций, которые должны быть переданы в систему 120 коммутации, логическое устройство 165 транзакций посылает REQ в адрес арбитра 110 (через тракт 301). Логическое устройство 165 транзакций посылает новый REQ арбитру 110 независимо от того, был ли принят GNT от арбитра 110.

Кроме того, в соответствии с одним вариантом осуществления, логическое устройство 165 транзакций определяет, имеет ли буфер 161 транзакций достаточно места для буферизации новых данных о транзакции. Если буфер 161 транзакции имеет достаточно места для буферизации новых данных, то логическое устройство 165 транзакций извлекает новые данные транзакций из блока 162 хранения данных транзакций и сохраняет извлеченные данные в буфер 161 транзакций (через тракт 302В). Если буфер 161 транзакции не имеет достаточного места для буферизации новых данных, то логическое устройство 165 транзакций обновляет логическое устройство 170 отслеживания. Логическое устройство 170 отслеживания выполнено с возможностью отслеживать число не подтвержденных REQs, чьи данные не были буферизованы в буфер 161 транзакций. В частности, в соответствии с одним вариантом осуществления, логическое устройство 165 транзакций увеличивает значение счетчика 170 (через тракт 302А), оставляя новые данные транзакций в блоке 162 хранения данных транзакций. Указанное счетчиком 170 значение представляет число не подтвержденного или приостановленного REQs, чьи данные транзакций не были буферизованы в буфер 161 транзакций. То есть, значение счетчика 170 представляет собой число транзакций, которые соответствует отправленным REQs, но их ассоциированные данные транзакций не были буферизованы в буфер 161 транзакций (например, до сих пор хранятся в блоке 162 хранения данных транзакций). Следует отметить, что данные транзакции, сохраненные в буфере 161 транзакций, могут быть обновлены посредством тракта 302В или логического устройства 170 отслеживания (например, соответствующее значение счетчика увеличивается), прежде чем его REQ подается в тракт 301.

Впоследствии, когда GNT принимается от арбитра 110 (по тракту 303), который может быть асинхронным или параллельным по отношению к операциям в трактах 302А и 302В, в одном варианте осуществления, логическое устройство 165 транзакций извлекает следующие данные транзакций соответственно (если существуют) из буфера 161 транзакций и помещает извлеченные данные в систему 120 коммутации (через тракт 304). Кроме того, логическое устройство 165 транзакций определяет, имеется ли какой-либо не подтвержденный или приостановленный REQ посредством проверки значения счетчика 170. Если значение счетчика 170 больше, чем заданное пороговое значение, такое как ноль, то это означает, что существует, по меньшей мере, один неподтвержденный REQ. В такой ситуации, логическое устройство 165 транзакций извлекает следующие данные транзакции соответственно из блока 162 хранения данных транзакций и помещает их в буфер 161 транзакций (по тракту 305), и уменьшает показания счетчика 170 (по тракту 306). В результате, размер буфера 161 может поддерживаться на относительно небольшой величине, с обеспечением достаточной степени латентности доступа к блоку 162 хранения данных транзакций.

Фиг. 4 представляет собой блок-схему алгоритма, иллюстрирующую механизм обработки транзакции в соответствии с другим вариантом осуществления. Как показано на фиг. 4, в этом варианте осуществления, способы, описанные выше, могут быть применены к ситуации, в которой данные нескольких каналов/полос (например, виртуальные каналы/полосы) с множеством классов (например, классы потоков), передаются по межкомпонентному соединению или систему коммутаций. Каждый канал может дополнительно нести несколько различных классов данных. Согласно одному варианту осуществления, буфер (например, буферы 161А - 161N) поддерживается для буферизации данных каждой из комбинации канала/полосы и класса (канал /класс). Для каждого канала/класса, конкретный счетчик (например, счетчики 170) и указатель отсчета (например, указатели 404 отсчета) поддерживаются логическим устройством 403 пополнения буфера, где логическое устройство 403 пополнения буфера осуществляет извлечение соответствующих данных конкретного канала/класса из местоположения, на которое указывает соответствующий указатель отсчета, и размещает извлеченные данные в одном из буферов 161А - 161N, в соответствии с этим конкретным каналом/классом. То есть, для каждой комбинации канал/класс, существует соответствующий указатель отсчета и счетчик. Указатель отсчета указывает на место хранения блока 162 хранения транзакции, в котором в следующие имеющиеся данные соответствующего канала/класса, сохраняются, в то время как соответствующий счетчик сохраняет значение, представляющее номер неподтвержденного REQs этой конкретной комбинации канал/класс.

Когда GNT принят от арбитра 110, арбитр 402 транзакции определяет, какая из комбинаций канал/класс соответствует принятому GNT сигналу, и информирует логическое устройство 403 пополнения буфера о необходимости загрузить данные, ассоциированные с этим конкретным каналом/классом из блока 162 хранения и поместить данные в соответствующий один из буферов 161А - 161N. Арбитр 402 транзакции может поддерживать информацию, идентифицирующую неподтвержденные запросы, и информация может быть использована для ассоциирования принятых GNTs с неподтвержденными REQs. В ответ на это, логическое устройство 403 пополнения буфера проверяет значение счетчика, соответствующее принятому GNT, и извлекает следующие доступные данные транзакций из места хранения, на которое ссылается соответствующий указатель отсчета. В результате, большое количество данных конкретного канала/класса не будет блокировать данные другого канала/класса.

Фиг. 5 представляет собой блок-схему алгоритма, иллюстрирующую способ обработки транзакции протоколов связи с квитированием, согласно одному варианту осуществления. Способ 500 может быть выполнен путем обработки логическим устройством, которое может включать в себя программное обеспечение, аппаратные средства или их сочетание. Способ 500 может быть выполнен IP агентом, как описано выше. Как показано на фиг. 5, на этапе 501, в ответ на данные транзакции, которые будут передаваться посредством межкомпонентного соединения (например, система коммутации, шина), данные транзакции буферизуются в буфер транзакции, если буфер имеет достаточно места. На этапе 502, REQ представляется арбитру, который ассоциирован с межкомпонентным соединением. На этапе 503, в ответ на прием GNT от арбитра, данные транзакции затем извлекаются из буфера транзакции и передаются на межкомпонентное соединение. На этапе 504, логическое устройство обработки определяет, имеется ли какой-либо неподтвержденный REQ, например, путем проверки значения счетчика, который показывает число неподтвержденного REQ. Если это так, то на этапе 505, логическое устройство пополнения буфера осуществляет обработку данных, извлеченных из блока хранения транзакции (например, регистры) и, возможно, уменьшает показания счетчика, если это необходимо.

Фиг. 6А показывает блок-схему, иллюстрирующую систему система-на-кристалле в соответствии с одним вариантом осуществления. Как показано на фиг. 6А, SoC 900 может включать в себя различные компоненты, все из которых могут быть интегрированы на одном полупроводниковом кристалле для обеспечения различных возможностей обработки при высоких скоростях и малой мощности, занимая сравнительно небольшое пространство. SoC 900 включает в себя процессор или центральный процессор (CPU) 901, имеющий один или несколько процессорных ядер 905А и 906В. В различных вариантах осуществления, ядра 905 могут быть относительно простыми ядрами с логикой последовательного выполнения команд или более сложными ядрами с логикой выполнением команд с изменением их очередности. Или может быть использовано объединение простого и сложного ядер на одном SoC. Как видно, ядра 905 могут быть соединены с помощью когерентного межкомпонентного соединения 915, которое дополнительно подключает память 910, например, общий кэш последнего уровня (LLC). Хотя объем вариантов осуществления настоящего изобретения не ограничивается в этом отношении, в одном варианте осуществления когерентное межкомпонентное соединение 915 может быть реализовано в соответствии со спецификацией последовательной кэш-когерентной шиной типа точка-точка (QPI) ™, разработанной Intel Corporation, Santa Clara, California.

Согласно одному варианту осуществления, когерентное межкомпонентное соединение 915 может устанавливать связь через мост 920 с системой 950 коммутаций, которая может быть IOSF системой. Когерентное межкомпонентное соединение 915 дополнительно может устанавливать связь посредством интегрированного контроллера памяти с памятью вне кристалла (не показано для простоты иллюстрации варианта осуществления). Различные компоненты могут соединяться с системой 950 коммутации, которая включает в себя модуль 940 обработки контента (СРМ), который может использоваться для выполнения различных операций, таких как выполнение функций безопасности, криптографических функций и так далее. Кроме того, процессор 945 дисплея может быть частью конвейера обработки медиа информации для воспроизведения видео на ассоциированном дисплее.

Как дополнительно показано, система 950 коммутаций может дополнительно подключаться к другим IP агентам. Кроме того, для обеспечения связи с другими устройствами на кристалле, система 950 коммутации может дополнительно осуществлять связь с контроллером 960 PCIe ™ и контроллером 965 универсальной последовательной шины (USB), оба из которых могут взаимодействовать с различными устройствами в соответствии с этими протоколами. Наконец, как показано в варианте осуществления, мост 970, который может быть использован для связи с дополнительными компонентами других протоколов, такими как протокол открытого ядра (ОСР) или расширенная шинная архитектура микроконтроллеров (AMBA) ARM протокола. Хотя вариант осуществления показан с конкретными компонентами, следует понимать, что объем настоящего изобретения не ограничивается этим, и в различных вариантах осуществления могут применяться дополнительные или другие компоненты.

Более того, следует понимать, что хотя вариант реализации показан в виде одного кристалла SoC, варианты осуществления могут быть дополнительно реализованы в системе, в которой множество микросхем устанавливают связь друг с другом через иной, чем IOSF интерфейс. На фиг. 6В показана блок-схема системы в соответствии с другим вариантом осуществления настоящего изобретения. Как показано на фиг. 6В, SoC 925 включает в себя северный комплекс 902 и южный комплекс 903. Северный комплекс 902 может включать в себя множество компонентов, аналогичные тем, которые обсуждались выше, и дополнительный интерфейс вне кристалла. Соответственно, северный комплекс 902 может осуществлять связь с другой микросхемой 903, которая может включать в себя различные функциональные возможности для обеспечения связи между этими двумя микросхемами, а также с различными устройствами вне кристалла, такими как различные периферийные устройства, в соответствии с одним или более различными характеристиками. В частности, вторая микросхема 903 показана, как включающая в себя интерфейс вне кристалла, чтобы обеспечить связь с микросхемой 902 и который, в свою очередь, взаимодействует с системой 980 коммутации, которая может быть ОСР системой коммутации в соответствии с вариантом осуществления. Как видно, система 980 коммутации дополнительно может быть соединена с различными контроллерами для установления связи с устройствами вне кристалла, включающие в себя контроллер 960 PCIe ™, контроллер 965 USB и мост 985. Мост 958 может быть соединен с другой ОСР системой коммутации и т.д.

Различные IP блоки или агенты, описанные выше, представляют компоненты или функциональные блоки (то есть функциональные блоки), обычно используемые в SoC конструкциях, включающие в себя, но не ограничиваясь ядрами процессора, компонентами кэш-памяти и агентами, контроллерами памяти, I/O контроллерами и интерфейсами, периферийными устройствами и периферийными интерфейсами, видео и аудио компонентами и интерфейсами, компонентами платформы управления и т.д.

Системы межкомпонентного соединения, такие как описаны выше, поддерживают связь между IP блоками с использованием соответствующей проводки и протоколов. Обычно структура данной системы межкомпонентного соединения может содержать матричную "сетку", свободно наполненную систему коммутации, содержащую множество соединений типа точка-точка, общую шинную архитектуру или кольцевую топологию. В одном варианте осуществления, SoC архитектура обобщается таким образом, что каждая система коммутации может быть сконфигурирована в любой из этих топологий. Кроме того, конкретная структура межкомпонентного соединения и протоколы также обобщены в SoC архитектуре так, что различные системы коммутации могут использовать одни и те же или различные структуры межкомпонентного соединения и протоколы. Например, может быть желательно использовать межкомпонентное соединение, которое поддерживает протокол поддержки когерентности кэшей (например, QPI), для связи между ядрами процессора и кэш-памятью IP блоков, в то время как другие структуры и протоколы, такие как ОСР, могут быть использованы для других систем коммутации в архитектуре. Возможно, один протокол может быть использован для всей архитектуры или структуры системы коммутации могут представлять собой часть SoC.

Протокол открытого ядра определяет интерфейс точка-точка между двумя взаимодействующими объектами, такими как IP ядра и модули шинных интерфейсов (оболочки интерфейса шины), также называемые здесь как агенты. Один объект выступает как ОСР ведущий, например, и другие, как ведомые. Только ведущий может представить команды и управлять объектом. Ведомый отвечает на поступившие команды, либо принимая данные от ведущего, либо представляя данные ведущему. Для двух объектов, которые устанавливают одноранговую связь, необходимо иметь два экземпляра ОСР, соединяющий их, где первый объект является ведущим и тот, где первый объект является ведомым.

Характеристики IP ядра определяют, нуждается ли ядро в ведомом, ведущем или в обеих сторонах ОСР; модули оболочки интерфейса должны работать как дополнительная сторона ОСР для каждого подключенного объекта. Передача по этой системе происходит следующим образом. Системный инициатор (как ОСР ведущий) осуществляет передачу команды управления и, возможно, данных в адрес подключенного ведомого (модуль оболочки шинного интерфейса). Модуль интерфейса передает запрос через систему шин на кристалле. ОСР не указывает на функциональность встроенной шины. Вместо этого структура интерфейса преобразует ОСР запрос во встроенную шину обмена. Принимающий модуль оболочки шинного интерфейса (в качестве ОСР ведущего) преобразует операцию встроенной шины в нормативную ОСР команду. Целевая система (ОСР ведомого) принимает команду и осуществляет требуемое действие.

Каждый экземпляр ОСР выполнен (выбором сигналов или битовой шириной конкретного сигнала) на основе требований подключенного объекта, и не зависит от других. Например, системные инициаторы могут потребовать дополнительные адресные биты в их ОСР экземплярах для определения системных целей; дополнительные адресные биты могут быть использованы встроенной шиной для выбора целевой шины, к которой обращается системный инициатор.

ОСР является гибким. Есть несколько полезных моделей для обеспечения коммуникации IP ядер друг с другом. Некоторые используют конвейер для улучшения пропускной способности и характеристик латентности. Другие используют модели многотактового доступа, где сигналы удерживаются статически в течение нескольких тактов, чтобы упростить временной анализ и уменьшить область применения. Поддержка этого шаблона поведения может оказываться путем использования синхронных сигналов квитирования, которые позволяют как ведущему, так и ведомому осуществлять управления, когда сигналы могут быть изменены.

Согласно одному варианту осуществления устройство включает в себя блок хранения данных транзакций для хранения данных транзакций, подлежащих передаче по межкомпонентному соединению системы обработки данных; буфер транзакций, соединенный с блоком хранения данных транзакций для буферизации, по меньшей мере, части данных транзакций и логическое устройство транзакции, соединенное с блоком хранения данных транзакций и буфером транзакций для передачи сигнала с запросом (REQ) в адрес арбитра, ассоциированного с межкомпонентным соединением, в ответ на первые данные транзакции, которые становятся доступными в блоке хранения данных транзакций, в ответ на принятый сигнал разрешения (GNT) от арбитра, извлечение вторых данных транзакции из буфера транзакций и передачу вторых данных транзакции в межкомпонентное соединение и пополнение буфера транзакций с третьими данными транзакций, извлеченными из блока хранения данных транзакций, после того, как вторые данные транзакций были переданы на межкомпонентное соединение. Буфер транзакций буферизует заранее определенное фиксированное количество данных транзакций. Логическое устройство транзакций определяет факт заполнения буфера транзакции в ответ на первые данные транзакций и буферизует первые данные транзакций в буфере транзакций, если буфер транзакций не заполнен. Логическое устройство транзакций увеличивает значение счетчика в ответ на определение, что буфер транзакций заполнен, после того, как REQ был передан. Счетчик показывает количество REQs, которые приостановлены и их ассоциированные данные транзакций не были буферизованы в буфере транзакций. Третьи данные транзакции буферизуются в буфер транзакций, только если значение счетчика превышает нулевое значение. Логическое устройство транзакций уменьшает значение счетчика после того, как вторые данные транзакции была переданы на межкомпонентное соединение.

Набор команд или архитектура системы команд (ISA) является частью компьютерной архитектуры, относящейся к программированию, и может включать в себя собственные данные, команды, регистровую архитектуру, способы адресации, архитектуру памяти, обработку прерываний и исключений и внешний ввод и вывод (I/O). Термин команда, как правило, относится здесь к макрокоманде - это команды, которые поставляются в процессор (или преобразователь команды, который преобразовывает (например, с помощью статического двоичного преобразования, динамического бинарного преобразования, включающее в себя динамическую компиляцию), трансформирует, эмулирует или иным образом преобразовывает команду из одной или более других команд, которые будут обрабатываться процессором) для выполнения - в отличие от микрокоманд или микроопераций (микрокоманды) - что является результатом декодирования макрокоманд декодером процессора.

ISA отличается от микроархитектуры, которая является внутренней структурой процессора, реализующей набор команд. Процессоры с различными микроархитектурами могут совместно использовать общий набор команд. Например, процессоры Intel® Pentium 4, процессоры Intel® Core ™ и процессоры Advanced Micro Devices, Inc. Sunnyvale CA реализовывают почти идентичные версии х86 набора команд (с некоторыми расширениями, которые были добавлены в более новых версиях), но имеют различные внутренние структуры. Например, та же архитектура регистра ISA может быть реализована по-разному в разных микроархитектурах с использованием хорошо известных способов, включающие в себя выделенные физические регистры, один или несколько динамически выделенных физических регистров, используя механизм переименования регистров (например, использование Таблицы псевдонимов регистров (RAT), Буфера переупорядочивания (ROB) и глобального внутрисхемного регистра процессорной логики; использование множества карт и пула регистров) и т.д. Если не указано иное, фразы архитектура регистров, набор регистров и регистр используются здесь для обозначения того, что доступно для программного обеспечения/программиста и способ, в котором команды определяют регистры. Там, где желательно указать на специфичность, будут использоваться прилагательные логическое, архитектурное представление или программное обеспечение для обозначения регистров/наборов в архитектуре регистров, в то время, как различные прилагательные будет использоваться для определения регистров в заданной микроархитектуре (например, физический регистр, буфер переупорядочения, глобальный внутрисхемный регистр процессорной логики, пул регистров).

Набор команд включает в себя один или несколько форматов команд. Данный формат команд определяет различные поля (число битов, расположение битов), чтобы указать, среди прочего, операцию, которая должна быть выполнена (код операции) и операнд (ы), по которым операция должна быть выполнена. Некоторые форматы команд дополнительно будут разбиты посредством определения шаблонов команд (или субформаты). Например, шаблоны команд заданного формата команд могут быть определены, чтобы иметь различные подмножества полей формата команд (включенные в состав поля, как правило, в том же порядке, но, по меньшей мере, у некоторых есть разные позиции битов, потому что включены в состав меньших полей) и/или определены, чтобы иметь заданное поле, что интерпретируется по-разному. Таким образом, каждая команда ISA выражается с помощью заданного формата команд (и, если определено, в заданном одном из шаблонов команд этого формата команд) и включает в себя поля для указания операции и операндов. Например, примерная команда ADD имеет специфический операнд и формат команд, который включает в себя поле операнда, чтобы указать поля кода операций и операнда для выбора операнда (источник 1/получатель и источник 2); и появление этой ADD команды в потоке команд будет иметь конкретный контент в полях операндов, которые выбирают конкретные операнды.

Научные, финансовые, общего назначения, RMS (понимание, выемка и синтез), визуальные и мультимедийные приложения (например, 2D/3D графика, обработка изображений, сжатие видео/распаковка, алгоритмы распознавания голоса и аудио манипуляции) часто требуют выполнения однотипных операций обработки большого количества элементов данных (именуемые как "параллелизм на уровне данных"). Один поток команд - много потоков данных (SIMD) относится к типу команд, который вызывает процессор выполнить операцию обработки множества элементов данных. SIMD технология особенно подходит для процессоров, которые могут логически разделять биты в регистре на количество элементов данных фиксированного размера, каждое из которых представляет собой отдельное значение. Например, биты в 256 - битовом регистре могут быть заданы как исходный операнд для обработки как четырех отдельных 64-битовых упакованных элементов данных (счетверенное слово (Q) размера элементов данных), восемь отдельных 32-битовых упакованных элементов данных (сдвоенное слово (D) размера элементов данных), шестнадцать отдельных 16-битовых упакованных элементов данных (слово (W) размера данных) или тридцать два отдельных 8-битовых элементов данных (байт (В) размера элементов данных). Этот тип данных упоминается как тип упакованных данных или тип данных вектора, и операнды этого типа данных, называются как операнды упакованных данных или вектор-операнд. Другими словами, элемент упакованных данных или вектор относится к последовательности элементов упакованных данных, и операнд упакованных данных или вектор-операнд является исходным или конечным операндом SIMD команды (также известная как команда упакованных данных или векторная команда).

В качестве примера, один тип SIMD команды определяет одновекторную операцию, которая должна быть выполнена на двух исходных вектор-операндах вертикально для генерации вектор-операнда получателя (также называемый как вектор-операнд результат) того же размера, с таким же количеством элементов данных и в том же порядке элемента данных. Элементы данных в исходном вектор-операнде называются элементами данных источника, в то время как элементы данных в вектор-операнде получателя называются элементами данных получателя или результата. Эти вектор-операнды источника имеют тот же самый размер и содержат элементы данных одной и той же ширины и, таким образом, они содержат одинаковое количество элементов данных. Элементы данных источника в одних и тех же позициях битов в двух вектор-операндах источника образуют пары элементов данных (также упоминаемые как соответствующие элементы данных, то есть, элемент данных в позиции 0 элемента данных каждого исходного операнда соответствуют, элементу данных в позиции 1 элемента данных каждого исходного операнда и так далее). Операция, определенная данной SIMD командой выполняется отдельно на каждой из этих пар элементов данных источника, чтобы генерировать соответствующий ряд элементов данных результата и, таким образом, каждая пара элементов данных источника имеет соответствующий элемент данных результата. Поскольку операция является вертикальной и вектор-операнд результат имеет такой же размер, имеется такое же число элементов данных и результирующие элементы данных хранятся в том же порядке элемента данных как вектор-операнды источника, элементы данных результата находятся на тех же битовых позициях вектор-операнда результата, как их соответствующие пары элементов данных источника в вектор-операндах источника. В дополнение к этому примерному типу SIMD команд, существует множество других типов SIMD команд (например, есть только один или более чем два вектор-операндов источника, которые работают горизонтально, что генерирует вектор-операнд результата, имеющий другой размер, различные размеры элементов данных и/или другой порядок элементов данных). Следует иметь в виду, что вектор-операнд получателя (или операнд получатель) определяется как непосредственный результат выполнения операции, указанной командой, включающий в себя сохранение операнда получателя на позиции (будь то регистр или адрес памяти, указанный этой командой) так, что она может быть доступна в качестве операнда источника посредством другой команды (с указанием той же позиции другой командой).

Технология SIMD, как, например, используемая процессорами Intel® Core ™, имеющая набор команд, включающая в себя х86, ММХ ™, потоковые SIMD расширения (SSE), SSE2, SSE3, SSE4.1 и SSE4.2 команды, что позволяет существенно улучшить производительность приложений. Описание дополнительного набора SIMD расширений, относящиеся к Расширению системы команд (AVX) (AVX1 и AVX2) и используя схему кодирования вектора расширений (VEX), было опубликовано (например, см Intel® 64 и IA-32 Руководство архитектуры разработчиков программного обеспечения, октябрь 2011; и см. Intel® Справочник по программированию систем команд расширения, июнь 2011).

Варианты осуществления команды, описанные в данном документе, могут быть реализованы в различных форматах. Кроме того, ниже приведено подробное описание примерных систем, архитектур и конвейеров. Варианты осуществления команды могут быть реализованы на таких системах, архитектурах и конвейерах, но не ограничиваются подробно описанными ниже.

VEX кодирование позволяет командам иметь более, чем два операнда и позволяет SIMD векторным регистрам иметь длину больше, чем 128 бит. Использование префикса VEX предусматривается для трехоперандного (или более) синтаксиса. Например, предыдущие двухоперандные команды выполняют операции, такие как А=А+В, которые перезаписывают исходный операнд. Использование VEX префикса позволяет операндам выполнить неразрушающие операции, такие как А=В+С.

Фиг. 7А показывает примерный формат команд AVX, включающий в себя VEX префикс 2102, вещественное поле 2130 кода операции, Mod R/M байт 2140, SEB байт 2150, поле 2162 смещения и IMM8 2172. Фиг. 7В иллюстрирует, какие поля, показанные на фиг. 7А, составляют полное поле 2174 кода операции и поле 2142 базовой операции. Фиг. 7С иллюстрирует, какие поля, показанные на фиг. 7А, составляют поле 2144 индексного регистра.

VEX префикс (байты 0-2) 2102 кодируется как три байта. Первый байт является форматом поля 2140 (VEX байт 0, биты [7:0]), который содержит эксплицитное значение байта С4 (уникальный значение, используемое для различения формата команд С4).

Второй-третий байты (VEX байты 1-2) включают в себя ряд битовых полей, обеспечивающих специфическую способность. В частности, REX поле 2105 (VEX байт 1, биты [7-5]) состоит из VEX.R битового поля (VEX байт 1, бит [7] - R), битовое поле VEX.X (VEX байт 1, бит [6] - X) и битовое поле VEX. B (VEX байт 1, бит [5] - В). Другие поля команд кодирования ниже трех бит индексов регистра, как известно в данной области техники, (rrr, ххх и bbb), так что Rrrr, Хххх и Bbbb могут быть образованы путем добавления VEX.R, VEX.X и VEX.B. Поле 2115 карты кода операции (VEX байт 1, бит [4:0] - mmmmm) включает в себя контент, чтобы закодировать подразумеваемый начальный байт кода операции. W поле 2164 (VEX байт 2, бит [7] - W) - представлено нотацией VEX.W и предоставляет различные функции в зависимости от команды. Роль VEX.vvvv 2120 (VEX байт 2, бит [6:3] -vvvv) может включать в себя следующее: 1) VEX.vvvv кодирует первый регистровый операнд источника, указанный в перевернутой (1S дополнение) форме и действует для команд с 2 или более исходными операндами; 2) VEX.vvvv кодирует регистровый операнд получателя, указанный в 1s форме дополнения для некоторых векторных сдвигов; или 3) VEX.vvvv не кодирует любой операнд, поле зарезервировано и должно содержать 1111b. Если VEX.L 2168 размер поля (VEX байт 2, бит [2] -L)=0, то это указывает на 128 битовый вектор; если VEX.L=1 указывает на 256 битовый вектор. Префикс кодирования поля 2125 (VEX байт 2, бит [1:0] -рр) предоставляет дополнительные биты для поля базовой операции.

Вещественное поле 2130 кода операции (байт 3) также известно как байт-код операции. Часть кода операции указывается в этом поле. MOD R / М поле 2140 (байт 4) включает в себя MOD поле 2142 (биты [7-6]), Reg поле 2144 (биты [5-3]) и R / М поле 2146 (биты [2-0]). Роль Reg поля 2144 может включать в себя следующее: кодирование либо регистрового операнда получателя или регистрового операнда источника (rrr из Rrrr) или рассматриваться как расширение кода операции и не используется для кодирования любого операнда команды. Роль R / М поля 2146 может включать в себя следующее: кодирование операнда команды, который ссылается на адрес памяти, или кодирование либо регистрового операнда получателя, либо регистрового операнда источника.

Масштаб, индекс, база (SIB) - контент поля 2150 масштаба (байт 5) включает в себя SS2152 (биты [7-6]), которое используется для генерации адреса памяти. Контент SIB.xxx 2154 (биты [5-3]) и SIB.bbb 2156 (биты [2-0]) были ранее упомянуты в связи с регистровыми индексами Хххх и Bbbb. Поле 2162 смещения и непосредственное поле (IMM8) 2172 содержат адресные данные.

Формат векторных команд представляет собой формат команд, который подходит для векторных команд (например, существуют определенные поля, специфичные для векторных операций). Хотя варианты осуществления описаны, где обе векторные и скалярные операции поддерживаются форматом векторных команд, альтернативные варианты осуществления используют только векторные операции формата векторных команд.

Фиг. 8А, 8В и 8С являются блок-схемами, иллюстрирующие общий формат векторных команд и их шаблоны команд в соответствии с вариантами осуществления изобретения. На фиг. 8А представлена блок-схема, иллюстрирующая общий формат векторных команд и класс А их шаблонов команд в соответствии с вариантами осуществления изобретения; на фиг. 8В изображается блок-схема, иллюстрирующая общий формат векторных команд и класс В их шаблонов команд в соответствии с вариантами осуществления изобретения. В частности, общий формат 2200 векторных команд, который определяется шаблонами команд класса А и класса В, оба из которых не включают в себя шаблоны команд доступа 2205 к памяти и шаблоны команд доступа 2220 к памяти. Термин общий в контексте формата векторных команд относится к формату команды, который не связан с каким-либо конкретным набором команд.

Хотя варианты осуществления настоящего изобретения будут описаны для случая, в котором формат векторных команд поддерживает следующие: 64 байтовую длину вектор-операнда (или размер) с 32 битами (4 байта) или 64 бит (8 байт) ширины элемента данных (или размеры) (и, следовательно, 64 байт вектор состоит из либо 16 элементов сдвоенного размера или, альтернативно, 8 элементов счетверенного слова); 64 байтовую длину вектор-операнда (или размер) с 16 бит (2 байта) или 8 бит (1 байт) элемента данных ширины (или размеров); 32 байт длина вектор-операнда (или размер) с 32 бит (4 байта), 64 бит (8 байт), 16 бит (2 байта) или 8 бит (1 байт) элемента данных ширины (или размеров); и 16 байтовую длину вектор-операнда (или размер) с 32 бит (4 байта) 64 бит (8 байт), 16 бит (2 байта) или 8 бит (1 байт) элемента данных ширины (или размеров); альтернативные варианты осуществления могут поддерживать больше, меньше и/или различные размеры вектор-операндов (например, 256 байт вектор-операнды) с больше, меньше или различной шириной элементов данных (например, 128 бит (16 байт) шириной элементов данных).

Шаблоны команд класс А на фиг. 8А включают в себя: 1) в пределах шаблонов команд без доступа 2205 к памяти показаны без доступа к памяти, шаблон команды всего цикла управления 2210 и без доступа к памяти, шаблон команды операции 2215 преобразования данных; и 2) в пределах шаблонов команд доступа 2220 к памяти, как показано с доступом к памяти, шаблон команд временного 2225 шаблон доступа к памяти, шаблон команд невременного 2230 доступа к памяти. Шаблоны команд класса В на фиг. 8В включают в себя: 1) в пределах шаблонов команд без доступа 2205 к памяти показаны без доступа к памяти, управление маски записи, шаблон команды частичного цикла управления 2210 и без доступа к памяти, управление маски записи, шаблон команды типа vsize операции 2217; и 2) в пределах шаблонов команд доступа 2220 к памяти, как показано с доступом к памяти, управление 2227 маски записи.

Общий формат 2200 векторных команд включает в себя следующие поля, перечисленные ниже в порядке, показанном на фиг. 8А и фиг. 8В. Поле 2240 формата представляет собой конкретное значение (значение идентификатора формата команды) в данном поле, которое однозначно идентифицирует формат векторной команды и, таким образом, вхождения команд формат векторных команд в потоках команд. Таким образом, это поле является возможным, в том смысле, что оно не нужно для набора команд, который имеет только общий формат векторных команд. Поле 2242 базовой операции определяет контент, который отличает разные базовые операции.

Поле 2244 регистрового индекса, контент которого, напрямую или через генерацию адресов, определяет местоположения операндов источника и получателя, будь то в регистрах или в памяти. Они включают в себя достаточное количество битов для выбора N регистров из Р×Q (например, 32×512, 16×128, 32×1024, 64×1024) набора регистров. Хотя в одном варианте осуществления N может иметь до трех регистров источника и одного регистра получателя, альтернативные варианты осуществления могут поддерживать больше или меньше регистров источника и получателя (например, может поддерживать до двух источников, где один из этих источников также действует как получатель, может поддерживать до для трех источников, где один из этих источников также выступает в качестве получателя, может поддерживать до двух источников и одного получателя).

Поле 2246 модификатора, контент которого отличает вхождение команд в общий формат векторных команд, который определяет доступ к памяти от тех, которые этого доступа не имеют; то есть, между шаблонами команд без доступа 2205 и шаблонами команд с доступом 2220 к памяти. Операции доступа к памяти считывают и/или записывают в иерархии памяти (в некоторых случаях с указанием адресов источника и/или получателя с помощью значений в регистрах) в то время, как операции без доступа к памяти не делают этого (например, источник и получатель являются регистрами). В то время, как в одном варианте осуществления данное поле также выбирает между тремя различными способами выполнения вычислений адреса памяти, альтернативные варианты осуществления могут поддерживать больше, меньше или различные способы для выполнения расчетов адреса памяти.

Поле 2250 дополнительного действия, контент которого отличает одну из множества различных операций, подлежащих выполнению в дополнение к базовой операции. Это поле является конкретным условием. В одном варианте осуществления настоящего изобретения, данное поле разделено на поле 2268 класса, альфа поле 2252 и бета поле 2254. Поле 2250 дополнительного действия позволяет общим группам операций быть выполненными в одной команде, а не посредством 2, 3 или 4 команд. Поле 2260 масштаба, контент которого позволяет выполнить масштабирование контента поля индекса для генерации адресов памяти (например, для генерации адресов, которые использует 2scale* Индекс + База).

Поле 2262А смещения, контент которого используется как часть генерации адресов памяти (например, для генерации адресов, которые используют 2scale * Индекс + База + Смещение). Поле 2262В коэффициента сдвига (обратите внимание, что размещение рядом поля 2262А смещения прямо над полем 2262В коэффициента сдвига указывает на используемый один или другой), контент которого используется как часть генерации адресов; что определяет коэффициент сдвига, который должен быть масштабирован размером доступа (N) к памяти - где N это количество байтов в доступе к памяти (например, для генерации адресов, которые использует 2scale * Индекс + База + масштабированное смещение). Избыточные младшие биты игнорируются и, следовательно, контент поля коэффициента сдвига умножается на общий размер (N) операндов памяти в целях получения окончательного смещения, которое будет использоваться при расчете эффективного адреса. Значение N определяется аппаратными средствами процессора во время работы на основании поля 2274 полного кода операции (описано ниже) и поля 2254С манипулирования данными. Поле 2262А смещения и поле 2262В коэффициента сдвига являются возможными, в том смысле, что они не используются для шаблонов команд без доступа 2205 к памяти и/или различные варианты осуществления могут реализовать только один или ни одного из двух.

Поле 2264 ширины элемента данных, контент которого отличает, которая одна из множества значений ширины элементов данных должна быть использована (в некоторых вариантах осуществления для всех команд, в других вариантах осуществления для только некоторых команд). Это поле является возможным, в том смысле, что оно не нужно, если поддерживается только одна ширина элемента данных и/или ширины элементов данных поддерживаются с помощью некоторого аспекта кода операции.

Поле 2270 маски записи, контент которого управляет на позиции каждого элемента данных, отражает ли эта позиция элемента данных в вектор-операнде получателя результат базовой операции и операции дополнения. Шаблоны команд класс А поддерживает слияния-маскировку бита на предоставление права доступа на запись, в то время как шаблоны команд класса В поддерживают как слияние-обнуление-маскировку бита на предоставление права доступа на запись. При слиянии, векторные маски позволяют любому набору элементов получателя быть защищенными от обновления во время выполнения какой-либо операции (указанной базовой операцией и операцией дополнения); в другом варианте осуществления сохраняется прежнее значение каждого элемента получателя, где соответствующая битовая маска имеет 0. В отличие от этого, когда обнуление векторных масок позволяет любому набору элементов получателя быть обнуленным во время выполнения какой-либо операции (указанной базовой операцией и операцией дополнения); в одном варианте осуществления, элемент получателя установлен на 0, когда соответствующая битовая маска имеет значение 0. Подмножество этой функциональности предоставляет возможность контролировать длину вектора выполняемой операции (то есть, диапазон элементов модифицируется от первого до последнего); тем не менее, это является возможным, что элементы, которые модифицированы, являются последовательными. Таким образом, поле 2270 маски записи позволяет выполнить частичные векторные операций, включающие в себя загрузку, хранение, арифметическое вычисление, логическое вычисление и т.д. Хотя варианты осуществления настоящего изобретения описаны, где контент поля 2270 маскировки бита на предоставление права доступа на запись выбирает один из нескольких регистров маскировки, который содержит маскировку бита на предоставление права доступа на запись, которые будут использоваться (и, таким образом, контент поля 2270 маскировки бита на предоставление права доступа на запись косвенно идентифицирует, что маскировка должна быть выполнена), альтернативные варианты осуществления вместо этого или дополнительно позволяют, чтобы контент поля 2270 маскировки бита на предоставление права доступа на запись непосредственно указывал на выполнение маскировки.

Непосредственное поле 2272, контент которого указывает на непосредственную спецификацию. Это поле не является обязательным, в том смысле, что отсутствует в варианте реализации общего формата вектора, который не поддерживает непосредственную операцию, и его нет в командах, которые не используются немедленно. Поле 2268 класса, контент которого различает различные классы команд. На фиг. 8А и 8В, контент этого поля выбирает команды класса А и класса В. На фиг. 8А и фиг. 8В, закругленные угловые квадраты используются для обозначения конкретного значения в поле (например, класс А 2268А и класс В 2268В для поля 2268 класса соответственно на фиг. 8А и фиг. 8В).

В случае шаблонов команд без доступа 2205 к памяти класса А, альфа поле 2252 интерпретируется как RS поле 2252А, контент которого отличает один из различных типов операций дополнения, который должен быть выполнен (например, шаблоны команд округления 2252А.1 и преобразования 2252А.2 данных соответственно, указано без доступа к памяти, операция 2210 округления и без доступа к памяти, операция 2215 преобразования данных), в то время как бета поле 2254 отличает, какая из операций указанного типа выполняться. В шаблонах команд без доступа 2205 к памяти, поле 2260 масштаба, поле 2262А смещения и поле 2262В смещения масштаба отсутствуют.

В шаблоне команды операции 2210 управления полным округлением без доступа к памяти, бета поле 2254 интерпретируется, как поле 2254А управления округлением, контент которого обеспечивает статическое округление. Хотя в описанных вариантах осуществления изобретения поле 2254А управления округлением включает в себя поле 2256 подавления всех исключений с плавающей запятой (SAE) и поле 2258 управления округлением, альтернативные варианты осуществления могут поддерживать кодирование в соответствии с данными концепциями в том же поле или только иметь одну или другую из этих концепций/полей (например, может иметь только поле 2258 управления округлением).

SAE поле 2256, контент которого отличает, сообщать или нет о событии исключения; когда контент SAE поля 2256 указывает, что функция подавления активна, то данная команде не сообщает каким-либо флагом исключений с плавающей запятой и не активирует обработчик исключений с плавающей запятой.

Поле 2258 управления операцией округления, контент которого отличает, какая из групп операций округления выполняется (например, округление с повышением, округление с понижением, округление к нулю и округление к ближнему). Таким образом, поле 2258 управление операцией округления позволяет изменить режим округления по предписанию. В одном из вариантов осуществления изобретения, где процессор включает в себя регистр управления для указания режимов округления, контент поля 2250 управления округлением замещает значение регистра.

В шаблоне команды типа операции 2215 преобразования данных без доступа к памяти, бета поле 2254 интерпретируется как поле 2254В преобразования данных, контент которого отличает один из ряда данных преобразований, который должен быть выполнен (например, без преобразования данных, выборка, трансляция).

В случае шаблона команды с доступом 2220 к памяти класса А, альфа поле 2252 интерпретируется как поле 2252В маркера замещения, контент которого отличает которой один из маркеров замещения будет использоваться (на фиг. 8А, временной 2252В.1 и невременной 2252В.2 соответственно, указанный для доступа к памяти, временной 2225 шаблон команды и доступ к памяти, невременной 2230 шаблон команд), в то время как бета поле 2254 интерпретируется как поле 2254С манипулирования данными, контент которого отличает, которая одна из ряда операций манипулирования данными (также известные как примитивы) должна быть выполнена (например, нет манипуляции; вещание; преобразование с повышением источника; и преобразование с понижением). Шаблоны команд доступа 2220 к памяти включают в себя поле 2260 масштаба и, возможно, поле 2262А смещения или поле 2262В смещения масштаба.

Команды вектора памяти выполняют загрузку вектора из и хранение вектора в памяти, с поддержкой преобразования. Как и в случае обычных векторных команд, команды вектора памяти передачи данных из/в память поэлементным образом, элементами, которые фактически переданы, указываются контентом векторной маски, который выбирается, как маска предоставления права доступа на запись.

Временные данные представляют собой данные, вероятно, которые будут повторно использоваться достаточно скоро, чтобы извлечь выгоду из кэширования. Это, однако, подсказка, и разные процессоры могут реализовать его по-разному, в том числе полностью игнорируя подсказку. Невременные данные представляют собой данные, которые вряд ли будут повторно использоваться достаточно скоро, чтобы извлечь выгоду из кэширования в кэше первого уровня, и должен быть отдан приоритет для согласования. Это, однако, является подсказкой, и разные процессоры могут реализовать его по-разному, в том числе полностью игнорируя подсказку.

В случае шаблонов команд класса В, альфа поле 2252 интерпретируется как поле 2252С управления (Z) маскировки бита на предоставление права доступа на запись, контент которого определяет факт того, что управление маскировкой бита на предоставление права доступа на запись посредством поля 2270 маскировки бита на предоставление права доступа на запись должно являться слиянием или обнулением.

В случае шаблонов команд без доступа 2205 к памяти класса В, часть бета поля 2254 интерпретируется как RL поле 2257А, контент которого отличает которой один из различных типов дополнительных операций должен быть выполнен (например, округление 2257А 0,1 и длина вектора (VSIZE) 2257А.2 соответственно, указанная для без доступа к памяти, управление маскировкой бита на предоставление права доступа на запись, шаблон команды типа операции 2212 управления частичного округления и без доступа к памяти, управление маскировкой бита на предоставление права доступа на запись, шаблон команды типа операции 2217 VSIZE), в то время как остальная часть бета поля 2254 отличает, какая из операций указанного типа должна быть выполнена. В шаблонах команд без доступа 2205 к памяти, поле 2260 масштаба, поле 2262А смещения и поле 2262В масштаба смещения не представлены.

Без доступа к памяти, управление маскировкой бита на предоставление права доступа на запись, шаблон команд типа операции 2210 управления частичным округлением, остальная часть бета поля 2254 интерпретируются как поле 2259А операции округления и функция отчетности события исключения отключена (данная команда не сообщает о каком-либо флаге исключения с плавающей запятой и не инициирует обработчик исключений с плавающей запятой).

Поле 2259А управления действием округления, являясь просто полем 2258 управления операцией округления, контент которого определяет какая из групп округления выполняется (например, округление с повышением, округление с понижением, округление к нулю и округление к ближнему). Таким образом, поле 2259А управления действием округления позволяет изменить режим округления по указанию. В одном из вариантов осуществления изобретения, где процессор включает в себя регистр управления для указания режимов округления, контент поля 2250 управления операцией округления замещает значение регистра.

В шаблоне команд типа операции 2217 VSIZE управление маскировкой бита на предоставление права доступа на запись без доступа к памяти, остальная часть бета поля 2254 интерпретируются как поле 2259В вектора длины, контент которого отличает, которая одна из ряда данных векторных длин должна быть выполнена (например, 128,256 или 512 байт).

В случае шаблона команды доступа 2220 к памяти класса В, часть бета поля 2254 интерпретируется как поле 2257 В вещания, контент которого отличает будет или нет выполняться операция манипулирования данными типа вещания, в то время как остальная часть бета поля 2254 интерпретируется поле 2259В векторной длины. Шаблоны команд доступа 2220 к памяти включают в себя поле 2260 масштаба и, возможно, поле 2262А смещения или поле 2262В масштаба смещения.

Что касается общего формата 2200 векторных команд, поле 2274 всего кода операции показана, включающее в себя поле 2240 формата, поле 2242 базовой операции и поле 2264 ширины элемента данных. В то время, как один из вариантов осуществления, где показана поле 2274 всего кода операции включает в себя все эти поля, поле 2274 всего кода операции включает в себя менее, чем все эти поля в вариантах осуществления, которые не поддерживают их все. Поле 2274 всего кода операции предоставляет код операции (код операции).

Поле 2250 дополнительного действия, поле 2264 ширины элемента данных и поле 2270 маскировки бита на предоставление права доступа на запись позволяют указать эти признаки в каждой команде в общем формате векторных команд. Объединение поля маскировки бита на предоставление права доступа на запись маски и поля ширины элемента данных создают типовые команды, которые позволяют применить маску, основанную на различных значениях ширины элементов данных.

Различные шаблоны команд, находящиеся в классе А и классе В, полезны в различных ситуациях. В некоторых вариантах осуществления изобретения, разные процессоры или различные ядра процессора, могут поддерживать только класс А, только класс В или оба класса. Например, высокая производительность ядра общего назначения с логикой изменения последовательности команд, предназначенное для универсальных вычислений, может поддерживать только класс В, ядро, предназначенное в первую очередь для работы с графикой и/или научными вычислениями может поддерживать только класса А, и ядро, предназначенное для обоих может поддерживать оба типа (конечно, ядро, которое имеет некоторое сочетание шаблонов и команд обоих классов, но не все шаблоны и команды обоих классов находится в компетенции данного изобретения). Кроме того, один процессор может содержать несколько ядер, каждое из которых поддерживают тот же класс или в котором разные ядра поддерживают различные классы. Например, в процессоре с отдельным графическим и универсальным ядрами, одно из графических ядер, предназначенное, главным образом, для графики и/или научных вычислений, может поддерживать только класса А, в то время как одно или более из ядер общего назначения может иметь высокую производительность ядра общего назначения с выполнением с изменением последовательности команд и переименованием регистров, предназначен для универсальных вычислений, которые поддерживают только класса В. Другой процессор, который не имеет отдельного графического ядра, может включать в себя еще одно универсальное упорядоченное ядро или с логикой изменения последовательности выполнения команд, которые поддерживают оба класс А и класс В. Конечно, признаки одного класса также могут быть реализованы в другом классе в различных вариантах осуществления изобретения. Программы, написанные на языке высокого уровня, будут поставлены (например, точно скомпилированы или статически скомпилированы) в разнообразных исполняемых формах, включающие в себя: 1) форму, имеющую только команды класса(ов), поддержанные целевым процессором для выполнения; или 2) форму, имеющую альтернативные процедуры, написанные с использованием различных комбинаций команд всех классов и имеющие код управления потоком, который выбирает подпрограммы для выполнения на основании команд, поддерживаемых процессором, который в настоящее время выполняет код.

На фиг. 9 показана блок-схема, иллюстрирующая примерный конкретный формат векторных команд в соответствии с вариантами осуществления изобретения. На фиг. 9 показан конкретный формат 2300 векторных команд, который является конкретным, в том смысле, что он определяет местоположение, размер, интерпретацию и порядок полей, а также значения для некоторых из этих полей. Конкретный формат 2300 векторных команд может быть использован для расширения х86 набора команд и, таким образом, некоторые поля могут быть одинаковыми или используются в существующем х86 наборе команд и их расширения (например, AVX). Этот формат по-прежнему соответствует полю префикса кодирования, вещественному полю кода операции, MOD R / М полю, SIB полю, полю смещения и непосредственным полям существующего х86 набора команд с расширениями. Проиллюстрированы поля, показанные на фиг. 8, в которые, поля, показанные на фиг. 9, сопоставлены.

Следует понимать, что, хотя варианты осуществления настоящего изобретения описаны со ссылкой на конкретный формат 2300 векторных команд в контексте общего формата 2200 векторных команд для иллюстративных целей, и что изобретение не ограничено конкретным форматом 2300 векторных команд, за исключением формулы изобретения. Например, общий формат 2200 векторных команд предусматривает целый ряд возможных размеров для различных полей, в то время как конкретный формат 2300 векторных команд показан как имеющий поля конкретных размеров. В качестве конкретного примера, в то время как поле 2264 ширины элемента данных показано как одно битовое поле в конкретном формате 2300 векторных команд, но изобретение не ограничено таким образом, (то есть, общий формат 2200 векторных команд) предусматривает другие размеры поля 2264 ширины элемента данных).

Общий формат 2200 векторных команд включает в себя следующие поля, перечисленные ниже в порядке, показанном на фиг. 9А. EVEX префикс (Байты 0-3) 2302 - кодируется в форме четырех байт. Поле 2240 формата (EVEX Байт 0, биты [7:0]) - первый байт (EVEX байт 0) является полем 2240 формата и содержит 0×62 (уникальное значение, используемое для различения формата векторной команды в одном варианте осуществления изобретения). Второй - четвертый байты (EVEX байты 1-3) включают в себя ряд битовых полей, обеспечиваюпшх определенную возможность.

REX поле 2305 (EVEX Байт 1, биты [7-5]) - состоит из EVEX. R битового поля (EVEX байт 1, бит [7] - R), EVEX. X битовое поле (EVEX байт 1, бит [6] - X) и 2257 ВЕХ байт 1, бит [5] - В). Битовые поля EVEX. R, EVEX. X и EVEX. B обеспечивают ту же функциональность, что и соответствующие битовые поля VEX, и закодированы с 1 с дополнительную форму, т.е. ZMM0 кодируется как 1111b, ZMM15 кодируется как 0000В. Другие поля команд кодируют нижние три бита регистра индексов, как известно в данной области техники (rrr, ххх и bbb), так что Rrrr, Хххх и Bbbb могут быть образованы путем добавления EVEX. R, EVEX. X и EVEX. B.

REX′ поле 2210 - первая часть REX′ поля 2210 является EVEX.R′ битовым полем (EVEX Байт 1, бит [4] - R′), которая используется для кодирования либо верхнего 16 или нижнего 16 расширенного 32 набора регистра. В одном варианте осуществления настоящего изобретения, этот бит, наряду с другими, как указано ниже, хранится в битовой перевернутом формате, чтобы отличить (в известного х86 32-битного режима) от BOUND команды, реальный опкод составляет 62, что но не учитывается MOD R / М (об этом ниже) полем значение 11 в MOD поле; альтернативные варианты осуществления изобретения не сохраняют этот и другие указанные биты в перевернутом формате. Значение 1 используется для кодирования нижних 16 регистров. Другими словами, R′Rrrr формируется путем объединения EVEX.R′, EVEX.R и других RRR из других полей.

Поле 2315 опкода (EVEX байт 1, биты [3:0] - mmmm) - контент которого кодирует применяемый первоначальный байт опкода (OF, OF 38 или OF 3). Поле 2264 ширины элемента данных (EVEX байт 2, бит [7] - W) представлено нотацией EVEX. W. EVEX. W используется для определения степени детализации (размера) типа данных (либо 32-битных элементов данных или 64-битовых элементов данных). EVEX.vvvv 2320 (EVEX байт 2, биты [6:3] - vvvv) роль EVEX.vvvv может включать в себя следующее: 1) EVEX.vvvv кодирует первый операнд регистра источника, указанный в перевернутой (1 с дополнения) форме и действует для команд с 2 или более операндами источника; 2) EVEX.vvvv кодирует операнд регистра получателя, указанный в Is форме дополнения для некоторых векторных сдвигов; или 3) EVEX.vvvv не кодирует любой операнд, поле зарезервировано и должно содержать 11 lib. Таким образом, поле 2320 EVEX.vvvv кодирует 4 бита нижнего разряда первого спецификатора регистра источника, хранящиеся в перевернутой (1S дополнительной) форме. В зависимости от команды, используется дополнительное EVEX битное поле для расширения размера спецификатора до 32 регистров. EVEX.U 2268 класс поле (EVEX байт 2, бит [2] -U) - если EVEX.U=0, то это означает класс А или EVEX.U0; если EVEX.U=1, то это означает класс В или EVEX.U1.

Поле 2325 префикса кодирования (EVEX байт 2, бит [1:0] -рр) - предоставляет дополнительные биты для поля базовой операции. В дополнение к предоставлению поддержки для унаследованных SSE команд в формате EVEX префикса также имеет преимущество при уплотнении SIMD префикса (не требуя байт для выражения SIMD префикса, EVEX префикс требует только 2 бита). В одном варианте осуществления для поддержки унаследованных SSE команд, которые используют SIMD префикс (66Н, F2H, F3H), как в традиционном формате, так и в формате EVEX префикса, унаследованные SIMD префиксы кодируются в поле кодирования SIMD префикса; и во время выполнения расширения в унаследованный SIMD префикс перед предоставлением в декодер PLA (так как PLA может выполнять как унаследованный, так и EVEX формат этих унаследованных команд без изменений). Хотя новые команды могут использовать контент поля кодирования EVEX префикса непосредственно как расширение опкода, определенные варианты осуществления расширяют таким же образом последовательности, но обеспечивают различные значения для определения этих унаследованных SIMD префиксов. Альтернативный вариант осуществления может переформатировать PLA для поддержки кодирования 2 битового SIMD префикса и, таким образом, не требует расширения.

Альфа поле 2252 (EVEX байт 3, бит [7] - ЕН; также известное как EVEX.EH, EVEX.rs, EVEX.RL, EVEX управление маской предоставления права доступа на запись, и EVEX. N; также обозначено α) - как было описано ранее, это поле является конкретным контекстом. Бета поле 2254 (EVEX байт 3, биты [6:4] -SSS, также известное как EVEX.s2-0, EVEX.r2-0, EVEX.rr1, EVEX.LLO, EVEX.LLB; также обозначено βββ) - как описано выше, это поле является конкретным контекстом.

REX′ поле 2210 - это остаток от REX′ поля и EVEX.V′ битового поля (EVEX байт 3, бит [3] - V′), которые могут быть использованы для кодирования либо верхних 16 или нижних 16 расширенного 32 набора регистра. Этот бит сохранен в битовом перевернутом формате. Значение 1 используется для кодирования нижних 16 регистров. Другими словами, V′VVVV формируется путем объединения EVEX.V′, EVEX.vvvv.

Поле 2270 маскировки бита на предоставление права доступа на запись (EVEX байт 3, биты [2:0] -kkk) - контент которого определяет индекс регистра в регистрах маскировки бита на предоставление права доступа на запись, как описано выше. В одном варианте осуществления настоящего изобретения, конкретное значение EVEX.kkk=000 имеет конкретное поведение, не применяя маскировку бита на предоставление права доступа на запись для конкретной команды (это может быть реализовано в различных формах, включающие в себя использование проводной записи маски ко всем из них или аппаратные средства, которые обходят аппаратные средства маскировки).

Поле 2330 реального опкода (Байт 4) также известен как байт опкода. Часть опкода указывается в данном поле. MOD R/M поле 2340 (Байт 5) включает в себя MOD поле 2342, Reg поле 2344 и R/M поле 2346. Как ранее описано, контент MOD поля 2342 различает операции с доступом к памяти и операций без доступа к памяти. Роль Reg поля 2344 можно описать для двух ситуаций: кодирование либо операнда регистра получателя, или операнда регистра источника, или рассматриваться как опкод расширения и не используется для кодирования любого операнда команды. Роль R/M поля 2346 может включать в себя следующее: кодирование операнда команды, который ссылается на адрес памяти, или кодирование либо операнда регистра получателя, или операнда регистра источника.

Масштаб, индекс, база (SIB) байт (байт 6) - как было описано ранее, контент поля 2250 масштаба используется для генерации адресов памяти. SIB.xxx 2354 и SIB.bbb 2356 - контент этих полей были ранее упоминались в связи с индексами регистров Хххх и Bbbb. Поле 2262А смещения (байты 7-10) - когда MOD поле 2342 содержит 10, байты 7-10 являются полем 2262А смещения и работает так же, как унаследованное 32-битное смещение (disp32) и работает на байтовой детализации.

Поле 2262В коэффициента смещения (байт 7) - когда MOD поле 2342 содержит 01, байт 7 является полем 2262В коэффициента смещения. Расположение этого поля является таким же, что унаследованный х86 набор команд 8-битного смещения (disp8), который работает на байтовой детализации. Так disp8 является знаком расширения, возможно обратиться только между 128 и 127 байтами смещения; с точки зрения строк 64 байтового кэша, disp8 использует 8 битов, которые могут быть установлены только на четыре действительных значениях -128, -64, 0 и 64; так как более большой диапазон часто необходим, то disp32 используется; однако, disp32 требует 4 байта. В отличие от disp8 и disp32, поле 2262 В коэффициента смещения является интерпретацией disp8; при использовании поля 2262 В коэффициента смещения, фактическое смещение определяется контентом поля коэффициента смещения, умноженного на размер операнда доступа (N) к памяти. Этот тип смещения упоминается как disp8 * N. Это уменьшает среднюю длину команд (один байт используется для смещения, но с гораздо большим диапазоном). Такое сжатое смещение основано на предположении, что эффективное смещение является кратным детализированному значению доступа к памяти и, следовательно, не требуется кодирование избыточных битов младшего разряда адреса смещения. Другими словами, поле 262В коэффициента смещения заменяет унаследованный х86 набор команд 8-битного смещения. Таким образом, поле 2262В коэффициента смещения кодируется так же, как х86 набор команд 8-битного смещения (так что нет изменений в правилах кодирования ModRM/SIB), с той лишь разницей, что disp8 увеличен посредством disp8 * N. Другими словами, нет никаких изменений в правилах кодирования или длины кодирования, но только в интерпретации значения смещения посредством аппаратных средств (который должен масштабировать смещение по размеру операнда памяти, чтобы получить побайтовый адрес смещения). Непосредственное поле 2272 работает, как описано выше.