Способ передачи информации с защитой от ошибок, способ приема информации с защитой от ошибок и передающая система для передачи информации - RU2186459C2

Код документа: RU2186459C2

Чертежи

Описание

Настоящее изобретение относится к способу передачи информации с защитой от ошибок, способу приема информации с защитой от ошибок, передающей системе для передачи информации, передающей секции и приемной секции такой системы.

Способ и система такого рода известны из книги "Кодирование с исправлением ошибок для цифровой связи" авторов Г.К. Кларк и Дж. Б. Кейн, Пленум Пресс Нью-Йорк. 1981, части 8.5 и 8.3.2.

В этой книге описывается система, предназначенная для противодействия помехам. Это достигается с помощью технологии расширения спектра, которая включает значительное расширение спектра передаваемого сигнала по отношению к скорости передачи информации. Ее суть заключается в том, что при этом источник помехи распределяет энергию помехи на гораздо более широкую полосу частот, чем в случае сигнала без расширения спектра.

В такой помехозащищенной системе информация модулируется последовательно на различных частотах. Частота "перепрыгивает" в функции от времени с одного частотного канала на другой. Для защиты от каналов, в которых присутствует помеха, перед модуляцией информация кодируется с помощью кода, исправляющего ошибки. Кроме того, эта кодированная информация подвергается интерливингу: временная последовательность, с помощью которой модулируются отдельные участки информации, переставляется по отношению к последовательности поступления информации в коде защиты от ошибок. В известных устройствах такого рода интерливинг служит для того, чтобы сделать помехозащищенную систему более устойчивой к импульсам, которые забивают все частотные каналы на некоторое время.

Описанная система очень не эффективно использует доступные частоты. Это вынуждает источник помехи распределять энергию своего сигнала на значительно расширенный диапазон частот, что является достаточным для защиты от помехи, как описано в книге авторов Г.К. Кларк и Дж. Б. Кейн.

Кроме прочего, задачей настоящего изобретения является применение псевдослучайного интерливинга для повышения эффективности использования доступных частот.

Другой задачей настоящего изобретения является обеспечение многоканального радиовещания, которое было бы устойчивым к потерям сигнала, вызываемым неоднозначностью пути распространения сигнала и который бы эффективно использовал доступные частоты.

В настоящем изобретении

описывается способ передачи информации с защитой от ошибок, причем этот способ включает основной цикл, содержащий следующие этапы:

кодирование информации в виде логической последовательности

с помощью кода, исправляющего ошибки, который имеет большую защиту от ошибок, разделенных друг от друга в этой логической последовательности, чем от ошибок в виде импульсного всплеска в логической

последовательности;

генерирование сигнала, включающего определенное количество одновременно активных модулированных частотных каналов;

выбор для каждого отдельно взятого

информационного участка конкретного частотного канала с определенной частотной позицией среди других частотных каналов, причем эта определенная частотная позиция является псевдослучайной функцией от

логической позиции этого участка информации в логической последовательности;

модулирование каждого частотного канала, в зависимости, по меньшей мере, от одного соответствующего участка

информации, причем конкретный частотный канал модулируется, по меньшей мере, в зависимости от этого конкретного участка информации;

передача сигнала.

В результате одновременной передачи информации по ряду частотных каналов доступные частоты используются эффективно. Настоящее изобретение в большей степени относится к решению проблемы передающих каналов с неоднозначным путем распространения сигнала, чем к защите от помех. При беспроводной радиотрансляции, например, в дополнение к прямому излучению электромагнитных волн могут возникать побочные излучения, например, вызванные отражением излучаемого сигнала от зданий. Было обнаружено, что это часто приводит к изменениям в уровне принимаемого сигнала на различных частотных каналах. Более того, было обнаружено, что такие изменения носят периодический характер, т.е. они периодически повторяются в функции от частоты через некоторое количество каналов. Период этого повторения зависит от условий приема и, в общем случае, не может быть заранее определен.

Использование псевдослучайного интерливинга предохраняет от возникновения импульсных ошибок-всплесков, вызванных неоднозначностью пути распространения сигнала, которые могут быть настолько длительными, что их нельзя будет скорректировать.

Способ в соответствии с настоящим изобретением, включает:

запись

участков информации в соответствующие места расположения в памяти в первом порядке следования участков информации, причем этот первый порядок следования участков информации получается при кодировании;

считывание участков информации из соответствующих участков памяти со вторым порядком следования участков информации, в котором отдельные участки информации вызываются для модуляции в порядке,

соответствующем указанной псевдослучайной функции;

способ, включающий выполнение последовательных вариантов указанного основного цикла, причем в каждом из этих вариантов логическая

последовательность следования участков информации и сигнал соответствуют одной из серий логических последовательностей и одной из серий последовательно передаваемых сигналов соответственно, причем

указанная запись участков информации выполняется для каждого конкретного варианта соответственно в третьем порядке расположения в памяти, причем этот порядок расположения в памяти получается при

считывании участков информации для непосредственно предшествующего варианта основного цикла, посредством чего указанный соответствующий третий порядок следования в конкретном варианте переставляется

по отношению к соответствующему третьему порядку следования в непосредственно предшествующем варианте в соответствии с псевдослучайной функцией. Таким образом, интерливинг выполняется с помощью записи

участков информации в память и с помощью последовательного считывания этих участков информации из нее в другом порядке. Новая информация записывается затем в участки памяти, освобождаемые в процессе

считывания, перед тем, как все другие участки памяти будут считаны, что делает возможным экономно использовать память. Применение таких монотонно увеличивающихся рядов адресов известно из

американского патента 5,151,976. В то же время, в настоящем изобретении это применяется для записи в соответствии с псевдослучайной последовательностью. Несмотря на то, что такая псевдослучайная

последовательность на много сложнее, чем монотонно увеличивающийся ряд, было обнаружено, что, в частности, запись непосредственно после считывания со случайной последовательностью можно использовать

для интерливинга.

В одном из вариантов осуществления способа в соответствии с настоящим изобретением адреса памяти выбираются поочередно в монотонно повышающемся или понижающемся порядке, или в псевдослучайной функции от указанного порядка. С использованием только двух различных последовательностей адресации поочередно,интерливинг упрощается.

В одном из

вариантов настоящего изобретения адреса вычисляются в соответствии с линейной конгруэнтной последовательностью, удовлетворяющей следующему уравнению:

Xn+1 = (a Xn + с)

mod М,

где n - положение конкретного участка информации во втором порядке следования информации, Хn - адрес считывания данного участка информации, М - количество выбираемых мест

расположения в памяти, а и с - множитель и слагаемое для линейной конгруэнтной последовательности соответственно, сочетание используемых множителя и слагаемого изменяется для каждого варианта

основного цикла. Множитель а и слагаемое с для линейных конгруэнтных последовательностей выбираются таким образом, что с является относительным простым числом по отношению к W, (а-1) является кратным

всем простым множителям М и (а-1) является кратным 4, если m кратно 4. Это обеспечивает простой способ вырабатывания адресов. В частности, было определено, что все "а", используемые для различных

вариантов, являются таковыми, что квадрат (а-1) делится на М, при этом обеспечивается то, что все ряды адресов, которые последовательно требуются для считывания участков информации, записанных в

порядке считывания предшествующих участков информации, всегда могут вырабатываться в соответствии с этой формулой.

Настоящее изобретение также относится к способу приема информации и к системе, использующей данный способ, и его компоненты, в которой соответствующие меры могут применяться с необходимыми изменениями для получения аналогичных преимуществ.

Этот и другие аспекты настоящего изобретения будут ясны из описания вариантов изобретения, приведенных ниже.

На чертежах:

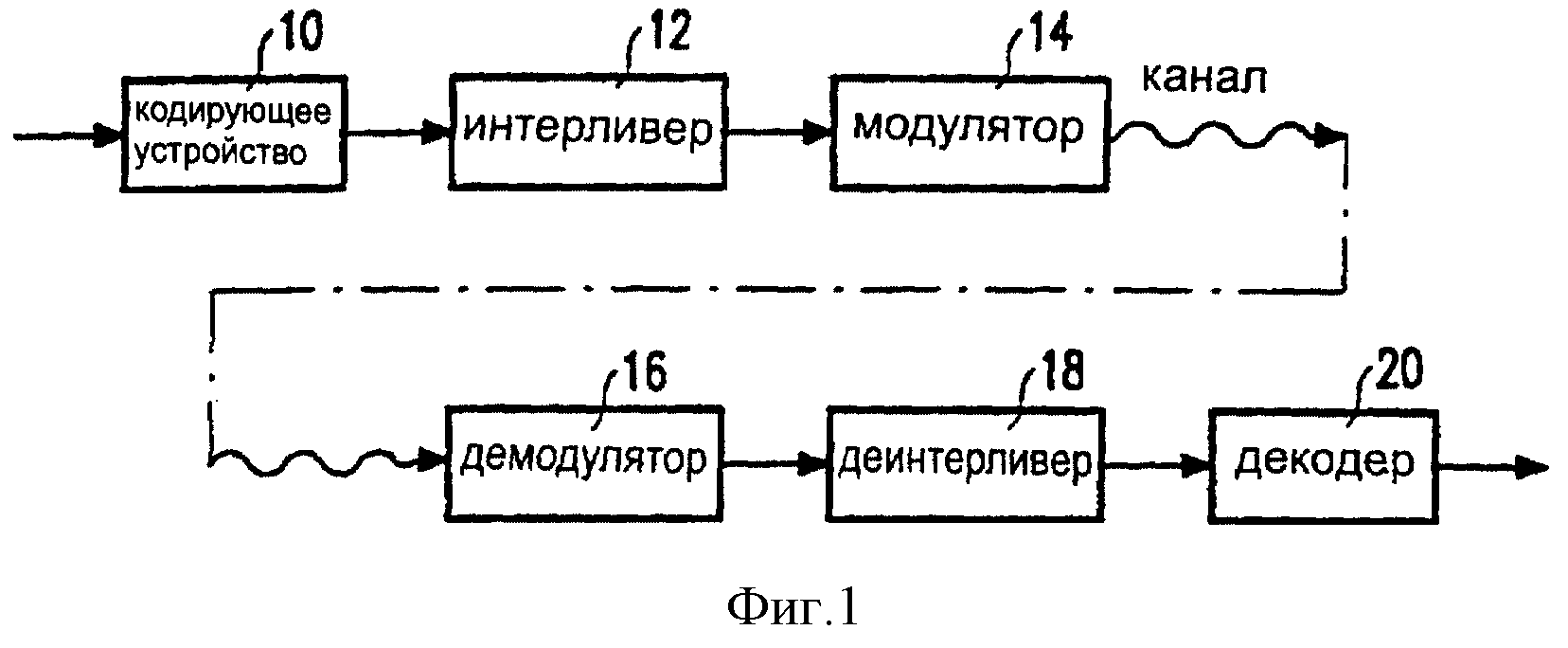

на фиг.1 представлена передающая система;

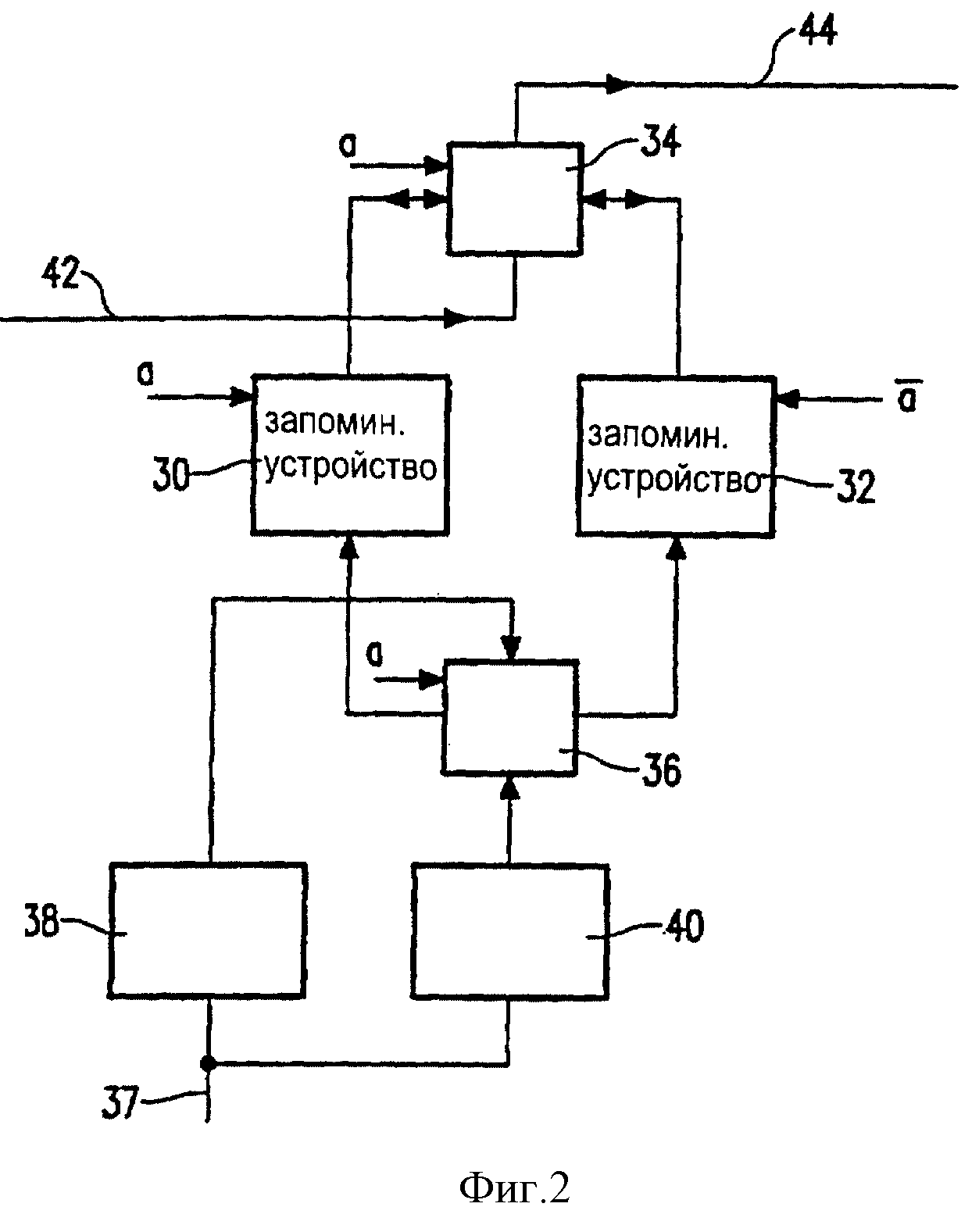

на фиг.2

представлен вариант осуществления интерливера;

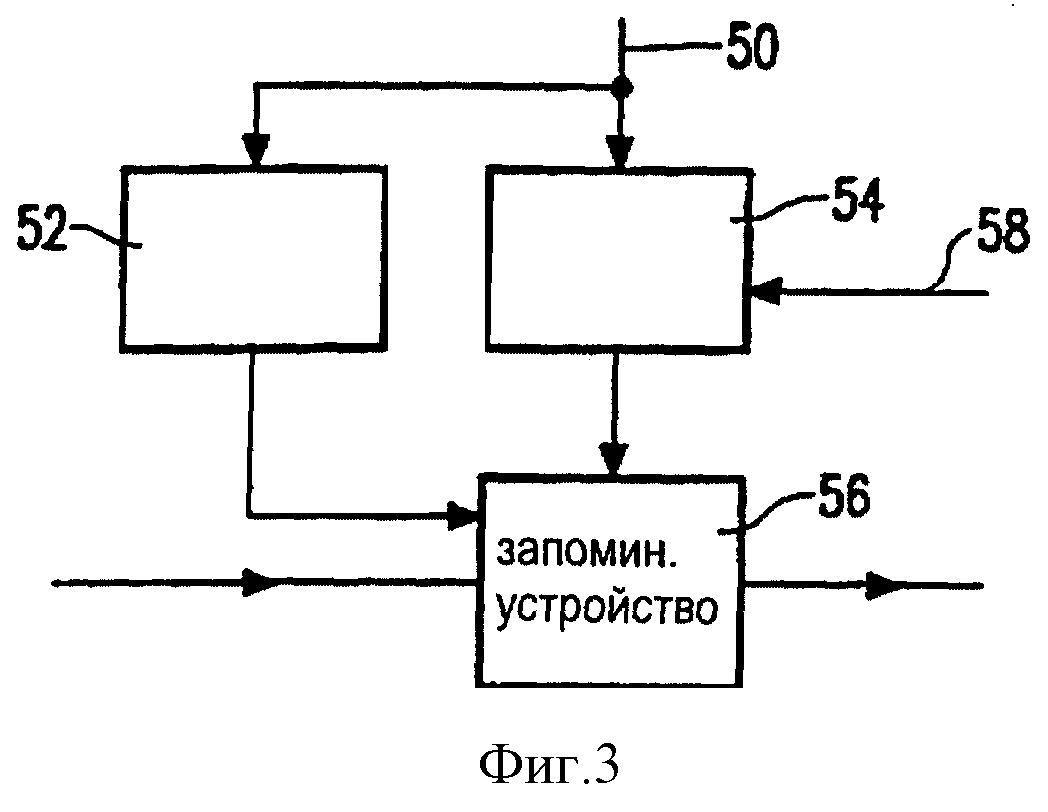

на фиг.3 представлен дополнительный вариант осуществления интерливера, а также

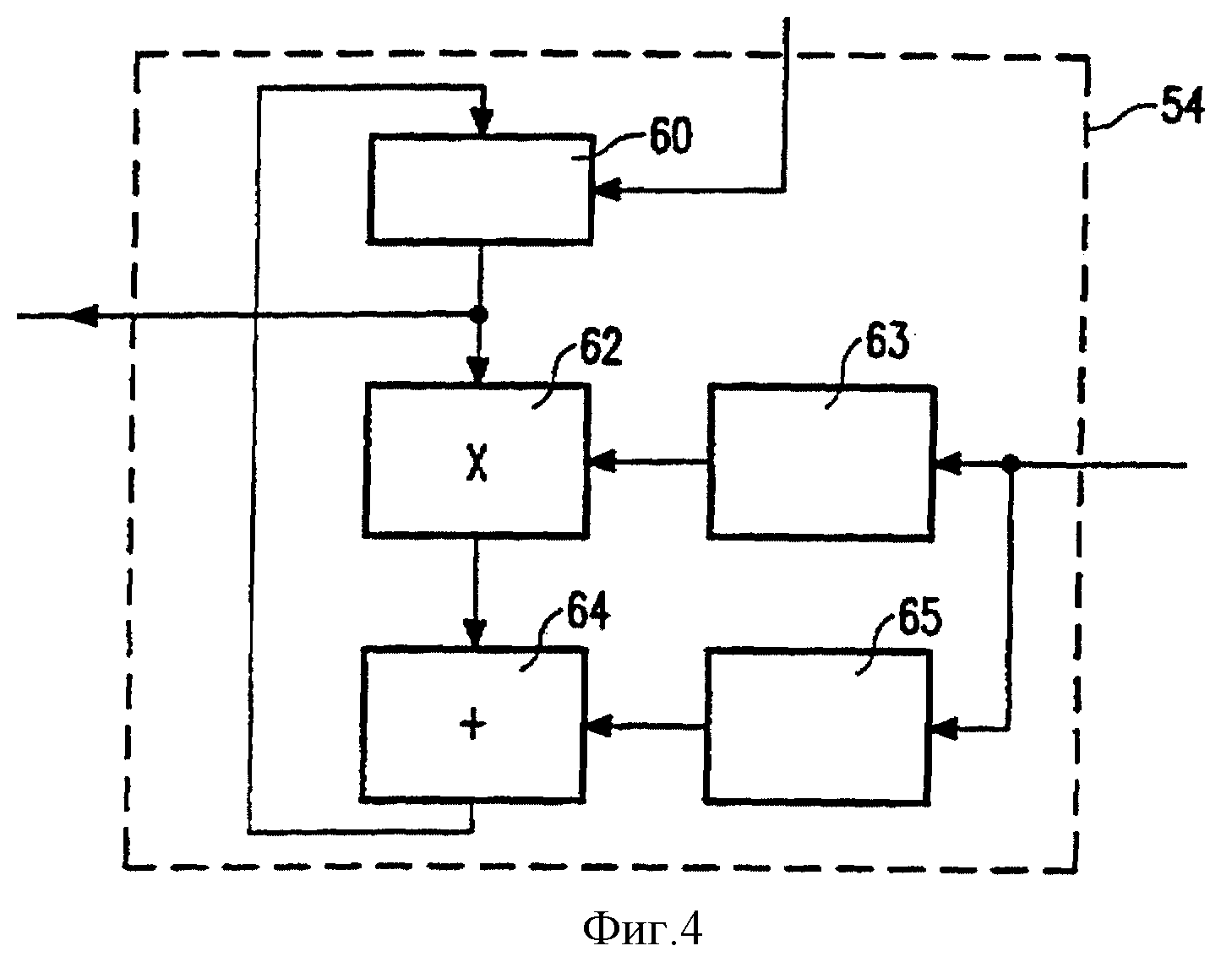

на фиг.4 представлен вариант генератора адресов.

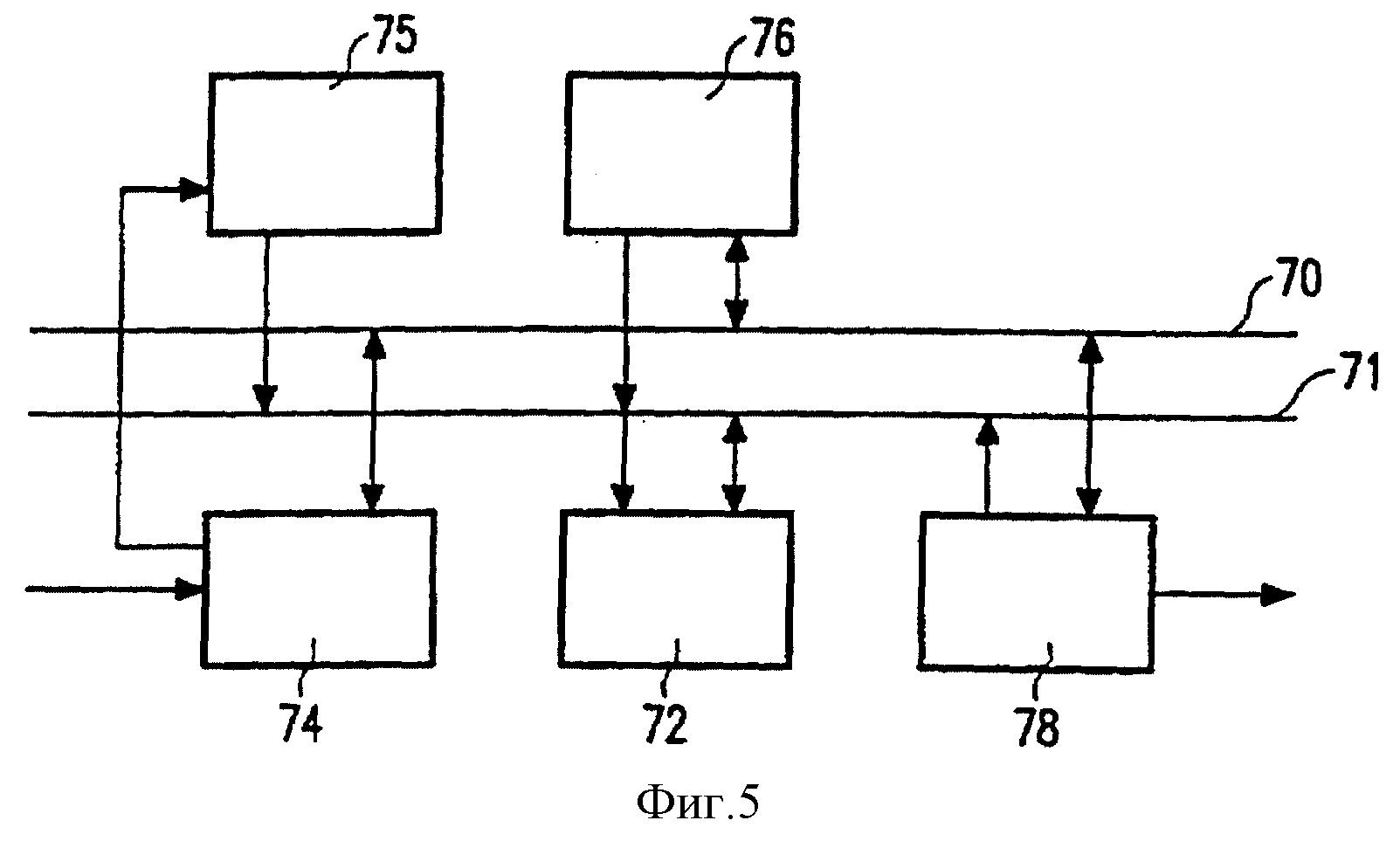

на фиг. 5 представлен вариант осуществления передающей секции в соответствии с настоящим изобретением.

На фиг. 1 представлена передающая система. Она включает последовательно соединенные каскады блока 10 кодирования, интерливера 12, модулятора 14, канала передачи, демодулятора 16, деинтерливера 18 и декодера 20.

При работе информация поступает на вход блока 10 кодирования. Блок 10 кодирования кодирует эту информацию с помощью кода, исправляющего ошибки. Например, для этой цели может использоваться свертываемый код. Кодированная информация состоит, например, из блоков, каждый из которых содержит логическую последовательность битов.

Декодер 20 соответствует блоку 10 кодирования и исправляет битовые ошибки, возникающие во время передачи от блока 10 кодирования к декодеру 20. Коды, исправляющие ошибки, выбираются таким образом, что битовые ошибки, возникающие по всей логической последовательности, могут сразу же исправляться. Импульсные ошибки-всплески, при которых некоторое количество последовательно расположенных битов в логической последовательности будут неправильными, исправляются не так просто в случае, когда они слишком длинные.

Модулятор 14 вырабатывает сигнал с определенным количеством частотных каналов, передаваемых одновременно. Биты в каждом блоке распределены вдоль ряда групп. Каждая группа соответствует определенному частотному каналу и битовая информация в каждой из этих групп передается в соответствующем частотном канале. Это может быть реализовано, например, с помощью интерпретации битов в каждой группе в виде чисел, размещения этих чисел в виде последовательностей и выполнения преобразования Фурье в этих последовательностях. Результат преобразования Фурье последовательно передается по каналу передачи, например, с помощью канала наземной беспроводной радиостанции. Преобразование Фурье и передача повторяются в виде последовательных блоков. Это соответствует известной технологии ОМЧР (ортогонального мультиплексирования с частотным разделением).

Демодулятор 16 соответствует модулятору 14. Демодулятор принимает различные частотные каналы одновременно и восстанавливает битовые группы, переданные в каждом соответствующем частотном канале. В соответствии с технологией ОМЧР это выполняется, например, с помощью инверсного преобразования Фурье принятого сигнала и с помощью восстановления чисел и соответствующих им информационных групп. Интерливер 12 служит для обеспечения того, что биты, которые непосредственно следуют друг за другом в логической последовательности, всегда модулируются в достаточно далеко разнесенных частотных каналах. Разнос этих каналов (в смысле каналов на промежуточных частотах), предпочтительно, должен быть больше нуля, так, чтобы непосредственно следующие друг за другом биты не поступали бы в соседние каналы. Это необходимо для того, чтобы помеха, возникающая в отдельном канале, или в ряде соседних каналов, не привела бы к возникновению импульсных ошибок-всплесков в логической последовательности.

Деинтерливер 18 соответствует интерливеру 12 и выполняет обратную операцию так, что логическая последовательность восстанавливается в ее временном порядке (т.е. за исключением битовых ошибок) перед тем, как она будет подана на декодер 20.

Интерливер 12 размещает каждую соседнюю пару бит, которые следуют друг за другом в логической последовательности на относительно удаленном расстоянии через определенное количество каналов друг от друга. Это относительное расстояние имеет различную величину, что обеспечивает то, что эти различные расстояния возникают равновероятно. В результате, система становится защищенной от помех в передающем канале, которые приводят к плохому приему в периодической системе частотных каналов (под периодической системой понимается система, в которой плохие условия приема периодически возникают как функция частоты каждый раз через определенное количество каналов).

Все другие пары битов, которые в достаточной степени близки друг к другу так, что одновременная ошибка в битах таких пар может вызвать проблемы с импульсными ошибками-всплесками, также размещаются в относительно удаленных друг от друга каналах. Это относительное расстояние, предпочтительно, также должно иметь различную величину, что обеспечивает то, что различное расстояние возникает приблизительно равновероятно.

На фиг. 2 представлен вариант осуществления интерливера; этот прибор способен также работать, как деинтерливер. Интерливер, показанный на фиг.2, содержит информационный вход 42, который соединен через мультиплексор 34 с соответствующими информационными входами/выходами первого и второго запоминающих устройств 30, 32. Информационные входы/выходы запоминающих устройств 30, 32 также соединены через мультиплексор 34 с выходом 44 интерливера.

Интерливер также включает вход синхронизации 37, соединенный с входами синхронизации первого и второго генераторов 38, 40 адресов. Выход каждого из генераторов адресов соединен с дополнительным мультиплексором адресов. Выходы этого дополнительного мультиплексора 36 соединены с соответствующими адресными входами первого и второго запоминающих устройств 38, 40.

Во время работы интерливер постоянно переключается с одного на другой режим и обратно. В первом режиме мультиплексор 34 соединяет вход 42 с информационным входом первого запоминающего устройства 30 и выход 44 с информационным выходом второго запоминающего устройства 32. Кроме того, дополнительный мультиплексор 36 соединяет выход первого генератора адресов с адресным входом первого запоминающего устройства 30 и выход второго генератора адресов 40 с адресным входом второго запоминающего устройства 32. Во втором режиме роль первого и второго запоминающих устройств 30, 32 меняется по сравнению с первым режимом.

Первый генератор 38 адресов генерирует первую синхронизированную серию адресов. Различные участки информации, приходящие на вход 42 во время последовательных тактов циклов синхронизации, записываются в эти адреса. Информация считывается из этого запоминающего устройства 32 аналогичным образом, адресуется с помощью второй серии адресов из второго генератора адресов и подается на выход 44. Первая и вторая серии адресов отличаются друг от друга, в результате чего достигается их интерливинг.

Первый ряд адресов может быть, например, монотонно возрастающим рядом (1, 2, 3, ...), а второй ряд адресов может представлять собой псевдослучайный ряд чисел, например ряд, в котором существует соответствующее расстояние между каждой парой непосредственно последовательно вырабатываемых адресов; эти соответствующие расстояния могут иметь различное значение, причем должно быть обеспечено, чтобы различные значения расстояний возникали приблизительно равновероятно.

Это расстояние соответствует расстоянию между частотными каналами, в которые будут помещаться последовательные биты логической последовательности.

Соответствующий деинтерливер имеет такую же структуру, как показано на фиг.2, причем первый генератор адресов деинтерливера вырабатывает ту же последовательность адресов, как и второй генератор адресов интерливера, и наоборот.

Псевдослучайные ряды чисел могут вырабатываться с помощью генератора адресов 40, который представляет собой сборку счетчика и ПЗУ, последовательные псевдослучайные адреса

хранятся в последовательных адресах ПЗУ. Кроме того, можно использовать известный линейный конгруэнтный ряд, в котором адреса Хn для запоминающего устройства 32 могут быть получены с

помощью рекурсии уравнения

Xn+1 = (a Xn + с) mod М.

Эти адреса могут быть получены с помощью умножения и сложения без использования ПЗУ. В качестве еще одной альтернативы можно использовать линейный сдвиговый регистр с обратной связью.

На фиг. 3 представлен еще один вариант осуществления интерливера. Этот вариант осуществления содержит только одно запоминающее устройство 56. Вход и выход интерливера соединяются с информационным входом и информационным выходом соответственно этого запоминающего устройства 56. Интерливер также содержит тактовый вход 50, который соединен с генератором 54 адресов. Выход генератора 54 адресов соединен с адресным входом запоминающего устройства 56. Тактовый вход 50 соединен также через устройство управления 52 чтения/записи с управляющим входом чтения/записи запоминающего устройства.

Во время работы генератор 54 адресов вырабатывает последовательность адресов. Для каждого адреса первый участок информации считывается с запоминающего устройства 56 и подается на выход; схема управления чтения/записи последовательно переключает запоминающее устройство в режим записи и участки информации, приходящие со входа, записываются в запоминающее устройство по этому адресу.

Генератор 54 адресов каждый раз вырабатывает такую последовательность адресов. Каждая последовательность содержит, в значительной степени, одни и те же адреса. Однако порядок, в котором адреса поступают в непосредственно следующих друг за другом последовательностях, каждый раз различен. Например, попеременно могут применяться псевдослучайная последовательность (X1, X2, X3,..., Xn) и нормальная монотонно возрастающая последовательность (1, 2, 3, . . ., N). Это приводит к интерливингу с, в достаточной степени, равномерным распределением расстояния между следующими друг за другом адресами.

При использовании только двух различных последовательностей адресов попеременно значительно упрощается деинтерливинг (используются те же две последовательности, так, что каждый раз участки информации записываются в память деинтерливера по адресам, соответствующим адресам, откуда они были считаны в интерливере). Однако такой подход имеет недостаток, заключающийся в том, что способ интерливинга часто повторяется так, что система передачи становится подверженной систематически повторяющимся помехам.

Поэтому, в качестве привлекательной альтернативы, возможно использовать большее, чем две, количество различных последовательностей, и повторять по заданной схеме последовательности адресов, используемых только после прохождения двух полных последовательностей. С этой целью, для использования в радиосвязи, предпочтительно применять линейную конгруэнтную последовательность на приемной стороне в деинтерливере, поскольку такая последовательность может быть просто получена. На передающей стороне может использоваться, например, интерливер, включающий ПЗУ, причем это ПЗУ содержит инверсное переставление того, что содержит деинтерливер на приемной стороне. Допустим, что интерливер воспроизводит такое переставление, это инверсное переставление может быть вычислено с помощью цифровых методов. Если в деинтерливере используется повторяющаяся схема взаимно различных последовательностей адресов, включающая монотонно возрастающий ряд чисел (1. 2, 3), такое инверсное переставление требует лишь ограниченное количество пространства в запоминающем устройстве ПЗУ.

В случае, когда используются различные адресные последовательности, между приемной и передающей сторонами необходим сигнал синхронизации так, чтобы деинтерливер мог начать схему последовательностей адресов в правильной фазе (так, чтобы быть инверсным по отношению к интерливеру). С этой целью предпочтительно использовать передаваемый сигнал синхронизации, который также служит для отметки информационного заголовка, для последующей обработки закодированных символов.

На фиг. 4 показан вариант осуществления генератора 54 адресов для использования в интерливере, представленном на фиг.2 или 3. Генератор 54 адресов содержит регистр 60, выход которого соединен с выходом генератора адресов и с первым умножителем 62 множимого. Выход умножителя 62 соединен с первым суммирующим входом сумматора 64. Выход сумматора 64 соединен со входом регистра 60. Генератор адресов содержит запоминающее устройство 63 множителя и запоминающее устройство 65 слагаемого, которые соединены по выходу со вторым входом умножителя 62 второго множителя и со входом сумматора 64 второго слагаемого соответственно.

Во время работы регистр 60 содержит адреса Xn

для запоминающего устройства. Используя умножитель 62 и сумматор 64, следующий адрес вычисляется в соответствии с формулой

Xn+1 = (a Xn + с) mod М,

где М - это

длина последовательности адресов. Множитель "а" и слагаемое "с" получаются из запоминающего устройства 64 множителя и запоминающего устройства 65 слагаемого соответственно. Между последовательными

рядами запоминающие устройства 64, 65 принимают сигналы, с помощью чего другой множитель и/или слагаемое подается на умножитель и сумматор так, что вырабатывается, в значительной степени, отличающаяся

последовательность. В одной из последовательностей, например, а=1 и с=1, что приводит к монотонно возрастающему ряду чисел. В другой последовательности а не равно 1 и вырабатывается известным способом,

при этом генерируется псевдослучайная последовательность (с - это соответствующее простое число по отношению к М, (а-1) кратно р для всех простых чисел р, составляющих М (например, если М=45=3•

3•5, то (а-1) должно быть одновременно кратно 3 и 5), а (а-1) является кратным 4, если М кратно 4).

При запоминании ряда различных используемых величин а и с может вырабатываться соответствующее количество различных последовательностей адресов. Предпочтительно, чтобы величина "а" выбиралась только таким образом, чтобы (а-1) в квадрате могло бы делиться на "М", т.е. так, чтобы значение (а-1) содержало каждый простой множитель m, по меньшей мере, в два раза меньше, чем само "М" (например, когда M=675=3•3•3•5•5, (а-1) может быть 45=3•3•5, в общем случае требуется, чтобы величина М была большой и содержала бы много простых множителей: среди значений М от 1 до 20 можно определить только M=8, 9, 12, 16, 18).

Можно доказать, что только значения "а", соответствующие тому, что квадрат (а-1) делится на "М", должны быть использованы для выработки адресов, любое псевдослучайное переставление битов, описанных формулой Xn+1 = (a Xn + с) mod М, может быть реализовано со значением "а", которое также удовлетворяет этому условию. Кроме того, было определено, что в этом случае адреса для интерливинга и деинтерливинга могут быть получены с помощью такого псевдослучайного представления. Следовательно, не требуется применения ПЗУ. Было определено также, что данное соотношение соответствует действительности только в случае, когда квадрат (а-1) делится на "М". В этом случае нет необходимости вычислять адреса с помощью формулы Xn+1 = (a Xn + с) mod M, вместо этого можно использовать Xn-1 = Xn+vn mod m; vn+1=vn+d mod m, при d= с(а-1), причем vo начинается со значения, удовлетворяющего выражению (а-1)Хо+с. (Например, когда М=100 (=2•2•5•5), "а" может быть выбрано со значением 21 (а-1=4•5) и с=1.

Если модуль числа М, с которым работает умножитель и сумматор сделать перенастраиваемым, интерливер/деинтерливер может просто переключаться на различную длину информационных блоков. Очевидно, что настоящее изобретение не ограничивается описанными вариантами осуществления. Например, вместо того, чтобы работать с битами, возможна также работа с более крупными символами, длина которых определяется способностью кода, исправляющего ошибки, в лучшей степени исправлять изолированные и случайные ошибки в этих символах, чем импульсные ошибки-всплески.

Более того, логическая последовательность битов, производимых кодирующим устройством, не обязательно должна быть временной последовательностью. Биты являются "логически следующими друг за другом", если одновременные ошибки в этих битах могут с меньшей вероятностью быть исправлены, чем одновременные ошибки в "не логически следующих друг за другом" битах.

Внутренний частотный интерливинг является псевдослучайным битовым интерливингом. Этот интерливинг имеет блоковую основу, т.е. биты в каждом ОМЧР-символе переставляются фиксированным способом так, что внезапно возникающие ошибки становятся случайными, однако биты в данном ОМЧР-символе не смешиваются с битами любого другого ОМЧР-символа.

В практическом примере ОМЧР-символ состоит из N используемых поднесущих, где N равно 6361 или 5937 так, что каждый из них содержит 2, 4 или 6 информационных битов. Задачей интерливера является декоррелировать биты на входе детектора Витерби.

Деинтерливер содержит запоминающее устройство (ОЗУ) с размером 8 раз по 8192 бита и устройство адресации. Устройство адресации вырабатывает 16-битовый адрес, который может быть разделен на три бита сдвига и 13-бит сегмента. 13-бит сегмента определяет конкретный подканал, в то время как три бита сдвига определяют расстояние конкретного бита от данного подканала. Каждый раз, когда происходит обращение к конкретному адресу в ОЗУ, его содержание считывается и передается на расположенный далее декодер и последующий бит, поступающий на его вход, записывается с текущим местоположением в памяти. За каждый цикл все соответствующие местоположения в памяти должны получить адреса. Эти три бита сдвига периодически проходят через соответствующие состояния (в зависимости от количества бит в символе), в то время как 13 битов сегмента генерируются с помощью алгоритма, вырабатывающего все соответствующие адреса с помощью специального уравнения.

Поскольку 6361 является простым числом и 5937 делится на три, адреса сдвига могут быть генерированы в парах, причем был определен алгоритм, который работает для двух бит информации, на поднесущую. и этот алгоритм используется 1, 2 или 3 раза, в зависимости от количества бит на символ, каждый раз с различным фиксированным смещением сдвига. Таким образом, обеспечивается то, что все биты будут адресованы, при любых обстоятельствах, перед тем, как устройство адресации перейдет в такое же состояние.

Одним из способов получения периодического интерливера может быть генерация последовательных адресов Xt.n, 0≤n

где

В целом настоящее изобретение относится к передающей системе, которая включает кодирующее устройство, интерливер, модулятор, передающий канал, демодулятор, деинтерливер и декодер. Кодирующее устройство используется для кодирования блока информации с помощью кода, исправляющего ошибки, содержащего логическую последовательность участков информации. Декодер используется для исправления ошибок, возникающих при передаче между кодирующим устройством и декодером. Код, исправляющий ошибки, более надежно защищает от ошибок, которые возникают одновременно и имеют изолированный вид в логической последовательности, чем от ошибок, которые возникают одновременно в форме импульсных ошибок-всплесков. Модулятор используется для генерирования сигнала, который содержит ряд частотных каналов для одновременной передачи, причем каждый из этих частотных каналов соответствует группе, которая содержит, по меньшей мере, один из участков информации и который модулируется в соответствующем канале. Канал передачи размещается между модулятором и демодулятором. Демодулятор восстанавливает группы и подает эти группы на декодер. Интерливер распределяет участки по группам и вводит псевдослучайную взаимозависимость между логическими посылками, а также определяет распределение между последующими частотными каналами. Деинтерливер восстанавливает логическую последовательность в группах, восстановленных демодулятором, перед ее подачей на декодер.

Такая передающая система может быть улучшена тем, что интерливер и/или деинтерливер будут реализовывать распределение с использованием немонотонно увеличивающейся линейной конгруэнтной последовательности.

Такая передающая система может быть дополнительно улучшена, когда интерливер и/или деинтерливер будут снабжены запоминающим устройством для участка информации и средством записи и считывания, средство записи будет каждый раз записывать участок информации с определенным местоположением в памяти, из которого непосредственно перед этим была считана информация, устройство считывания считывает участок информации из следующего места размещения информации в памяти, порядок размещения информации в памяти, а также логическая последовательность для записи различаются для следующих друг за другом логических последовательностей.

Дальнейшее улучшение передающей системы может касаться того, что этот порядок периодически повторяется, причем период повторения должен быть, по меньшей мере, большим двух блоков с монотонно повышающимся или понижающимся порядком. Устройства записи и/или считывания могут также содержать генератор адресов, который включается для формирования линейной конгруэнтной последовательности с множителем и слагаемым, а также используется для смены множителя и/или слагаемого от одного блока к другому.

Таким образом, информация может передаваться с помощью следующих этапов:

кодирование информации с помощью кода, исправляющего ошибки;

интерливинг информации

в соответствии с псевдослучайной последовательностью;

модулирование информации в ряде частотных каналов, причем участки информации, которые не могут быть исправлены вместе, размещаются в

различных частотных каналах с помощью интерливинга;

демодулирование информации;

деинтерливинг информации;

декодирование информации.

На фиг.5 представлен вариант осуществления передающей секции в соответствии с настоящим изобретением. Передающая секция содержит информационную шину 70 и адресную шину 71, соединенные с запоминающим устройством 72, процессор 76 и передатчик 78. Кодирующее устройство 74 соединено с информационной шиной 70. Кодирующее устройство 74 соединено с адресной шиной 71 через устройство 75 генерации адресов.

Во время работы кодирующее устройство 74 принимает блоки информации и кодирует их в виде последовательности битов. Каждый последующий бит подается на информационную шину 70 и о появлении этого бита сообщается на генератор 75 адресов. Генератор 75 адресов вырабатывает соответствующие адреса для каждого последующего бита в соответствии с псевдослучайной последовательностью. Этот адрес указывает как на расположение слова в запоминающем устройстве 72, так и на расположение бита внутри расположения слова. Расположение слова соответствует группе, которой принадлежит данный бит, а расположение бита соответствует расположению бита внутри этой группы. Генератор 75 адресов обеспечивает то, что биты, которые логически расположены рядом друг с другом, всегда запоминаются в достаточной степени различных местах расположения слов. Расстояния между этими расположениями слов, предпочтительно, должны быть больше нуля, так, что логически находящиеся рядом биты, попадают в удаленные друг от друга места расположения слов.

Этот адрес подается на информационную шину, и бит запоминается в запоминающем устройстве 72 в месте положения, которое соответствует адресу, вырабатываемому для него с помощью генератора 75 адресов. Когда весь блок информации будет закодирован таким образом с помощью кода, защищающего от ошибок, и записан в запоминающее устройство 72, включается процессор 76. Процессор 76 вычисляет преобразования Фурье для слов, записанных в запоминающем устройстве 72. С этой целью он считывает слова каждый раз, когда они требуются для алгоритма преобразования Фурье. С этой целью может использоваться известный алгоритм преобразования Фурье, который обращается по адресам к местам расположения слов в запоминающем устройстве 72 обычным путем, т.е. не учитывая процесс интерливинга. Поскольку биты, которые логически являются соседствующими друг другу, всегда записываются в память в различных в достаточной степени местах расположения слов, эти соседние биты будут модулированы в различных частотных каналах в результате преобразования Фурье. Результат этого преобразования последовательно считывается передатчиком 78 и передается через канал передачи (не показан).

Структура, аналогичная представленной на фиг.5, может использоваться и в приемной секции, при этом вместо передатчика 78, устанавливается приемник, а вместо кодирующего устройства 74 - декодер. В этом случае приемник записывает слова в память 72, и процессор выполняет преобразования Фурье этих слов. Генератор 75 адресов обеспечивает выполнение псевдослучайного интерливинга, вырабатывая последовательные адресные пары слов/битов для считывания результатов преобразования Фурье, бит за битом, для исправления ошибок с помощью декодера.

Реферат

Заявленное изобретение относится к способам передачи и приема информации с защитой от ошибок, передающей системе для передачи информации, передающей секции и приемной секции такой системы. Техническим результатом является то, что данные передаются с помощью сигнала, содержащего набор одновременно активных модулированных частотных каналов, и что эти данные кодируются с помощью кода, защищающего от ошибок. Это достигается тем, что последовательные участки информации размещаются с псевдослучайной зависимостью в различных частотных каналах. Это защищает от затуханий, которые происходят в частотных каналах, расположенных на периодическом удалении друг от друга. Псевдослучайное размещение реализуется с помощью записи участков информации в запоминающее устройство в одном порядке и считывания их из памяти - в другом порядке. Таким образом модулируются последовательные сигналы. Место расположения в памяти освобождается при считывании для модуляции одного сигнала и заполняется участками информации для модуляции последовательного сигнала. Это производится с помощью переставления порядка мест расположения в памяти, в которых участки информации записываются для каждого последующего сигнала. 5 с. и 23 з.п.ф-лы, 5 ил.

Формула

Xn+1= (аХn+с) mod М,

где n - это местоположения конкретного участка информации во втором порядке;

Хn - адрес, из которого считывается этот конкретный участок информации;

М - номер выбираемого местоположения в памяти;

а и с - множитель и слагаемое для линейной конгруэнтной последовательности соответственно, при этом комбинация используемого множителя и слагаемого меняется для каждого варианта основного цикла.

Хn+1= (аХn+с) mod М,

где n - это позиция конкретного участка информации во втором порядке;

Хn - адрес, из которого этот конкретный участок считывается;

М - номер выбираемого местоположения в памяти;

а и с - множитель и слагаемое для линейной конгруэнтной последовательности соответственно,

а комбинация множителя и слагаемого изменяется для каждого варианта основного цикла.

Комментарии