Система и способ тестирования и конфигурирования fpga - RU2733092C2

Код документа: RU2733092C2

Чертежи

Описание

Область техники, к которой относится изобретение

Настоящее изобретение относится к программируемым логическим устройствам, а более конкретно - к устройствам программируемой пользователем вентильной матрицы.

Уровень техники

FPGA являются типом программируемого логического устройства. Они в общем случае основаны на стандартном программируемом логическом блоке, большое количество которых размещается вместе для реализации различных функций.

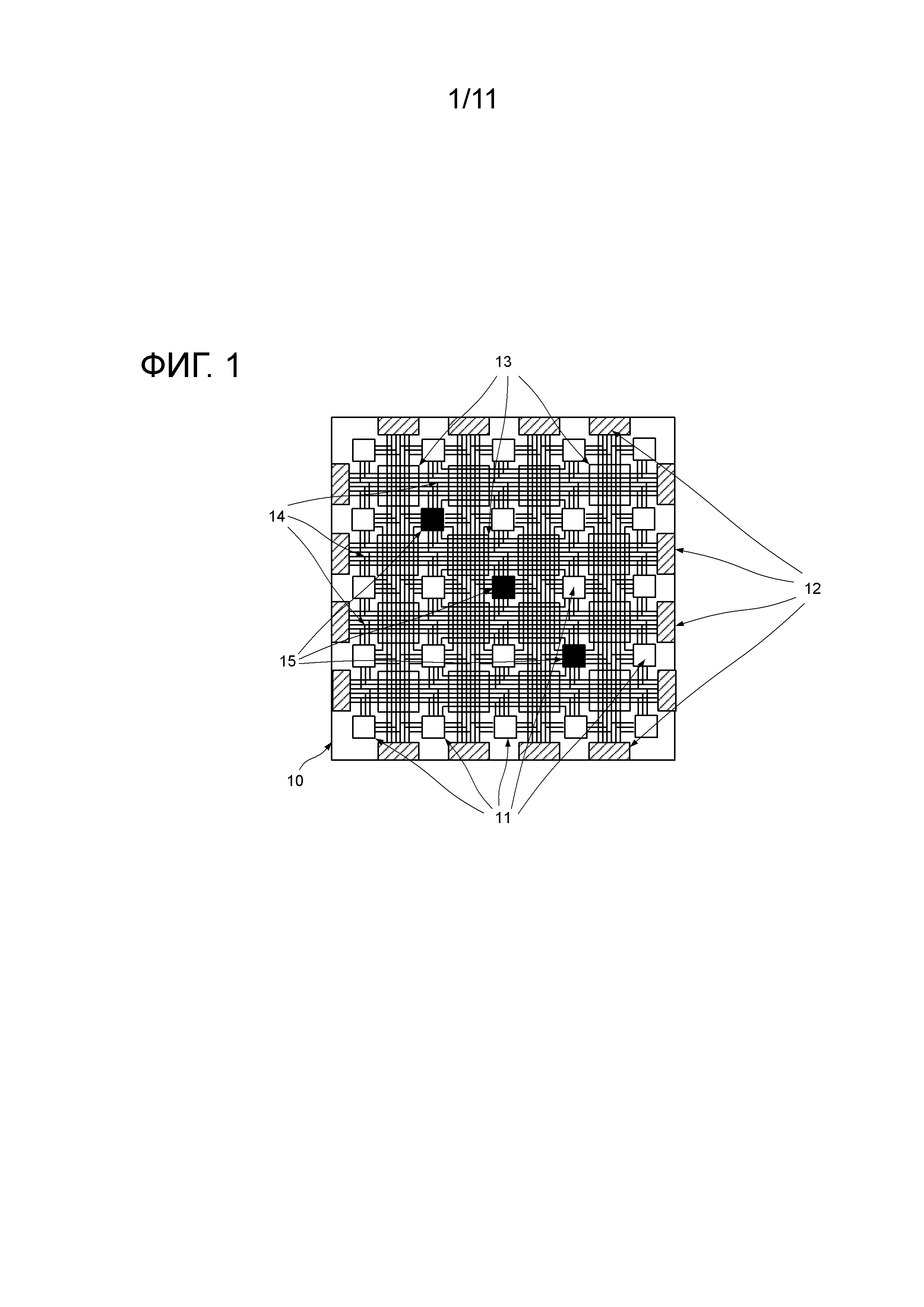

Фиг. 1 схематично показывает пример системы FPGA, которая известна в уровне техники.

Как показано на фиг. 1, кристалл 10 FPGA содержит множество логических блоков 11, например, как описано выше. Кристалл также содержит множество портов 12 ввода/вывода. Эти логические блоки 11 и порты 12 ввода/вывода подключаются с помощью множества дорожек 14. В узловых точках этих дорожек обеспечивается множество областей 13 программируемой маршрутизации. В этих областях программируемой маршрутизации обеспечивается переключатели, которые могут выборочно подключать любую пару пересекающихся дорожек под управлением логического значения, сохраненного в ячейке запоминающего устройства, подключенной к каждому переключателю. Значения запоминающего устройства переключателя устанавливаются при запуске системы из энергонезависимого запоминающего устройства. Соответственно, с помощью установки требуемых значений в запоминающем устройстве переключателя любые подключения в любом логическом блоке могут соединяться с подключениями в любом другом логическом блоке или с любым портом 12 ввода/вывода. Таким образом, с помощью правильного конфигурирования запоминающих устройств для определения работы каждого логического блока и запоминающих устройств 13 переключателей для установления соответствующих подключений между логическими блоками могут реализовываться любые необходимые функциональные возможности.

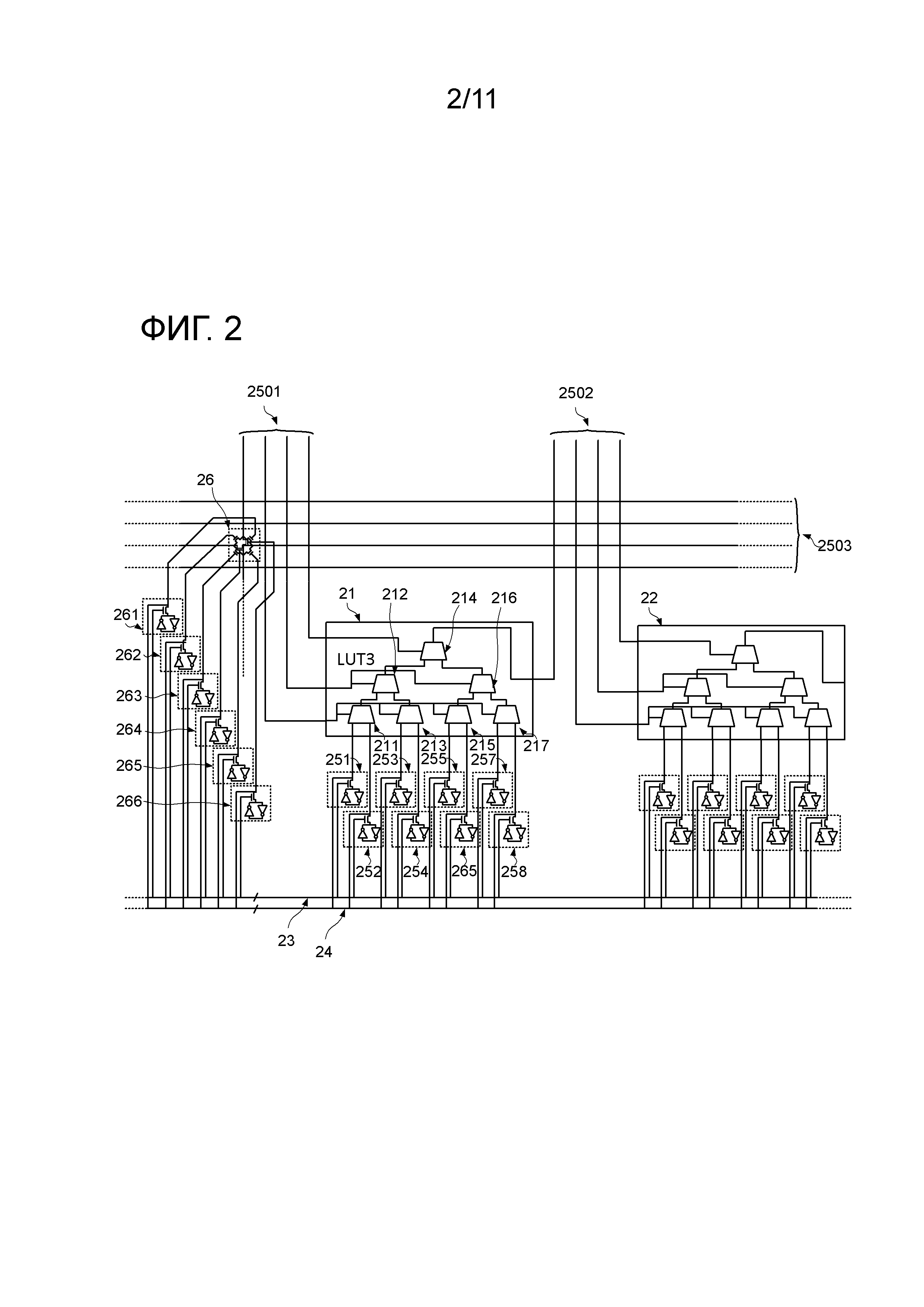

Фиг. 2 показывает более подробную информацию об элементах системы FPGA, которая известна в уровне техники.

Элементы, показанные на фиг. 2, формируют типичный пример частичной реализации частей функциональных возможностей, описанных выше по отношению к фиг. 1.

Как показано на фиг. 2, обеспечивается первая поисковая таблица (LUT) 21 и вторая поисковая таблица (LUT) 22 и множество дополнительных LUT (не показаны). Первая LUT 21 содержит семь двухвходовых мультиплексоров 211, 212, 213, 214, 215, 216, 217 соответственно. Вторая LUT и дополнительные LUT конфигурируются аналогичным образом. Эти мультиплексоры размещаются каскадным способом с тремя рядами, формируя 8-входовой мультиплексор, выход которого формирует выход LUT. Каждый из обоих первых рядов мультиплексоров (211, 213, 215 и 217) в каждой каскадной структуре имеет в общей сложности восемь входов. Эти восемь входов формируют программирующие входы первой LUT 21. Входы выбора каждого ряда объединяются для образования трех входов данных LUT. Входы данных и выход данных первой LUT подключаются к набору дорожек 2501, 2502. Входы и выходы второй и дополнительных LUT подключаются, соответственно, к сети дополнительных дорожек (не показаны). Традиционно LUT с 3 входами данных таким образом упоминается как «LUT3». Каждый из восьми программирующих входов первой LUT 21 подключается к соответствующим запоминающим устройствам 251, 252, 253, 254, 255, 256, 257, 258 статической ОП (оперативной памяти). Соответствующие запоминающие устройства статической ОП обеспечивают конфигурационные входы второй LUT 22 и других LUT, обеспеченных в системе (не показаны). При работе эти запоминающие устройства 251, 252, 253, 254, 255, 256, 257, 258 обеспечивают постоянное предопределенное логическое значение к каждому из восьми программирующих входов каждой LUT. Содержимое каждой ячейки SRAM схематично показано, как содержащее триггер-защелки, созданные из двух инверторов, каждый принимает выход другого, с транзисторным переключателем, переключаемым с помощью числовой линии 23, обеспеченной для вывода выборочного выводимого значения на выходе одного из инверторов в триггер-защелке к битовой линии, подключенной к соответствующему конфигурационному входу LUT 217, и также к линии 24 данных, посредством которой может устанавливаться значение триггер-защелки. Битовая линия каждого запоминающего устройства 251, 252, 253, 254, 255, 256, 257, 258 подключается к шине 24 выбора, и числовая линия каждого запоминающего устройства 251, 252, 253, 254, 255, 256, 257, 258 подключается к шине 23 данных. Во время фазы включения схемы каждое запоминающее устройство 251, 252, 253, 254, 255, 256, 257, 258 адресуется по очереди, и требуемое значение устанавливается в рассматриваемую триггер-защелку. Логические параметры работы LUT в соответствии с любым двоичным значением на его трех входах данных может таким образом определяться при необходимости. Это является базовым фундаментальным понятием технологии FPGA. Следует признать, однако, что функции, которые может реализовывать один логический блок, содержащий две LUT3, ограничены, однако с помощью взаимного подключения множества соответствующим образом конфигурируемых LUT, как описано выше, может реализовываться любая произвольная комбинаторная функция. Это взаимное подключение достигается через программируемое взаимное подключение каналов 2501, 2502 передачи данных и дополнительных каналов (не показаны), переносящих данные от другой LUT. Как показано, когда каналы 2501, 2502 размещаются вертикально, обеспечивается дополнительный канал 2503, пересекающий каналы 2501, 2502. На пересечении соответствующих линий каналов 2501 и 2503 обеспечивается программируемый переключающий блок 26. Полагая, что пересечение этих двух линий формирует в общей сложности четыре подключения в переключающем блоке, переключающий блок содержит 6 транзисторных переключателей, подготовленных для того, чтобы создавать и разрывать подключение между любыми двумя из этих четырех подключений. Каждый из этих транзисторных переключателей устанавливается в открытое или закрытое состояние с помощью значения, принимаемого из соответствующего блока статического запоминающего устройства 261, 262, 263, 264, 265, 266. Дополнительно, такие программируемые переключающие блоки с соответствующими статическими запоминающими устройствами обеспечиваются на многих или на всех пересечениях дорожек (не показаны). Эти статические запоминающие устройства 261, 262, 263, 264, 265, 266, как показано, идентичны запоминающим устройствам 251, 252, 253, 254, 255, 256, 257, 258, и подключаются к тем же самым адресной шине и шине данных 23 и 24, так, чтобы во время фазы включения схемы и запоминающие устройства LUT, и запоминающие устройства переключателя могли адресоваться по очереди, и требуемое значение устанавливалось в рассматриваемую триггер-защелку, так, чтобы режим работы каждой LUT и ее подключение к любой другой LUT могли конфигурироваться, когда требуется.

WO2012/123243 A1, US7463056 B1, US6021513 A, US5432441 A, US8091001 B2, US5675589 A и US5027355 A описывают конкретные аспекты вышеописанного.

Статья, озаглавленная «Bridging the Gap between Soft and Hard eFPGA Design», by Victor Olubunmi AkenʹOva, глава 3.22, доступная из https://www.ece.ubc.ca/~lemieux/publications/akenova-masc2005.pdf, обеспечивает дополнительную справочную информацию.

Хотя описанный подход очень гибок, следует признать, что дорожки взаимного подключения между LUT и адресной шиной и шинами данных запоминающих устройств занимают значительное количество пространства. Даже в сильно упрощенной структуре на фиг. 2 количество показанных линий является значительным, и это быстро становится обременительным в любой реальной реализации. Это дополнительно усиливается необходимостью реализовывать функциональные возможности тестирования в схеме, обеспечиваемой для подтверждения правильного режима работы, когда устройство изготавливается, что требует добавления еще дополнительных функций.

Сущность изобретения

Согласно первому аспекту обеспечивается программируемая пользователем вентильная матрица, имеющая возможность реализации логической функции, указанная программируемая пользователем вентильная матрица содержит множество аппаратных поисковых таблиц, линии выбора или выходы каждой поисковой таблицы программируемым образом взаимно подключаются к линиям выбора или выходам другой указанной поисковой таблицы посредством множества программируемых переключателей. Эта программируемая пользователем вентильная матрица отличается тем, что дополнительно содержит множество триггеров в конфигурации сдвигового регистра и создает программируемый сдвиговый регистр, каждая поисковая таблица имеет по меньшей мере один вход, соединенный с выходом соответствующего указанного триггера, и каждый указанный программируемый переключатель соединен с выходом дополнительного соответствующего указанного триггера; и причем указанная программируемая пользователем вентильная матрица подготавливается для работы в первом режиме, в котором указанный программирующий сдвиговый регистр загружается предопределенными тестовыми значениями, и во втором режиме, в котором указанный программирующий сдвиговый регистр загружается значениями, реализующими указанную логическую функцию.

Программирование FPGA посредством программирующего сдвигового регистра уменьшает пространство кристалла, выделенное для адресации ячеек запоминающих устройств, и улучшает возможность тестирования методами цепочки сканирования, в особенности в целях производства в промышленных масштабах.

Согласно развитию первого аспекта первый триггер в программирующем сдвиговом регистре соединен с входным мультиплексором, принимающим предопределенные тестовые значения на первом входе, и указанные значения, реализующие указанную логическую функцию - на втором входе, и в зависимости от сигнала выбора режима, настроенному для подачи к указанному первому триггеру или тестового образца, или битового потока данных.

Это подразумевает, что конкретные физические ресурсы могут совместно использоваться двумя функциональными возможностями, не увеличивая площадь поверхности.

Согласно дальнейшему развитию первого аспекта программирующий сдвиговый регистр является одним из множества таких программирующих сдвиговых регистров, выполненных с возможностью обеспечения различных частей указанной программируемой пользователем вентильной матрицы.

Множество программирующих сдвиговых регистров увеличивает гибкость при тестировании из-за возможности использования модульного подхода для организации в цепочку сканирования, и уменьшает потребляемую мощность из-за меньшего количества триггеров, синхронизируемых в любой момент времени.

Согласно дальнейшему развитию первого аспекта множество программирующих сдвиговых регистров конфигурируются для загрузки указанными предопределенными тестовыми значениями в указанном первом режиме или указанными значениями, реализующими указанную логическую функцию, - в указанном втором режиме, параллельно.

Параллельная загрузка множества программирующих сдвиговых регистров может уменьшать время инициализации и ограничивать суммарную потребляемую мощность из-за совместного использования синхросигналов.

Согласно дальнейшему развитию первого аспекта множество программирующих сдвиговых регистров конфигурируются для загрузки указанными предопределенными тестовыми значениями в указанном первом режиме или указанными значениями, реализующими указанную логическую функцию, - в указанном втором режиме, последовательно.

Последовательная загрузка множества программирующих сдвиговых регистров может упрощать программирование и ограничивать суммарную потребляемую мощность.

Согласно дальнейшему развитию первого аспекта программируемая пользователем вентильная матрица дополнительно содержит систему адресации, посредством которой любой из указанного множества программирующих сдвиговых регистров может отдельно или группой адресоваться для загрузки указанными предопределенными тестовыми значениями в указанном первом режиме или указанными значениями, реализующими указанную логическую функцию, - в указанном втором режиме.

Возможность адресации отдельно или группой программирующих сдвиговых регистров увеличивает гибкость и уменьшает время инициализации и потребляемую мощность из-за возможности адресации только тех программирующих сдвиговых регистров, которые на самом деле требуются для конкретного применения.

Согласно дальнейшему развитию первого аспекта система адресации содержит соответствующим образом адресуемый синхронизирующий логический элемент, ассоциированный с каждым программирующим сдвиговым регистром или группой, синхронизирующий логический элемент настраивается для обеспечения синхросигнала к программирующему сдвиговому регистру, с которым он ассоциирован, когда адресуется таким образом.

Управление адресацией посредством синхронизации уменьшает потребляемую мощность с помощью ограничения распространения синхроимпульсов.

Согласно дальнейшему развитию первого аспекта программируемая пользователем вентильная матрица дополнительно настраивается для реализации третьего режима работы, в котором значения, реализующие логическую функцию, загруженные в программирующие сдвиговые регистры во втором режиме работы, считываются назад из программирующих сдвиговых регистров для сравнения со значениями, реализующими логическую функцию, загруженными во втором режиме.

Возможность сравнения исходного битового потока конфигурирования с фактической конфигурацией в триггерах после рабочей фазы обеспечивает средство для обнаружения ошибочных результатов из-за повреждения конфигурационных значений, например, в космических, военных приложениях или в приложениях ядерной промышленности.

Согласно второму аспекту обеспечивается способ работы FPGA, содержащий этапы, на которых выдают команду мультиплексору, который имеет выход, соединенный с программирующим сдвиговым регистром, выбрать вход, принимающий конфигурационные значения, реализующие тестовый протокол, и дают команду множеству триггеров LUT, чтобы они вошли в тестовую конфигурацию, в которой каждый указанный триггер LUT принимает вводимую информацию, реализующую указанный тестовый протокол, и причем указанные триггеры LUT подключаются в качестве сдвигового регистра. Программирующий сдвиговый регистр затем синхронизируется для загрузки его первого набора элементов конфигурационными значениями LUT, принадлежащими указанным конфигурационным значениям, реализующим указанный тестовый протокол, и загрузки второго набора элементов указанного сдвигового регистра конфигурацией маршрутизирующего переключателя, принадлежащей указанным конфигурационным значениям, реализующим указанный тестовый протокол. Затем дают команду множеству триггеров LUT, чтобы они вошли в рабочую конфигурацию, в которой каждый указанный триггер LUT принимает вводимую информацию с выходов множества LUT, соответственно, и вводимые данные затем применяются ко множеству LUT. Триггеры LUT затем синхронизируются для выборки выходов каждой указанной LUT в соответствующий указанный триггер, выходы зависят от указанного тестового протокола и указанных входов данных. Затем триггерам LUT дают команду, чтобы они вошли в тестовую конфигурацию, в которой триггеры LUT подключаются в сдвиговом регистре LUT, и они подключаются в качестве сдвигового регистра, и синхронизируют для считывания значений указанного сдвигового регистра LUT, содержащего указанные выходы указанных LUT, в зависимости от указанного тестового протокола и указанных входов данных.

Согласно третьему аспекту обеспечивается способ работы FPGA, содержащий этапы, на которых дают команду мультиплексору, который имеет выход, соединенный с программирующим триггером, выбрать вход, принимающий конфигурационные значения, реализующие логическую функцию, и дают команду указанному множеству триггеров LUT войти в рабочую конфигурацию, в которой каждый указанный триггер LUT принимает вводимую информацию с выходов LUT, соответственно. Способ затем переходит к синхронизации программирующего сдвигового регистра для загрузки его первого набора элементов конфигурационными значениями LUT, принадлежащими указанным конфигурационным значениям, реализующим указанную логическую функцию, и загрузки второго набора элементов указанного сдвигового регистра конфигурацией маршрутизирующего переключателя, принадлежащей указанным конфигурационным значениям, реализующим указанную логическую функцию.

Согласно развитию третьего аспекта способ содержит дополнительные этапы, на которых подают разрешающий сигнал для вывода первого программирующего сдвигового регистра в качестве указанного программирующего сдвигового регистра, и повторяют этапы синхронизации и выдачи команды дополнительным указанным программирующим сдвиговым регистрам.

Согласно четвертому аспекту обеспечивается способ работы FPGA, содержащий этапы, на которых синхронизируют первый программирующий сдвиговый регистр для считывания его первого набора элементов с конфигурационными значениями LUT, реализующими логическую функцию, и для считывания второго набора элементов указанного сдвигового регистра с конфигурацией маршрутизирующего переключателя, реализующей логическую функцию.

Согласно развитию четвертого аспекта способ содержит дополнительные этапы, на которых подают разрешающий сигнал для вывода первого программирующего сдвигового регистра в качестве указанного программирующего сдвигового регистра, и повторяют этапы синхронизации для дополнительных программирующих сдвиговых регистров.

Согласно дальнейшему развитию четвертого аспекта способ содержит дополнительный этап сравнения конфигурации LUT, реализующей логическую функцию, и конфигурации маршрутизирующего переключателя, реализующей логическую функцию, которые считываются из программирующего сдвигового регистра, с конфигурацией LUT, реализующей логическую функцию, и конфигурацией маршрутизирующего переключателя, реализующей логическую функцию, которые первоначально записываются в сдвиговый регистр.

Согласно пятому аспекту изобретения обеспечивается компьютерная программа, настроенная для реализации этапов способа по второму или третьему аспекту.

Реализация способа в компьютерной программе обеспечивает удобный механизм для взаимодействия с FPGA и реализации изобретения на гибкой и стандартизированной платформе.

Согласно шестому аспекту изобретения обеспечивается считываемый компьютером носитель, который содержит на себе компьютерную программу по пятому аспекту.

Краткое описание чертежей

Вышеупомянутые и другие преимущества настоящего изобретения будут теперь описаны со ссылкой на сопроводительные чертежи, на которых:

фиг. 1 схематично показывает пример системы FPGA, которая известна в уровне техники;

фиг. 2 показывает более подробную информацию об элементах системы FPGA, которая известна в уровне техники;

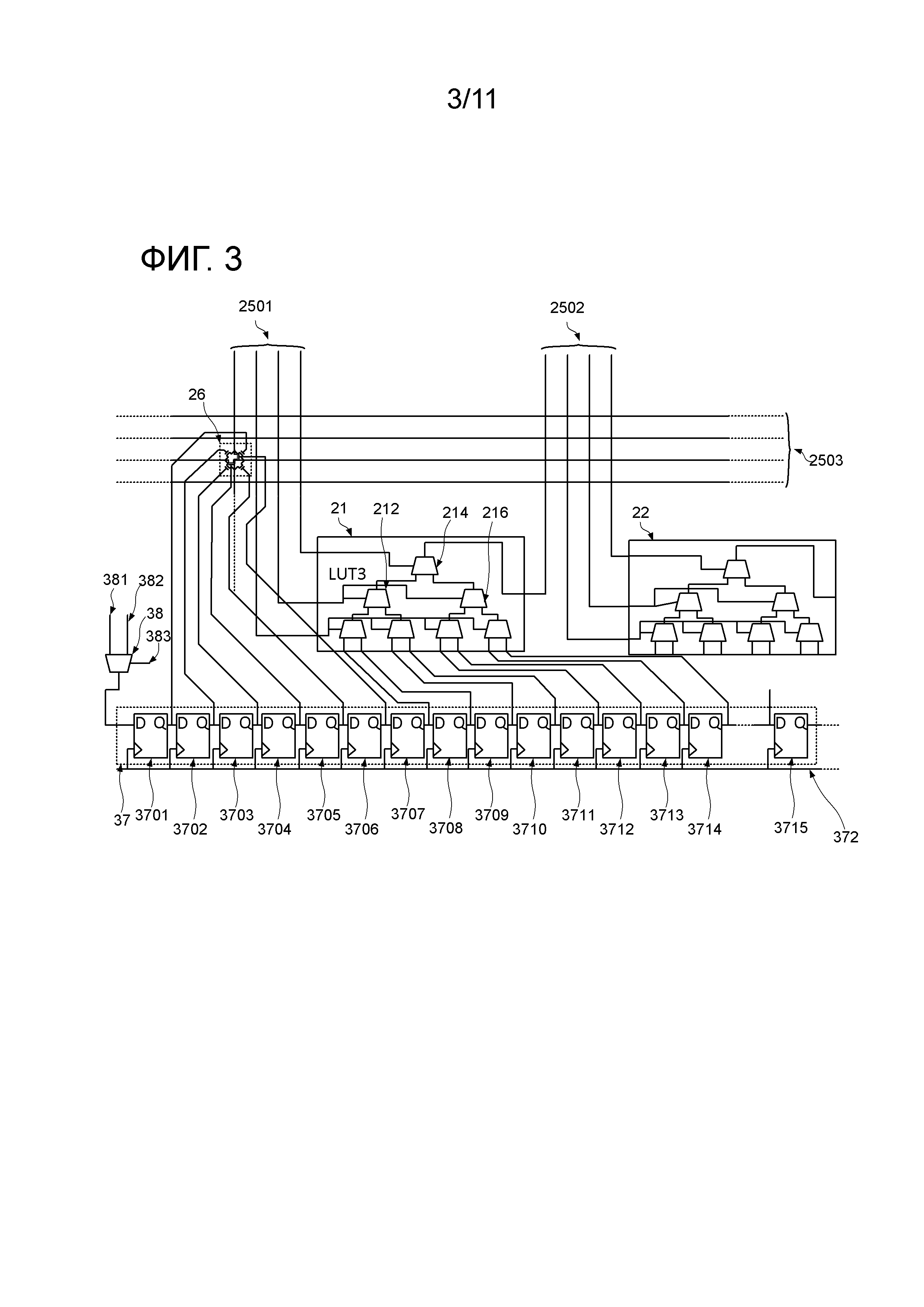

фиг. 3 показывает элементы системы FPGA в соответствии с вариантом осуществления настоящего изобретения;

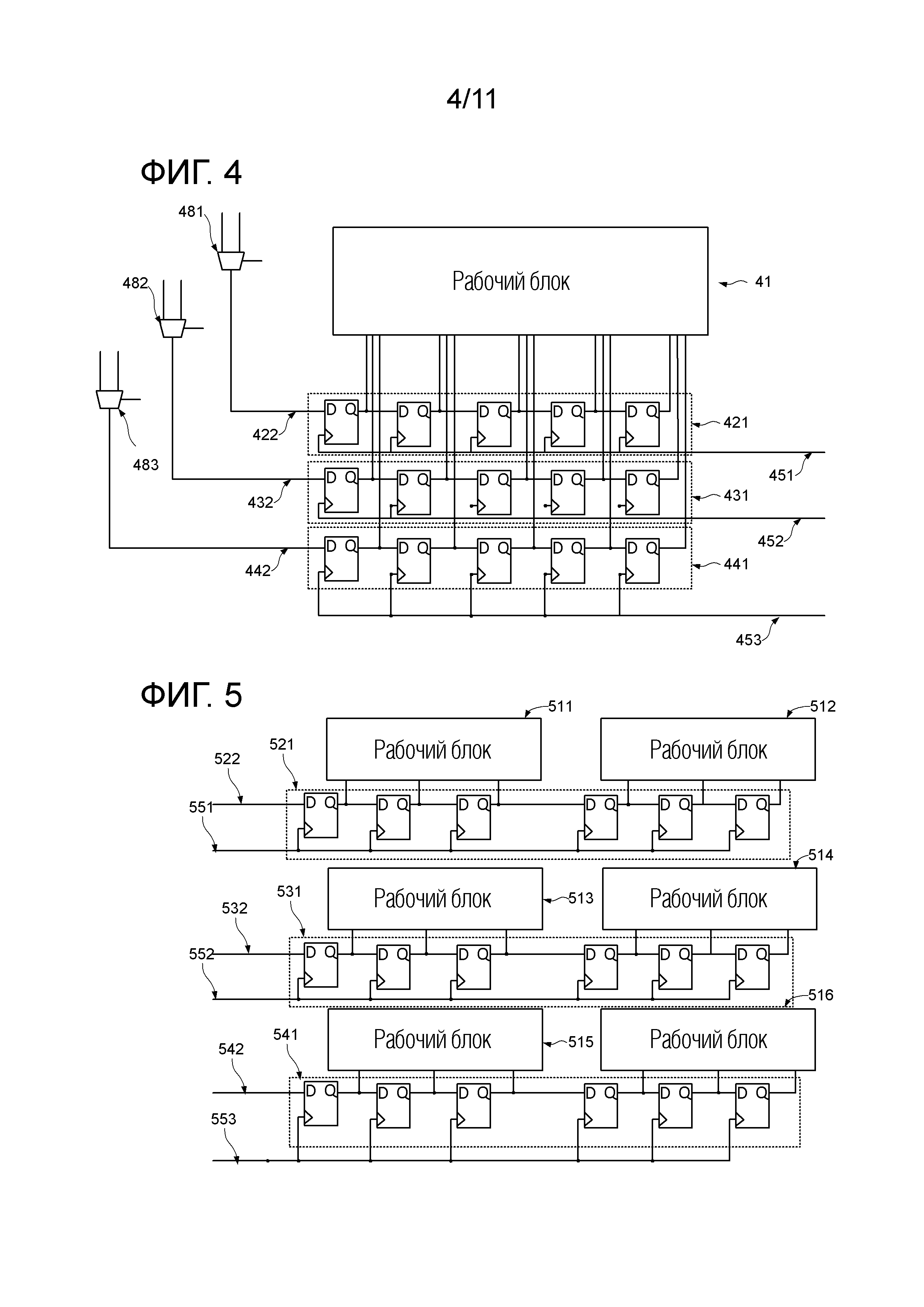

фиг. 4 показывает первую конфигурацию для конфигурирования схемы FPGA;

фиг. 5 показывает вторую конфигурацию для конфигурирования схемы FPGA;

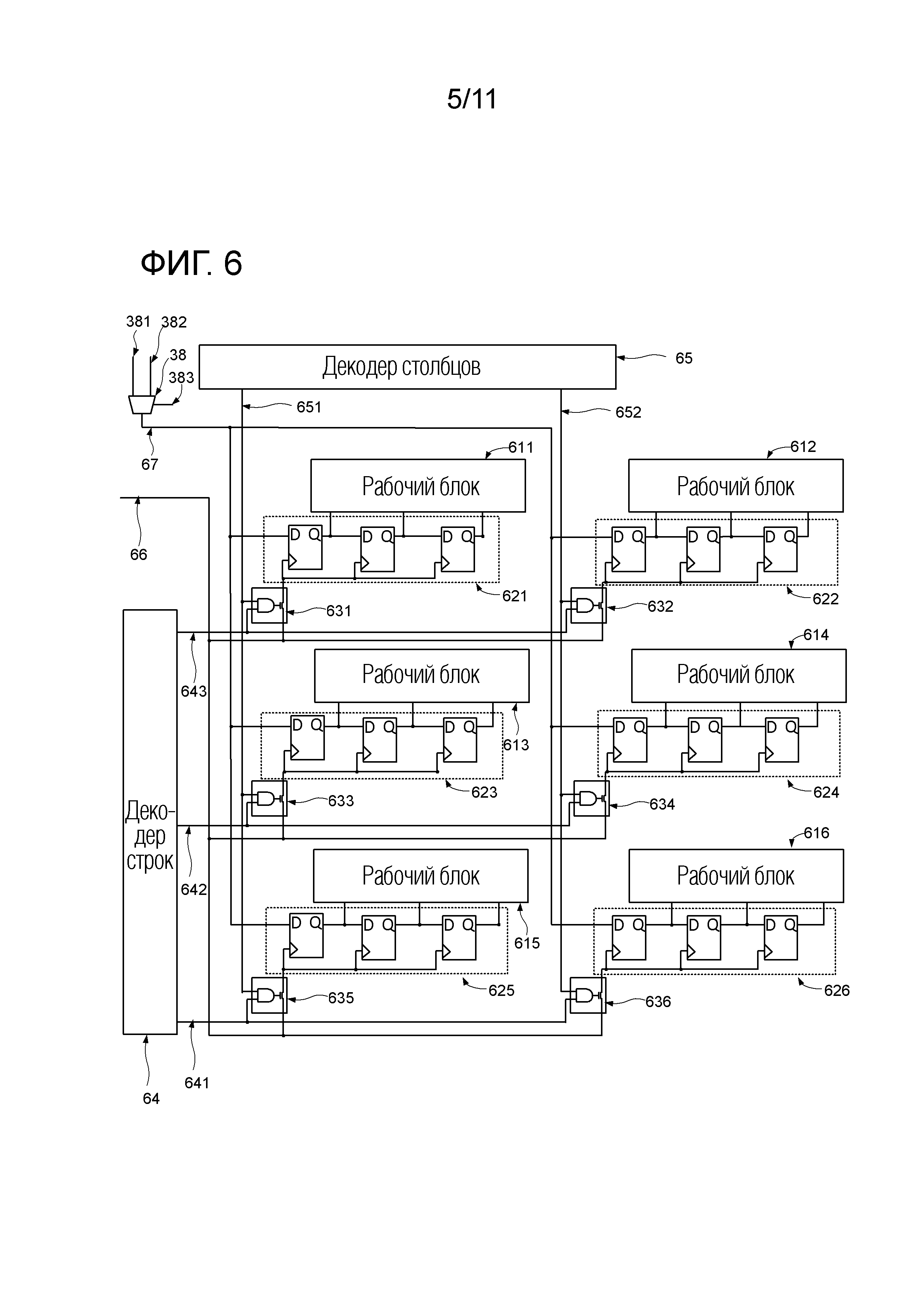

фиг. 6 показывает третью конфигурацию для конфигурирования схемы FPGA;

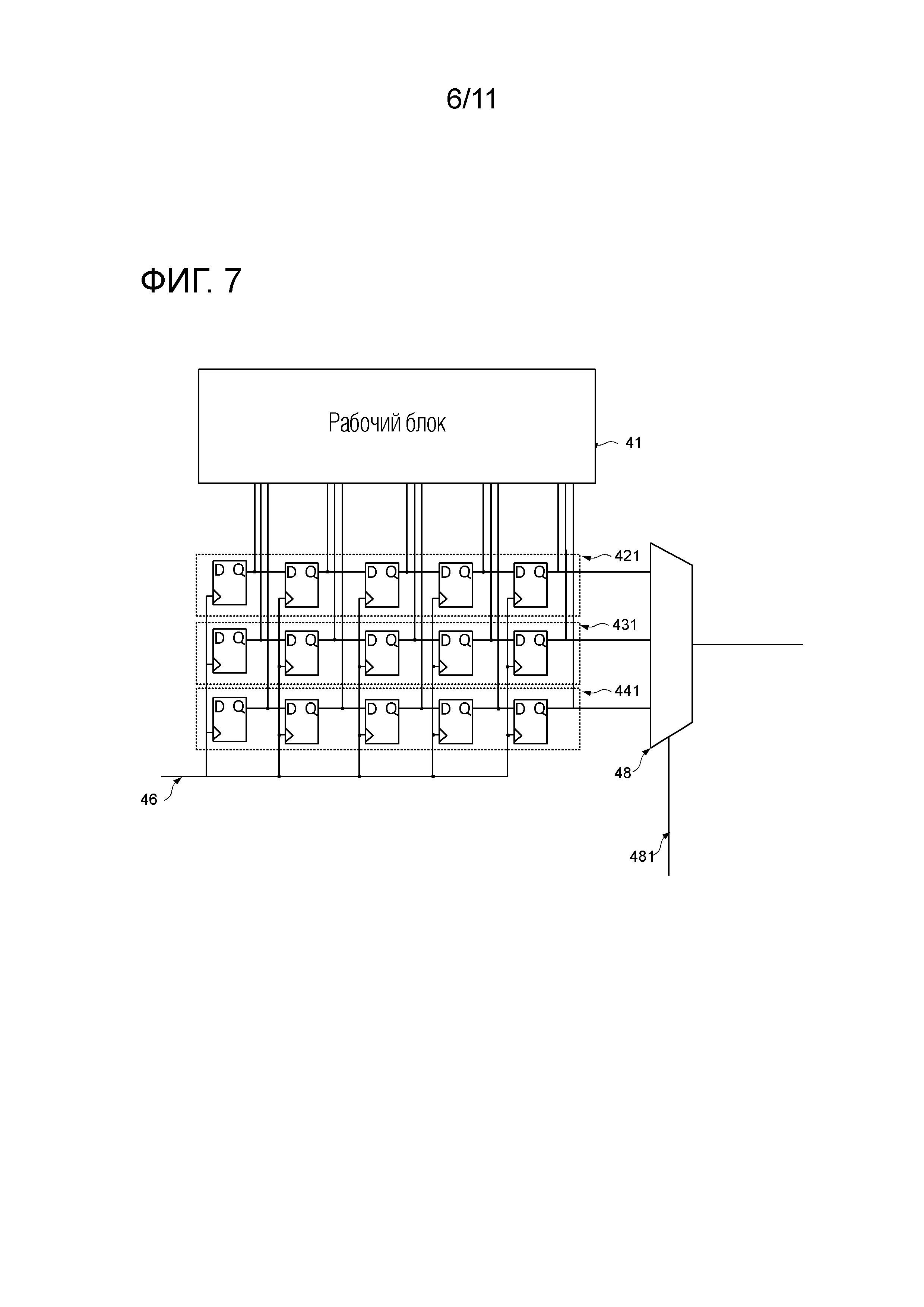

фиг. 7 показывает модификацию структуры на фиг. 4, настроенную для считывания конфигурации;

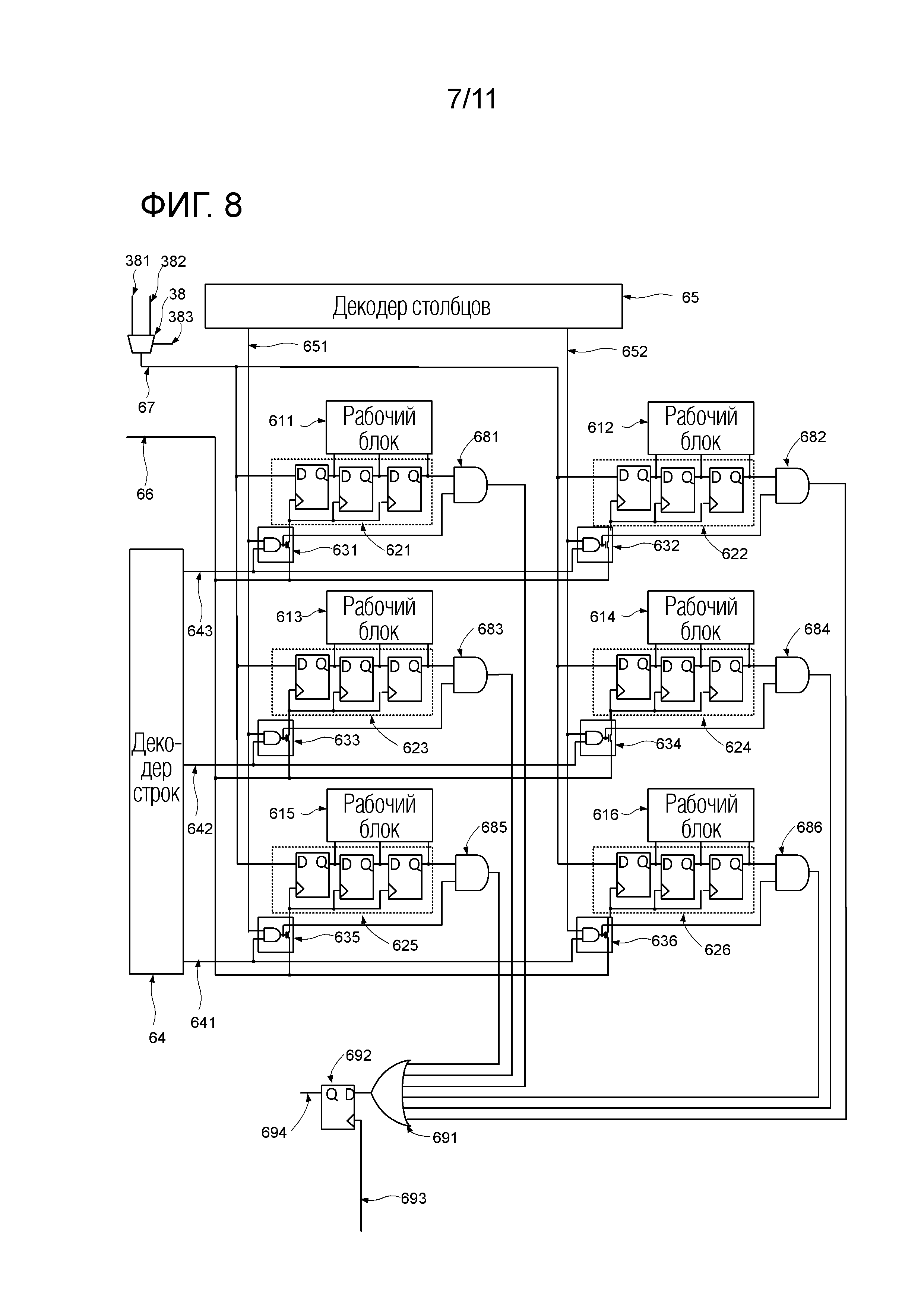

фиг. 8 показывает модификацию структуры на фиг. 6, настроенную для считывания конфигурации;

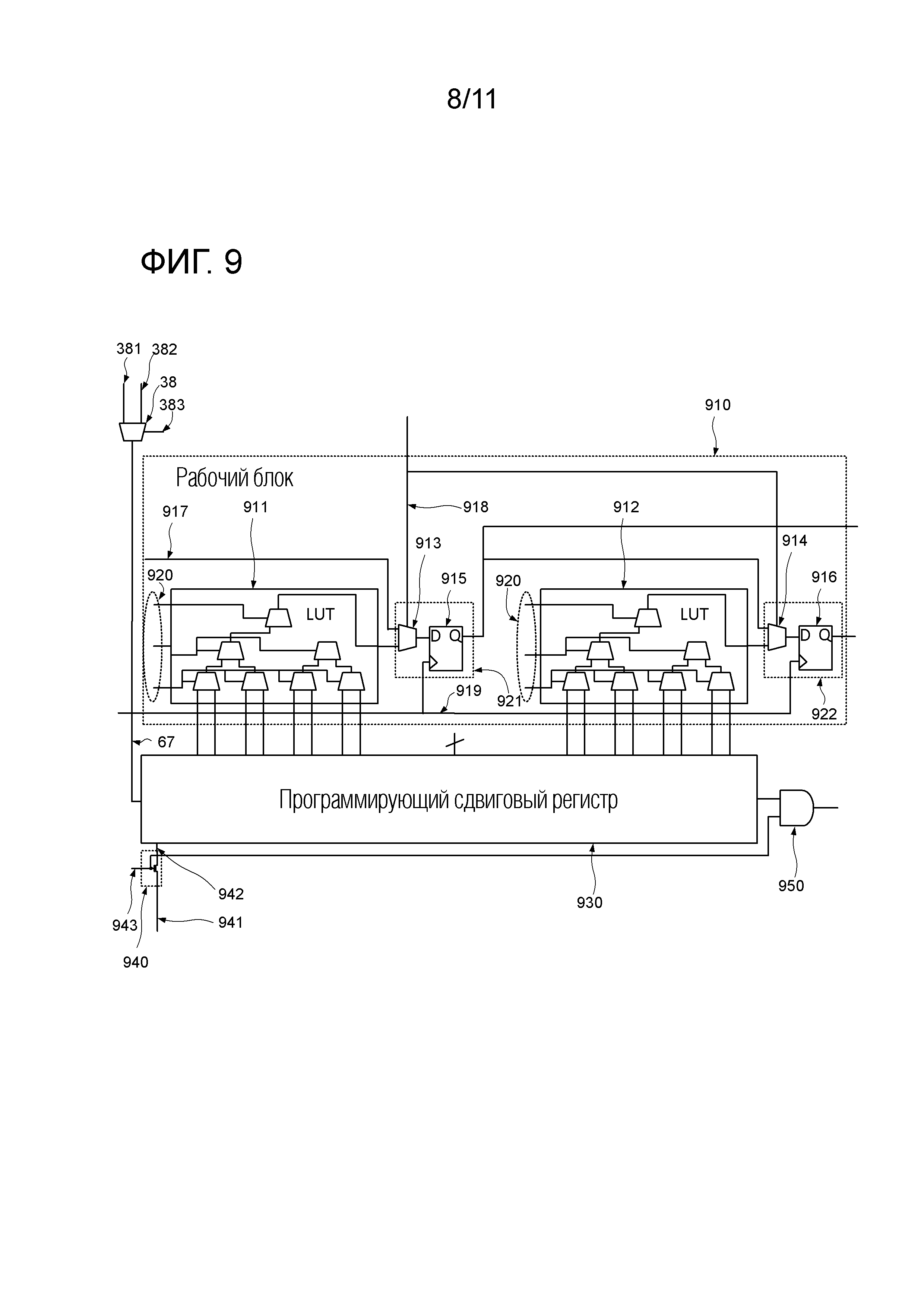

фиг. 9 показывает более подробную информацию о рабочем блоке в соответствии с дополнительным вариантом осуществления;

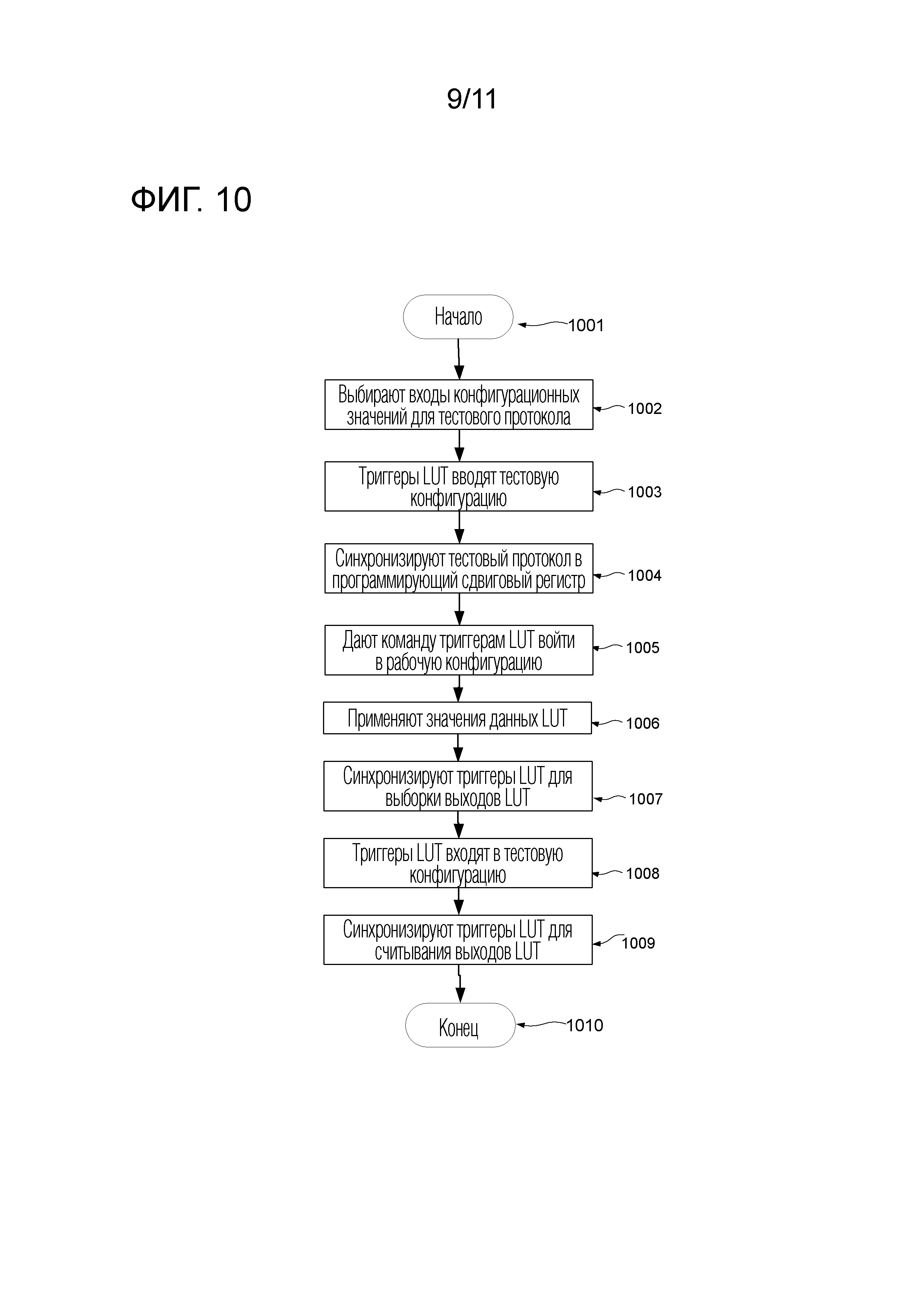

фиг. 10 показывает способ загрузки FPGA в соответствии с вариантом осуществления;

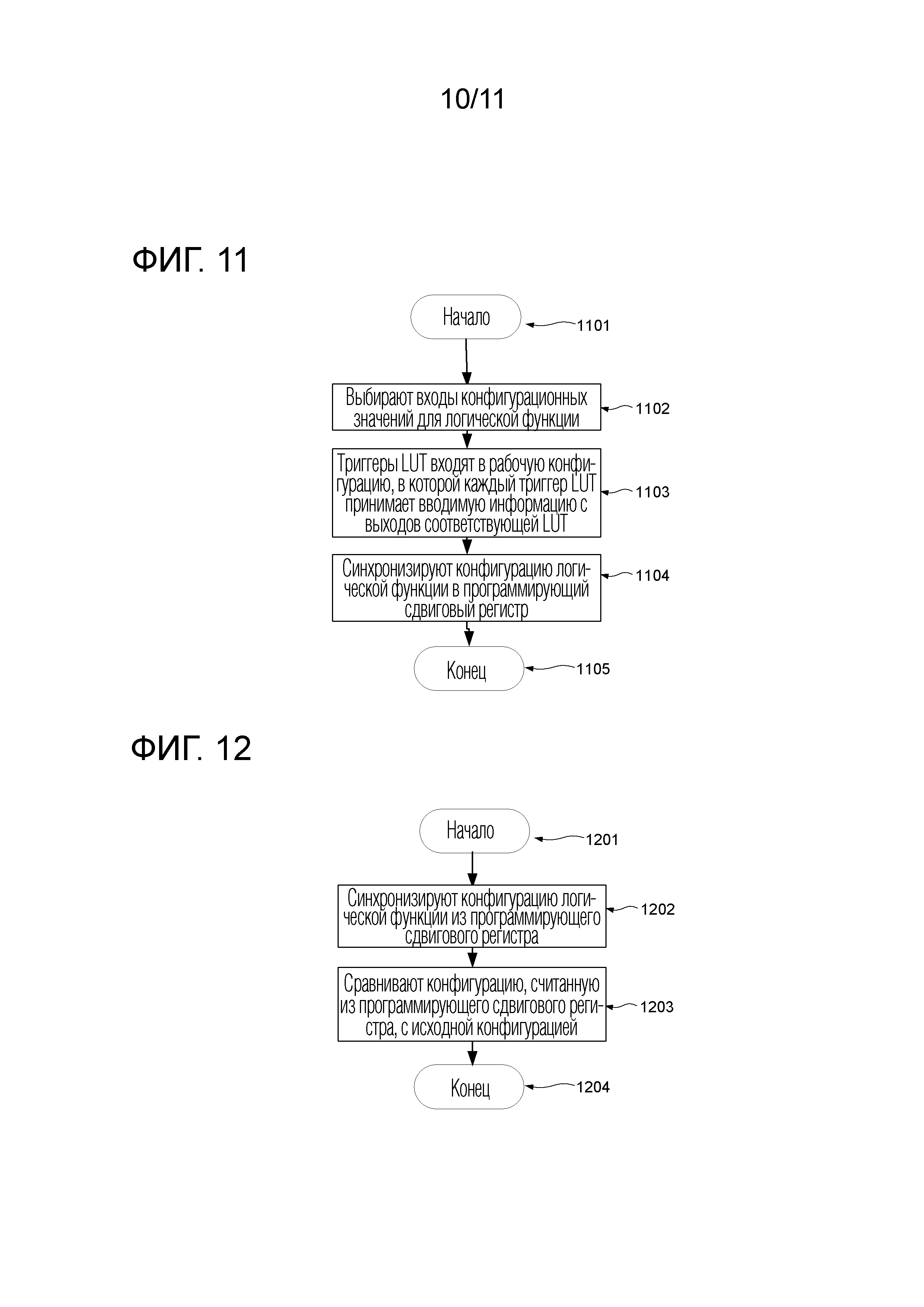

фиг. 11 показывает способ работы FPGA в соответствии с вариантом осуществления;

фиг. 12 показывает способ проверки FPGA в соответствии с дополнительным вариантом осуществления;

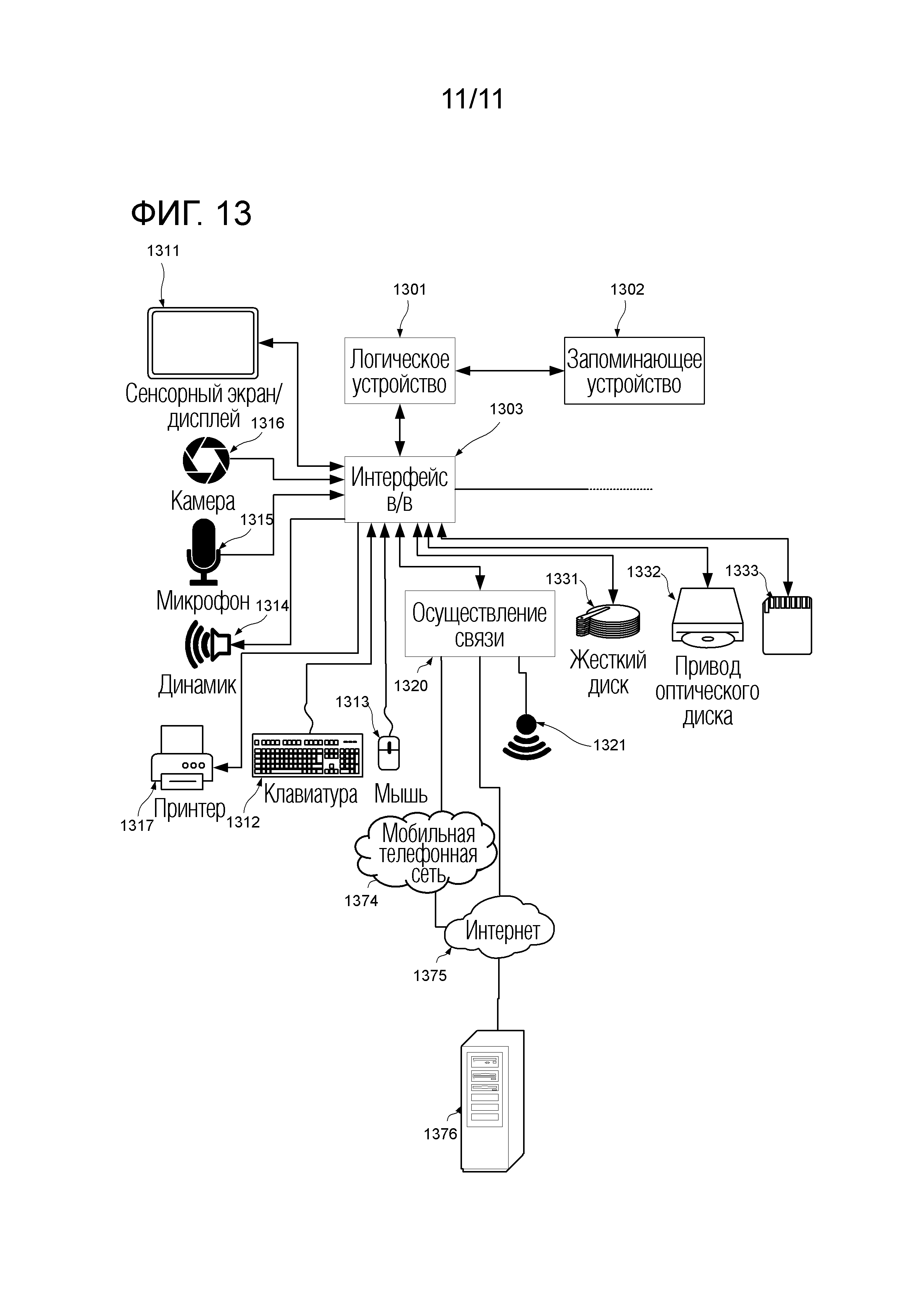

фиг. 13 показывает универсальную вычислительную систему, подходящую для реализации вариантов осуществления изобретения.

Осуществление изобретения

Фиг. 3 показывает элементы системы FPGA в соответствии с вариантом осуществления настоящего изобретения.

Элементы, показанные на фиг. 3, формируют типичный пример частичной реализации частей функциональных возможностей, описанных выше по отношению к фиг. 1, в соответствии с вариантом осуществления настоящего изобретения.

Как показано на фиг. 3, обеспечивается первая поисковая таблица (LUT) 21 и вторая поисковая таблица (LUT) 22, и множество дополнительных LUT (не показаны). Первая LUT 21 содержит семь двухвходовых мультиплексоров 211, 212, 213, 214, 215, 216, 217 (ссылочные знаки не используются на фиг. 3), соответственно. Вторая LUT и дополнительные LUT конфигурируются так же. Эти мультиплексоры размещаются каскадным способом с тремя рядами, формируя 8-входовой мультиплексор, выход которого формирует выход LUT. Оба первых ряда мультиплексоров (211, 213, 215 и 217) в каждой каскадной структуре имеют в общей сложности восемь входов. Эти восемь входов формируют программирующие входы первой LUT 21. Входы выбора каждого ряда объединяются для образования трех входов данных LUT. Входы данных и выход данных первой LUT подключаются к набору дорожек 2501, 2502. Входы и выходы второй и дополнительных LUT подключаются, соответственно, к сети дополнительных дорожек (не показаны). Традиционно LUT с 3 входами данных таким образом упоминается как «LUT3».

В соответствии с этим вариантом осуществления каждый из восьми программирующих входов первой LUT 21 подключается, соответственно, к контакту Q D-триггера 3707, 3708, 3709, 3710, 3711, 3712, 3713, 3714.

Точно так же конфигурационные входы второй LUT 22 и других LUT, обеспеченных в системе (не показаны), обеспечиваются дополнительными D-триггерами (не показаны). Эти триггеры размещаются с триггерами 3707, 3708, 3709, 3710, 3711, 3712, 3713, 3714 для образования программирующего сдвигового регистра 37 с помощью подключения выхода Q каждого триггера к входу D следующего и объединения входов синхронизации каждого триггера в одну линию 372 синхронизации. При работе эти запоминающие устройства обеспечивают постоянное предопределенное логическое значение к каждому из восьми программирующих входов каждой LUT, таким же образом, как устройства SRAM, описанные со ссылкой на фиг. 2

Во время фазы инициирования схемы кодовое слово, соответствующее необходимому окончательному значению каждого триггера в программирующем сдвиговом регистре, вводится в первый триггер 3701 в программирующем сдвиговом регистре бит за битом и синхронизируется по программирующему сдвиговому регистру один бит единовременно до тех пор, пока первый бит не достигнет последнего триггера и первый триггер не примет свое окончательное значение.

Система на фиг. 3 реализует механизм взаимных подключений, аналогичный механизму взаимных подключений, описанному выше по отношению к фиг. 2. В соответствии с этим вариантом осуществления, однако, каждый транзисторный переключатель программируемого блока 26 переключения устанавливается в открытое или закрытое состояние с помощью значения, принятого от соответствующего триггера 3701, 3702, 3703, 3704, 3705, 3706, принадлежащего программирующему сдвиговому регистру 37. Дополнительно, такие программируемые переключатели с соответствующими триггерными устройствами обеспечиваются на многих или на всех пересечениях дорожек (не показаны). Соответственно, во время фазы включения схемы битовый поток, соответствующий необходимому окончательному значению каждого триггера в программирующем сдвиговом регистре для реализации любой логической функции, которая требуется от FPGA, вводится в первый триггер 3701 в программирующем сдвиговом регистре бит за битом и синхронизируется по программирующему сдвиговому регистру один бит единовременно до тех пор, пока первый бит не достигнет последнего триггера и первый триггер не примет свое окончательное значение, таким образом определяя значения маршрутизирующих переключателей и конфигурационных входов LUT за один раз.

Система на фиг. 3 дополнительно содержит мультиплексор 38, переключающийся между двумя входами 381 и 382. В соответствии с вариантом осуществления один вход 381 может принимать поток параметров установки, соответствующий значениям параметров установки, которые будут загружены в программирующий сдвиговый регистр 37 для реализации используемой программы FPGA, т.е. любой произвольной последовательности битов, и может требоваться для пользователя, пока другой вход 382 мультиплексора может принимать поток параметров установки, соответствующий установкам, требуемым для различных компонентов системы в тестовой конфигурации.

Замена ячеек запоминающего устройства SRAM D-триггерами подразумевает увеличение количества транзисторов и, соответственно, идет вразрез с требованиями разработки стандартной ИС.

С помощью использования триггеров для управления маршрутизирующими переключателями и конфигурационными входами LUT становится возможным реализовать способ тестирования цепочек сканирования, не добавляя дополнительных триггеров, в частности, для тестирования. Это не только компенсирует упомянутое выше увеличение количества транзисторов, но и дополнительно упрощает структуру кристалла, в частности, по отношению к маршрутизации и управлению тестовыми компонентами.

Кроме того, с помощью устранения необходимости адресации и шин данных для большого количества ячеек SRAM, можно значительно сэкономить с точки зрения области кристалла, обычно выделяемой для этих целей.

Соответственно, раскрывается программируемая пользователем вентильная матрица, имеющая возможность реализации логической функции, указанная программируемая пользователем вентильная матрица содержит множество аппаратных поисковых таблиц, линии выбора или выходы каждой поисковой таблицы программируемым образом взаимно подключаются к линиям выбора или выходам другой указанной поисковой таблицы посредством множества программируемых переключателей, указанная программируемая пользователем вентильная матрица отличается тем, что дополнительно содержит:

множество триггеров в конфигурации программирующего сдвигового регистра, каждая указанная поисковая таблица имеет по меньшей мере один вход, соединенный с выходом соответствующего указанного триггера, и каждый указанный программируемый переключатель соединен с выходом дополнительного соответствующего указанного триггера; и

причем указанная программируемая пользователем вентильная матрица подготавливается для работы в первом режиме, в котором указанный программирующий сдвиговый регистр загружается предопределенными тестовыми значениями, и во втором режиме, в котором указанный программирующий сдвиговый регистр загружается значениями, реализующими указанную логическую функцию.

Первый триггер в указанном программирующем сдвиговом регистре может соединяться с входным мультиплексором, указанный входной мультиплексор принимает указанные предопределенные тестовые значения на первом входе и указанные значения, реализующие указанную логическую функцию, на втором входе, и в зависимости от сигнала выбора режима, настраиваться для подачи к указанному первому триггеру или указанного тестового образца, или указанного битового потока данных.

Хотя фиг. 3 показывает один программирующий сдвиговый регистр 37, следует признать, что поскольку предложенный механизм масштабируется для слияния большего количества LUT и программируемых переключателей, может стать необходимым реализовать множество или многомерные программирующие сдвиговые регистры.

Соответственно, программирующий сдвиговый регистр, например, который описан со ссылкой на фиг. 3, может быть одним из множества таких программирующих сдвиговых регистров, выполненных с возможностью обеспечения различных частей указанной программируемой пользователем вентильной матрицы.

Такое множество программирующих сдвиговых регистров может конфигурироваться для загрузки предопределенными тестовыми значениями в первом режиме или указанными значениями, реализующими логическую функцию, во втором режиме, параллельно или последовательно.

Специалист должен признать, что хотя система на фиг. 3 сильно упрощена, реальные системы будут значительно более сложными, не отступая от принципов, описанных в настоящем документе. В частности, каждый логический блок может содержать больше одной LUT и может дополнительно содержать дополнительные логические схемы, например, для поддержания расширенных функциональных возможностей или представления последовательного контроля. Множество таких логических блоков могут размещаться вместе в группах.

Возвращаясь к фиг. 1, очевидно, что хотя дорожки 14, которые обеспечивают подключения между элементами в рабочем режиме, показаны схематично, адресные шины и шины данных 23 и 24 не показаны, в реальном устройстве они будут вносить очень значительный вклад в площадь поверхности устройства. Структура программирующего сдвигового регистра на фиг. 3 решает эту проблему, так как становится возможно загружать битовый поток для большого количества запоминающих устройств в программирующий сдвиговый регистр, без необходимости отдельной адресации каждой ячейки запоминающего устройства. Это и более просто в работе, и менее требовательно с точки зрения площади поверхности, что касается дорожек шины и адресации. Следует признать, тем не менее, что может быть нежелательно обеспечивать один программирующий сдвиговый регистр, который содержит в себе все конфигурационные ячейки для всего устройства FPGA, так как такой программирующий сдвиговый регистр станет неуправляемо длинным, с последствиями для управления синхронизацией, потребляемой мощности и т.п. Между тем, возможно применять подход на основе множества программирующих сдвиговых регистров, причем каждый программирующий сдвиговый регистр управляет параметрами конфигурирования для конкретной части кристалла. Первый триггер в каждом таком программирующем сдвиговом регистре или группе программирующих сдвиговых регистров может адресоваться аналогично отдельным ячейкам запоминающего устройства на фиг. 2, или иным образом. Выбор длины каждого программирующего сдвигового регистра в таком случае становится компромиссом между более длинными программирующими сдвиговыми регистрами с более простым распределением битового потока конфигурирования с одной стороны и более короткими программирующими сдвиговыми регистрами с более сложным распределением битового потока конфигурирования - с другой, что может подразумевать более широкие шины и/или более сложную адресацию. Оптимальный компромисс в любом данном случае будет зависеть от используемой полупроводниковой технологии и различных характеристик самой схемы FPGA.

Фиг. 4 показывает первую конфигурацию для конфигурирования схемы FPGA. Как показано, обеспечивается рабочий блок 41, содержащий одну или более LUT, возможно со вспомогательной схемой и соответствующими программируемыми маршрутизирующими переключателями, и т.д. Как показано, этот рабочий блок 41 обеспечивается конфигурационными значениями с помощью трех программирующих сдвиговых регистров 421, 431 и 441, принимающих вводимые значения от трех входных подключений 422, 432, 442, и каждый имеет соответствующие синхроимпульсы 451, 452, 453. Каждая линия 422, 432, 442 имеет свой собственный соответствующий входной мультиплексор 481, 482, 483, которым можно управлять для переключения между рабочим битовым потоком или тестовым образцом, как описано выше, например, при программируемом управлении. В альтернативных вариантах осуществления множество программирующих сдвиговых регистров может принимать вводимую информацию от одного мультиплексора. Выход мультиплексора может передаваться к соответствующим программирующим сдвиговым регистрам с помощью соответствующим образом управляемого демультиплексора, или может адресоваться, например, как объясняется в последующих вариантах осуществления.

Как показано, три программирующих сдвиговых регистра имеют только пять триггеров, однако следует признать, что в рабочих реализациях программирующие сдвиговые регистры в общем случае будут значительно более длинными. Рабочие реализации будут также в общем случае содержать больше трех программирующих сдвиговых регистров. Программирующие сдвиговые регистры показаны, как все содержащие одинаковое количество триггеров, однако в некоторых случаях конкретный программирующий сдвиговый регистр может содержать любое количество триггеров.

Внимание должно уделяться синхронизации различных программирующих сдвиговых регистров для обеспечения, чтобы правильное значение достигало каждого триггера. Это подразумевает, что каждый программирующий сдвиговый регистр должен принимать количество синхронизирующих импульсов, равное его длине, и не больше, так как дополнительные импульсы привели бы к синхронизации значений вперед вне их правильного места назначения. Одним из подходов к этой проблеме является определение всех программирующих сдвиговых регистров, как имеющих одинаковую длину, как показано на фиг. 4. В качестве альтернативы, когда определяются сдвиговые регистры отличающейся длины, они могут ассоциироваться со схемой управления синхронизацией, настроенной для обеспечения, чтобы каждый сдвиговый регистр принимал количество синхросигналов, равное его длине, во время фазы инициализации. Согласно еще одному дополнительному подходу, для каждого программирующего сдвигового регистра может обеспечиваться схема управления синхронизацией, настроенная для распознавания конкретной последовательности битов, указывающей на конкретное расположение в битовом потоке, предназначенном для этого сдвигового регистра, такой как начало или конец битового потока. Когда устройство управления синхронизацией обнаруживает эту последовательность, оно отключает вход синхронизации. Этот подход имеет преимущество в том, что каждый сдвиговый регистр становится независимым, и оставляет разработчику свободу определять программирующие сдвиговые регистры произвольного размера. Также переключение между сигналами и синхронизация программирующих сдвиговых регистров могут приводиться в действие с помощью программного обеспечения.

Фиг. 5 показывает вторую конфигурацию для конфигурирования схемы FPGA. Как показано на фиг. 5, FPGA структурируется вокруг матрицы из логических блоков 511, 512, 513, 514, 515, 516, аналогичным образом, как FPGA на фиг. 1. Каждому ряду логических блоков обеспечивают соответствующий программирующий сдвиговый регистр, так, чтобы логические блоки 511 и 512 принимали конфигурационные значения из программирующего сдвигового регистра 521, чтобы логические блоки 513 и 514 принимали конфигурационные значения из программирующего сдвигового регистра 531, а логические блоки 515 и 516 принимали конфигурационные значения из программирующего сдвигового регистра 541. Как показано, каждый из трех программирующих сдвиговых регистров содержит шесть триггеров, из которых три соединяются с каждым логическим блоком. У всех триггеров в соответствующем программирующем сдвиговом регистре входы синхронизации объединены, в то время как каждый программирующий сдвиговый регистр имеет свои собственные соответствующие синхроимпульсы 551, 552, 553.

Как показано, три программирующих сдвиговых регистра имеют только шесть триггеров, однако следует признать, что в рабочих реализациях программирующие сдвиговые регистры в общем случае будут значительно более длинными. Рабочие реализации будут также в общем случае содержать больше трех программирующих сдвиговых регистров. Программирующие сдвиговые регистры показаны, как все содержащие одинаковое количество триггеров, однако в некоторых случаях это может быть недопустимым конструктивным ограничением, в этом случае каждый программирующий сдвиговый регистр может содержать любое количество триггеров.

Внимание должно уделяться синхронизации отличающихся программирующих сдвиговых регистров для обеспечения, что правильное значение достигает каждого триггера, в этом отношении применяются аналогичные меры, как обсуждается выше по отношению к фиг. 4.

Мультиплексирование между рабочим битовым потоком и тестовым образцом может реализоваться, например, как описано по отношению к предшествующим вариантам осуществления. Распределение рабочего битового потока или тестового образца и, соответственно, синхросигналов, может распределяться среди программирующих сдвиговых регистров, например, как описано по отношению к предыдущим вариантов осуществления.

С помощью реализации прямой структурной связи между архитектурой программирующего сдвигового регистра и расположением логических блоков, вводится структурированный подход для генерации битового потока конфигурирования, который, вероятно, упростит программирование FPGA.

Фиг. 6 показывает вторую конфигурацию для конфигурирования схемы FPGA. Как показано на фиг. 6, FPGA структурируется вокруг матрицы логических блоков 611, 612, 613, 614, 615, 616, аналогичным образом по отношению к FPGA на фиг. 5. Каждому логическому блоку предоставляют соответствующий программирующий сдвиговый регистр 621, 622, 623, 624, 625, 626. Как показано, каждый из шести программирующих сдвиговых регистров 621, 622, 623, 624, 625, 626 содержит три триггера, обеспечивая конфигурационные значения для ассоциированного с ними логического блока.

Первый триггер каждого программирующего сдвигового регистра принимает свой вход на входной линии 67, которая соединяется совокупно с входом D первого триггера каждого программирующего сдвигового регистра.

У всех триггеров в каждом программирующем сдвиговом регистре входы синхронизации объединены.

Единая сеть 66 распространения синхроимпульсов соединяется с линией синхронизации каждого программирующего сдвигового регистра с помощью соответствующего синхронизирующего логического элемента 631, 632, 633, 634, 635, 636. Эти синхронизирующие логические элементы, как показано, каждый имеет входы выбора ряда и выбора столбца, посредством чего одновременно присутствующие логические единицы на обоих входах замыкает переключатель, подключая линию синхронизации соответствующего программирующего сдвигового регистра к сети 66 распространения синхроимпульсов для приема синхронизирующих импульсов.

Как показано, существуют 2 линии 651 и 652 выбора столбца и 3 линии 641, 642, 643 выбора ряда. Входы выбора каждого синхронизирующего логического элемента подключаются к соответствующим образом отличающейся комбинации линий выбора столбца и линий выбора ряда, так, чтобы с помощью установки конкретной линии выбора столбца и линии выбора ряда в логический высокий уровень, был активирован один синхронизирующий логический элемент, вход выбора ряда и вход выбора столбца которого подключены к этим двум линиям выбора.

Так как значения данных от входной линии будут распространяться только через программирующий сдвиговый регистр, когда он принимает входные синхроимпульсы, с помощью направления синхросигнала к одному выбранному программирующему сдвиговому регистру можно выборочно программировать любой программирующий сдвиговый регистр с помощью одной входной линии 67.

Линиями 651, 652 выбора столбца управляют с помощью декодера 65 столбца, а линиями выбора ряда 641, 642, 643 управляют с помощью декодера 64 ряда. Эти декодеры принимают команды, координируемые со значениями на входной линии 67, для адресации значения на входной линии 67 туда, куда программирующий сдвиговый регистр предназначен. По сути, во время фазы инициализации схема на фиг. 6 принимает не только битовый поток конфигурирования на линии 67 и синхроимпульсы на линии 66, но также и битовый поток адресации в декодерах 64 и 65.

Тот факт, что только подмножество триггеров, т.е. те триггеры, которые принадлежат логическим блокам, программируются для синхронизации в установленное время, приводит к значительному сокращению потребляемой мощности.

Следует признать, что в реальных системах, реализуемых в FPGA, множество логических блоков будут конфигурироваться одинаково для реализации обычных функций. Преимуществом настоящего изобретения является то, что можно подавать разрешающий сигнал на синхронизирующий логический элемент больше одного программирующего сдвигового регистра так, чтобы те же конфигурационные значения могли синхронизироваться в несколько программирующих сдвиговых регистров параллельно. Это уменьшает время инициализации FPGA и уменьшает потребляемую мощность.

Как показано, три программирующих сдвиговых регистра имеют только три триггера, однако следует признать, что в рабочих реализациях программирующие сдвиговые регистры в общем случае будут значительно более длинными. Рабочие реализации будут также в общем случае содержать больше шести логических блоков и, соответственно, больше шести программирующих сдвиговых регистров. Программирующие сдвиговые регистры показаны, как содержащие все одинаковое количество триггеров, однако, так как каждый программирующий сдвиговый регистр синхронизируется независимо, подход на фиг. 6 одинаково хорошо подходит для структуры, в которой каждый программирующий сдвиговый регистр может содержать любое количество триггеров.

Эти функциональные возможности адресации могут также реализоваться посредством стандартных интегральных схем стробирования синхронизации, или иным образом. Конкретные варианты осуществления могут обеспечивать общий разрешающий сигнал для группы или для всех программирующих сдвиговых регистров вместе с помощью отдельной адресации.

С помощью реализации прямой структурной связи между архитектурой программирующего сдвигового регистра и расположением логических блоков, вводится структурированный подход для генерации битового потока конфигурирования, который, вероятно, упростит программирование FPGA.

Следует признать, что данная FPGA может подразделяться на узлы, которые программируются независимо, и что комбинации отличающихся архитектур программирующего сдвигового регистра, например, как описано по отношению к фиг. 4, 5 и 6, возможны в той же FPGA по отношению к ее отличающимся частям.

В некоторых применениях будет необходимо считывать назад параметры конфигурации, сохраненные в отличающихся ячейках конфигурирующего запоминающего устройства. Несмотря на то, что в принципе они, как можно ожидать, будут идентичны битовому потоку конфигурирования, обеспеченному при инициализации системы, на практике существуют конкретные обстоятельства, когда это может не происходить. Например, облучение ионизирующим излучением, как это может происходить в космосе, при высотных полетах, в применениях в ядерной энергетике и военных применениях, которые могут изменять значения в ячейках конфигурирующего запоминающего устройства случайным образом, фальсифицируя результаты последующей обработки с помощью FPGA. Сравнение исходного битового потока с сохраненными считанными значениями из битов конфигурационного запоминающего устройства обеспечивает средство для определения, могло ли это произойти.

По сути, раскрыта программируемая пользователем вентильная матрица, содержащая систему адресации, посредством которой любой из указанного множества программирующих сдвиговых регистров может отдельно адресоваться для загрузки указанными предопределенными тестовыми значениями в указанном первом режиме или указанными значениями, реализующими указанную логическую функцию, в указанном втором режиме.

Кроме того, эта система адресации может содержать соответствующим образом адресуемый синхронизирующий логический элемент, ассоциированный с каждым из программирующих сдвиговых регистров, этот синхронизирующий логический элемент настраивается для обеспечения синхросигнала к программирующему сдвиговому регистру, с которым он ассоциирован, когда адресуется таким образом.

Фиг. 7 показывает модификацию структуры на фиг. 4, настроенную для считывания конфигурации. Как показано на фиг. 7, обеспечивается тот же рабочий блок 41, ассоциированный с теми же программирующими сдвиговыми регистрами 421, 431, 441, как описано со ссылкой на фиг. 4. Как показано, последний триггер в каждом из трех программирующих сдвиговых регистров обеспечивает свой выход не только к компонентам схемы FPGA 41, но также и к мультиплексору 48. Мультиплексор 48 таким образом принимает вводимую информацию от последнего триггера каждого из трех программирующих сдвиговых регистров 421, 431, 441.

При работе, когда фаза обработки FPGA завершена и результаты созданы, может быть необходимо сохранить конфигурацию конфигурирующих триггеров для обеспечения непротиворечивости с исходным битовым потоком, как обсуждается выше. Когда это требуется, программирующие сдвиговые регистры синхронизируются через линию 46 синхронизации, и выход каждого программирующего сдвигового регистра выбирается с помощью мультиплексора 48 для создания мультиплексированного битового потока, который обычно должен быть идентичен исходному битовому потоку конфигурации. Сигнал 481 выбора к мультиплексору может просто побуждать циклический выбор трех входов с частотой синхронизации в три раза больше на линии 46 синхронизации или может содержать программирующую последовательность, конкретную для каждого синхронизирующего импульса, например, когда программирующие сдвиговые регистры имеют отличающуюся длину.

Следует признать, что подход на фиг. 7 легко настраивается для структуры на фиг. 5.

Фиг. 8 показывает модификацию структуры на фиг. 6, настроенную для считывания конфигурации. Как показано на фиг. 8, FPGA структурируется вокруг той же матрицы логических блоков 611, 612, 613, 614, 615, 616, каждому логическому блоку предоставляют соответствующий программирующий сдвиговый регистр 621, 622, 623, 624, 625, 626 и синхронизирующие логические элементы 631, 632, 633, 634, 635, 636, как описано по отношению к фиг. 6. Как показано, структура дополнительно содержит шесть логических элементов 681, 682, 683, 684, 685, 686 «И», каждый имеет один вход, подключенный к выходу последнего триггера соответствующего одного из шести программирующих сдвиговых регистров 621, 622, 623, 624, 625, 626. Каждый из вторых входов каждого из этих шести логических элементов 681, 682, 683, 684, 685, 686 «И» подключается к выходу логического элемента «И» соответствующего синхронизирующего логического элемента 631, 632, 633, 634, 635, 636. Таким образом механизм адресуемого разрешения синхронизации может также использоваться для выборочного разрешения вывода из рабочего блока. Каждый из выходов этих шести логических элементов «И» подключается к соответствующим входам шестивходового логического элемента 691 «ИЛИ», выход которого подается на вход D выходного триггера 692.

При работе, когда рабочая фаза FPGA завершена и результат создан, может быть необходимо сохранить конфигурацию конфигурирующих триггеров для обеспечения непротиворечивости с исходным битовым потоком, как обсуждается выше. Когда это требуется, разрешающая линия устанавливается в высокий логический уровень, так, чтобы выбранный логический элемент «И» передавал значение на выходе последнего триггера каждого программирующего сдвигового регистра к логическому элементу 691 «ИЛИ». На синхронизирующий логический элемент, чьи значения программирующего сдвигового регистра должны выводиться, подается разрешающий сигнал через декодер 64 ряда и декодер 65 столбца таким же образом, как для ввода описанного выше битового потока конфигурирования, и первый синхронизирующий импульс достигает выбранного программирующего сдвигового регистра. Если последний триггер в синхронизируемом программирующем сдвиговом регистре производит логический высокий уровень, то это побуждает соответствующий логический элемент «И», принимающий это значение, выводить логический высокий уровень, который передается с помощью логического элемента «ИЛИ» 691 к входу D выходного триггера 692 и хранится там до тех пор, пока выход триггер не принимает синхронизирующий импульс на входе 693, после чего значение выводится на линию 684. Таким образом, посредством подачи разрешающего сигнала для вывода через синхронизирующий логический элемент, как описано выше, синхронизируя программирующие сдвиговые регистры и выходной триггер координируемым образом, сохраненные значения в каждом программирующем сдвиговом регистре конфигурирования могут считываться и сравниваться с исходным битовым потоком.

Соответственно, программируемая пользователем вентильная матрица может дополнительно настраиваться для реализации третьего режима работы, в котором значения, реализующие логическую функцию, загруженные в программирующие сдвиговые регистры во втором режиме работы, считываются назад из указанных программирующих сдвиговых регистров.

Следует понимать, что конкретные варианты осуществления могут описываться с точки зрения последовательности этапов способа программирования FPGA.

Хотя приведенное выше в общем случае описывает программирующие сдвиговые регистры, предназначенные для конфигурирования или маршрутизирующих переключателей, или LUT, следует признать, что любой триггер в любом программирующем сдвиговом регистре может соединяться с любым элементом FPGA, по требованию.

Фиг. 9 показывает более подробную информацию о рабочем блоке в соответствии с дополнительным вариантом осуществления.

Как показано на фиг. 9, обеспечивается рабочей блок 910, соответствующий диапазону рабочих блоков, например, которые описаны со ссылкой на предшествующие варианты осуществления. Этот рабочий блок 910 содержит две LUT 911 и 912. Выход каждой LUT 911, 912 подключается к соответствующему мультиплексору 913, 914. Выход этих мультиплексоров 913, 914 подключается к соответствующему триггеру 915, 616. Вместе, соответствующий мультиплексор 913, 914 и соответствующий триггер 915, 916, формируют соответствующий триггер 921, 922 двойной конфигурации LUT. Второй вход мультиплексора 913 подключается к линии 917 ввода тестового значения. Второй вход мультиплексора 914 подключается к выходу 916 триггера LUT. Входы выбора этих двух мультиплексоров 913, 914 подключаются совокупно к линии 918 выбора тестового режима. Выход каждого триггера 915, 916 LUT обеспечивает выходную линию рабочего блока 910. Два триггера 915, 916 LUT управляются с помощью общей линии 919 синхронизации. Каждая LUT 911, 912 имеет три входа данных, которые вместе формируют 6 входов 920 данных рабочего блока. Дополнительно обеспечивается программирующий сдвиговый регистр 930, соответствующий программирующим сдвиговым регистрам, например, которые описаны со ссылкой на предшествующие варианты осуществления. Программирующий сдвиговый регистр обеспечивает конфигурационные значения для LUT 911, 912, и по существу множество программируемых маршрутизирующих переключателей (не показаны), как описано со ссылкой на предшествующие варианты осуществления. Синхроимпульсы 941 выборочно подключаются к линии 942 синхронизации программирующего сдвигового регистра 930 с помощью синхронизирующего логического элемента 940. Синхронизирующие логические элементы 940, как показано, имеют разрешающий вход, посредством которого логический высокий уровень замыкает переключатель, подключая линию синхронизации программирующего сдвигового регистра к синхроимпульсам 941, для приема синхроимпульсов. Вход 943 разрешения синхронизации также подключаются к одному входу программирующего выходного логического элемента «И» 950, другой вход логического элемента 950 «И» подключается к выходу последнего триггера в программирующем сдвиговом регистре 930. Первый триггер программирующего сдвигового регистра формирует вход 67 данных программирующего сдвигового регистра. Следует признать, что рабочий блок может содержать любое количество LUT, что эти LUT могут иметь любое количество входов, и что независимо от количества входов, LUT могут иметь множество выходов, некоторые или все из которых могут быть ассоциированы с триггерами LUT. Как описано выше, когда мультиплексор 913 (и 914) принимает соответствующий вход выбора, два триггера 915, 916 LUT (называют тестовым режимом) формируют сдвиговый регистр LUT. Этот сдвиговый регистр может содержать любое количество триггеров LUT, которые включают в себя триггеры в отличающихся рабочих блоках. Любая из различных конфигураций, описанных по отношению к предшествующим вариантам осуществления, одинаково настраивается для структуры на фиг. 9.

При работе эта структура поддерживает способ тестирования FPGA, который описан со ссылкой на фиг. 10.

Фиг. 10 показывает способ загрузки FPGA в соответствии с вариантом осуществления.

Как показано на фиг. 10, обеспечивается способ работы FPGA, содержащий следующие этапы. Способ начинается на этапе 1001 и переходит на этап 1002, на котором дают команду мультиплексору 38, который имеет выход, соединенный с программирующим сдвиговым регистром 930, выбрать вход 381, принимающий конфигурационные значения, реализующие тестовый протокол.

На этапе 1003 дают команду множеству триггеров 921, 922 LUT, чтобы они вошли в тестовую конфигурацию, в которой каждый указанный триггер LUT принимает вводимую информацию, реализующую указанный тестовый протокол, и причем указанные триггеры LUT подключаются в качестве сдвигового регистра LUT.

На этапе 1004 синхронизируют указанный программирующий сдвиговый регистр 930 для загрузки его первого набора элементов конфигурационными значениями LUT, принадлежащими указанным конфигурационным значениям, реализующим указанный тестовый протокол; и синхронизируют указанный программирующий сдвиговый регистр для загрузки второго набора элементов указанного сдвигового регистра конфигурацией маршрутизирующего переключателя, принадлежащей указанным конфигурационным значениям, реализующим указанный тестовый протокол.

Следует понимать, что первый набор элементов сдвигового регистра и второй набор элементов сдвигового регистра могут перемежаться по тому же самому сдвиговому регистру. Загрузка значений в сдвиговый регистр будет приводить к синхронизации сдвигового регистра для перемещения соответствующих конфигурационных значений в их необходимое заключительное положение. В некоторых случаях может быть необходимо адресовать сдвиговый регистр, в который должны загружаться эти значения. Может быть необходимо загружать значения во множество сдвиговых регистров параллельно или последовательно, в этом случае способ может выполнять итерации по множеству сдвиговых регистров перед переходом на следующий этап.

На этапе 1005 дают команду указанному множеству триггеров 921, 922 LUT, чтобы они вошли в рабочую конфигурацию, в которой каждый указанный триггер 921, 922 LUT принимает вводимую информацию с выходов множества LUT, соответственно.

На этапе 1006 применяют значения данных к указанному множеству LUT (на входах 920).

На этапе 1007 синхронизируют указанные триггеры LUT для выборки выходов каждой указанной LUT в соответствующий указанный триггер, указанные выходы зависят от указанного тестового протокола и указанных входов данных.

На этапе 1008 дают команду указанным триггерам LUT, чтобы они вошли в тестовую конфигурацию, в которой указанные триггеры LUT подключаются в сдвиговом регистре LUT, и они подключаются в качестве сдвигового регистра, и

На этапе 1009 синхронизируют указанные триггеры LUT для считывания значений указанного сдвигового регистра LUT, содержащего указанные выходы указанных LUT, в зависимости от указанного тестового протокола и указанных входов данных, и заканчивают работу на этапе 1010.

Когда тестовые значения загружаются, режим работы FPGA будет оцениваться, чтобы подтвердить соответствие ожиданиям. Подробные данные об этой процедуре тестирования будут зависеть от характеристики самой системы FPGA и выходят за рамки настоящего изобретения.

Вообще говоря, описанный выше тестовый режим используется только при заводской настройке для гарантии, что FPGA полностью обеспечивает свои функциональные возможности после изготовления.

В некоторых вариантах осуществления может определяться множество тестовых протоколов, в этом случае вышеупомянутые этапы могут выполняться с помощью итераций множество раз, каждая итерация последовательно загружает отличающийся тестовый протокол.

При работе структура на фиг. 9 дополнительно поддерживает способ работы FPGA, который описан со ссылкой на фиг. 11.

Фиг. 11 показывает способ работы FPGA в соответствии с вариантом осуществления.

Как показано на фиг. 11, обеспечивается способ работы FPGA, содержащий следующие этапы. Способ начинается на этапе 1101 и переходит на этап 1102, на котором дают команду мультиплексору, имеющему выход, соединенный с программирующим триггером, выбрать вход, принимающий конфигурационные значения, реализующие логическую функцию.

На этапе 1103 дают команду множеству триггеров LUT, чтобы они вошли в рабочую конфигурацию, в которой каждый указанный триггер LUT принимает вводимую информацию с выходов множества LUT, соответственно.

На этапе 1104 синхронизируют указанный программирующий сдвиговый регистр для загрузки его первого набора элементов конфигурационными значениями LUT, принадлежащими указанным конфигурационным значениям, реализующим указанную логическую функцию; и синхронизируют указанный программирующий сдвиговый регистр для загрузки второго набора элементов указанного сдвигового регистра конфигурацией маршрутизирующего переключателя, принадлежащей указанным конфигурационным значениям, реализующим указанную логическую функцию, и заканчивают работу на этапе 1105.

В соответствии с развитием варианта осуществления на фиг. 11, способ может содержать дополнительные этапы, на которых подают разрешающий сигнал для вывода из первого программирующего сдвигового регистра из множества программирующих сдвиговых регистров, реализующих этапы на фиг. 11 по отношению к первому программирующему сдвиговому регистру, и затем повторяют эти этапы для каждого из указанного множества сдвиговых регистров.

При работе структура на фиг. 9 дополнительно поддерживает способ проверки FPGA. Этот способ может содержать этапы синхронизации указанного первого программирующего сдвигового регистра для считывания его первого набора элементов с указанными конфигурационными значениями LUT, реализующими логическую функцию; и синхронизации указанного первого программирующего сдвигового регистра для считывания второго набора элементов указанного сдвигового регистра с конфигурацией маршрутизирующего переключателя, реализующей логическую функцию.

В соответствии с развитием этого варианта осуществления способ может содержать дополнительные этапы, на которых подают разрешающий сигнал для вывода из первого программирующего сдвигового регистра из множества программирующих сдвиговых регистров, реализующих описанное выше по отношению к первому программирующему сдвиговому регистру, и затем повторяют эти этапы для каждого из указанного множества сдвиговых регистров.

Фиг. 12 показывает способ проверки FPGA в соответствии с дополнительным вариантом осуществления.

Вариант осуществления на фиг. 12 является развитием предыдущего варианта осуществления.

Как показано на фиг. 12, обеспечивается способ работы FPGA, содержащий следующие этапы. Способ начинается на этапе 1201 и переходит на этап 1202, на котором синхронизируют указанный первый программирующий сдвиговый регистр для считывания его первого набора элементов с указанными конфигурационными значениями LUT, реализующими логическую функцию, и синхронизируют указанный первый программирующий сдвиговый регистр для считывания второго набора элементов указанного сдвигового регистра с конфигурацией маршрутизирующего переключателя, реализующей логическую функцию. Способ затем переходит на этап 1203, на котором сравнивают конфигурацию LUT, реализующую логическую функцию, и конфигурацию маршрутизирующего переключателя, реализующую логическую функцию, которые считываются из указанного сдвигового регистра, с конфигурацией LUT, реализующей логическую функцию, и конфигурацией маршрутизирующего переключателя, реализующей логическую функцию, которые первоначально вводятся в указанный сдвиговый регистр, например, в соответствии со способом, описанным со ссылкой на фиг. 11. Способ затем заканчивается на этапе 1204.

При обычных обстоятельствах ожидается, что битовый поток, загруженный в сдвиговый регистр, должен быть идентичен битовому потоку, считанному из сдвигового регистра. В случае, когда обнаруживают, что два битовых потока идентичны, рабочее состояние FPGA и соответствующие результаты могут считаться проверенными. В случае, когда битовый поток, загруженный в сдвиговый регистр, не идентичен битовому потоку, считанному из сдвигового регистра, некоторые или все результаты должны считаться ошибочными.

Следует признать, что различные комбинации этапов, описанных со ссылкой на фиг. 10, 11 и 12, могут формировать варианты осуществления изобретения.

Во многих случаях некоторые или все этапы способа могут реализоваться посредством программирования, взаимодействующего с FPGA и обеспечивающего подходящие битовые потоки, как описано выше во время тестового режима, рабочего режима и режима проверки. В некоторых случаях некоторые или все эти функциональные возможности могут реализоваться на том же самом кристалле, как FPGA, или выполняться с помощью части большей системы, которой принадлежит FPGA. В других случаях эти функциональные возможности могут обеспечиваться с помощью системы тестирования или проверки, с которой FPGA временно соединяется в целях тестирования после изготовления или проверки после генерации подозрительных результатов или появление вызывающих ошибку условий.

В некоторых вариантах осуществления способы и процессы, описанные в настоящем документе, могут реализоваться полностью или частично с помощью вычислительного устройства. Эти способы и процессы могут реализоваться посредством прикладных компьютерных программ или услуг, прикладного программного интерфейса (API), библиотеки и/или другого компьютерного программного продукта или любой комбинации таких объектов.

Фиг. 13 показывает универсальную вычислительную систему, подходящую для реализации вариантов осуществления изобретения.

Показанная на фиг. 13 система включает в себя логическое устройство 1301 и запоминающее устройство 1302. Система может дополнительно включать в себя подсистему 1311 отображения, подсистему 1312, 1313, 1315 ввода, подсистему 1320 связи и/или другие, не показанные компоненты.

Логическое устройство 1301 включает в себя одно или более физическое устройство, выполненное с возможностью исполнения команд. Например, логическое устройство 1301 может быть выполнено с возможностью исполнения команд, которые являются частью одного или более приложений, услуг, программ, подпрограмм, библиотек, задач, компонентов, структур данных или других логических конструкций. Такие команды могут реализоваться для выполнения задачи, реализации типа данных, получения состояния одного или более компонента, достижения технического результата или получения иным образом необходимого результата.

Логическое устройство 1301 может включать в себя один или более процессоров, выполненных с возможностью исполнения команд программного обеспечения. Дополнительно или альтернативно, логическое устройство может включать в себя одно или более аппаратных или аппаратно-программных логических устройств, выполненных с возможностью исполнения аппаратных или аппаратно-программных команд. Процессоры логического устройства могут быть одноядерными или многоядерными, и выполняемые в них команды могут быть выполнены с возможностью последовательной, параллельной и/или распределенной обработки. Отдельные компоненты логического устройства 1301 дополнительно могут распределяться среди двух или более отдельных устройств, которые могут удаленно располагаться и/или конфигурироваться для координируемой обработки. Аспекты логического устройства 1301 могут виртуализироваться и выполняться с помощью удаленно доступных сетевых вычислительных устройств, конфигурируемых в конфигурацию облачных вычислений.

Запоминающее устройство 1302 включает в себя одно или более физическое устройство, выполненное с возможностью хранения команд, выполняемых с помощью логического устройства для реализации способов и процессов, описанных в настоящем документе. Когда такие способы и процессы реализуются, состояние запоминающего устройства 1302 может видоизменяться - например, для хранения различных данных.

Запоминающее устройство 1302 может включать в себя съемные и/или встроенные устройства. Запоминающее устройство 1302 может содержать один или более типов запоминающих устройств, которые включают в себя оптическое запоминающее устройство (например, CD (компакт-диск), DVD (цифровой универсальный диск), HD-DVD (DVD высокой плотности), диск Blu-ray и т.д.), полупроводниковое запоминающее устройство (например, ОП, EPROM (стираемое программируемое постоянное запоминающее устройство), EEPROM (электрически стираемое программируемое постоянное запоминающее устройство) и т.д.) и/или магнитное запоминающее устройство (например, жесткий диск, гибкий диск, лентопротяжное устройство, MRAM (магнитная ОП) и т.д.), среди других. Запоминающее устройство может включать в себя энергозависимые, энергонезависимые, динамические, статические, чтения-записи, только для чтения, произвольного доступа, последовательного доступа, адресуемые по расположению, адресуемые по файлам и/или адресуемые по содержанию устройства.

В конкретной структуре система может содержать интерфейс 1303, настроенный для осуществления связи между логическим устройством 1301 и дополнительными компонентами системы. Например, дополнительные компоненты системы могут содержать съемные и/или встроенные расширенные запоминающие устройства. Расширенные запоминающие устройства могут содержать один или более типов запоминающих устройств, которые включают в себя оптическое запоминающее устройство 1332 (например, CD, DVD, HD-DVD, диск Blu-ray и т.д.), полупроводниковое запоминающее устройство 1333 (например, ОП, EPROM, EEPROM, флэш-память и т.д.) и/или магнитное запоминающее устройство 1331 (например, жесткий диск, гибкий диск, лентопротяжное устройство, MRAM и т.д.), среди других. Такое расширенное запоминающее устройство может включать в себя энергозависимые, энергонезависимые, динамические, статические, чтения-записи, только для чтения, произвольного доступа, последовательного доступа, адресуемые по расположению, адресуемые по файлам и/или адресуемые по содержанию устройства.

Следует признать, что запоминающее устройство включает в себя одно или более физическое устройство и исключает распространяющиеся сигналы как таковые. Однако аспекты команд, описанных в настоящем документе, могут альтернативно распространяться с помощью среды передачи (например, электромагнитного сигнала, оптического сигнала и т.д.), в противоположность хранению на запоминающем устройстве.

Аспекты логического устройства 1301 и запоминающего устройства 1302 могут интегрироваться вместе в одном или более логических аппаратных компонентов. Такие логические аппаратные компоненты могут включать в себя программируемые пользователем вентильные матрицы (FPGA), специализированные интегральные схемы для программ и приложений (PASIC/ASIC), стандартные части специализированных интегральных схем для программ и приложений (PSSP/ASSP), системы на кристалле (SOC) и сложные программируемые логические устройства (CPLD), например.

Термин «программа» может использоваться для описания аспекта вычислительной системы, реализуемой для выполнения конкретной функции. В некоторых случаях программу можно иллюстрировать через логическое устройство, выполняющее машиночитаемые команды, хранящиеся с помощью запоминающего устройства. Следует понимать, что отличающиеся модули могут иллюстрироваться из того же самого приложения, услуги, кодового блока, задачи, библиотеки, подпрограммы, API, функции и т.д. Аналогично, та же самая программа могут иллюстрировать с помощью отличающегося приложения, услуги, кодового блока, задачи, подпрограммы, API, функции и т.д. Термин «программа» может охватывать отдельные или группы исполняемых файлов, файлов данных, библиотек, драйверов, сценариев, записей базы данных и т.д.

В частности, система на фиг. 13 может использоваться для реализации вариантов осуществления изобретения.

Например, программа, реализующая этапы, описанные по отношению к фиг. 10, 11 или 12, может храниться в запоминающем устройстве 1302 и выполняться с помощью логического устройства 1301. Битовый поток, загружаемый в сдвиговый регистр или регистры, может генерироваться с помощью логического устройства 1301 и/или сохраняться в запоминающем устройстве 1302 или в расширенных запоминающих устройствах 1332, 1333 или 1331. Битовый поток может загружаться в сдвиговый регистр или регистры с помощью действия логического устройства 1301 через интерфейс 1320 связи. Битовый поток, считываемый из сдвигового регистра или регистров, может извлекаться с помощью действия логического устройства 1301 через интерфейс 1320 связи и/или сохраняться в запоминающем устройстве 1302 или в расширенных запоминающих устройствах 1332, 1333 или 1331. Логическое устройство 1301 может извлекать битовый поток, загруженный в сдвиговый регистр или регистры, и битовый поток, считанный из сдвигового регистра или регистров в режиме проверки, и выполнять сравнение для определения достоверности результатов.

Соответственно, изобретение может реализоваться в форме компьютерной программы.

Следует признать, что «услуга», в целях настоящего документа, является прикладной программой, выполняемой по множеству пользовательских сессий. Услуга может быть доступна одному или более компоненту системы, программ и/или других услуг. В некоторых реализациях услуга может работать на одном или более серверном вычислительном устройстве.

Когда система включает в себя подсистему 1311 отображения, она может использоваться для представления визуального представления данных, хранящихся с помощью запоминающего устройства. Это визуальное представление может принимать форму графического интерфейса пользователя (GUI). Поскольку в настоящем документе описанные способы и процессы изменяют данные, хранящиеся с помощью запоминающего устройства 1302, и таким образом преобразовывают состояние запоминающего устройства 1302, состояние подсистемы 1311 отображения может аналогично преобразовываться для визуального представления изменений в базовых данных. Подсистема 1311 отображения может включать в себя один или более дисплеев, использующим фактически любой тип технологии. Такие дисплеи могут объединяться с логическим устройством и/или запоминающим устройством в общем корпусе, или такие дисплеи могут быть внешними дисплеями.

Когда система включает в себя подсистему ввода, она может содержать или соединяться с одним или более устройством ввода данных пользователем, таким как клавиатура 1312, мышь 1313, сенсорный экран 1311 или игровой контроллер (не показан). В некоторых вариантах осуществления подсистема ввода может содержать или соединяться с выбранными компонентами естественного ввода данных пользователем (NUI). Такие компоненты могут интегрированными или внешними, и преобразование и/или обработка вводимых действий могут выполняться внутри подсистемы или вне ее. Примерные компоненты NUI могут включать в себя микрофон для распознавания речи и/или голоса; инфракрасную, цветную, стереоскопическую камеру и/или камеру глубины для машинного зрения и/или распознавания жестов; средство отслеживания головы, средство отслеживания глаз, акселерометр и/или гироскоп для обнаружения движения и/или распознавания направленности; а также компоненты обнаружения электрического поля для оценки мозговой деятельности.

Когда система включает в себя подсистему 1320 связи, она может быть выполнена с возможностью соединения с возможностью осуществления связи вычислительной системы с одним или более другим вычислительным устройством. Например, модуль связи может соединять с возможностью осуществления связи вычислительное устройство с удаленной услугой, размещаемой, например, на удаленном сервере 1376, через сеть любого размера, которая включает в себя, например, персональную сеть, локальную сеть, глобальную сеть или Интернет. Подсистема связи может включать в себя проводные и/или беспроводные устройства, совместимые с одним или более отличающимся протоколом связи. В качестве неограничивающих примеров подсистема связи может быть выполнена с возможностью осуществления связи через беспроводную телефонную сеть 1374 или через проводную или беспроводную локальную или глобальную сеть. В некоторых вариантах осуществления подсистема связи может предоставлять возможность вычислительной системе отправлять и/или принимать сообщения к и/или от других устройств через сеть, такую как Интернет 1375. Подсистема связи может дополнительно осуществлять индуктивную связь 1321 ближнего радиуса действия с пассивными устройствами (NFC (ближняя бесконтактная связь), RFID (радиочастотная идентификация) и т.д.).

Согласно конкретным вариантам осуществления конфигурационные значения для поисковых таблиц (LUT) и программируемых маршрутизирующих переключателей в FPGA обеспечиваются посредством множества триггеров, расположенных в сдвиговом регистре. Этот сдвиговый регистр может принимать тестовые значения в режиме заводского тестирования и рабочие конфигурационные значения (реализующие любую функциональную возможность, которая требуется клиенту от FPGA) в рабочем режиме. Битовые потоки обеспечиваются на одном конце сдвигового регистра, и он синхронизируется до тех пор, пока последний триггер не примет свое значение. Значения могут также синхронно выводиться на другом конце сдвигового регистра для сравнения с исходным битовым потоком для идентификации повреждения сохраненных значений, например, из-за радиоактивного облучения. Архитектура стробирования синхроимпульсами предложена для загрузки данных или считывания данных из конкретных выбранных сдвиговых регистров.

Следует понимать, что конфигурации и/или подходы, описанные в настоящем документе, являются примерными по своей природе, и что эти конкретные варианты осуществления или примеры нельзя рассматривать в ограничивающем смысле, потому что возможны многочисленные разновидности. Конкретные подпрограммы или способы, описанные в настоящем документе, могут представлять одну или более из любого количества стратегий обработки. По сути, различные показанные и/или описанные действия могут совершаться в показанной и/или описанной последовательности, в других последовательностях, параллельно, или не использоваться. Аналогично, порядок вышеописанных процессов может изменяться.

Тема настоящего раскрытия включает в себя все новые и неочевидные комбинации и подкомбинации различных процессов, систем и конфигураций и других особенностей, функций, действий и/или свойств, раскрытых в настоящем документе, а также любые и все их эквиваленты.

Реферат

Группа изобретений относится к программируемым логическим устройствам. Техническим результатом является уменьшение пространства кристалла, выделенного для адресации ячеек запоминающих устройств, улучшение тестирования. Программируемая пользователем вентильная матрица (FPGA), выполненная с возможностью реализации логической функции, при этом FPGA содержит множество аппаратных поисковых таблиц (LUT), причем линии выбора или выходы каждой LUT программируемым образом взаимно подключаются к линиям выбора или выходам другой LUT посредством множества программируемых переключателей, множество триггеров в конфигурации сдвигового регистра, при этом каждая LUT имеет по меньшей мере один вход, соединенный с выходом соответствующего триггера, и каждый программируемый переключатель соединен с выходом дополнительного соответствующего триггера; причем FPGA выполнена с возможностью работы в первом режиме, в котором сдвиговый регистр загружается заранее определенными тестовыми значениями, и во втором режиме, в котором сдвиговый регистр загружается значениями, реализующими упомянутую логическую функцию. 5 н. и 10 з.п. ф-лы, 13 ил.

Комментарии