Дифференциальный операционный усилитель - RU2616573C1

Код документа: RU2616573C1

Чертежи

Описание

Изобретение относится к области радиоэлектроники и может быть использовано в качестве прецизионного устройства усиления широкополосных сигналов.

В современной радиоэлектронной аппаратуре находят применение дифференциальные операционные усилители (ОУ), выполненные на базе входного дифференциального каскада (ДК) с активной нагрузкой в виде классических токовых зеркал [1-7]. ОУ с такой архитектурой широко применяются в составе микросхем, выпускаемыми как отечественными так и зарубежными фирмами (СА 3078, LM13600, LM13700 и NF5517) [8-11]. В них токовые зеркала обеспечивают высокую стабильность статического режима выходных транзисторов промежуточного каскада (ПК) ОУ и преобразуют изменения выходных токов входного ДК в соответствующие приращения выходного тока ПК. Однако в ОУ с данной архитектурой коэффициент усиления по напряжению получается небольшим. Это связано с тем, что входное сопротивление классических токовых зеркал, на котором выделяются выходные напряжения входного ДК, не велико (десятки Ом).

Ближайшим прототипом заявляемого устройства является операционный усилитель по патенту US 5.132.640, fig. 2. Кроме этого данная архитектура ОУ приведена в других патентах [1-7].

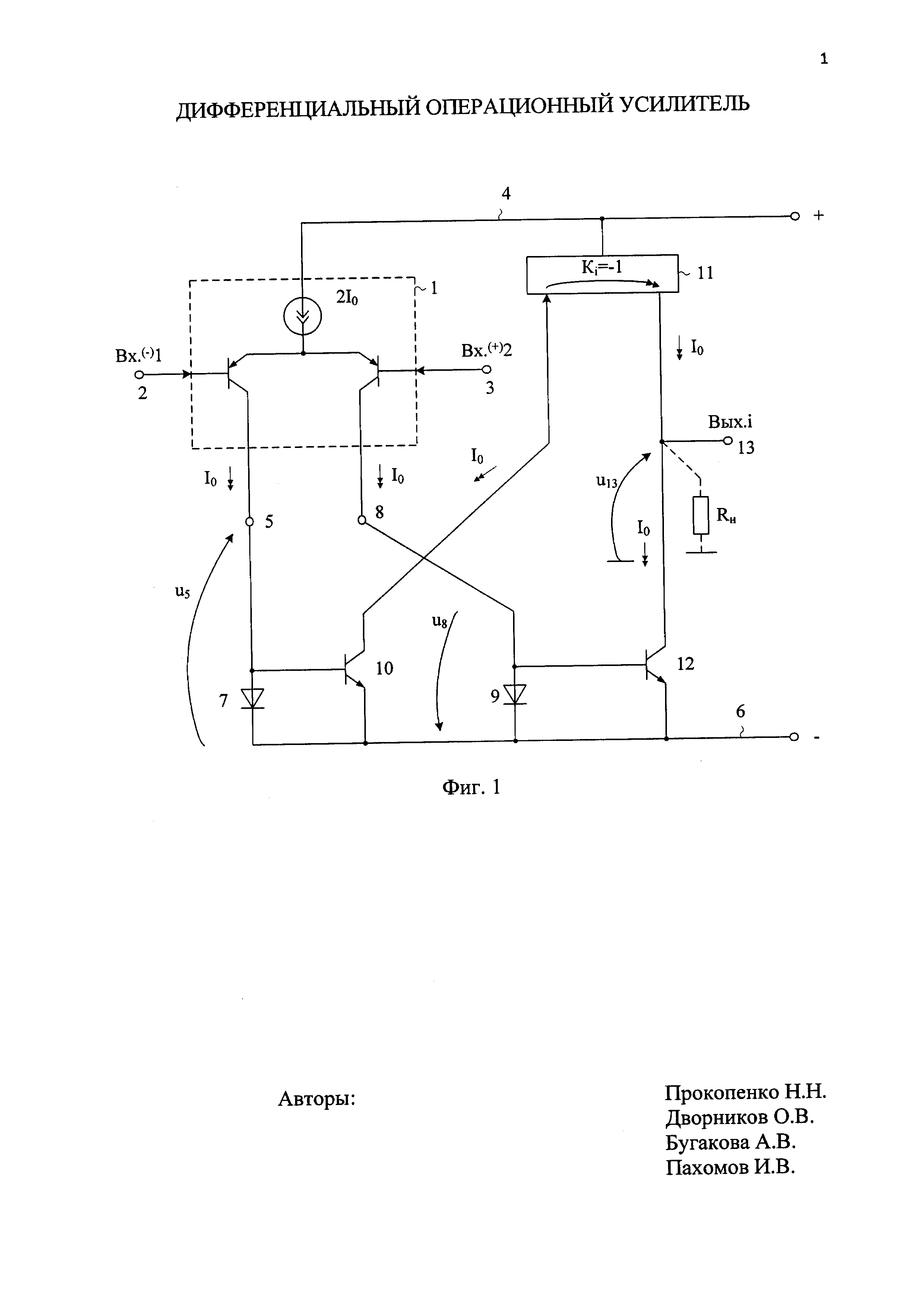

ОУ-прототип содержит (фиг. 1) входной дифференциальный каскад 1 с первым 2 и вторым 3 основными входами, согласованный с первой 4 шиной источника питания, первый 5 токовый выход входного дифференциального каскада 1, связанный со второй 6 шиной источника питания через первый 7 согласующий двухполюсник, второй 8 токовый выход входного, дифференциального каскада 1, связанный со второй 6 шиной источника питания через второй 9 согласующий двухполюсник, первый 10 выходной транзистор, база которого соединена с первым 5 токовым выходом входного дифференциального каскада 1, эмиттер подключен ко второй 6 шине источника питания, а коллектор связан со входом токового зеркала 11, согласованного с первой 4 шиной источника питания, второй 12 выходной транзистор, эмиттер которого подключен ко второй 6 шине источника питания, база соединена со вторым 8 токовым выходом входного, дифференциального каскада 1, а коллектор связан с токовым выходом токового зеркала 11 и соединен с токовым выходом устройства 13.

Существенный недостаток известного ОУ состоит в том, что при выполнении условий обеспечения высокой стабильности статического режима транзисторов его промежуточного каскада в нем невозможно получить повышенный коэффициент усиления по напряжению.

Основная задача предлагаемого изобретения состоит в повышении в 80-100 раз коэффициента усиления (Ку) разомкнутого ОУ при сохранении высокой температурной и радиационной стабильности статического режиме транзисторов его промежуточного каскада.

Поставленная задача достигается тем, что в дифференциальном операционном усилителе фиг. 1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 основными входами, согласованный с первой 4 шиной источника питания, первый 5 токовый выход входного дифференциального каскада 1, связанный со второй 6 шиной источника питания через первый 7 согласующий двухполюсник, второй 8 токовый выход входного дифференциального каскада 1, связанный со второй 6 шиной источника питания через второй 9 согласующий двухполюсник, первый 10 выходной транзистор, база которого соединена с первым 5 токовым выходом входного дифференциального каскада 1, эмиттер подключен ко второй 6 шине источника питания, а коллектор связан со входом токового зеркала 11, согласованного с первой 4 шиной источника питания, второй 12 выходной транзистор, эмиттер которого подключен ко второй 6 шине источника питания, база соединена со вторым 8 токовым выходом входного дифференциального каскада 1, а коллектор связан с токовым выходом токового зеркала 11 и соединен с токовым выходом устройства 13, предусмотрены новые элементы и связи - в схему введены первый 14, второй 15, третий 16 и четвертый 17 дополнительные выходные транзисторы, эмиттеры которых подключены ко второй 6 шине источника питания, базы первого 14 и второго 15 дополнительных выходных транзисторов соединены с базой первого 10 выходного транзистора, базы третьего 16 и четвертого 17 дополнительных выходных транзисторов соединены с базой второго 12 выходного транзистора, коллекторы первого 14 и третьего 16 дополнительных выходных транзисторов соединены с первым 5 токовым выходом входного дифференциального каскада 1, коллекторы второго 15 и четвертого 17 дополнительных выходных транзисторов соединены со вторым 8 токовым выходом входного дифференциального каскада 1, причем в качестве первого 7 и второго 9 согласующих двухполюсников используются токостабилизирующие двухполюсники с высоким внутренним сопротивлением.

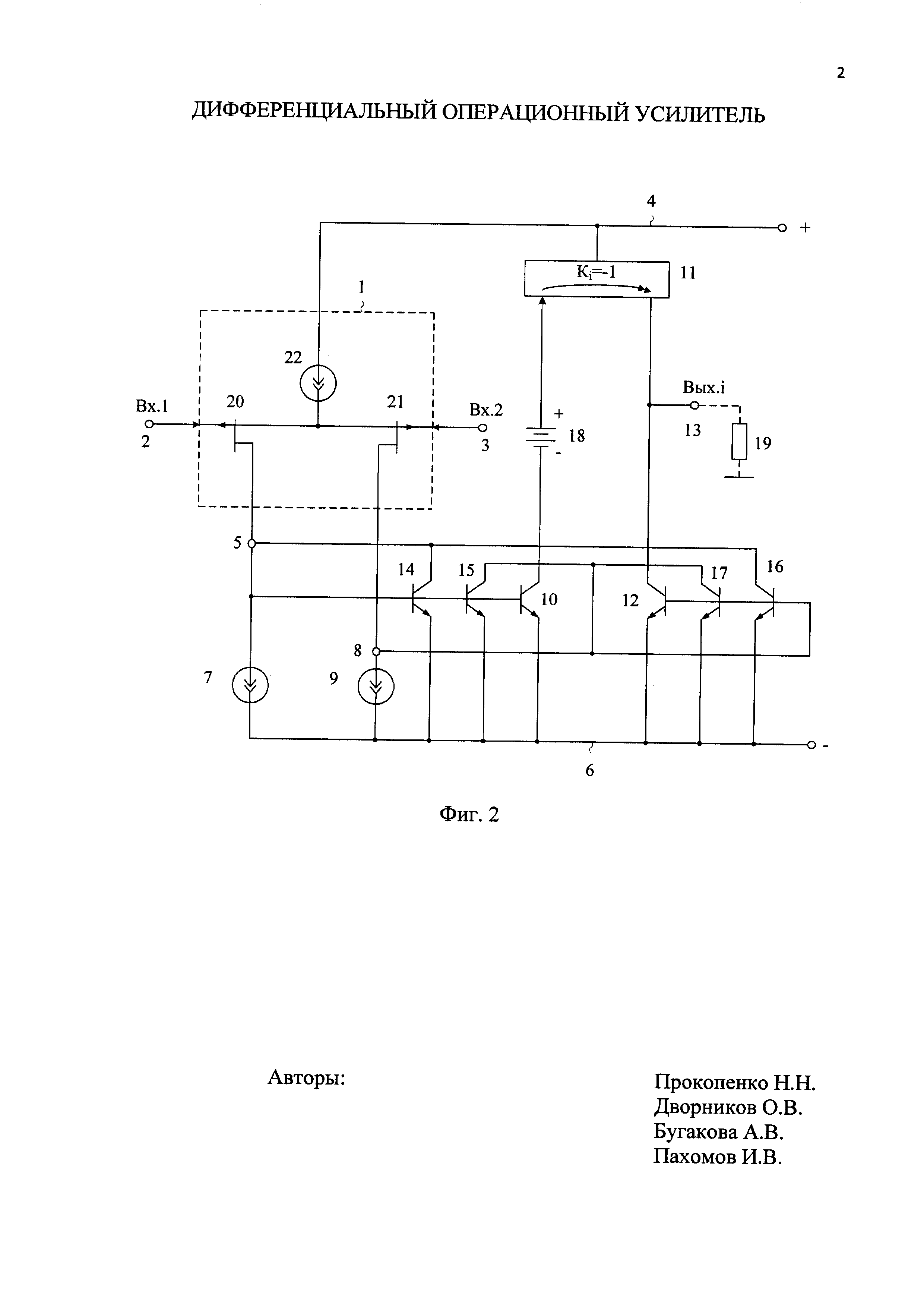

На фиг. 1 показана схема ОУ-прототипа, а на фиг. 2 - схема заявляемого устройства в соответствии с п. 1 формулы изобретения.

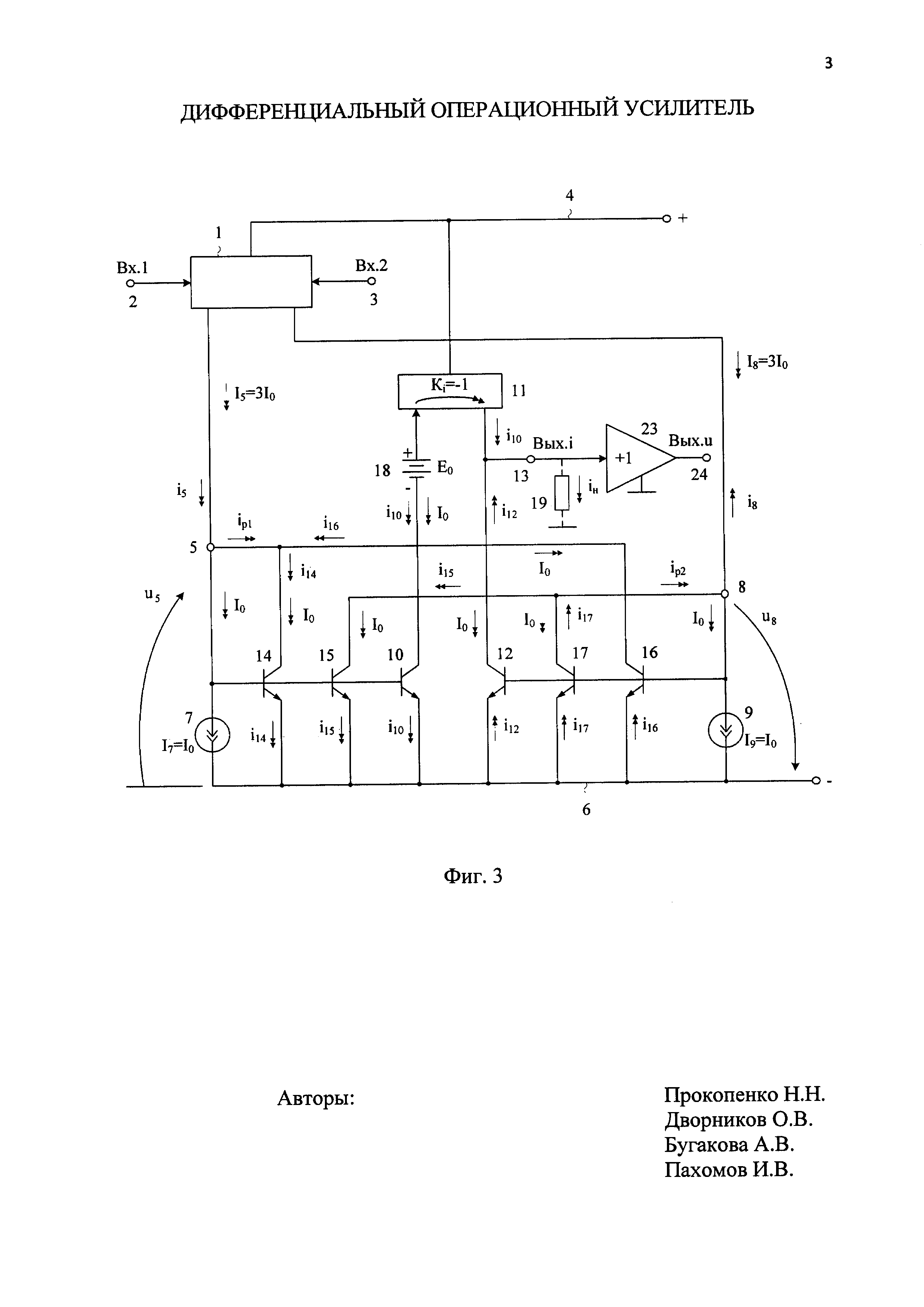

На фиг. 3 приведена схема заявляемого ОУ фиг. 2, на которой показаны приращения токов и напряжений, позволяющие количественно оценить эффект повышения его коэффициента усиления по напряжению.

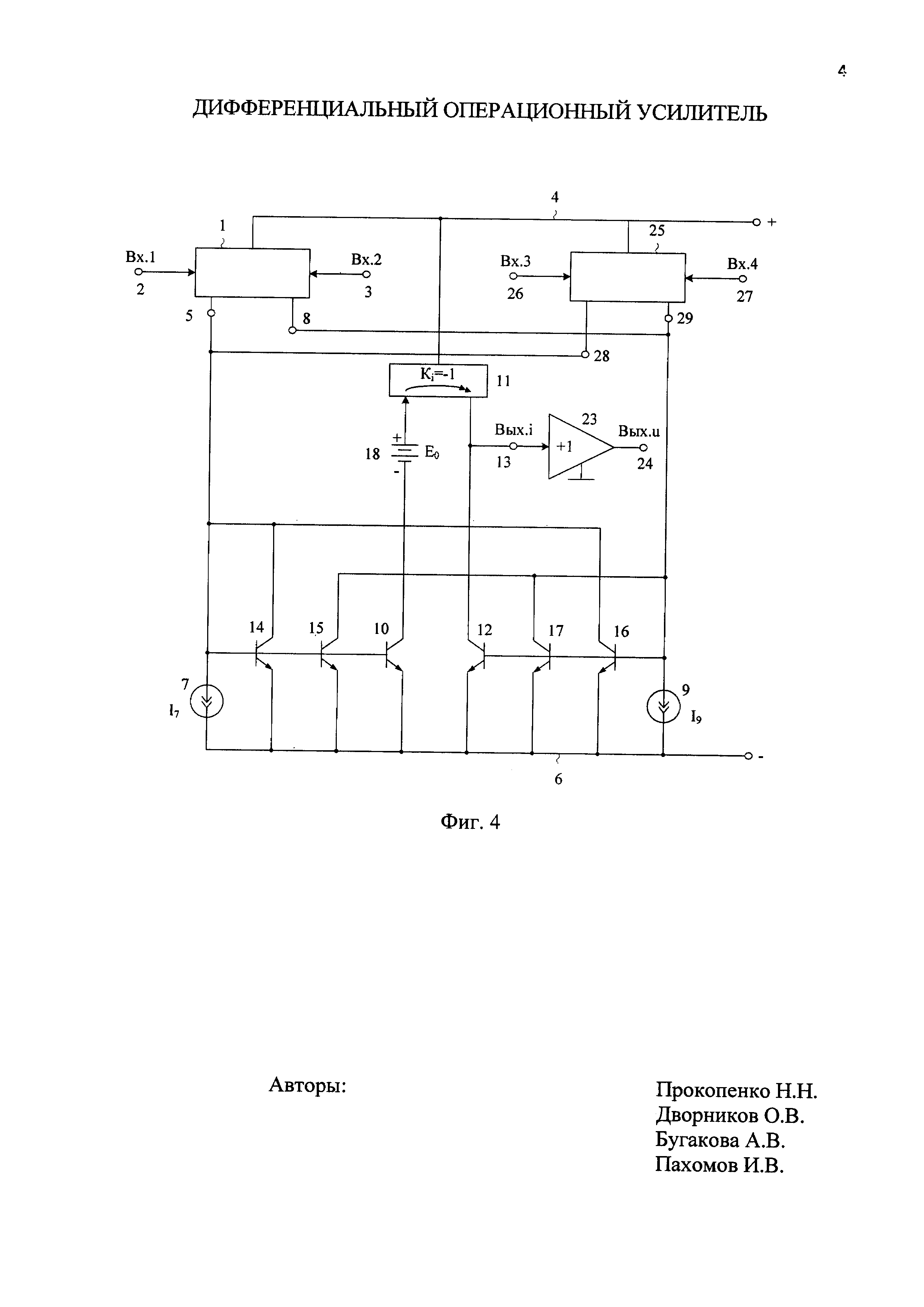

На фиг. 4 представлена схема заявляемого устройства в соответствии с п. 2 формулы изобретения.

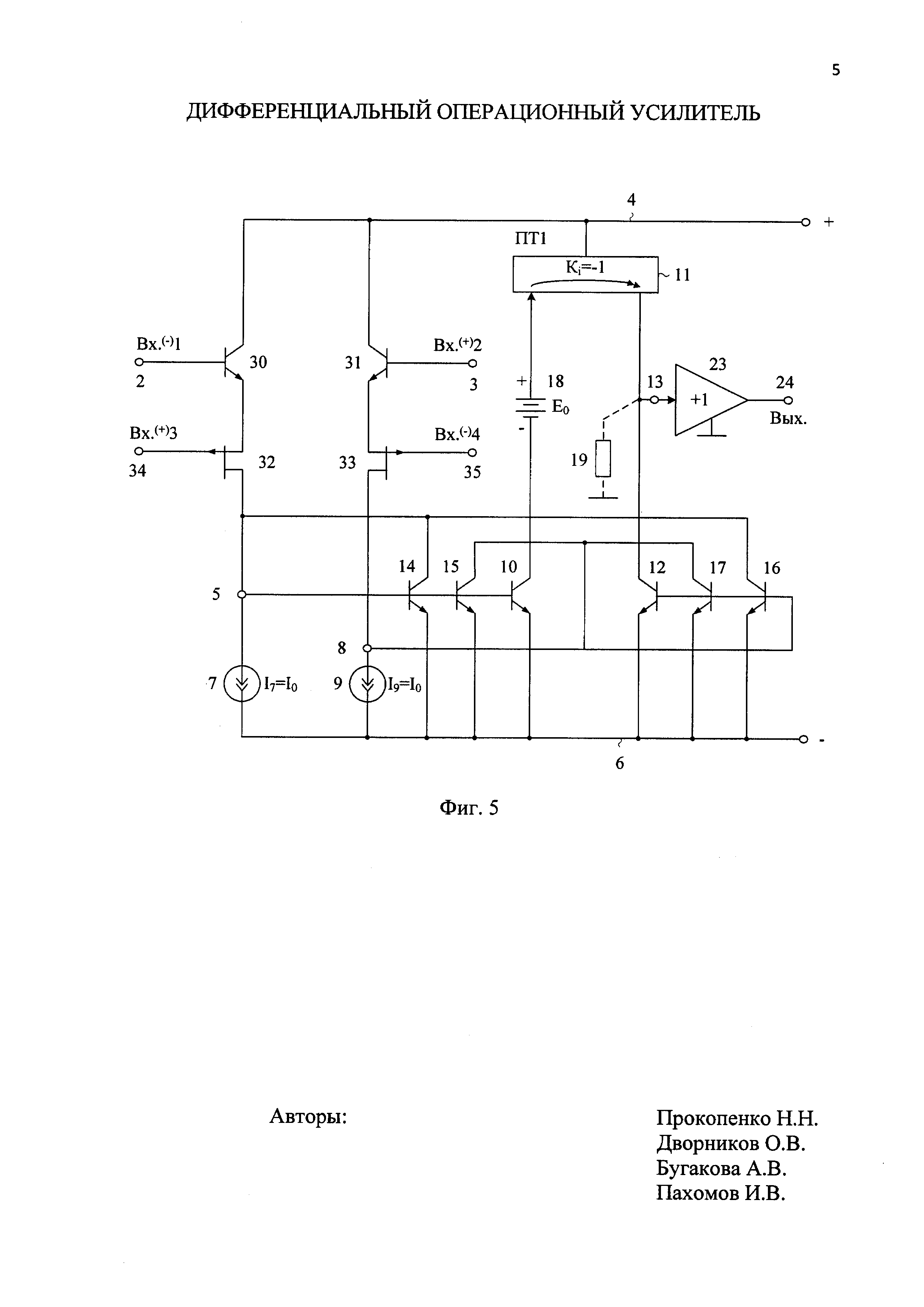

На фиг. 5 представлена схема заявляемого устройства в соответствии с п. 3 формулы изобретения.

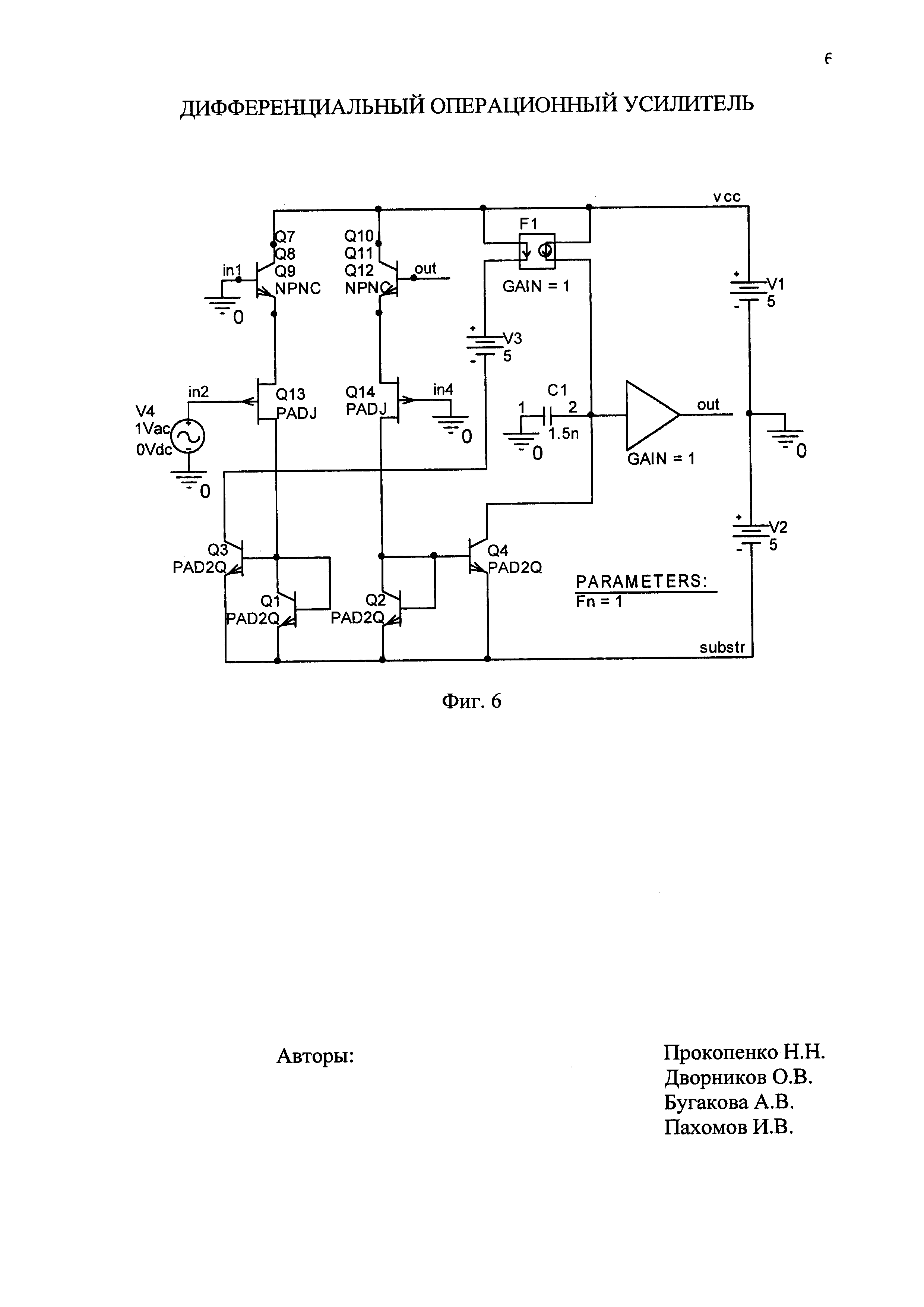

На фиг. 6 приведена схема ОУ-прототипа фиг. 1 в среде PSpice на моделях интегральных транзисторов АБМК_1_4 НПО «Интеграл» (г. Минск). В данной схеме используется такой же входной каскад, что и в ОУ фиг. 5. Это позволяет сравнить характеристики известного (фиг. 1) и заявляемого (фиг. 5) ОУ в одинаковых условиях (при идентичных входных каскадах 1).

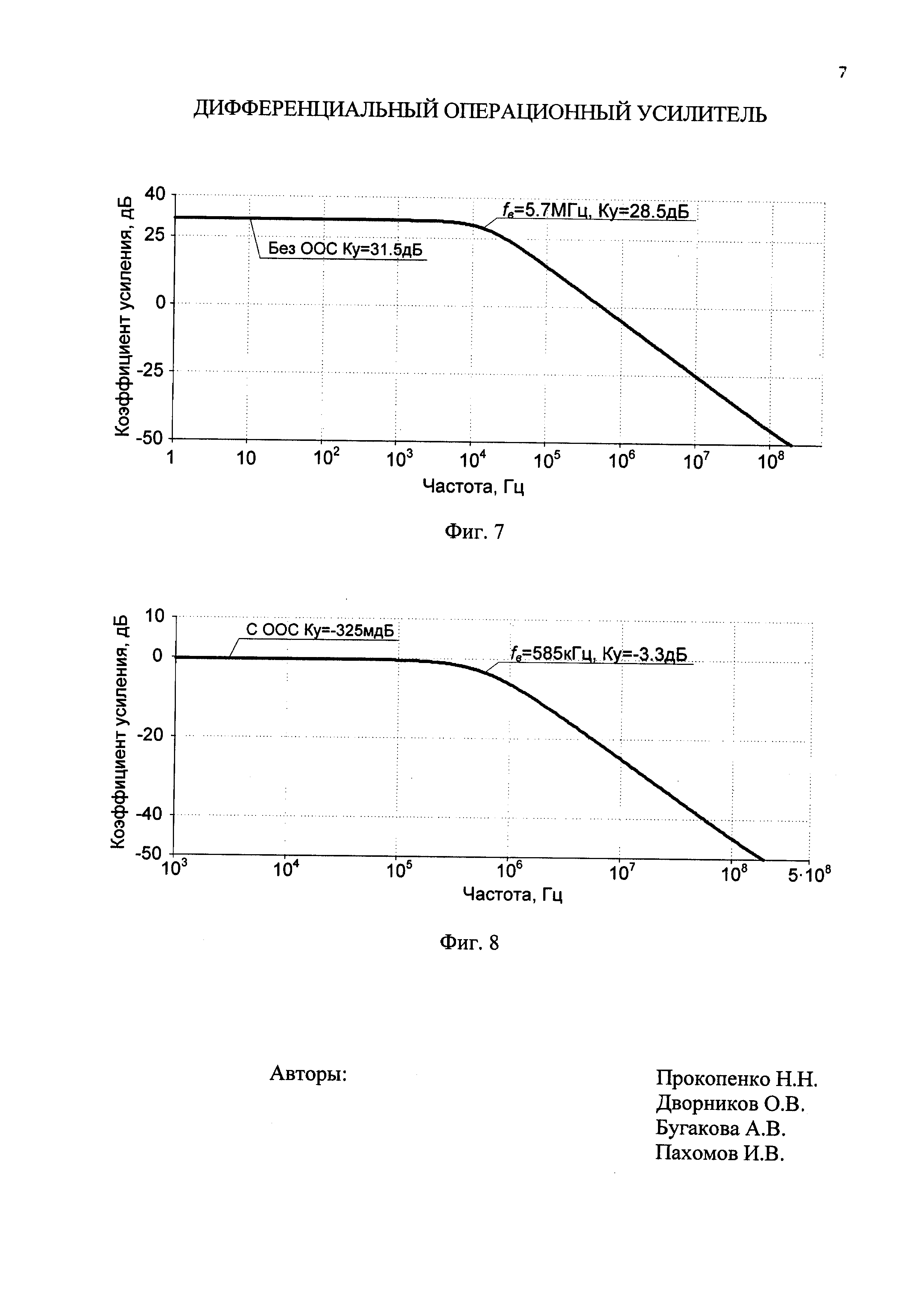

На фиг. 7 показана амплитудно-частотная характеристика дифференциального операционного усилителя-прототипа (фиг. 6) без отрицательной обратной связи (ООС).

На фиг. 8 показана амплитудно-частотная характеристика дифференциального операционного усилителя-прототипа (фиг. 6) со 100% отрицательной обратной связью.

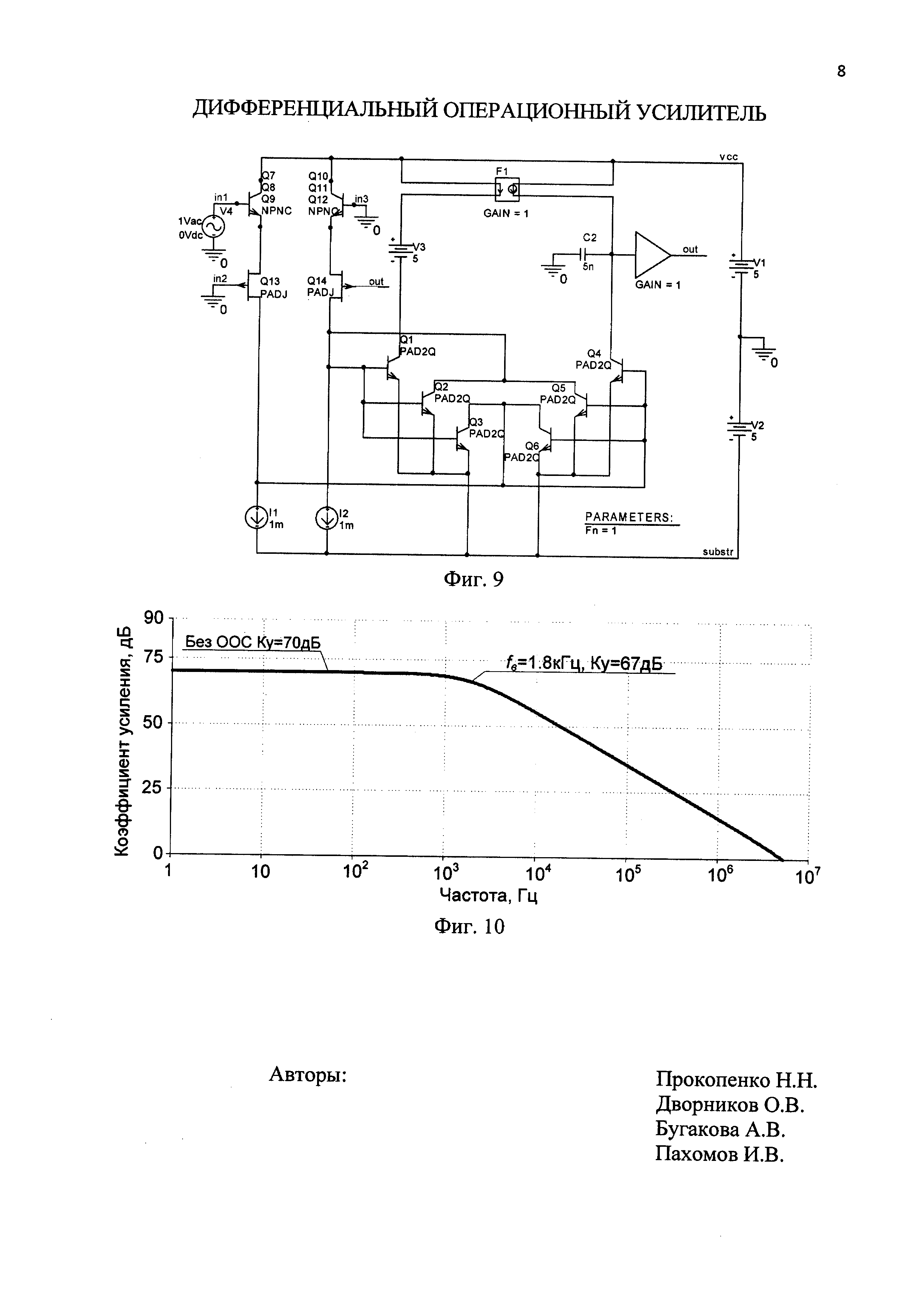

На фиг. 9 приведена схема заявляемого устройства фиг. 5 в режиме инвертирующего усилителя с коэффициентом передачи Ку=-1 в среде PSpice на моделях интегральных транзисторов АБМК_1_4 НПО «Интеграл» (г. Минск), которая использовалась для моделирования его амплитудно-частотных характеристик.

На фиг. 10 показана амплитудно-частотная характеристика дифференциального операционного усилителя фиг. 9 без отрицательной обратной связи.

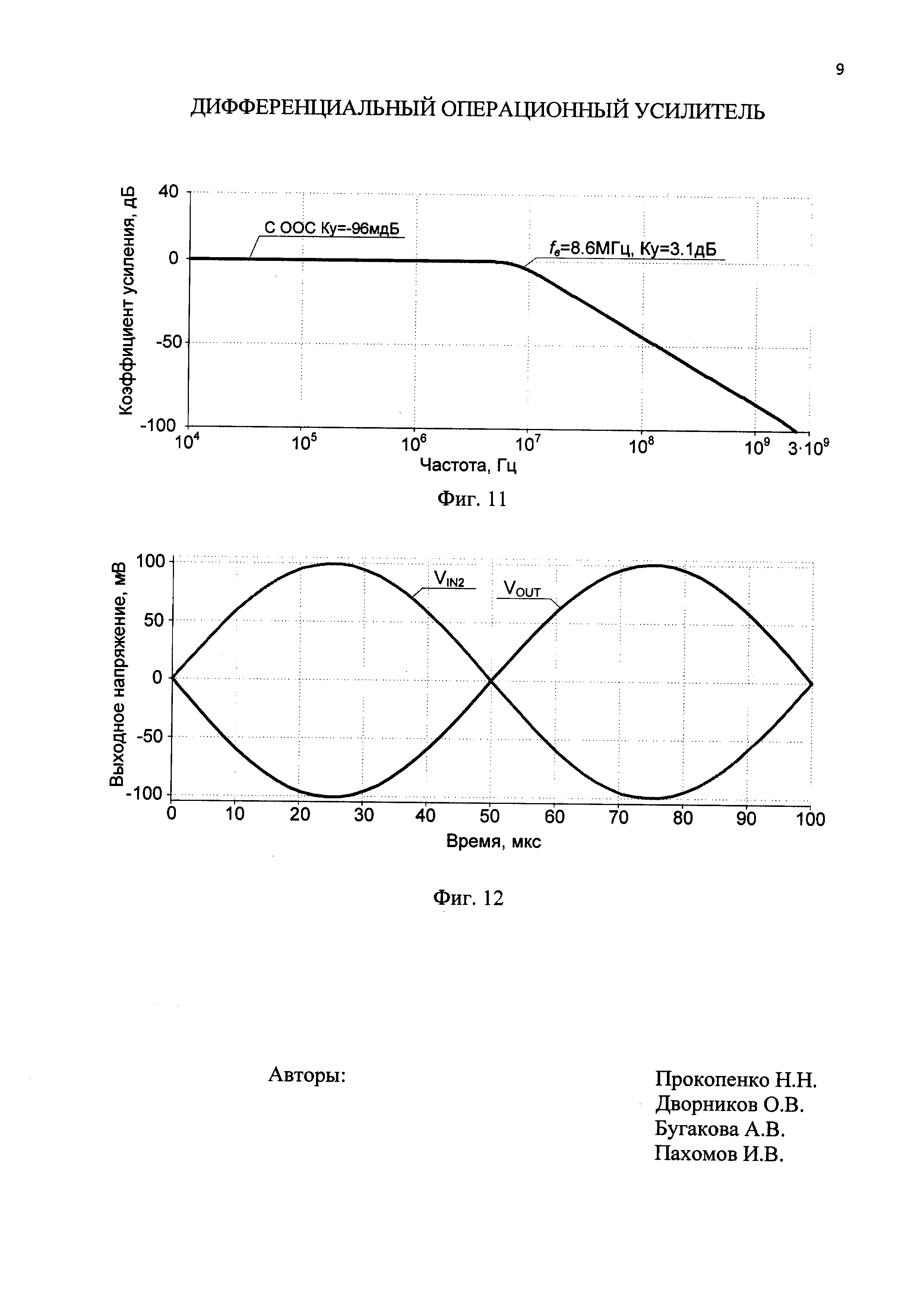

На фиг. 11 показана амплитудно-частотная характеристика дифференциального операционного усилителя фиг. 9 со 100% отрицательной обратной связью. Из анализа фазовых соотношений в схеме фиг. 9 следует, что коэффициент усиления по напряжению ОУ фиг. 9 равен минус единице, что в принципе не реализуется на основе схемы ОУ-прототипа с типовыми входными каскадами.

На фиг. 12 приведены временные характеристики входного и выходного синусоидального напряжения схемы фиг. 9, которые показывают, что выходное напряжение заявляемого устройства в данной схеме включено противофазно его входному напряжению.

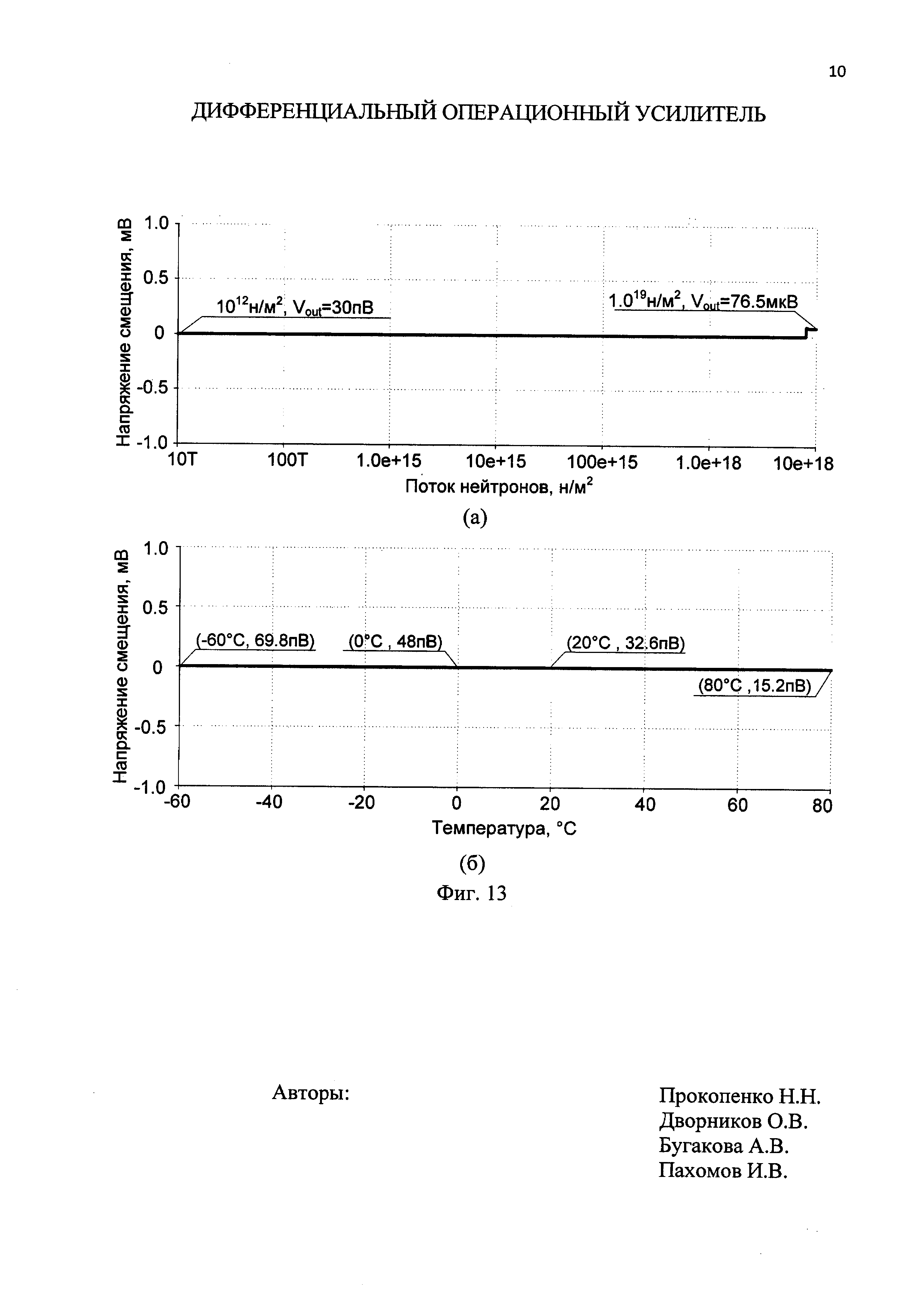

На фиг. 13 приведена зависимость напряжения смещения нуля ОУ фиг. 9 от потока нейтронов (а) и температуры в диапазоне минус 60-80°C (б). Данные характеристики получены для случая, когда элементы схемы обладают высокой идентичностью, т.е. данные графики показывают предельные возможности заявляемого ОУ.

Дифференциальный операционный усилитель фиг. 2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 основными входами, согласованный с первой 4 шиной источника питания, первый 5 токовый выход входного дифференциального каскада 1, связанный со второй 6 шиной источника питания через первый 7 согласующий двухполюсник, второй 8 токовый выход входного дифференциального каскада 1, связанный со второй 6 шиной источника питания через второй 9 согласующий двухполюсник, первый 10 выходной транзистор, база которого соединена с первым 5 токовым выходом входного дифференциального каскада 1, эмиттер подключен ко второй 6 шине источника питания, а коллектор связан со входом токового зеркала 11, согласованного с первой 4 шиной источника питания, второй 12 выходной транзистор, эмиттер которого подключен ко второй 6 шине источника питания, база соединена со вторым 8 токовым выходом входного дифференциального каскада 1, а коллектор связан с токовым выходом токового зеркала 11 и соединен с токовым выходом устройства 13. В схему введены первый 14, второй 15, третий 16 и четвертый 17 дополнительные выходные транзисторы, эмиттеры которых подключены ко второй 6 шине источника питания, базы первого 14 и второго 15 дополнительных выходных транзисторов соединены с базой первого 10 выходного транзистора, базы третьего 16 и четвертого 17 дополнительных выходных транзисторов соединены с базой второго 12 выходного транзистора, коллекторы первого 14 и третьего 16 дополнительных выходных транзисторов соединены с первым 5 токовым выходом входного дифференциального каскада 1, коллекторы второго 15 и четвертого 17 дополнительных выходных транзисторов соединены со вторым 8 токовым выходом входного дифференциального каскада 1, причем в качестве первого 7 и второго 9 согласующих двухполюсников используются токостабилизирующие двухполюсники с высоким внутренним сопротивлением на переменном токе, например классические источники опорного тока, высокоомные резисторы, индуктивности и т.п.

Для уменьшения влияния напряжения Эрли первого 10 и второго 12 выходных транзисторов на напряжение смещения нуля ОУ фиг. 2 предусмотрена цепь смещения 18, которая может быть выполнена в виде стабилитрона, резистора или нескольких прямосмещенных р-n переходов.

На фиг. 2 эквивалентное входное сопротивление токового выхода 13 моделируется резистором нагрузки 19. При этом входной дифференциальный каскад 1 выполнен (в частном случае) на полевых транзисторах 20 и 21 и источнике опорного тока 22.

В схеме фиг. 3 предусмотрен буферный усилитель 23, который обеспечивает потенциальный выход устройства 24 и его низкое выходное сопротивление.

На фиг. 4, в соответствии с п. 2 формулы изобретения, введен дополнительный входной дифференциальный каскад 25, согласованный с первой 4 шиной источника питания, имеющий первый 26 и второй 27 дополнительные входы, причем первый 28 токовый выход дополнительного входного дифференциального каскада 25 связан с первым 5 токовым выходом входного дифференциального каскада 1, а второй 29 токовый выход дополнительного входного дифференциального каскада 25 связан со вторым 8 токовым выходом входного дифференциального каскада 1.

На фиг. 5, в соответствии с п. 3 формулы изобретения, входной дифференциальный каскад 1 выполнен на основе первого 30 и второго 31 биполярных транзисторов, а также первого 32 и второго 33 полевых транзисторов с управляющим р-n переходом, причем коллекторы первого 30 и второго 31 биполярных транзисторов связаны с первой 4 шиной источника питания, база первого 30 биполярного транзистора соединена с первым 2 основным входом входного дифференциального каскада 1, база второго 31 биполярного транзистора соединена со вторым 3 основным входом входного дифференциального каскада 1, эмиттер первого 30 биполярного транзистора соединен с истоком первого 32 полевого транзистора с управляющим p-n переходом, эмиттер второго 31 биполярного транзистора соединен с истоком второго 33 полевого транзистора с управляющим р-n переходом, сток первого 32 полевого транзистора с управляющим р-n переходом связан с первым 5 токовым выходом входного дифференциального каскада 1, сток второго 33 полевого транзистора с управляющим р-n переходом соединен со вторым 8 токовым выходом входного дифференциального каскада 1, затвор первого 32 полевого транзистора с управляющим р-n переходом связан с первым 34 дополнительным входом входного дифференциального каскада 1, затвор второго 33 полевого транзистора с управляющим р-n переходом связан со вторым 35 дополнительным входом входного дифференциального каскада 1.

Сравним работу ОУ фиг. 1 и фиг. 3.

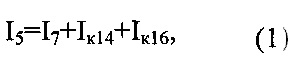

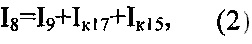

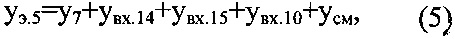

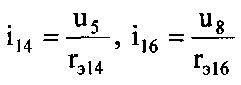

Статический режим по току транзисторов ОУ фиг. 3 определяется следующими уравнениями Кирхгофа:

где Iк14=Iк16=Iк17=Iк15=Iк10=Iк12 - коллекторные токи соответствующих транзисторов (14, 16, 17, 15, 10, 12);

I7=I9 - токи первого 7 и второго 9 согласующих двухполюсников с высоким внутренним сопротивлением;

I5=I8 - токи первого 5 и второго 8 выходов входного дифференциального каскада 1.

Если выбрать I7=I9=I0, то при I5=I8=3I0 коллекторные токи всех транзисторов схемы будет равны некоторому опорному току I0, например I0=1 мА. При других значениях I5=I8 статические коллекторные токи определяются уравнениями (1) и (2).

Таким образом, в заявляемой схеме, так же как и в ОУ-прототипе, обеспечивается высокая стабильность статического режима транзисторов промежуточного каскада, которая определяется опорным током I0.

Рассмотрим далее динамические параметры сравниваемых ОУ.

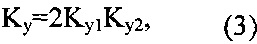

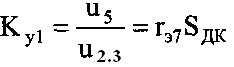

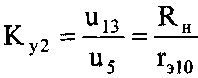

Коэффициент усиления по напряжению ОУ-прототипа фиг. 1 при усилении по току токового зеркала 11, равном единице (Ki=1), определяется формулой

где

u13 - напряжение в цепи токового выхода 13;

rэ7 - дифференциальное сопротивление первого 7 согласующего двухполюсника;

rэ10 - дифференциальное сопротивление эмиттерного перехода первого 10 выходного транзистора;

SДК - крутизна преобразования входного напряжения ОУ (u2.3) в выходной ток токовых выходов 5 и 8;

Rн=R19 - эквивалентное сопротивление нагрузки в цепи токового выхода 13.

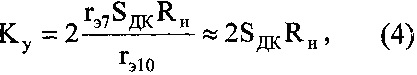

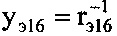

Таким образом, в ОУ-прототипе фиг. 1:

где rэ7≈rэ10.

Следует заметить, что в схеме фиг. 1 увеличение rэ7 за счет применения источников опорного тока в качестве согласующего двухполюсника 7 (9) приведет к резкому повышению нестабильности коллекторных токов транзистора 10 (12), нарушит работоспособность схемы.

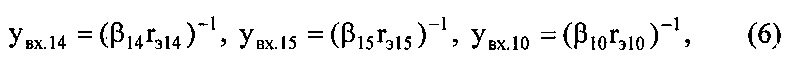

В заявляемом ОУ фиг. 3 эквивалентная проводимость в цепи токового выхода 5 определяется суммой из нескольких составляющих:

где усм - проводимость участка цепи между токовым выходом 5 и коллекторами транзисторов 14 и 16;

y7 - проводимость первого 7 согласующего двухполюсника;

yвx.i - входные проводимости транзисторов 14, 15, 10 по цепи базы.

Причем

βi - коэффициент усиления по току базы i-го транзистора.

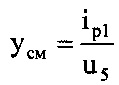

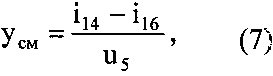

В формуле (5)

где

rэi - сопротивление эмиттерного перехода i-го транзистора.

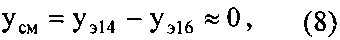

Таким образом, при высокой симметрии схемы, когда u5=u8, можно найти, что

где

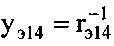

Поэтому при y7≈0 коэффициент усиления по напряжению предлагаемого ОУ

где β=β14=β15=β10>>1.

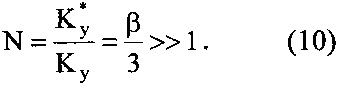

Сравнение формул (4) и (9) показывает, что предлагаемый ОУ имеет в N-раз более высокий коэффициент усиления по напряжению, где

Данный теоретический вывод подтверждается результатами компьютерного моделирования (фиг. 7, фиг. 10), из которых следует, что предлагаемая схема ОУ имеет в 100 раз более высокое усиление по напряжению без введения дополнительных каскадов.

При 100% отрицательной обратной связи схема фиг. 9 является инвертирующим повторителем входного напряжения с Kу≈-1 (фиг. 12). Следует заметить, что на базе известного ОУ-прототипа такой режим (без резисторов отрицательной обратной связи) не реализуется.

Предлагаемые схемотехнические решения имеют малые значения систематической составляющей напряжения смещения нуля при температурных и радиационных воздействиях (фиг. 13), что свидетельствует о высокой стабильности статического режима транзисторов.

Таким образом, предлагаемое устройство имеет существенные преимущества в сравнении с известными и может найти широкое применение в системах обработки радиотехнических сигналов.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 5.371.476, fig. 1

2. Патент US 4.348.602, fig. 2

3. Патент US 6.657.465

4. Патент US 7.786.799, fig. 3

5. Патент Японии JP 61-140210, fig. 1

6. Патент US 7.411.451, fig. 2

7. Патент US 4.607.232

8. Справочник: операционные усилители и компараторы (Авербух В.Д. и др.). - М.: Изд-во «Додэка-ХХI», 2001, С. 106 (микросхема СА3078).

9. Микросхема LM13600

http://www.komponenten.es.aau.dk/fileadmin/komponenten/Data_Sheet/Linear/LM13600.pdf

10. Микросхема LM13700 http://pdfl.alldatasheet.com/datasheet-pdf/view/549473/TI1/LM13700MX.html

11. Микросхема NF5517 http://pdfl.alldatasheet.com/datasheet-pdf/view/175236/ONSEMI/NE5517.html

Реферат

Изобретение относится к области радиоэлектроники. Технический результат: повышение коэффициента усиления по напряжению в разомкнутом дифференциальном операционном усилителе при высокой температурной и радиационной стабильности статического режима транзисторов его промежуточного каскада. В схему введены первый (14), второй (15), третий (16) и четвертый (17) дополнительные выходные транзисторы, эмиттеры которых подключены ко второй 6 шине источника питания, базы первого (14) и второго (15) дополнительных выходных транзисторов соединены с базой первого (10) выходного транзистора, базы третьего (16) и четвертого (17) дополнительных выходных транзисторов соединены с базой второго (12) выходного транзистора, коллекторы первого (14) и третьего (16) дополнительных выходных транзисторов соединены с первым (5) токовым выходом входного дифференциального каскада (1), коллекторы второго (15) и четвертого (17) дополнительных выходных транзисторов соединены со вторым (8) токовым выходом входного дифференциального каскада (1), причем в качестве первого (7) и второго (9) согласующих двухполюсников используются токостабилизирующие двухполюсники с высоким внутренним сопротивлением. 2. з.п. ф-лы, 13 ил.

Комментарии