Устройство селекции двоичных чисел - RU2675301C1

Код документа: RU2675301C1

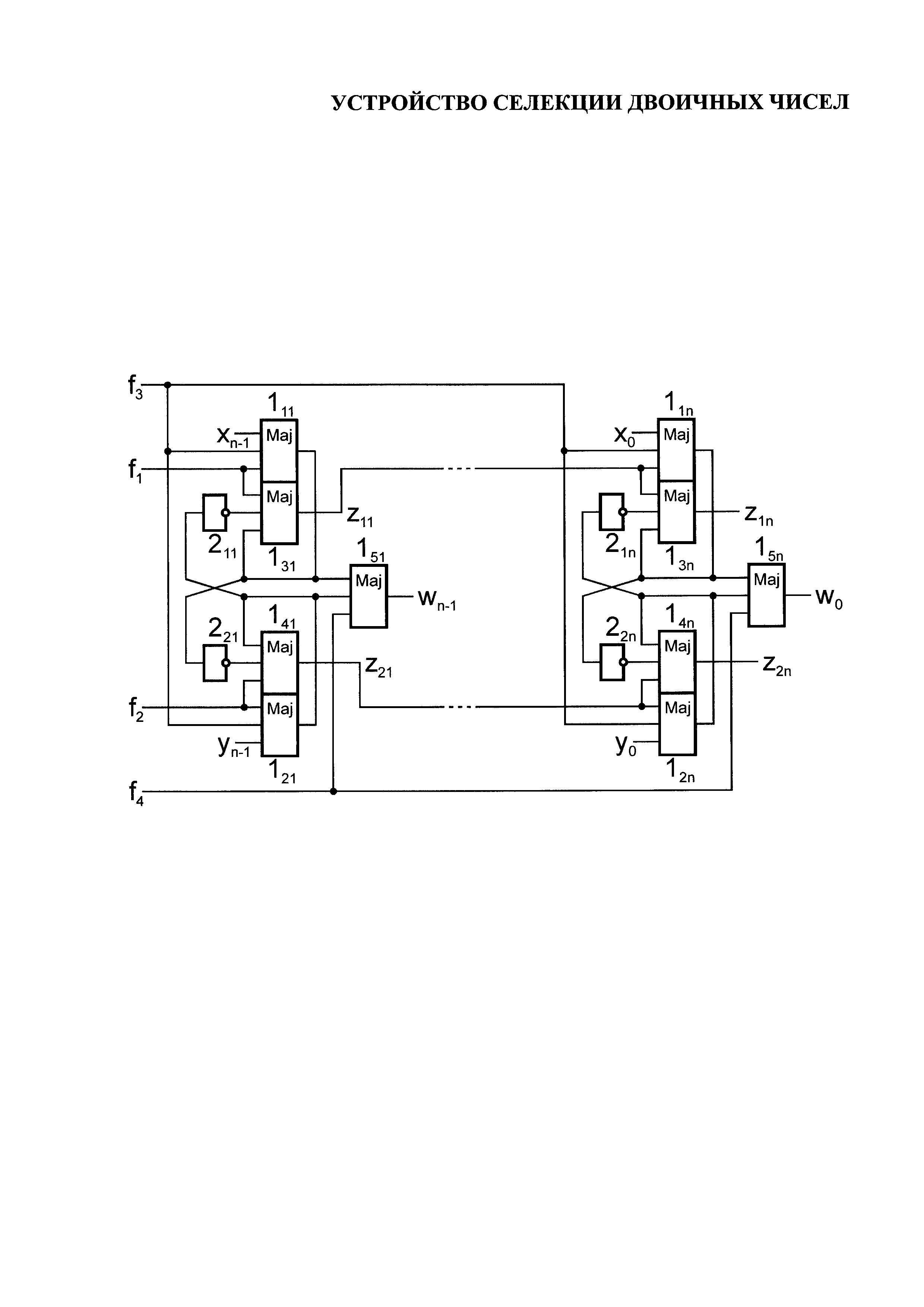

Чертежи

Описание

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны устройства селекции двоичных чисел (см., например, патент РФ 2300135, кл. G06F 7/02, 2007 г.), выполняющие селекцию большего из двух n-разрядных двоичных чисел, задаваемых двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных устройств селекции двоичных чисел, относятся ограниченные функциональные возможности, обусловленные тем, что не выполняется идентификация большего, либо селекция и идентификация меньшего, либо селекция произвольно назначенного из двух n-разрядных двоичных чисел, задаваемых двоичными сигналами.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятое за прототип устройство селекции двоичных чисел (патент РФ 2363038, кл. G06F 7/02, 2009 г.), которое содержит мажоритарные элементы, 2×n элементов НЕ и выполняет селекцию и идентификацию меньшего, либо селекцию и идентификацию большего, либо селекцию произвольно назначенного из двух n-разрядных двоичных чисел, задаваемых двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся большие аппаратурные затраты, обусловленные тем, что прототип содержит 7×n мажоритарных элементов.

Техническим результатом изобретения является уменьшение аппаратурных затрат при сохранении функциональных возможностей прототипа.

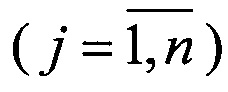

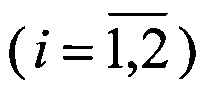

Указанный технический результат при осуществлении изобретения достигается тем, что в устройстве селекции двоичных чисел, содержащем n групп элементов, каждая из которых содержит пять мажоритарных элементов и два элемента НЕ, причем в j-й (

На чертеже представлена схема предлагаемого устройства селекции двоичных чисел.

Устройство селекции двоичных чисел содержит мажоритарные элементы 111, …, 15n и элементы НЕ 211, …, 22n, которые сгруппированы в n групп так, что j-я (

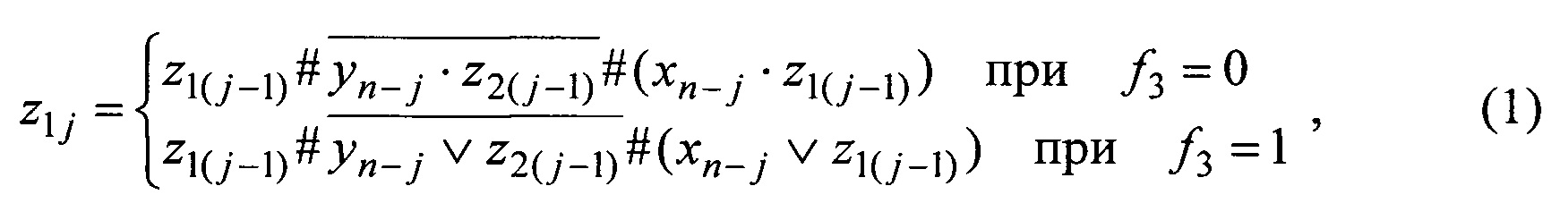

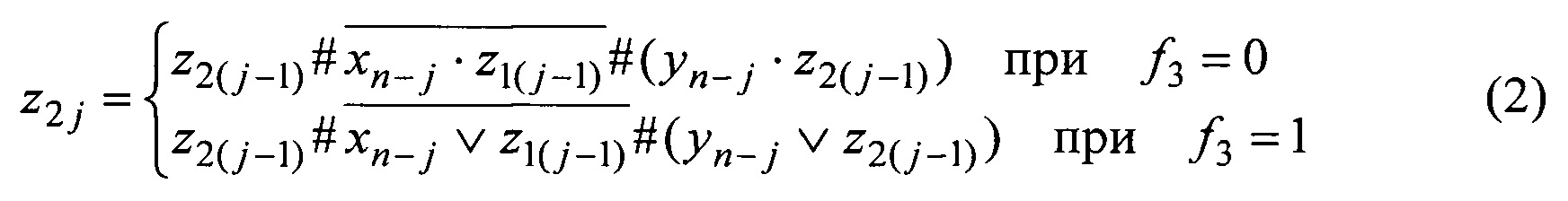

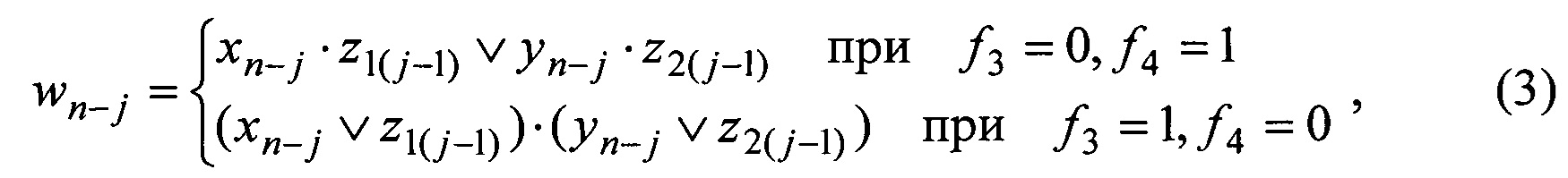

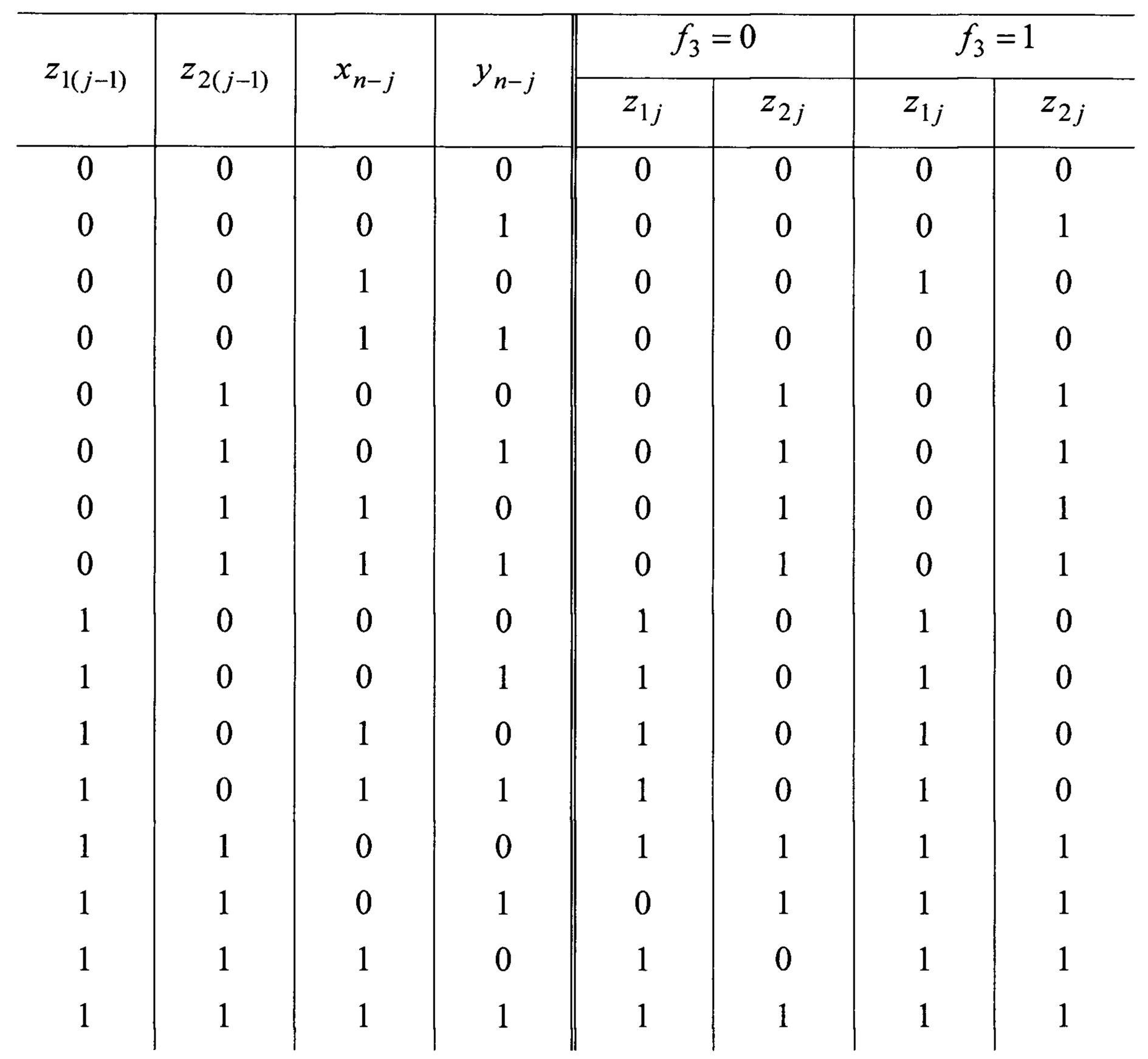

Работа предлагаемого устройства селекции двоичных чисел осуществляется следующим образом. На его первом, …, четвертом настроечных входах фиксируются соответственно необходимые двоичные сигналы ƒ1, …, ƒ4 ∈ {0,1}. На его первый, …, n-й и (n+1)-й, …, (n+n)-й входы подаются соответственно двоичные сигналы xn-1, …, x0 ∈ {0,1} и yn-1, …, y0 ∈ {0,1}, которые задают подлежащие обработке n-разрядные двоичные числа xn-1…x0 и yn-1…y0 (xn-1, yn-1 и х0, y0 определяют значения старших и младших разрядов соответственно). Сигнал на выходе мажоритарного элемента равен 1 (0) только тогда, когда на двух или на трех входах этого элемента действуют сигналы, равные 1 (0). Следовательно, если на одном из трех входов мажоритарного элемента фиксируется 1 (0), то этот элемент будет выполнять операцию ИЛИ (И) над сигналами, действующими на двух других его входах. На основании изложенного сигналы на выходах элементов 13j, 14j (

и

где ∨,

Анализ данных, приведенных в таблице, позволяет заключить, что при ƒ3=0: 1) z1j=0 (z2j=0) когда z1(j-1)=0 (z2(j-1)=0) или z1(j-1)=z2(j-1)=1 и xn-j

и

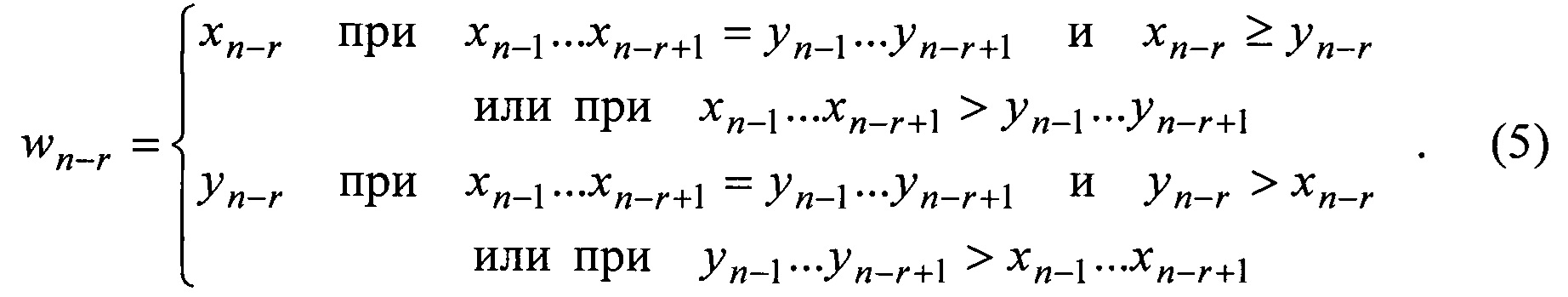

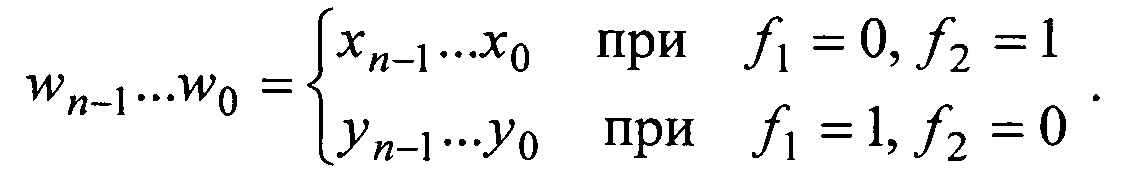

Здесь и далее xn-1…xn-r+1 и yn-1…yn-r+1 - фрагменты n-разрядных двоичных чисел xn-1…х0 и yn-1…y0. Согласно (4), (5) предлагаемое устройство реализует операцию wn-1…w0=max(xn-1…x0, yn-1…y0) селекции большего из чисел xn-1…х0, yn-1…y0. При этом z1n=1 (z2n=1) когда xn-1…х0=max(xn-1…х0, yn-1…y0) (yn-1…y0=max(xn-1…xQ, yn-1…y0)), то есть предлагаемое устройство одновременно с селекцией выполняет идентификацию селектируемого числа. Если ƒ3=0, ƒ4=1 и ƒ1≠ƒ2, то согласно (3) и данных таблицы предлагаемое устройство воспроизводит операцию

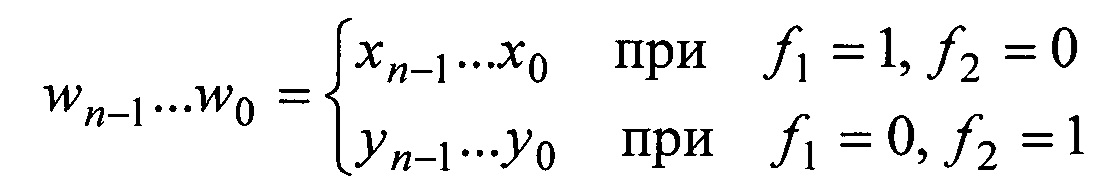

селекции числа, назначенного сигналами ƒ1, ƒ2 (операцию мультиплексирования). Отметим, что wn-1…w0 - n-разрядное двоичное число, задаваемое двоичными сигналами w0, …, wn-1 ∈ {0,1} (wn-1 и w0 определяют значения старшего и младшего разрядов соответственно). При ƒ1=ƒ2=ƒ4=0, ƒ3=1 с учетом (3) имеем

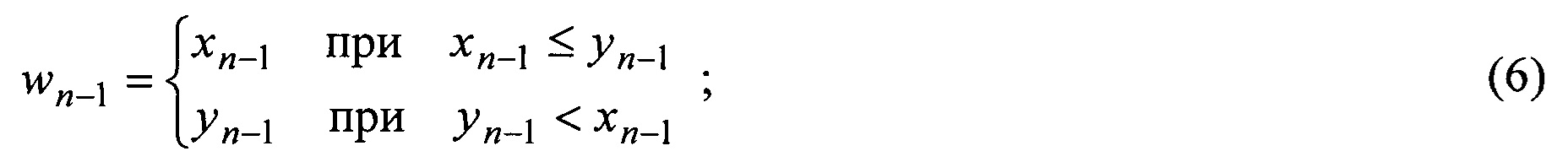

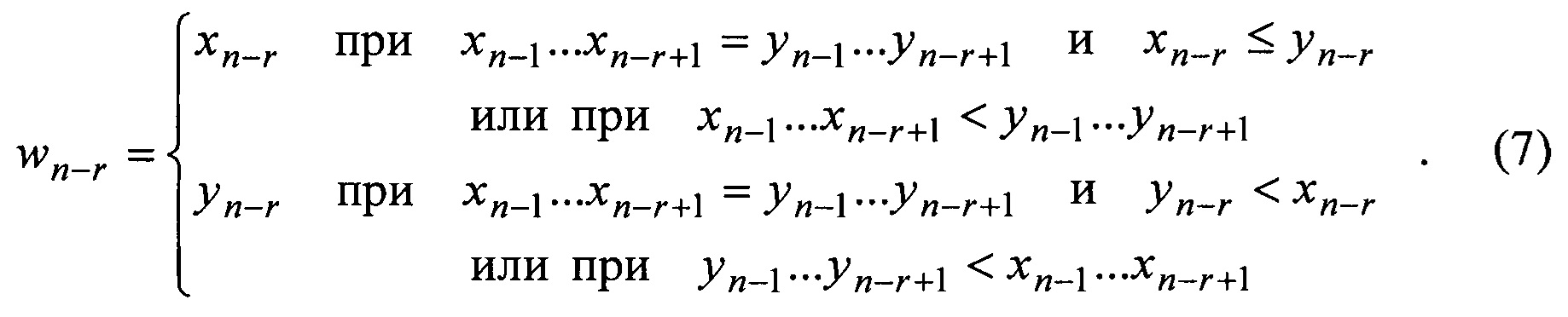

Согласно (6), (7) предлагаемое устройство реализует операцию wn-1…w0=min(xn-1…х0, yn-1…y0) селекции меньшего из чисел xn-1…x0, yn-1…y0. При этом выполняется идентификация селектируемого числа, поскольку z1n=0 (z2n=0) когда xn-1…x0=min(xn-1…x0, yn-1…y0) (yn-1…y0=min(xn-1…x0, yn-1…y0)). Если ƒ3=1, ƒ4=0 и ƒ1≠ƒ2, то согласно (3) и данных таблицы предлагаемое устройство воспроизводит следующую операцию мультиплексирования:

Отметим, что указанное устройство содержит 5×n мажоритарных элементов и 2×n элементов НЕ.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство выполняет селекцию и идентификацию меньшего, либо селекцию и идентификацию большего, либо селекцию произвольно назначенного из двух n-разрядных двоичных чисел, задаваемых двоичными сигналами, и обладает меньшими по сравнению с прототипом аппаратурными затратами.

Реферат

Изобретение относится к области вычислительной техники и может быть использовано для выполнения селекции и идентификации меньшего, либо селекции и идентификации большего, либо селекции произвольно назначенного из двух n-разрядных двоичных чисел, задаваемых двоичными сигналами. Техническим результатом является уменьшение аппаратурных затрат. Устройство содержит 5×n мажоритарных элементов и 2×n элементов НЕ. 1 ил., 1 табл.

Формула

Документы, цитированные в отчёте о поиске

Устройство селекции экстремального числа из двух двоичных чисел

Комментарии