Вычислитель для режектирования помех - RU2628904C1

Код документа: RU2628904C1

Чертежи

Описание

Изобретение относится к вычислительной технике и может быть использовано в когерентно-импульсных радиолокационных системах для выделения сигналов движущихся целей на фоне пассивных помех при групповой перестройке несущей частоты зондирующих импульсов.

Известно радиолокационное устройство для обнаружения движущейся цели [1], содержащее последовательно включенные блоки задержки, умножитель комплексных чисел и вычитатель. Однако это устройство обладает низкой эффективностью выделения сигнала движущейся цели.

Другим известным устройством является корреляционный автокомпенсатор [2], который содержит ряд блоков задержки, два перемножителя, сумматор и блок оценки параметров коррелированной помехи. Недостатком этого устройства является плохое подавление кромок протяженной помехи из-за большой постоянной времени цепи адаптивной обратной связи.

Наиболее близкое к данному изобретению цифровое устройство для подавления пассивных помех [3], выбранное в качестве прототипа, содержит два блока задержки, блок весовых коэффициентов, два комплексных перемножителя, весовой блок и комплексный сумматор. Однако данное устройство из-за переходного процесса при поступлении кромки пассивной помехи имеет низкую эффективность выделения сигналов движущихся целей.

Задачей, решаемой в изобретении, является повышение эффективности режектирования пассивной помехи и выделения сигналов движущихся целей при обработке группы импульсов на фоне пассивных помех с априорно неизвестной доплеровской скоростью.

Для решения этой задачи в вычислитель для режектирования помех, содержащий первый и второй блоки задержки, блок весовых коэффициентов, первый и второй комплексные перемножители, весовой блок и комплексный сумматор, введены блок комплексного сопряжения, блок переключения, блок точности, блок коммутации, двухканальный коммутатор и синхрогенератор.

Дополнительные блоки, введенные в предлагаемое устройство, являются известными. Так, соединенные вместе первый блок задержки, первый комплексный перемножитель, весовой блок и комплексный сумматор применяются для режектирования пассивных помех, однако неизвестно их применение совместно с блоком коммутации и двухканальным коммутатором для более точной компенсации помехи. Новыми являются связи между блоком весовых коэффициентов и блоком переключения и весовым блоком, блоком точности и вторым комплексным перемножителем, вторым блоком задержки, двухканальным коммутатором, вторым комплексным перемножителем и блоком коммутации, а также связи между синхрогенератором и остальными блоками вычислителя для режектирования помех, обеспечивающими соответственно оптимальную и согласованную обработку группы импульсов, что приводит в сочетании с более точной компенсацией помехи к повышению эффективности выделения сигналов движущихся целей при перестройке несущей частоты на фоне пассивных помех с априорно неизвестной доплеровской скоростью.

Сравнение с техническими решениями, известными из опубликованных источников информации, показывает, что заявляемое решение обладает новизной и имеет изобретательский уровень.

Заявляемое решение носит технический характер, осуществимо, воспроизводимо и, следовательно, является промышленно применимым.

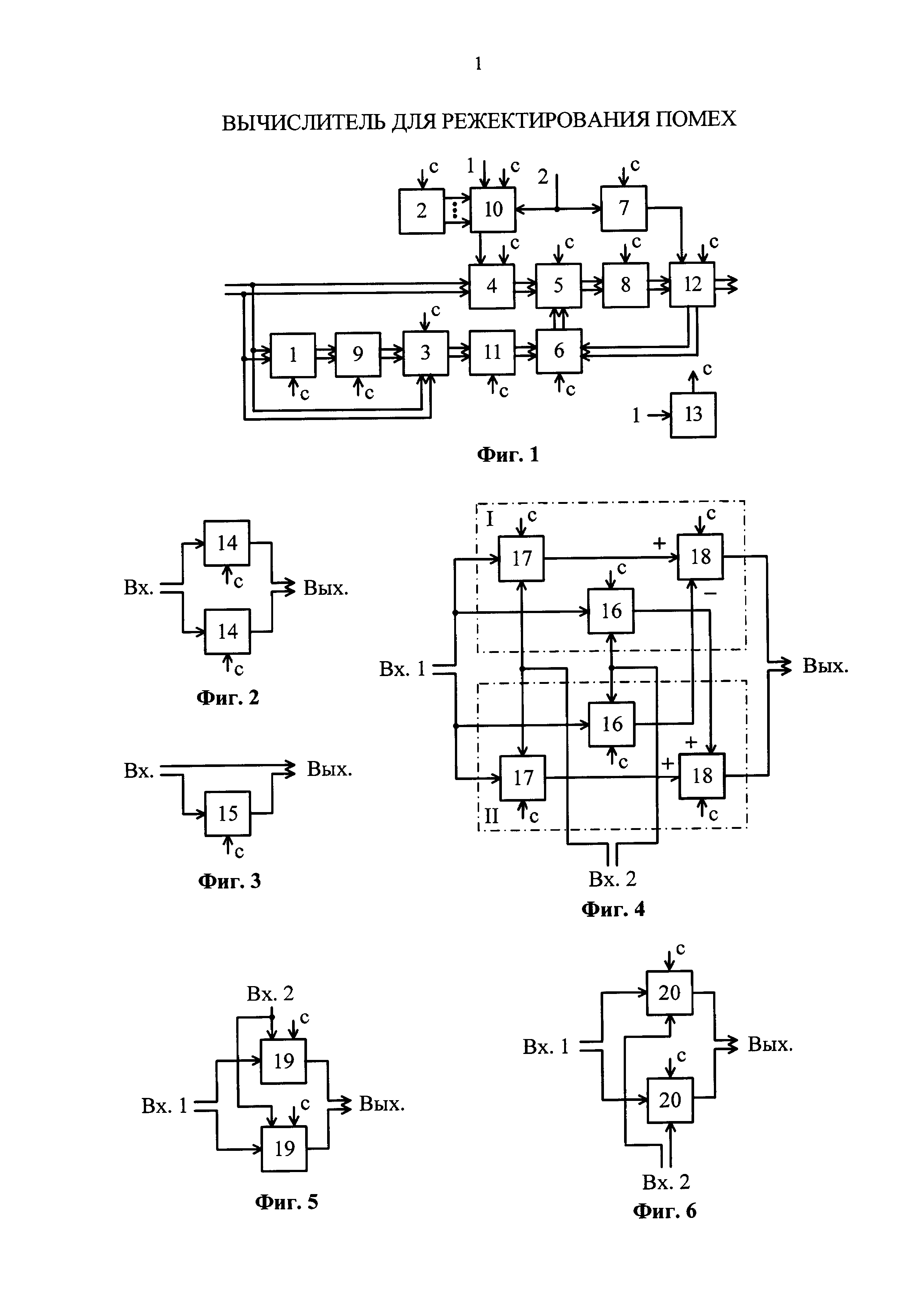

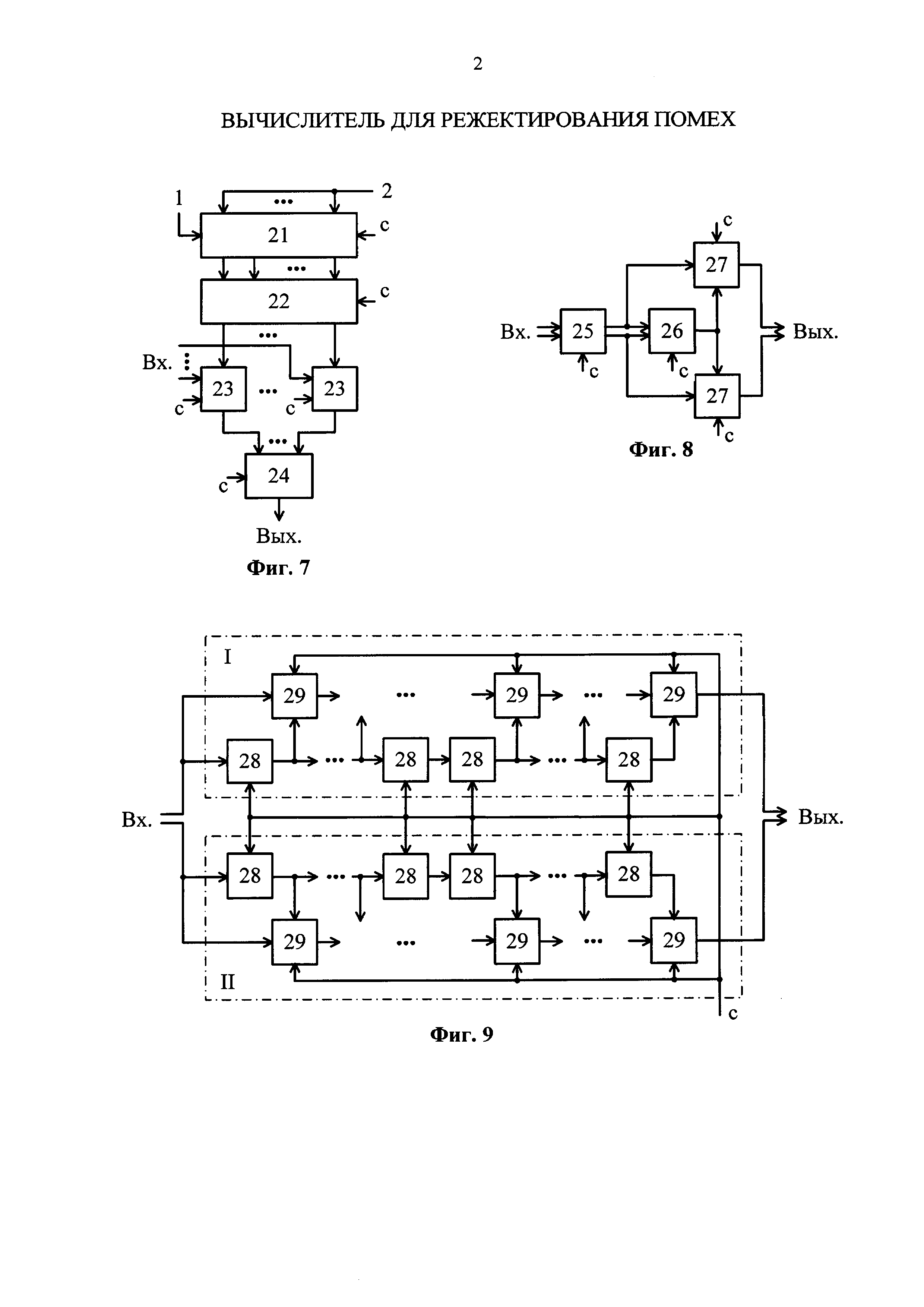

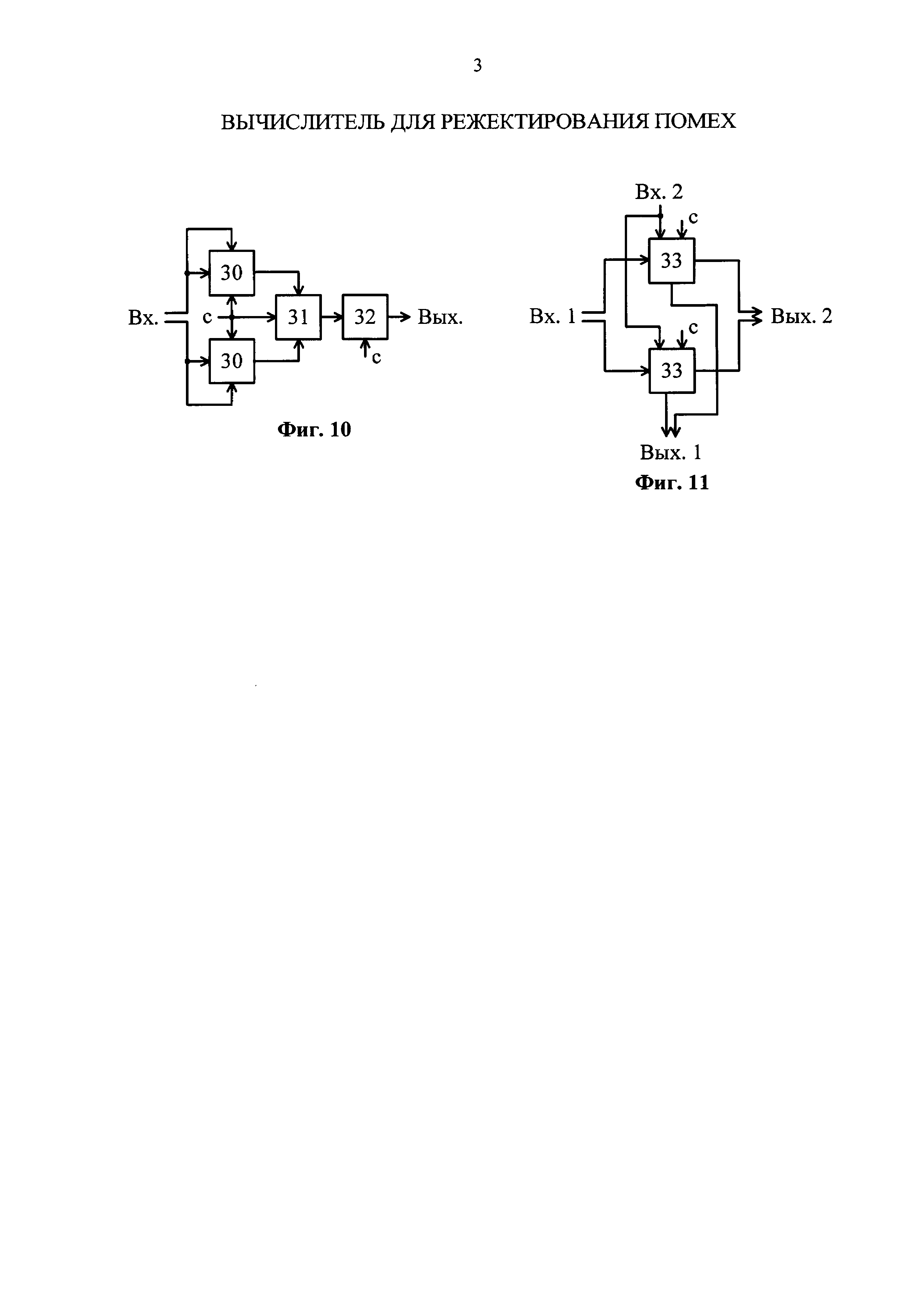

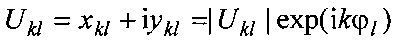

На фиг. 1 представлена структурная электрическая схема вычислителя для режектирования помех; на фиг. 2 - блока задержки; на фиг. 3 - блока комплексного сопряжения; на фиг. 4 - комплексного перемножителя; на фиг. 5 - весового блока; на фиг. 6 - комплексного сумматора; на фиг. 7 - блока переключения; на фиг. 8 - блока точности; на фиг. 9 - накопителя; на фиг. 10 - блока вычисления модуля; на фиг. 11 - двухканального коммутатора.

Вычислитель для режектирования помех (фиг. 1) содержит первый блок 1 задержки, блок 2 весовых коэффициентов, первый комплексный перемножитель 3, весовой блок 4, комплексный сумматор 5, второй комплексный перемножитель 6, блок 7 коммутации, второй блок 8 задержки, блок 9 комплексного сопряжения, блок 10 переключения, блок 11 точности, двухканальный коммутатор 12 и синхрогенератор 13.

Блоки 1, 8 задержки (фиг. 2) содержат два оперативных запоминающих устройства 14; блок 9 комплексного сопряжения (фиг. 3) содержит инвертор 15; комплексный перемножитель 3, 6 (фиг. 4) содержит два канала (I, II), каждый из которых содержит перемножители 16, 17 и сумматор 18; весовой блок 4 (фиг. 5) содержит два перемножителя 19; комплексный сумматор 5 (фиг. 6) содержит два сумматора 20; блок 10 переключения (фиг. 7) содержит счетчик 21, дешифратор 22, блоки 23 совпадений и сумматор 24; блок 11 точности (фиг. 8) содержит накопитель 25, блок 26 вычисления модуля и два делителя 27; накопитель 25 (фиг. 9) содержит два канала (I, II), состоящих из n элементов 28 задержки на интервал tд и n сумматоров 29; блок 26 вычисления модуля (фиг. 10) содержит два перемножителя 30, сумматор 31 и блок 32 извлечения квадратного корня; двухканальный коммутатор 12 (фиг. 11) содержит два коммутатора 33.

Вычислитель для режектирования помех работает следующим образом.

Группа когерентных радиоимпульсов, первоначально излученных с одинаковой несущей частотой и состоящих из сигнала от движущейся цели и пассивной помехи, значительно превышающей сигнал, поступает на вход радиоприемного устройства, в котором усиливается, в квадратурных фазовых детекторах переносится на видеочастоту, а затем подвергается аналого-цифровому преобразованию (соответствующие блоки на фиг. 1 не показаны).

Цифровые коды

где k - номер текущего периода,

Цифровые отсчеты в заявляемом устройстве (фиг. 1) поступают на входы первого блока 1 задержки (фиг. 2) и на соединенные с ними входы весового блока 4 (фиг. 5). Каждый из блоков 1, 8 задержки (фиг. 2) состоит из параллельно включенных оперативных запоминающих устройств (ОЗУ) 14. Причем каждое ОЗУ 14 служит для хранения значений отсчетов с колец дальности каждого квадратурного канала в течение одного периода.

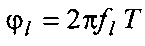

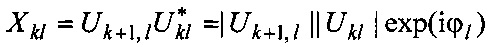

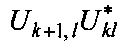

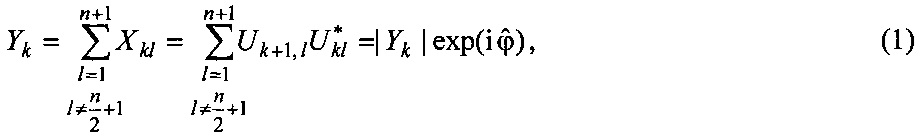

В блоке 9 комплексного сопряжения с помощью инвертора 15 (фиг. 3) происходит инвертирование знака мнимых проекций задержанных отсчетов. В комплексном перемножителе 3 происходит перемножение соответствующих комплексных чисел, реализуемое путем операций с проекциями этих чисел в соответствии с фиг. 4. Образованные величины

поступают в блок 11 точности (фиг. 8), в котором накопитель 25 (фиг. 9) осуществляет с помощью элементов 28 задержки и сумматоров 29 скользящее вдоль дальности в каждом периоде повторения суммирование произведений

где

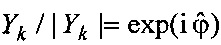

В блоке 26 вычисления модуля (фиг. 10) определяются величины |Yk|, а затем на выходах делителей 27 (фиг. 8) - величины

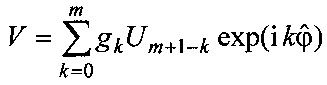

В весовом блоке 4 (фиг. 5) происходит взвешивание поступающих отсчетов весовыми коэффициентами gk, которые хранятся в блоке 2 весовых коэффициентов. Число весовых коэффициентов gk определяется реализуемым порядком вычислителя m, связанным с числом импульсов в группе, равным m+1. В частности, при m=1 весовые коэффициенты g0=-g1=1; при m=2-g0=g2=1, g1=-2; при m=3-g0=-g3=1, g2=-g3=-3. Весовые коэффициенты переключаются в каждом периоде повторения блоком 10 переключения (фиг. 7), который обеспечивает обработку группы импульсов (отсчетов) с одинаковой исходной несущей частотой.

Импульс от синхронизатора радиолокатора (на фиг. 1 не показан), соответствующий излучению зондирующего импульса в каждом периоде, поступает на первый управляющий вход (1) вычислителя (фиг. 1), являющийся первым управляющим входом (1) блока 10 переключения, а затем на счетный вход счетчика 21 (фиг. 7). Показания счетчика, соответствующие номеру импульса в группе, в дешифраторе 22 преобразуются в единичный сигнал на соответствующем номеру импульса выходе дешифратора 22. Этот сигнал открывает подключенный к нему каскад совпадений 23, через который проходит соответствующий весовой коэффициент, поступающий через сумматор 24 на выход блока 10 переключения. Таким образом, каждому периоду и, следовательно, каждому импульсу в группе соответствует свой весовой коэффициент.

Взвешенные в весовом блоке 4 отсчеты суммируются в комплексном сумматоре 5 с задержанными во втором блоке 8 задержки на период повторения T, прошедшими через двухканальный коммутатор 12 и умноженными во втором комплексном перемножителе 6 на величину

Двумерный поворот задержанных отсчетов на угол

Время задержки вводимых во втором комплексном перемножителе 6 фазовых сдвигов обеспечивает их соответствие среднему элементу обучающей выборки, исключенному в накопителе 25 (фиг. 9) в соответствии с выражением (1). Тогда в случае сигнала, соизмеримого по величине с помехой, или разрывной помехи при режектировании отсчетов помехи с элемента разрешения, содержащего сигнал, исключается возможность ослабления или подавления сигнала за счет его влияния на используемые оценки.

После завершения обработки данных m+1 периодов и очередной перестройки несущей частоты на вторые управляющие входы (2) устройства (фиг. 1) и блока 10 переключения (фиг. 7) и управляющий вход блока 7 коммутации поступает импульс, который обнуляет счетчик 21, а в блоке 7 коммутации переключает релаксационный генератор (мультивибратор). По команде блока 7 коммутации двухканальный коммутатор 12 переключает второй блок 8 задержки к выходу вычислителя, и в течение периода повторения Т происходит считывание результатов режектирования V. На вход устройства поступают и начинают обрабатываться данные первого периода следующей группы.

Синхронизация вычислителя для режектирования помех осуществляется подачей на все блоки заявляемого устройства последовательности синхронизирующих импульсов от синхрогенератора 13 (фиг. 1), управляемого совместно с блоком 10 переключения импульсами (1) синхронизатора радиолокатора (на фиг. 1 не показан), следующими с интервалом Т. Период повторения синхронизирующих импульсов равен интервалу временной дискретизации tд, выбираемому из условия требуемой разрешающей способности по дальности.

Достигаемый технический результат состоит в следующем. На выход устройства не поступают нескомпенсированные остатки помехи в переходном режиме, традиционно маскирующие сигнал от цели. В предлагаемом устройстве на выход поступают только скомпенсированные остатки помехи в установившемся режиме, что исключает эффект «кромки» помехи и повышает эффективность выделения сигналов движущихся целей.

Таким образом, вычислитель для режектирования помех повышает эффективность компенсации помехи и выделения сигналов движущихся целей на фоне пассивных помех с априорно неизвестной доплеровской скоростью.

Библиография

1. Патент №63-49193 (Япония), МПК G01S 13/52. Радиолокационное устройство для обнаружения движущейся цели / К.К. Тосиба. Опубл. 03.10.1988. - Изобретения стран мира. - 1989. – Вып. 109. - №15. - С. 52.

2. Радиоэлектронные системы: основы построения и теория. Справочник / Я.Д. Ширман, С.Т. Багдасарян, А.С. Маляренко, Д.И. Леховицкий [и др.]; под ред Я.Д. Ширмана. - 2-е изд., перераб. и доп. - М.: Радиотехника, 2007; с. 439, рис. 25.22.

3. А.с. 743208 СССР, МПК G01S 7/36. Цифровое устройство для подавления пассивных помех / Д.И. Попов. - №2540079/09; заявл. 03.11.1977; опубл. 25.06.1980. Бюл. №23. - 4 с.

Реферат

Изобретение относится к вычислительной технике и предназначено для выделения сигналов движущихся целей на фоне пассивных помех при групповой перестройке несущей частоты зондирующих импульсов. Техническим результатом является повышение эффективности выделения сигналов движущихся целей. Вычислитель для режектирования помех содержит первый и второй блоки задержки, блок весовых коэффициентов, первый и второй комплексные перемножители, весовой блок, комплексный сумматор, блок комплексного сопряжения, блок переключения, блок точности, блок коммутации, двухканальный коммутатор и синхрогенератор, определенным образом соединенные между собой и осуществляющие когерентную обработку исходных отсчетов. 11 ил.

Комментарии