Устройство для защиты интегральной схемы вертикального отклонения для монитора - RU2124225C1

Код документа: RU2124225C1

Чертежи

Описание

Данное изобретение касается в общем защиты интегральной схемы (ИС) вертикального отклонения для монитора и, в частности, устройства для защиты ИС вертикального отклонения для монитора с использованием специализированной интегральной схемы (ИС), чипа, канала передачи данных дисплея (DDC), который может воспрепятствовать повреждению ИС вертикального отклонения из-за мгновенной подачи вертикального синхросигнала в 25 кГц или более в схему вертикального отклонения монитора, когда данные, хранимые в специализированном чипе DDC, считываются компьютером.

Описание предшествующего уровня техники

В целом, монитор может использовать специализированный чип DDC,

в котором информация о спецификации, дате производства, серийном номере монитора и т. д. была сохранена производителем. В случае необходимости такая DDC информация может быть выведена на экран

монитора пользователем.

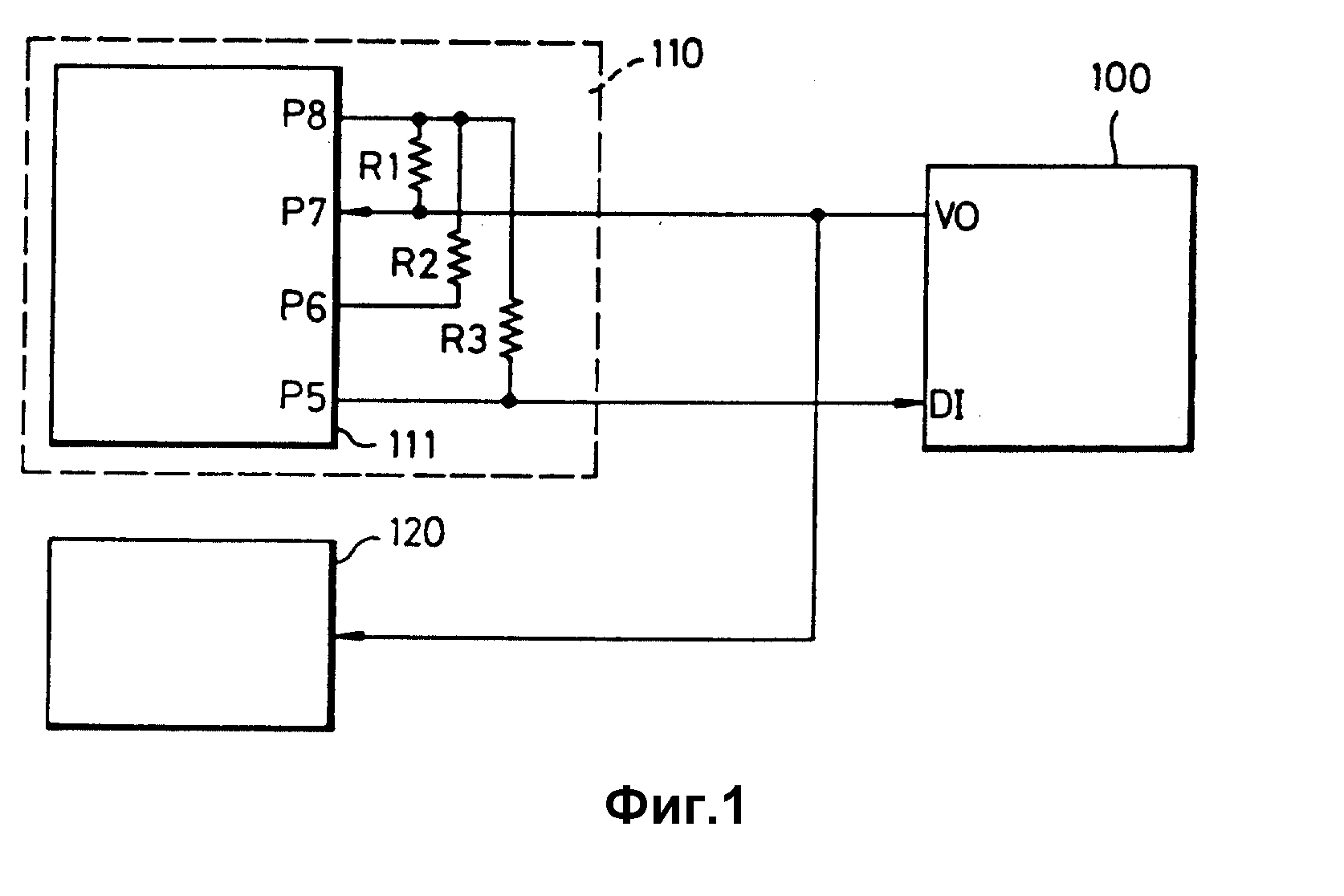

Фиг. 1 является блок-схемой известного устройства для монитора, использующего специализированный чип DDC. Согласно фиг. 1 стандартное устройство снабжено секцией ввода-вывода (I/0) 100 компьютера, которая выдает вертикальный синхросигнал, подаваемый из компьютера в DDC секцию 110 и секцию 120 вертикального отклонения при подаче энергии, а затем получает информационные данные монитора от DDC секции 110 после истечения заданного времени; DDC секцией 110, которая получает вертикальный синхросигнал, выдаваемый из I/0 секции 100 компьютера, а затем выдает информационные данные монитора, хранящиеся в ней, I/0 секции 100 компьютера по истечении заданного времени; и секцией 120 вертикального отклонения, которая получает вертикальный синхросигнал, выдаваемый от секции 100 I/0 компьютера, и производит вертикальное отклонение в соответствии с входным вертикальным синхросигналом.

Работа известного устройства для монитора, использующего чип DDC, будет описана в деталях.

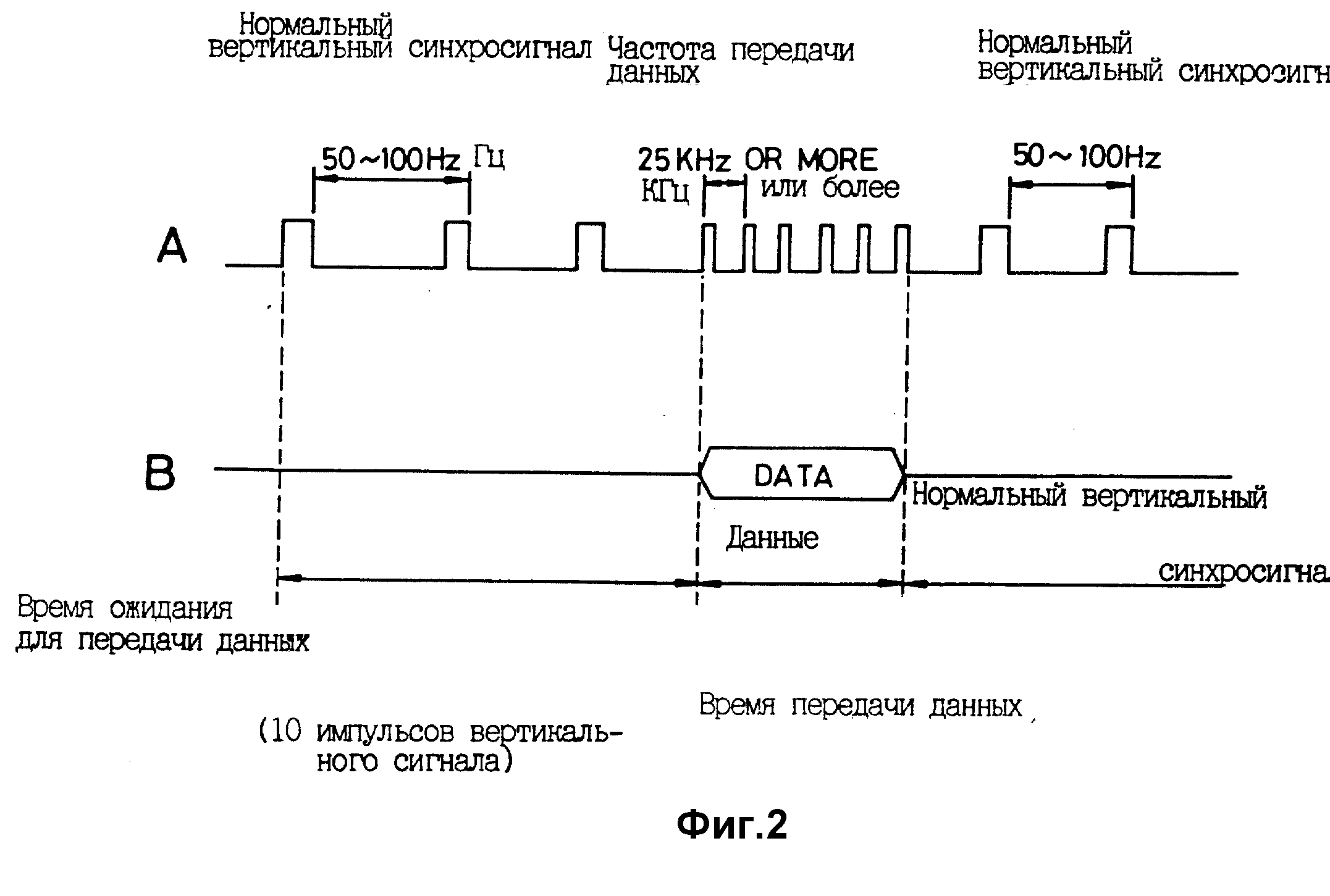

При подаче энергии на монитор секция 100 I/0 компьютера выводит вертикальный синхросигнал около 50-100 Гц, как показано на фиг. 2А, через ее терминал вывода VO на седьмой вывод P7 специализированного чипа DDC111 в DDC секции 110 и в секцию 120 вертикального отклонения.

Период, за который выводятся десять импульсов вертикального синхросигнала, соответствует времени ожидания для передачи данных, как показано в фиг. 2В. По истечении этого времени ожидания DDC секция 110 выводит информационные данные монитора, хранящиеся в специализированном чипе DDC 111 через ее пятый вывод Р5 в терминал ввода данных D1 секции 100 I/0 компьютера.

В это время информационные данные монитора передаются с частотой передачи данных около 25 кГц или более для того, чтобы сократить время передачи данных. Другими словами, вертикальный синхросигнал около 25 кГц или более выводится из терминала вывода VO секции 110 I/0 компьютера в секцию 120 вертикального отклонения, и таким образом вертикальное отклонение ИС (не показано) в секции 120 вертикального отклонения производит вертикальное отклонение в соответствии с вертикальным синхросигналом. В результате информация, хранящаяся в специализированном чипе DDC 111 в DDC секции 110, подается на экран монитора.

После завершения передачи данных, как описано выше, секция 100 I/0 компьютера выдает нормальный вертикальный синхросигнал около 50-100 Гц через ее терминал вывода VO на седьмой вывод Р7 специализированного чипа DDC 111 в DDC секции 110 и в секцию 120 вертикального отклонения, что приводит к показу на экране монитора нормального изображения.

В стандартном устройстве для монитора, использующего специализированный чип DDC, однако, вертикальное отклонение ИС в секции 120 вертикального отклонения предназначено для работы с вертикальным синхросигналом около 50-100 кГц, и, таким образом, оно подвержено повреждению в случае введения вертикального синхросигнала около 25 кГц для передачи данных DDC и тем самым ухудшению надежности монитора.

Данное изобретение направлено на решение проблем, имеющихся в известном уровне техники. Целью данного изобретения является обеспечение устройства защиты ИС вертикального отклонения для монитора, использующего специализированный чип DDC. Это устройство может помешать повреждению ИС вертикального отклонения путем прерывания ввода вертикального синхросигнала около 25 кГц для применения в передаче данных в схему вертикального отклонения в мониторе, когда данные, хранящиеся в специализированном чипе DDC, считываются компьютером.

Для достижения вышеуказанной цели обеспечено устройство для защиты ИС

вертикального отклонения для монитора, соединенного с компьютером и имеющего средства DDC и средства вертикального отклонения, включающие в себя ИС вертикального отклонения, причем это устройство

содержит

средство I/0 (ввода/вывода) компьютера, обеспечивающее вертикальный синхросигнал для DDC средства и средства вертикального отклонения при подаче энергии и получающее информационные

данные монитора от DDC по истечении заданного времени;

DDC средство, получающее вертикальный синхросигнал, обеспечиваемый средством I/0 компьютера, и обеспечивающее информационные данные

монитора для I/0 компьютера по истечении заданного времени; и

средство управления выбором вертикальной частоты, обеспечивающее вертикальный синхросигнал для средства вертикального отклонения,

если этот вертикальный синхросигнал получен от I/0 компьютера, и превышающее ввод неправильного вертикального синхросигнала к средству вертикального отклонения, имеющего более высокую частоту, чем

частота вертикального синхросигнала, при получении неправильного вертикального синхросигнала от I/0 компьютера.

Вышеуказанная цель и другие характеристики данного изобретения станут

более очевидными при описании его предпочтительного варианта со ссылкой на приложенные рисунки, в которых

фиг. 1 является блок-схемой известного устройства для монитора, использующего

специализированный чип DDC,

фиг. 2А и 2В являются диаграммами в форме сигналов, объясняющими работу устройства фиг. 1,

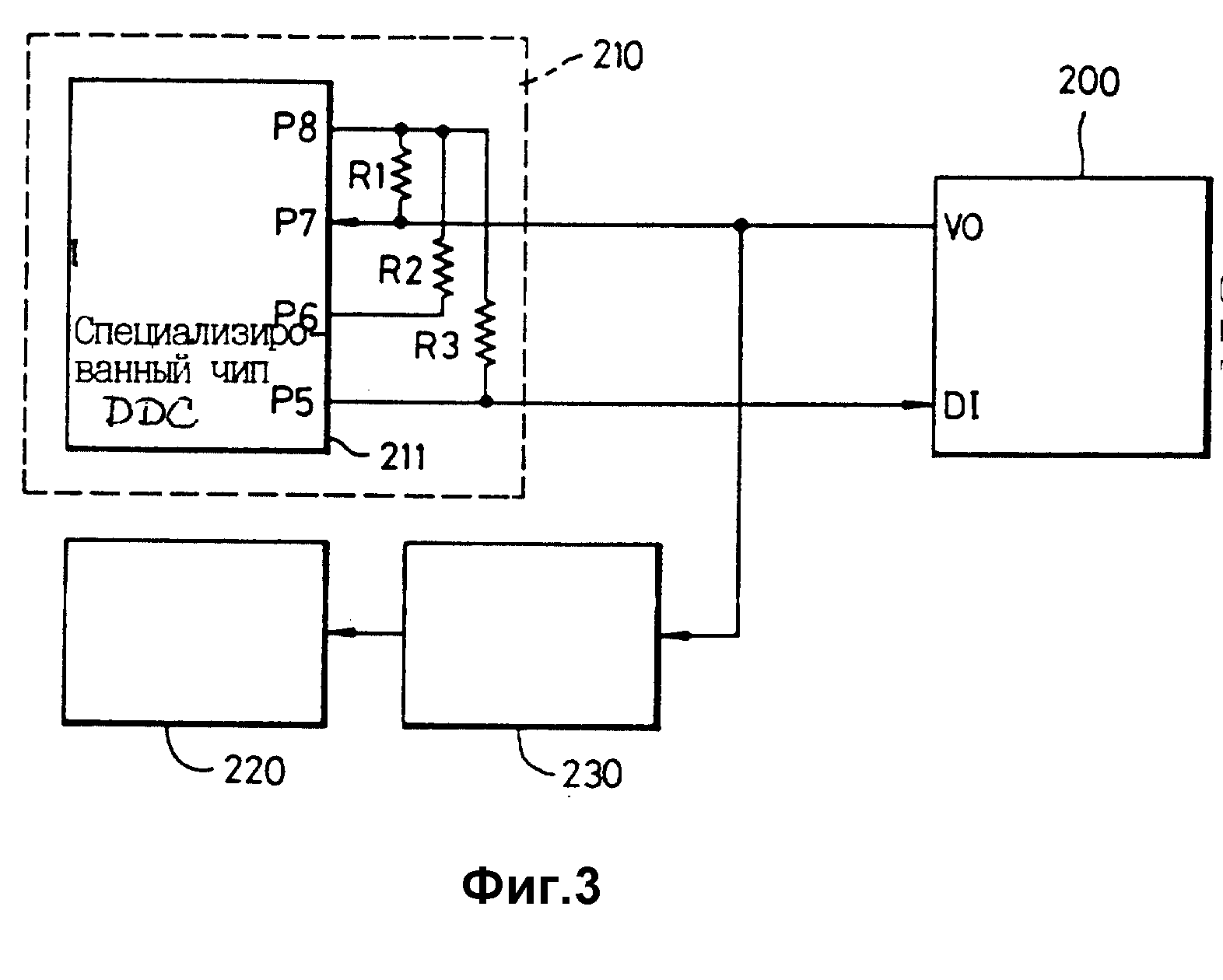

фиг 3 является блок-схемой защитного устройства согласно

данному изобретению,

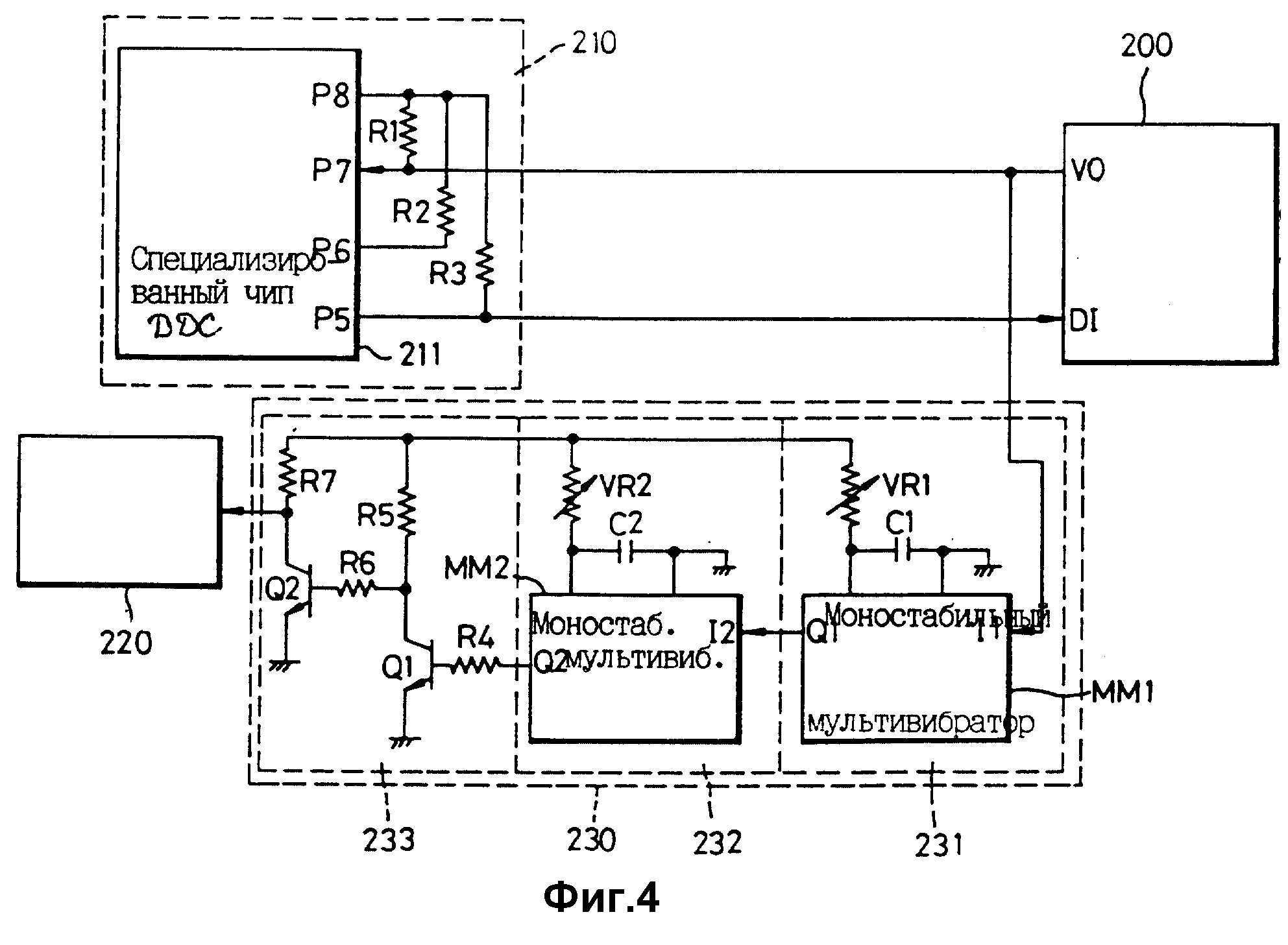

фиг. 4 является принципиальной схемой варианта защитного устройства согласно изобретению,.

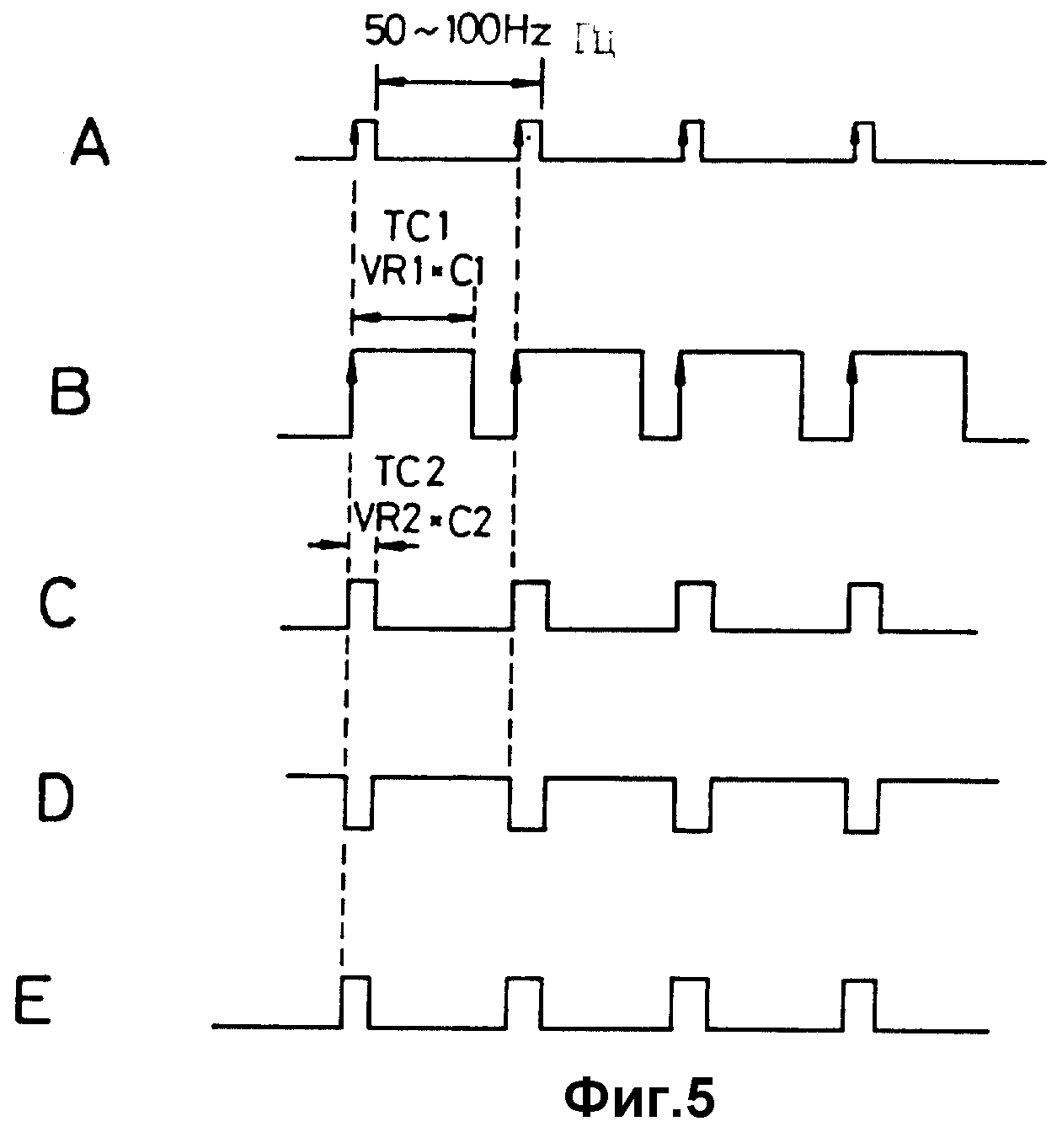

фиг. 5А-5Е являются диаграммами в форме сигналов, объясняющими

работу секции управления выбором вертикальной частоты в фиг. 4 при введении нормального вертикального синхросигнала,

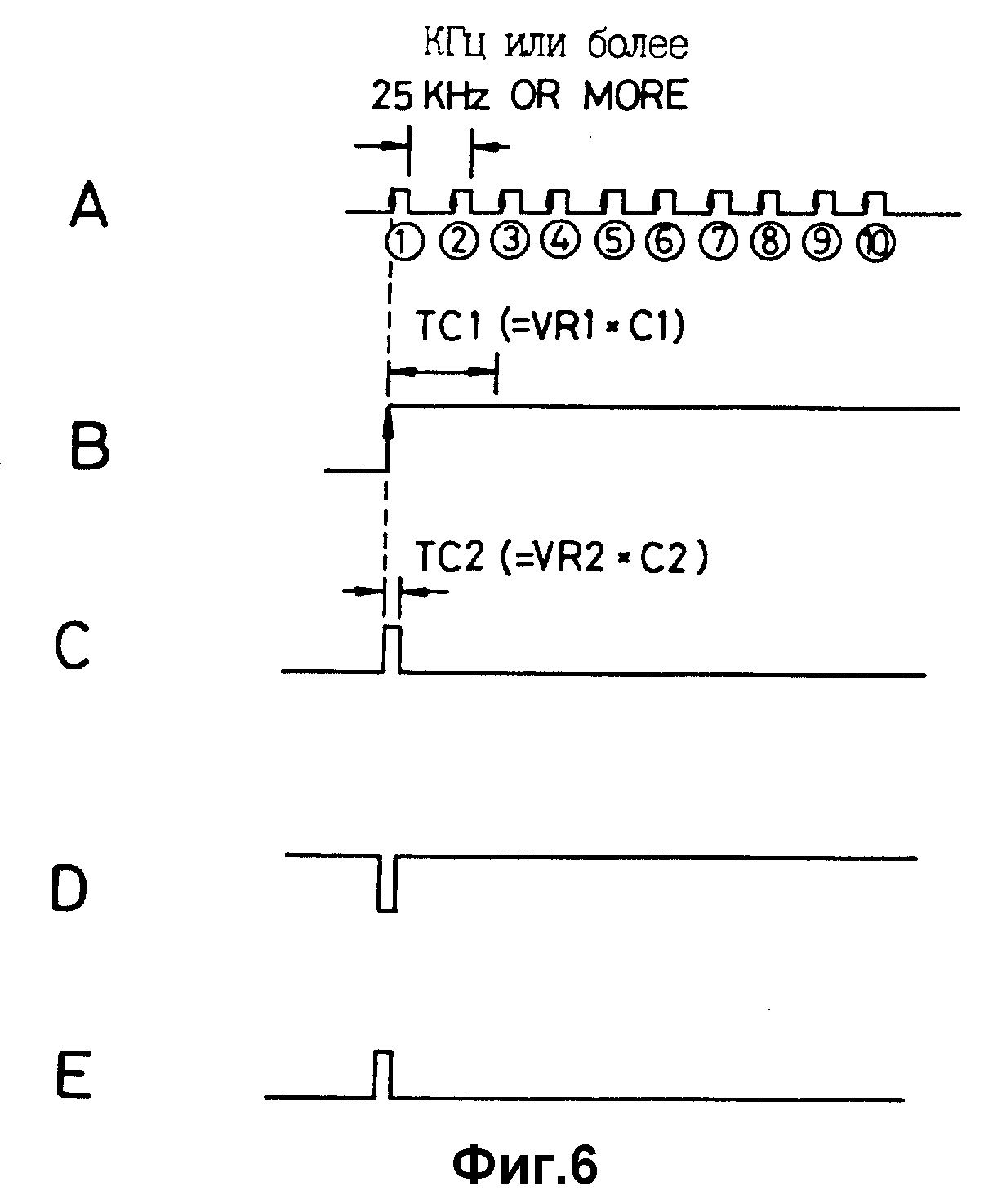

фиг. 6А-6Е являются диаграммами в форме сигналов, объясняющими работу

секции управления выбором вертикальной частоты в фиг. 4 при введении неправильного вертикального синхросигнала, имеющего частоту выше частоты нормального вертикального синхросигнала.

Фиг. 3 является блок-схемой защитного устройства согласно данному изобретению. Согласно фиг. 3 защитное устройство данного изобретения снабжено секцией 200 I/0 компьютера, которая выводит вертикальный синхросигнал, подающийся из компьютера, в DDC секцию 210 и секцию 220 вертикального отклонения при подаче электроэнергии и получает информационные данные монитора от DDC секции 210 по истечении заданного времени; DDC секцией 210, которая получает вертикальный синхросигнал, выданный из секции 200 I/0 компьютера, и выдает информационные данные монитора в секции 200 I/0 компьютера по истечении заданного времени; секцией 230 управления выбором вертикальной частоты, которая выдает вертикальный синхросигнал в секцию 220 вертикального отклонения, если вертикальный синхросигнал получен от секции 100 I/0 компьютера, и которая прерывает ввод неправильного вертикального синхросигнала в секцию 220 вертикального отклонения, имеющего частоту, более высокую, чем частота вертикального синхросигнала, при получении неправильного вертикального синхросигнала от секции 100 I/0 компьютера; секцией 220 вертикального отклонения, которая производит вертикальное отклонение в соответствии с вертикальным синхросигналом, полученным от секции 230 управления выбором вертикальной частоты.

Между тем секция 230 управления выбором вертикальной частоты содержит секцию 231 первого моностабильного мультивибратора, которая получает вертикальный синхросигнал и выводит сигнал первого импульса, имеющий первую ширину, определяемую первой временной константой, секцию 232 второго моностабильного мультивибратора, которая получает сигнал первого импульса, выданный от секции 231 первого моностабильного мультивибратора, и выводит сигнал второго импульса, имеющий ширину второго импульса, определяемую второй временной константой, и переключающую секцию 233, которая является управляемым переключателем в соответствии с сигналом второго импульса, выданным от секции 232 второго моностабильного мультивибратора, и передает сигнал второго импульса в секцию 220 вертикального отклонения.

Работа защитного устройства ИС вертикального отклонения согласно данному изобретению, как показано выше, будет теперь объяснена ссылкой на фиг. 3, 4, 5А-5Е, 6А-6Е.

Секция 200 I/0 компьютера, DDC секция 210 и секция 220 вертикального отклонения в фиг. 3 и 4 являются такими же, что и в случае стандартного устройства в конструкции и работе соответственно и поэтому детальное объяснение для этих секций будет опущено.

Если нормальный вертикальный синхросигнал, имеющий частоту от 50 до 100 Гц, как показано в фиг. 5А, выводится от секции 200 I/0 компьютера, как показано в фиг. 5А, первый моностабильный мультивибратор ММ1 в секции 230 управления выбором вертикальной частоты получает нормальный вертикальный синхросигнал через его терминал ввода 11. Первый моностабильный мультивибратор ММ1 запускается на положительном перепаде вертикального синхросигнала и затем регулирует ширину импульса его выходного сигнала в соответствии с первой временной константой, определяемой переменным резистором VR1 и конденсатором C1, которые соединены с внешними терминалами ввода первого моностабильного мультивибратора ММ1, как показано в фиг. 5В.

Сигнал с отрегулированной шириной импульса затем выводится из терминала вывода Q1 первого моностабильного мультивибратора ММ1. В это время при правильном регулировании переменного резистора VR1 выходной сигнал первого моностабильного мультивибратора ММ1 переходит на "низкий" уровень перед введением следующего импульса вертикального синхросигнала в первый моностабильный мультивибратор ММ1.

Второй моностабильный мультивибратор ММ2 получает выходной сигнал импульса первого моностабильного мультивибратора ММ1 через его терминал ввода 12 и регулирует ширину импульса его выходного сигнала в соответствии с второй временной константой, определяемой переменным сопротивлением VR2 и конденсатором C2, которые соединены с внешними входными терминалами второго моностабильного мультивибратора ММ2, как показано в фиг. 5C. В это время при правильной регулировке переменного резистора VR2 импульсный сигнал, выведенный с выходного терминала Q2 второго моностабильного мультивибратора ММ2, имеет такую же ширину импульса, что и в случае с вертикальным синхросигналом, полученным секцией 200 I/0 компьютера.

Сигнал выходного импульса второго моностабильного мультивибратора ММ2 вводится на базу транзистора Q1 в переключающей секции 233, транзистор Q1 повторяет операцию включения-выключения для вывода через его коллектор сигнала инвертированного импульса, как показано в фиг. 5D. Сигнал импульса обратной полярности вводится на базу транзистора Q2 и, таким образом, транзистор Q2 выводит через его коллектор сигнал импульса обратной полярности вторично, как показано в фиг. 5Е.

В результате сигнал выходного импульса второго моностабильного мультивибратора ММ2 является идентичным вертикальному синхросигналу, полученному от секции 200 I/0 компьютера, и вводится в секцию 220 вертикального отклонения.

Между тем, если неправильный вертикальный синхросигнал, имеющий высокую частоту около 25 кГц, выводится от секции 200 I/0 компьютера в терминал 11 ввода первого моностабильного мультивибратора ММ1 в секции 230 контроля выбора вертикальной частоты, как показано в фиг. 6А, то есть в случае, когда информационные данные монитора передаются от DDC секции 210 в секцию 200 I/0 компьютера, первый моностабильный мультивибратор ММ1 запускается при положительном перепаде вертикального синхросигнала, как показано в фиг. 6В, и затем регулирует ширину импульса его выходного сигнала в соответствии с первой временной константой, определяемой переменным резистором VR1 и конденсатором C1.

С учетом высокой частоты входного вертикального синхросигнала, было определено, что в это время первая временная константа является относительно большой, и это заставляет выходной сигнал через выходной терминал Q1 первого моностабильного мультивибратора ММ1 удерживаться в "высоком" уровне, как показано в фиг. 6В, до тех пор, пока следующие импульсы вертикального синхросигнала не будут введены в первый моностабильный мультивибратор ММ1. Согласно этому выходной сигнал первого моностабильного мультивибратора ММ1 удерживается в "высоком" уровне, пока передача данных от DDC секции 210 не завершится.

Второй моностабильный мультивибратор ММ2 получает через его входной терминал 12 сигнал "высокого" уровня, выданный от выходного терминала Q1 первого моностабильного мультивибратора ММ1, и затем регулирует ширину импульса его выходного сигнала согласно второй временной константе, определяемой переменным резистором VR2 и конденсатором C2, как показано в фиг. 6С. Выходной сигнал второго моностабильного мультивибратора ММ2 переходит на "низкий" уровень по истечении периода второй временной константы, и такое состояние "низкого" уровня поддерживается, пока передача данных от DDC секции 210 не завершится. Выходной сигнал второго моностабильного мультивибратора ММ2, как описано выше, затем вводится в переключающую секцию 233.

Транзистор Q1 во втором моностабильном мультивибраторе ММ2 инвертирует выходной сигнал второго моностабильного мультивибратора ММ2 и выводит этот инвертированный сигнал через его коллектор, как показано в фиг. 6D. Инвертированный сигнал, выданный из транзистора Q1, инвертируется вторично транзистором Q2, как показано в фиг. 6Е, а затем вводится в секцию 220 вертикального отклонения.

В результате сигнал одного импульса, имеющий ширину импульса, которая соответствует второй временной константе, определенной переменным резистором VR2 и конденсатором C2 в секции 232 второго моностабильного мультивибратора, вводится в секцию 220 вертикального отклонения во время передачи данных DDC секцией 210.

Из предыдущего должно быть ясно, что защитное устройство согласно данному изобретению обеспечивает такие преимущества, что оно может препятствовать повреждению ИС вертикального отклонения в мониторе путем прерывания ввода сигнала высокой частоты около 25 кГц в ИС вертикального отклонения при передаче данных от специализированного чипа DDC в компьютер.

Хотя данное изобретение было описано и иллюстрировано здесь со ссылкой на его предпочтительный вариант, специалистам будет ясно, что могут быть сделаны различные его изменения в форме и деталях без отхода от существа и объема данного изобретения.

Реферат

Защитное устройство интегральной схемы (ИС) вертикального отклонения для монитора использует специализированную интегральную схему (чип) канала передачи данных дисплея (DDС ), которая может препятствовать повреждению ИС вертикального отклонения путем прерывания ввода сигнала высокой частоты около 25 кГц в ИС вертикального отклонения при считывании компьютером информационных данных монитора, хранящихся в чипе. Защитное устройство содержит средство канала передачи данных дисплея, получающее вертикальный синхросигнал от средства ввода/вывода компьютера и выдающее DDС данные в средство ввода/вывода компьютера по истечении заданного времени, и средство управления выбором вертикальной частоты, которая прерывает ввод неправильного вертикального синхросигнала, имеющего более высокую частоту, чем частота нормального вертикального синхросигнала, в ИС вертикального отклонения, когда неправильный вертикальный синхросигнал вводится от средства ввода/вывода компьютера для передачи DDС данных. Технический результат заключается в том, что устройство обеспечивает защиту ИС вертикального отклонения. 1 з.п.ф-лы. 6 ил.

Комментарии