Возбудитель/приемник двухнаправленной линии передачи - RU2142194C1

Код документа: RU2142194C1

Чертежи

Описание

Настоящая заявка частично является продолжением находящейся на рассмотрении заявки с серийным номером 08/376,708, поданной 23 января 1995 года на возбудитель/приемник двухнаправленной линии передачи.

ПРЕДПОСЫЛКИ ИЗОБРЕТЕНИЯ

Область техники

Представлен приемопередатчик линии передачи. Более конкретно, представлен приемопередатчик линии передачи, имеющий активную оконечную нагрузку линии передачи и источник сигнала переменного уровня,

который хорошо приспособлен к работе одновременно в двух направлениях.

Описание уровня техники

По мере возрастания скорости работы процессоров компьютеров, на устройства,

которые должны посылать и принимать логические сигналы, налагаются дополнительные требования.

Во время измерения высокочастотных сигналов частота дискретизации разумеется больше, чем при измерении низкочастотных сигналов. Измерить точную величину сигнала при высокой частоте дискретизации сложнее, чем при низкой частоте дискретизации, так как переходные режимы, которые не влияют сколько-нибудь заметно в течение относительно длительного периода времени низкой частоты дискретизации, могут оказывать существенное влияние в течение более короткого периода времени более высокой частоты дискретизации.

Одним из высокочастотных воздействий, с которым имеет дело настоящее изобретение, связано с отражением сигнала, что имеет место, когда полное сопротивление канала связи не согласуется с полным сопротивлением нагрузки на принимающем конце этого канала. (Канал связи между посылающим (передающим) и принимающим устройством включает такой канал связи, как шина между устройствами на единой монтажной плате или кабель между устройствами на различных платах. В любом случае, так как в настоящем изобретении рассматриваются относительно высокочастотные сигналы, при рассмотрении которых необходимо учитывать влияние линии передачи, то канал связи может рассматриваться как линия передачи). В идеальном случае оконечная нагрузка будет принимать переданный сигнал немедленно после его поступления на нагрузку, так что величина сигнала может быть дискретизирована немедленно после его поступления на нагрузку, точная величина сигнала может быть определена из выборки. Однако, если оконечная нагрузка не согласована с полным сопротивлением линии передачи, то нагрузка будет принимать только часть сигнала после его первого поступления. Остальная часть сигнала будет отражаться обратно в передающую линию. Обычно, в зависимости от некоторого количества факторов, по крайней мере часть этой отраженной части сигнала в конечном счете будет отражаться от других нагрузок линии передачи обратно к окончательной нагрузке и такое отражение туда и обратно от нагрузок линии будет повторяться до тех пор, пока в конце концов все большая и большая часть сигнала не будет принята оконечной нагрузкой.

Влияние такого отражения сигнала в лучшем случае заключается в задержке по времени точной дискретизации сигнала до момента, когда сигнал пройдет, возможно, через множество циклов отражения в линии передачи. В худшем случае, когда существенная часть отраженной части рассеивается в самой линии передачи или поглощается другими нагрузками линии передачи, влияние такого отражения заключается в значительном понижении точности, с которой может быть измерена величина сигнала, может быть настолько, что невозможным окажется сколько-нибудь точно определить логическую величину сигнала. Поэтому желательно исключить или по крайней мере сильно уменьшить отражение сигнала путем согласования, насколько это возможно, сопротивления оконечной нагрузки и сопротивления линии передачи.

Хорошо известно, что для облегчения одновременной двунаправленной передачи, от передающего устройства к принимающему устройству посылаются многозначные логические сигналы. Для многозначного логического сигнала приемник должен быть более избирательным, чем приемник, который просто определяет состояние включения или состояние выключения. То есть приемник для многозначных логических сигналов должен измерять величину принимаемого сигнала гораздо точнее, чем приемник, который должен просто определять присутствие или отсутствие сигнала. Таким образом, имеется огромный стимул для согласования полного сопротивления в случае высокочастотных многозначных сигналов.

Хотя относительно просто и экономично изготовлять линию передачи между устройствами с жестким контролем полного сопротивления линии передач, но не так просто с экономической точки зрения производить фиксированную оконечную нагрузку с жесткими пределами полного сопротивления. Поэтому желательно иметь возможность эффективного согласования полного сопротивления оконечной нагрузки и тока логического сигнала во время работы для исключения или значительного уменьшения отражения сигнала благодаря использованию компонентов, которые могут быть произведены с малыми затратами.

Согласование внутреннего сопротивления посредством активных устройств может быть достигнуто путем подачи, дополнительно к сигналу передачи, первого сигнала, по первой опорной линии от отправителя к получателю, сообщающего получателю амплитуду логического сигнала, а также второго сигнала по второй опорной линии от получателя к отправителю, сообщающего отправителю полное сопротивление оконечной нагрузки линии передачи в приемнике. Однако, в частности, если по линии связи взаимодействует несколько отправителей и получателей, то эта конструкция непригодна, так как необходимо наличие некоторого количества опорных линий. Поэтому желательно также минимизировать отражение сигнала с одной опорной линии между устройствами, на линии передачи.

Адаптивная схема, которая согласует выходное полное сопротивление опорного возбудителя с сопротивлением опорной линии передачи и генерирует управляющее напряжение для согласования выходных полных сопротивлений других возбудителей в одной и той же микросхеме с тем же внутренним сопротивлением, описана автором Patel и др. в "Адаптивный возбудитель линии передачи CMOS (КМОП-структура)", труды: Шестая ежегодная IEEE международная конференция ASIC и выставка Rochester, NY, США, страницы 460-463. Рассогласование сопротивлений несомненно существенно понижено.

В US-A-2620188 описана многоуровневая логическая схема, включающая по крайней мере один детектор входного уровня, который может принимать один или более многоуровневых входных сигналов, управляющее коммутирующее устройство и генератор выходного уровня, передающий один многоуровневый выходной сигнал. Обобщенная схема позволяет создавать различные логические вентили, работающие с любой выбранной базой n.

КРАТКОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

В соответствии с первым аспектом

настоящего изобретения представлено передающее устройство (возбудитель) и принимающее устройство, взаимосвязанные посредством линии передачи с определенным характеристическим полным сопротивлением для

передачи логических сигналов по линии передачи между этими устройствами. Возбудитель имеет источник для передачи логических сигналов, а также задающий генератор, связанный с источником для установки

величины сигналов, передаваемых источником. Приемник имеет нагрузку линии передачи для приема сигналов, а также задающий генератор, связанный с нагрузкой для установки смещения оконечной нагрузки для

установления определенного семейства внутренних сопротивлений нагрузки для приема сигналов. Задающий генератор возбудителя и задающий генератор приемника интерактивно согласуют внутреннее

сопротивление нагрузки с линией передачи для установки величины сигналов.

Предпочтительно, чтобы схема принимающего и передающего устройства для генерации и приема цифровых сигналов по линии передачи реагировала на ввод генерируемых внешним образом цифровых данных и на сигналы управления. Предпочтительно, чтобы эталонная схема, вырабатывающая первый и второй опорные сигналы, была общей для схемы генерации и приема сигнала. В частности, предпочтительно использование одной опорной линии для передачи опорных сигналов между передающими и принимающими устройствами.

В соответствии с предпочтительным исполнением настоящего изобретения схема генерации сигнала включает источник сигнала, связанный с линией передачи для генерации цифрового сигнала переменного уровня, а также схему согласования и коммутации опорного уровня ("схему RLA/S"), которая реагирует на ввод цифровых данных и на первый опорный сигнал. Схема RLA/S связана с источником сигнала для выбора уровня цифрового сигнала переменного уровня и подачи сигнала коммутации. Выход источника сигнала согласуется и коммутируется таким образом, что источник сигнала генерирует в линию передачи цифровой сигнал, после чего следует ввод цифровых данных на выбранном уровне выходного сигнала.

Предпочтительно также, чтобы схема приема сигнала имела схему с переменным входным полным сопротивлением, связанную с линией передачи, которая реагировала бы на второй опорный сигнал для приема цифровых сигналов переменного уровня по линии передачи. Кроме этого она включает схему детектирования, подключенную для приема цифровых сигналов переменного уровня от схемы с переменным входным полным сопротивлением. Схема детектирования реагирует на первый опорный сигнал и выявляет логические состояния цифровых сигналов переменного уровня, установленные первым опорным сигналом. Схема детектирования кроме этого преобразует выявленные логические состояния в соответствующие логические сигналы заранее определенных выходных уровней.

В соответствии с другими аспектами схемы генерации сигнала схема RLA/S ускоряет коммутацию источника сигнала, поддерживая уровень выходного цифрового сигнала источника сигнала не выше уровня, установленного первым опорным сигналом. То есть во время генерации выходного цифрового сигнала источник сигнала переключается между первым и вторым выходными состояниями, скорость переключения источника сигнала зависит от уровня сигнала коммутации, подаваемого на источник сигнала, а на исходном этапе коммутации уровень сигнала коммутации, подаваемого на источник сигнала от схемы RLA/S, увеличивается до уровня, превышающего уровень, установленный первым опорным сигналом, чтобы схема коммутации увеличивала скорость коммутации источника сигнала. Затем, после исходного этапа коммутации уровень сигнала коммутации согласуется с первым опорным сигналом так, что выходной цифровой сигнал источника сигнала не превышает по уровню уровень, установленный первым опорным сигналом.

В соответствии с другими аспектами схемы генерации сигнала имеется схема переопределения выходного уровня. Схема переопределения связана со схемой RLA/S и в ответ на цифровой сигнал управления переопределяет уровень выбранного выходного сигнала, установленный первым опорным сигналом согласования так, что устанавливается определенный, заранее установленный максимальный уровень выходного сигнала.

В соответствии с другими аспектами настоящего изобретения общая эталонная схема кроме этого вырабатывает третий опорный сигнал, а схема приема сигнала далее имеет схему с фиксированным входным полным сопротивлением, связанную с линией передачи для приема цифровых сигналов переменного уровня по линии передачи. Совместно со схемой с фиксированным полным сопротивлением подключается вторая схема детектирования для приема цифровых сигналов переменного уровня по линии передачи. Вторая схема детектирования реагирует на первый и третий опорные сигналы и выявляет логические состояния цифровых сигналов переменного уровня, определенные первым и третьим опорными сигналами. Вторая схема детектирования кроме этого преобразует выявленные логические состояния в соответствующие логические сигналы с заранее определенными выходными уровнями.

В соответствии с другими аспектами принимающей схемы, в ответ на один из внешних сигналов управления, схема с переменным входным полным сопротивлением, содержащая блокивующий коммутатор, устанавливает режим блокировки, имеющий высокое входное полное сопротивление так, что линия передачи разгружается.

Другие цели и преимущества настоящего изобретения станут очевидными знакомым с данной областью техники после следующего детального описания. Предпочтительное исполнение настоящего изобретения показано путем иллюстрации наилучшего режима, предлагаемого для осуществления настоящего изобретения. Возможны и другие исполнения, а детали могут быть изменены для различных ситуаций без отрыва от сути настоящего изобретения. Например, для логических сигналов вместо токов могут использоваться напряжения. В качестве другого примера оконечной нагрузкой линии передачи выбирается полевой транзистор ("FET"). Могут использоваться и биполярные устройства. Кроме этого, хотя и показаны экранированные опорные линии и линии передачи, но могут использоваться также и неэкранированные линии. Соответственно, к чертежам и к описанию необходимо относиться как к иллюстративным по сущности, а не как к ограничивающим.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Предпочтительное исполнение будет описано со ссылкой на прилагаемые чертежи, на которых:

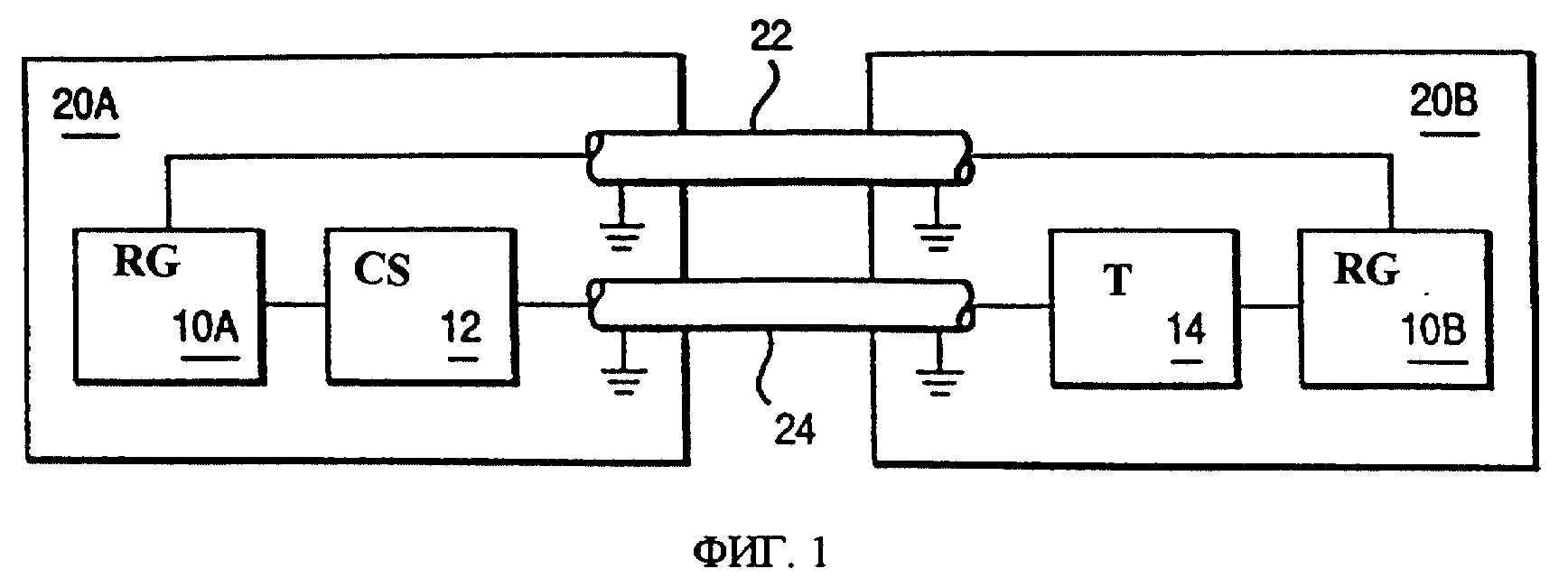

Фиг. 1 является

блок-схемой возбудителя, взаимосвязанного посредством линии передачи с приемником;

Фиг. 2 является блок-схемой возбудителя/приемника, взаимосвязанных линией передачи;

Фиг. 3 является

более детальной блок-схемой одного из возбудителей/приемников;

Фиг. 4 является диаграммой схемы дифференциального усилителя напряжения задающего генератора;

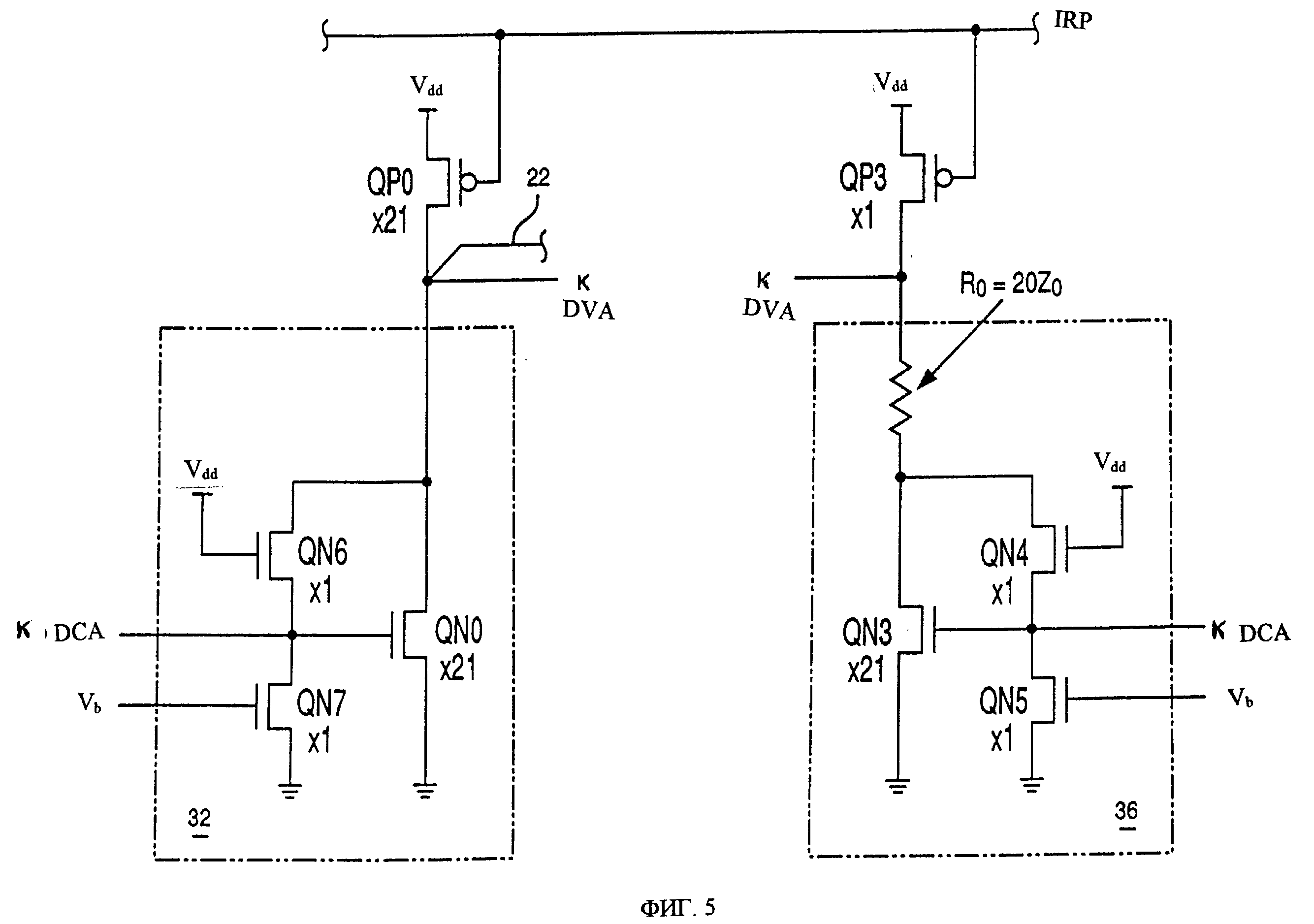

Фиг. 5 является

диаграммой схемы опорных оконечных нагрузок;

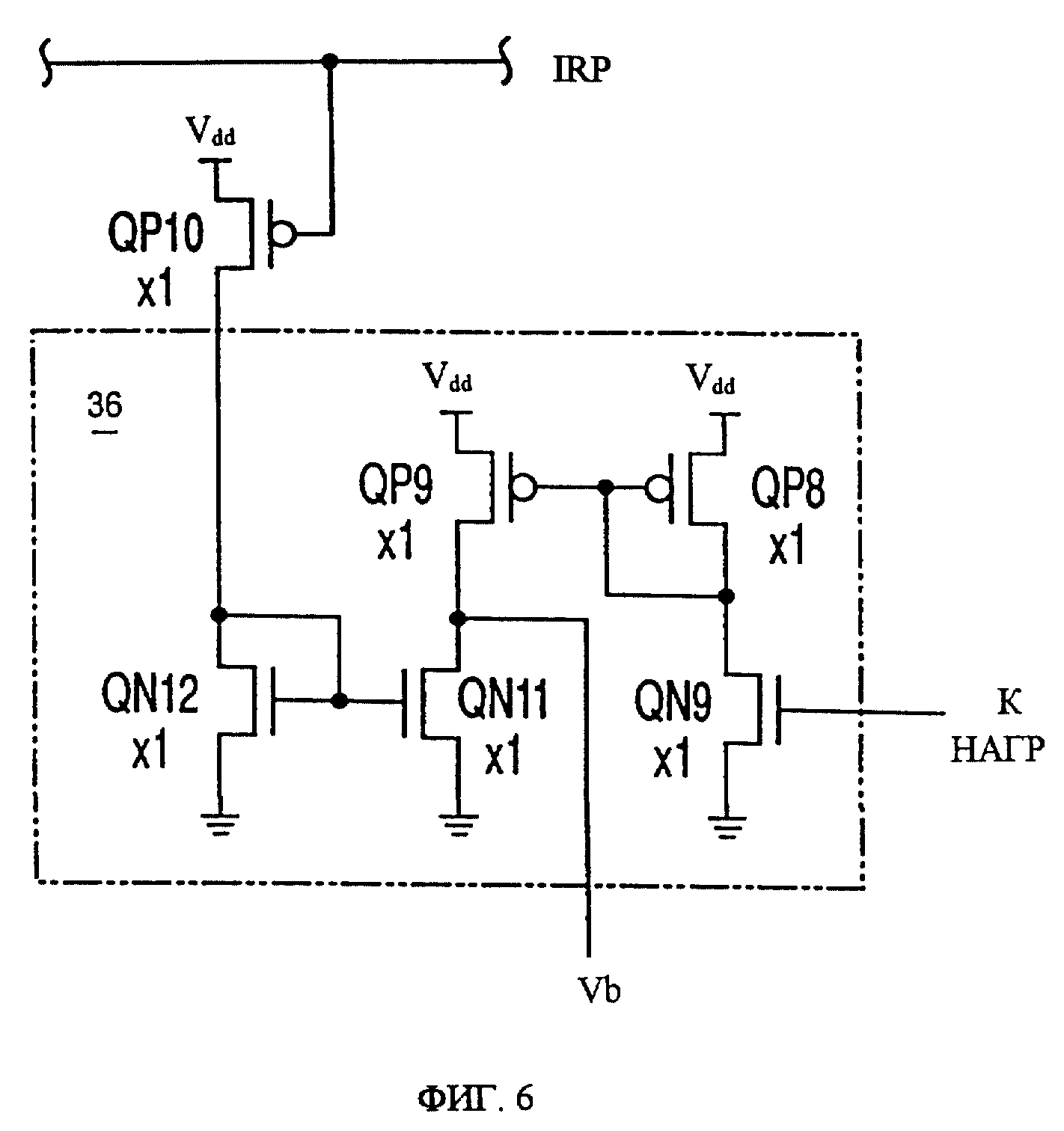

Фиг. 6 является диаграммой схемы дифференциального усилителя тока задающего генератора;

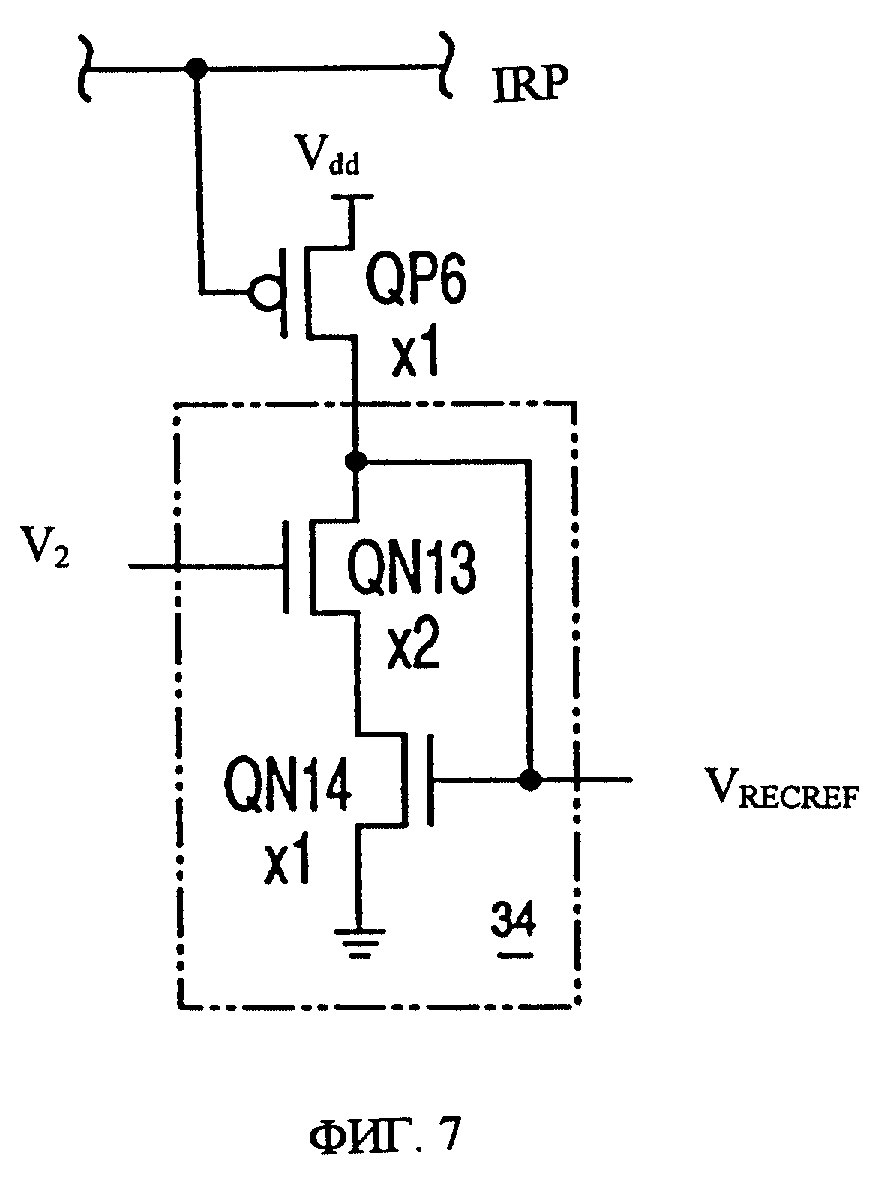

Фиг. 7 является диаграммой схемы задающего

генератора приемника задающего генератора;

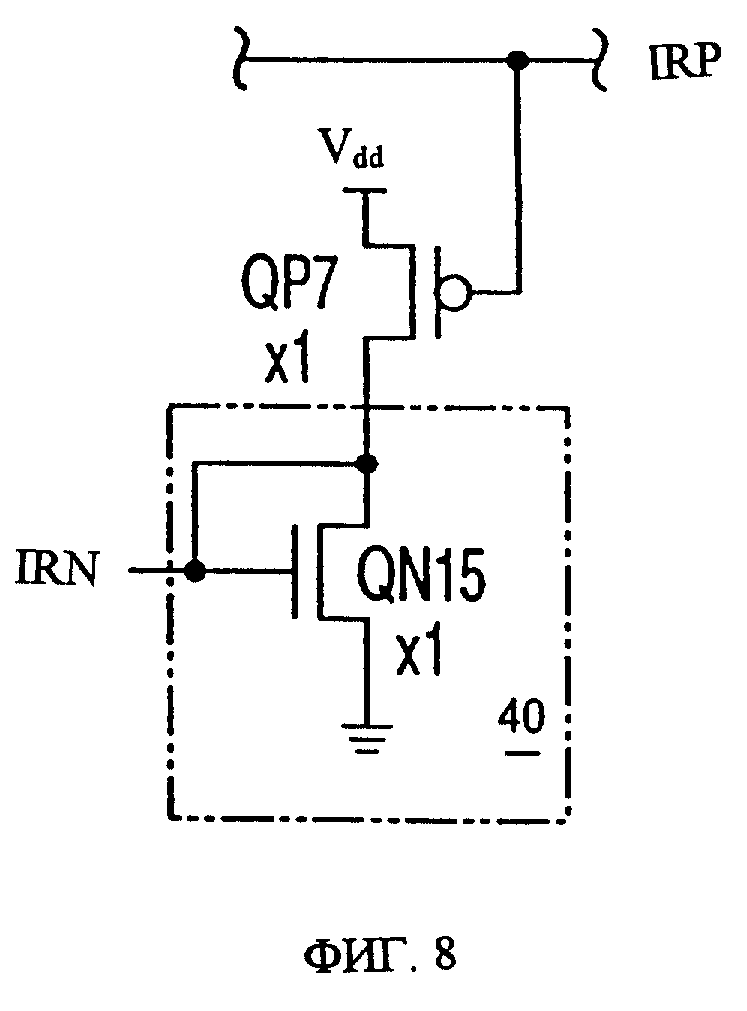

Фиг. 8 является диаграммой схемы токового зеркала задающего генератора;

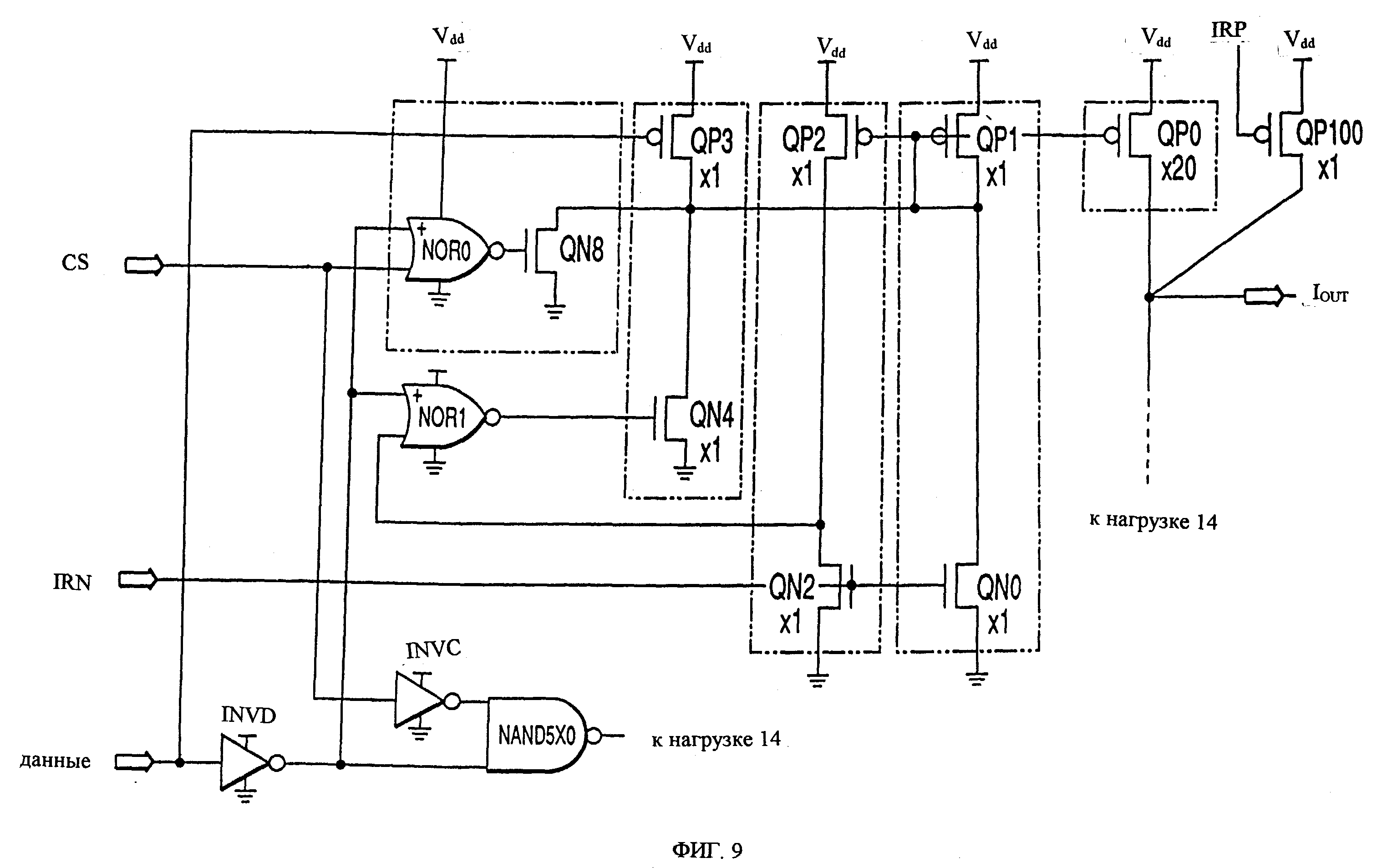

Фиг. 9 является диаграммой схемы коммутируемого источника тока;

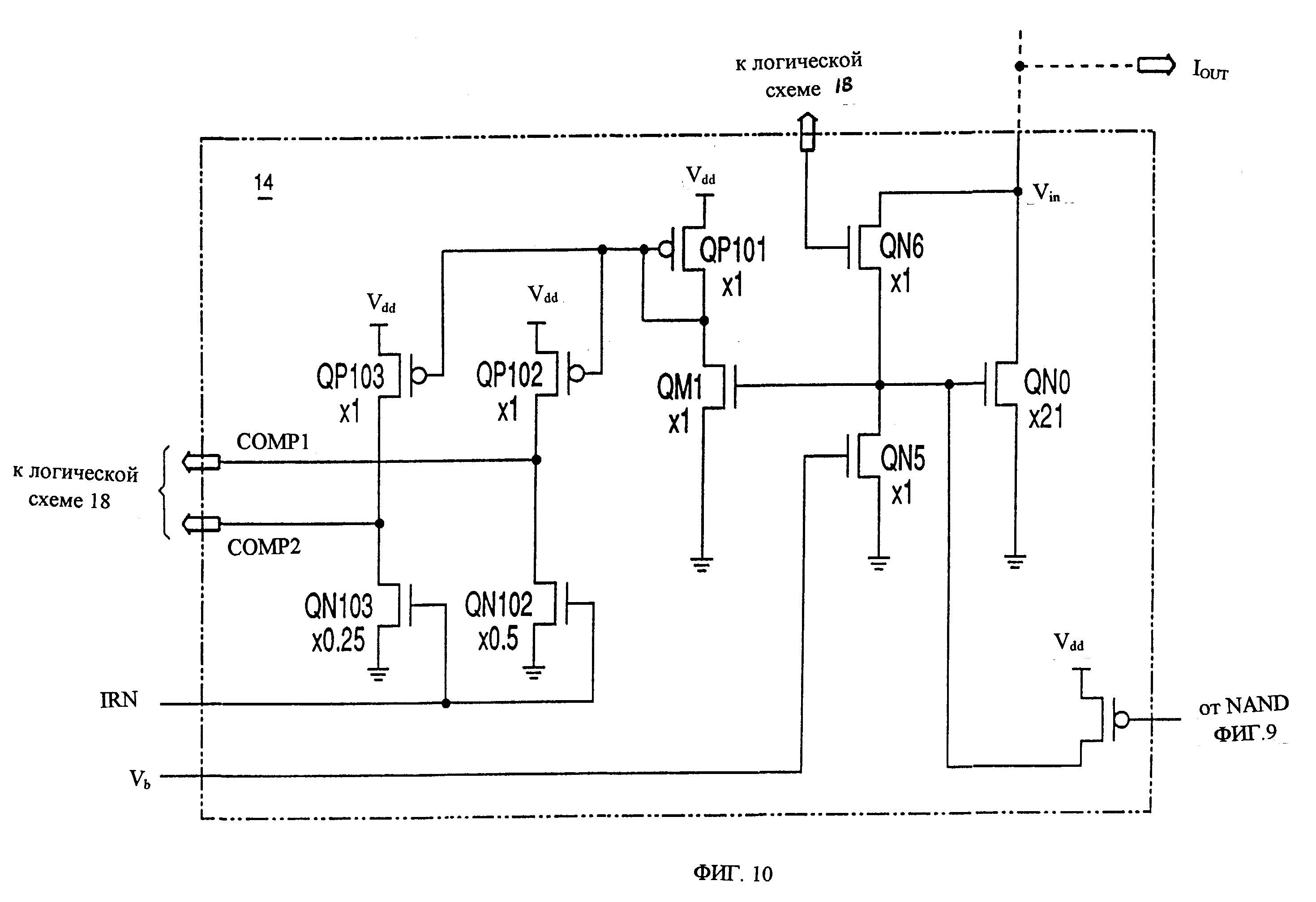

Фиг. 10 является диаграммой схемы оконечной нагрузки линии передачи; а

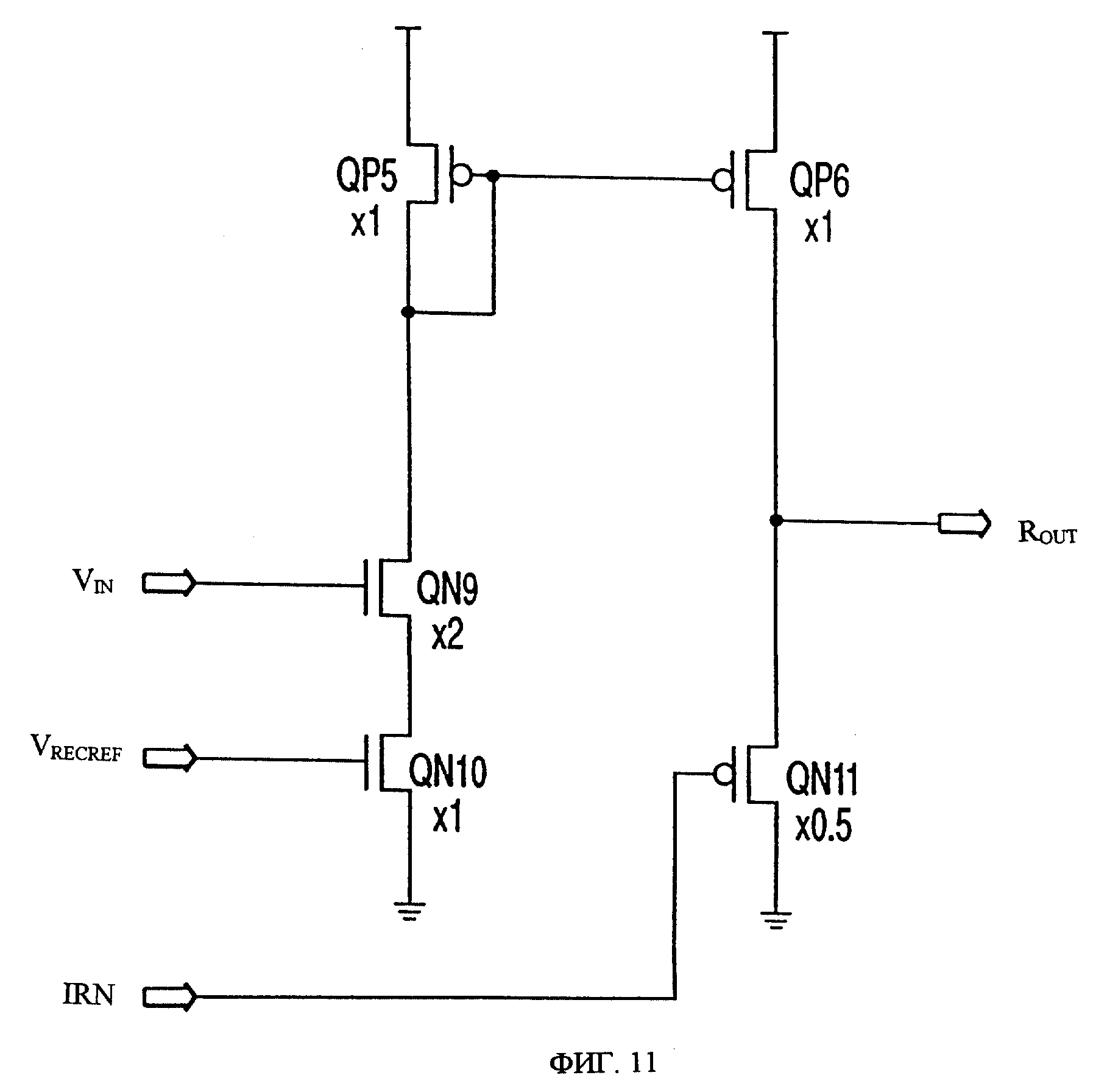

Фиг. 11 является диаграммой схемы многоотводного приемника;

ОПИСАНИЕ ПРЕДПОЧТИТЕЛЬНОГО ИСПОЛНЕНИЯ

На блок-схеме фиг.1 показан возбудитель 20A с опорным генератором 10a, вырабатывающим опорный сигнал на источник тока 12. Источник тока связан с одним из концов линии передачи 24, имеющей заранее

определенное полное сопротивление. На другом конце линии передачи 24 имеется второй возбудитель 20B со своим собственным опорным генератором 10B, вырабатывающим опорный сигнал на активную опорную

нагрузку 14. Опорные генераторы 10A и 10B взаимосвязаны опорной линией 22. Опорный сигнал опорного генератора 10A возбудителя 20A, передаваемый на источник тока 12, устанавливает определенную величину

текущего сигнала, передаваемого источником тока 12 на приемник 20 В по линии передачи 24. Опорный сигнал опорного генератора 10B приемника 20B, передаваемый на активную оконечную нагрузку 14,

устанавливает семейство полных сопротивлений для нагрузки линии передачи 24 в активной оконечной нагрузке 14 линии передачи так, чтобы для величины текущего сигнала, установленной задающим генератором

возбудителя 10A, сопротивление активной оконечной нагрузки 14 согласовывалось бы с полным сопротивлением линии передачи. Опорные генераторы 10A и 10B устанавливают семейство полных сопротивлений и

величину тока интерактивно и непрерывно, используя канал обратной связи опорной линии 22.

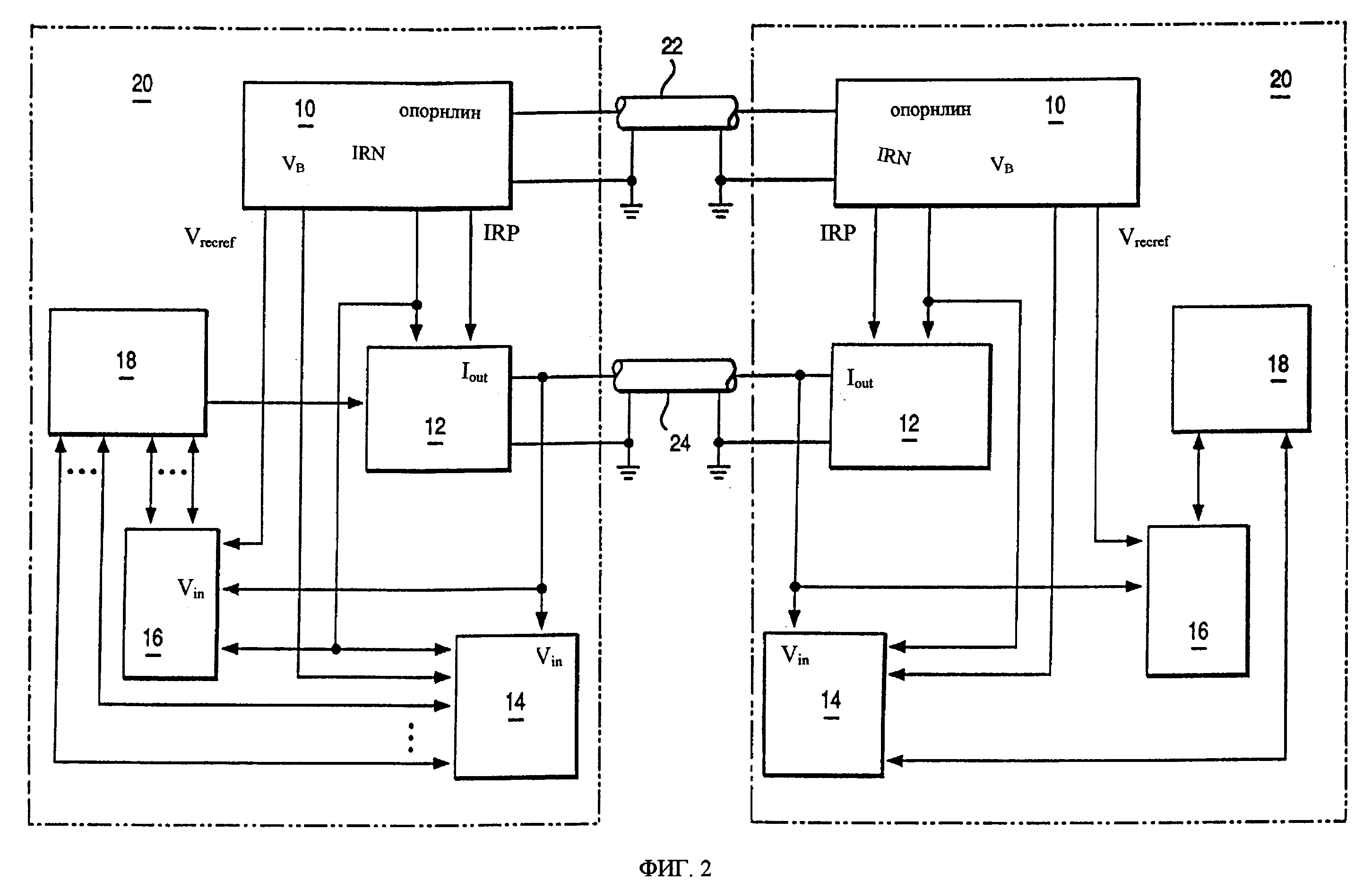

На фиг. 2 показано другое исполнение, содержащее элементы исполнения фиг. 1 и дополнительные элементы. На фиг. 2 показан задающий генератор 10, коммутируемый источник тока 12, активная оконечная нагрузка 14, далее по тексту в целях сокращения - "активная нагрузка" или "нагрузка", многоотводный приемник 16 и логическая схема 18 в первом и втором возбудителе/приемнике 20. Опорные генераторы 10 взаимосвязаны единой опорной линией 22 с заземленным экраном. Опорная линия 22 осуществляет обратную связь между возбудителями/приемниками 20 посредством общего опорного сигнала, генерируемого опорными генераторами 10. Опорный генератор 10 в возбудителе/приемнике 20 кроме этого генерирует опорные сигналы, которые передаются на коммутируемый источник тока 12, активную нагрузку 14 и приемник 16 в возбудителе/приемнике 20. Коммутируемый источник тока 12, активная нагрузка 14 и приемник 16 в устройстве возбудителя/приемника 20 связаны с концом линии передачи 24 для передачи логических сигналов между устройствами возбудителя/приемника 20. Линия передачи 24 тоже имеет заземленный экран.

Приемник 16, нагрузка 14 и коммутируемый источник тока 12 в устройстве возбудителя/приемника 20 связаны с логической схемой 18 данного устройства. Логическая схема 18 инициализирует генерацию импульсов тока, представляющих логические сигналы в коммутируемом источнике тока 12 для передачи по линии передачи 24 между устройствами возбудителя/приемника 20. Логическая схема 18 кроме этого принимает логические сигналы, обнаруженные приемником 16 или нагрузкой 14, среди сигналов, полученных по линии передачи 24 и измеренных приемником 16 или нагрузкой 14. Логическая схема 18 передает также сигналы выбора режима на источник тока 12, приемник 16 и нагрузку 14 для осуществления выбора между источником 12, вырабатывающим ток логического сигнала фиксированной величины, и током переменной величины, который согласуется с полным сопротивлением линии передачи 24, а также для переключения нагрузки 14 в устройстве 20 в состояние включено или выключено.

Опорные сигналы, генерируемые задающим генератором 10, управляют сопротивлением нагрузки 14, амплитудой передаваемых импульсов тока, представляющих логические сигналы, генерируемые источником тока 12, а также амплитудой импульсов напряжения, которые многоотводный приемник 16 или нагрузка 14 выделяют как логические сигналы из сигналов, принимаемых по линии передачи 24. Эта общая опорная линия между устройствами возбудителя/приемника 20 позволяет устройствам 20 получать общую основу для параметров, управляемых задающими генераторами 10.

Так как ток логического сигнала, передаваемый возбудителем 20, изменяется задающим генератором 10 в возбудителе 20 в соответствии с механизмом обратной связи, описанным выше, то ток сигнала или напряжение, которые измеряет приемник 16 или нагрузка 14, не имеют фиксированной величины. Поэтому приемник 16 или нагрузка 14 используют опорные сигналы, полученные от задающего генератора 10, для сравнения с сигналом, принимаемым по линии передачи 24 для определения величины логического сигнала.

Сигналы, принимаемые возбудителем/приемником 20 по линии передачи 24 могут воспроизводиться либо многоотводным приемником 16, либо детектором в нагрузке 14. Из приведенного ниже описания приемника очевидно, что приемник 16 не нагружает линию передачи 24. Приемник 16 поэтому полезен для приложений, где линией передачи 24 совместно связано много устройств возбудителя/приемника 20. Нагрузка 14 обладает тем преимуществом, что она обеспечивает такую нагрузку линии передачи 24, которая точнее согласуется с внутренним сопротивлением линии передачи 24, так что сигналы могут измеряться более точно. Так как в случае нескольких активных нагрузок 14 линии передачи 24 линия передачи 24 будет перегружена и рассогласована, то в изобретении предусмотрено средство, позволяющее посредством логической схемы 18 отключать нагрузку 14.

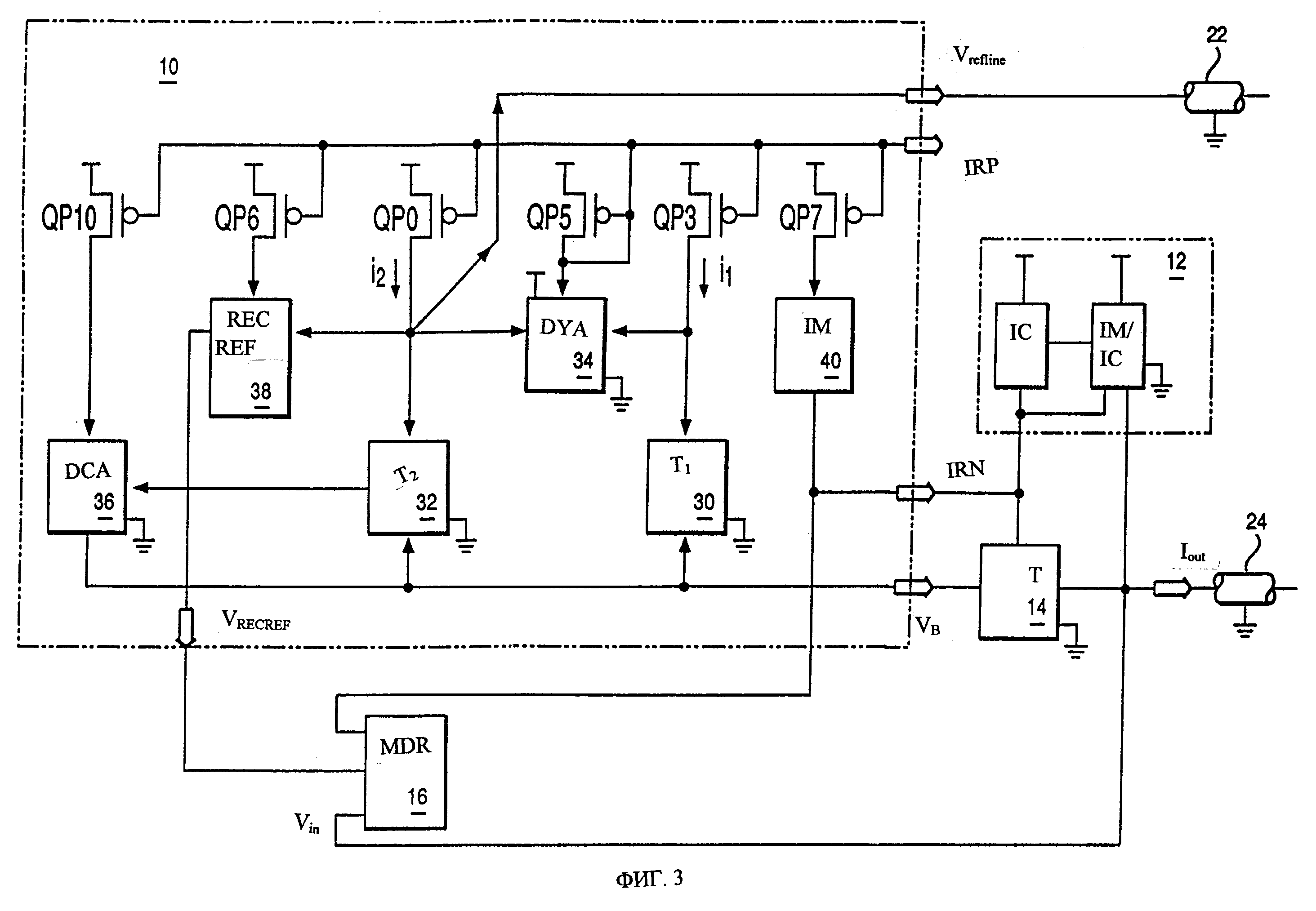

Диаграмма, фиг. 3, представляет другую, более детальную диаграмму блоков для одного из возбудителей/приемников 20, фиг. 2. Задающий генератор 10 имеет первую и вторую опорную активную нагрузку 30 и 32, дифференциальный усилитель напряжения 34, дифференциальный усилитель тока 36, генератор опорного напряжения приемника 38, а также токовое зеркало 40. Для того, чтобы сосредоточить внимание на работе устройств во время генерации, передачи и приема сигналов, на фиг. 3 опущена логическая схема 18 и линии управления логикой, показанные на фиг. 2.

Дифференциальный усилитель напряжения ("DVA") 34 принимает первый входной сигнал напряжения V1, то есть напряжение, создаваемое током i1, протекающим через первую нагрузку 30, содержащую резистор 20Z0 (фиг. 5), и второй входной сигнал напряжения V2, то есть напряжение на второй нагрузке 32, создаваемое током i2, протекающим через вторую нагрузку 32. DVA 34 передает выходной сигнал на вентили из полевых транзисторов QP0, QP3, QP5, QP6, QP7 и QP10 по шине, обозначенной как "IRP" ("шина IRP полевых транзисторов"). Выходной сигнал DVA 34 по шине IRP устанавливает определенный ток в QP5, которые возвращаются в DVA 34. Возрастание напряжения на выходе DVA вызывает уменьшение тока шины IRP полевых транзисторов. Полевые транзисторы отражают ток в QP5 по шине IRP.

Термин "отражение" применяется для хорошо согласованных полевых устройств. "Отражение" тока означает, что на затворы согласованных полевых транзисторов подается одно и то же напряжение, создающее один и тот же ток стока, или заранее определенный согласующий отмасштабированный ток стока полевых транзисторов. Хотя величина тока стока может быть неизвестна, но так как полевые транзисторы согласованы, то предполагается, что ток стока будет согласован в каждом из полевых транзисторов, независимо от того, чему равен этот ток стока.

Тот же принцип используется и для биополярных транзисторов, так что эти схемы токовых зеркал могут составляться и на основе биополярных транзисторов. Имеется некоторое отличие между полевым эффектом и биполярными устройствами, но это не препятствует использованию настоящего изобретения с биполярными транзисторами. Одно из отличий заключается в том, что биполярные транзисторы создают ток базы, в то время, как в полевых транзисторах отсутствует ток затвора. Поэтому в данном приложении желательнее использовать полевые транзисторы. Другое отличие заключается в том, что биполярные транзисторы имеют более плоскую линейную область кривой зависимости тока стока от напряжения исток-затвор. Это является преимуществом биполярных устройств.

Повышая или понижая свое выходное напряжение, DVA 34 увеличивает или уменьшает токи i1, и i2 протекающие через опорные нагрузки 30 и 32 в случае какого-либо различия между двумя входными напряжениями DVA, так что токи i1, и i2 через нагрузки 30 и 32 будут увеличивать и уменьшать напряжения на нагрузках 30 и 32. В конечном счете определенная комбинация токов i1, и i2 порождает существенно равное падение напряжения на нагрузках 30 и 32 и таким образом удовлетворяется DVA 34.

Дифференциальный усилитель тока ("DCA") 36 принимает первый входной сигнал тока от второй нагрузки. Этот входной сигнал является током, который отражает ток i2, установленный DVA 34 во второй нагрузке 32. DCA тоже получает входной сигнал тока от полевого транзистора QP10 по шине IRP. Так как QP10 согласуется с QP5 и QP3 и так как выходной сигнал DVA создает напряжение затворов для QP3, QP5 и QP10, то выходное напряжение, подаваемое от DVA 34, устанавливает ток через QP10, который совпадает с током i1.

Этот ток через QP10 сравнивается посредством DCA 36 с первым входным сигналом тока. DCA 36 вырабатывает выходной сигнал, который согласует сопротивление обеих опорных нагрузок 30 и 32, благодаря чему весь ток через QP0 протекает через вторую нагрузку 32, так что ток не протекает через опорную линию 22 и через узел между QP0 и второй нагрузкой 32.

Опорная линия 22 между опорными генераторами 10 на каждом конце линии передачи 24 создает одно и то же падение напряжения на каждой второй нагрузке 32 на каждом из концов линии передачи 24. И, как только что описывалось, DVA 34 в опорном генераторе 10 обеспечивает существенное равенство напряжения на первой нагрузке 30 задающего генератора и напряжения на его второй нагрузке 32. Таким образом, на обеих опорных нагрузках 30 и 32 в обоих опорных генераторах 10, показанных на фиг. 1, создается одно и то же падение напряжения.

Токовое зеркало 40 задающего генератора 10 подает выходное напряжение IRN на коммутируемый источник тока 12 и приемник 16 для возбуждения другого согласованного полевого транзистора для отражения тока i1.

Показанный на фиг.3 коммутируемый источник тока 12 вырабатывает ток смещения величиной i1, который устанавливается напряжением шины IRN, поступающим от задающего генератора 10, а также ток сигнала величиной 20 i1, который может быть установлен выходным напряжением IRN токового зеркала 40, поступающим от задающего генератора 10. Ток сигнала включается и выключается логической схемой 18. Фиксированный уровень тока сигнала может устанавливаться и логической схемой, не используя для этой цели задающий генератор.

Активная оконечная нагрузка 14, показанная на фиг. 3, имеет полевой транзистор (на фиг.3 не показан) в качестве нагрузки линии передачи 24. Напряжение смещения vb от DCA 36, подаваемое на активную оконечную нагрузку 14, настраивает сопротивление нагружающего полевого транзистора так, чтобы оно согласовывалось с сопротивлением линии передачи 24 при наличии конкретного тока, передаваемого соответствующим устройством 20 с другого конца линии передачи 24. Активная оконечная нагрузка 14 кроме этого имеет детектор, который сравнивает ток сигнала, протекающий в нагрузке линии передачи с опорным значением, и передает один или более выходных сигналов на логическую схему 18, указывая логическое значение тока сигнала.

Приемник (или "многоотводный приемник") 16, показанный на фиг.3, имеет первый вход, обозначенный как Vrecref, на который подается напряжение Vrecref от эталонной схемы приемника 38, второй вход, обозначенный как IRN, на который подается напряжение от токового зеркала 40 задающего генератора 10, а также третий вход, обозначенный как Vin, на который подается напряжение по линии передачи. Ток сигнала, передаваемый отправителем/получателем 20, устанавливается механизмом обратной связи отправителей/получателей так, что логический сигнал, имеющий ток, равный 20i1, соответствующий логическому значению 1, который суммируется с током смещения, равным i1, будет создавать напряжение на третьем входе Vin, равное V1, которое совпадает с напряжением на опорных оконечных нагрузках 30 и 32. Напряжение Vin будет изменяться от малой величины, создаваемой током смешения величиной i1, когда на приемник не подается сигнал тока, до большей величины Vfinal, во время приема дополнительного сигнала тока, величиной 20i1 (соответствующего логическому сигналу 1). После такого изменения Vin, с выхода приемника 16 на логическую схему 18 подается сигнал высокого уровня, указывая, что был принят логический сигнал 1.

Эталонная схема 38 генерирует опорное напряжение Vrecref, которое определенным образом соответствует напряжению передаваемого сигнала. В приемнике 16 Vrecref используется для сравнения с напряжением сигнала, измеренного приемником 16 в линии передачи 24, для определения величины логического сигнала. Эталонная схема приемника 38 принимает первый входной сигнал, который представляет собой ток, согласующийся с входным током второй опорной оконечной нагрузки 32, а также второй входной сигнал, который представляет собой напряжение V2 на второй опорной оконечной нагрузке 32 (и которое будет совпадать с V1 - напряжением на первой опорной оконечной нагрузке 30). На этих входах создается опорное напряжение Vrecref , которое используется схемой приемника 16 для установки функции передачи для логического сигнала, принятого от устройства 20 по линии передачи 24.

ДЕТАЛЬНОЕ ОПИСАНИЕ СХЕМЫ

Устройство передачи/приема настоящего изобретения может быть построено на основании различных схем, как очевидно знакомым с

данной областью техники из приведенного выше описания работы различных частей устройства. Далее следует описание схем, используемых в предпочтительных исполнениях настоящего изобретения. Описанные

здесь полевые транзисторы вообще являются согласующими полевыми транзисторами. Настоящее изобретение не ограничено относительными масштабными коэффициентами полевых транзисторов, которые приведены

далее. Для достижения результатов, описанных для передающих/принимающих устройств, могут использоваться различные масштабирующие множители. Далее предполагается, что величина напряжения питания равна

Vdd.

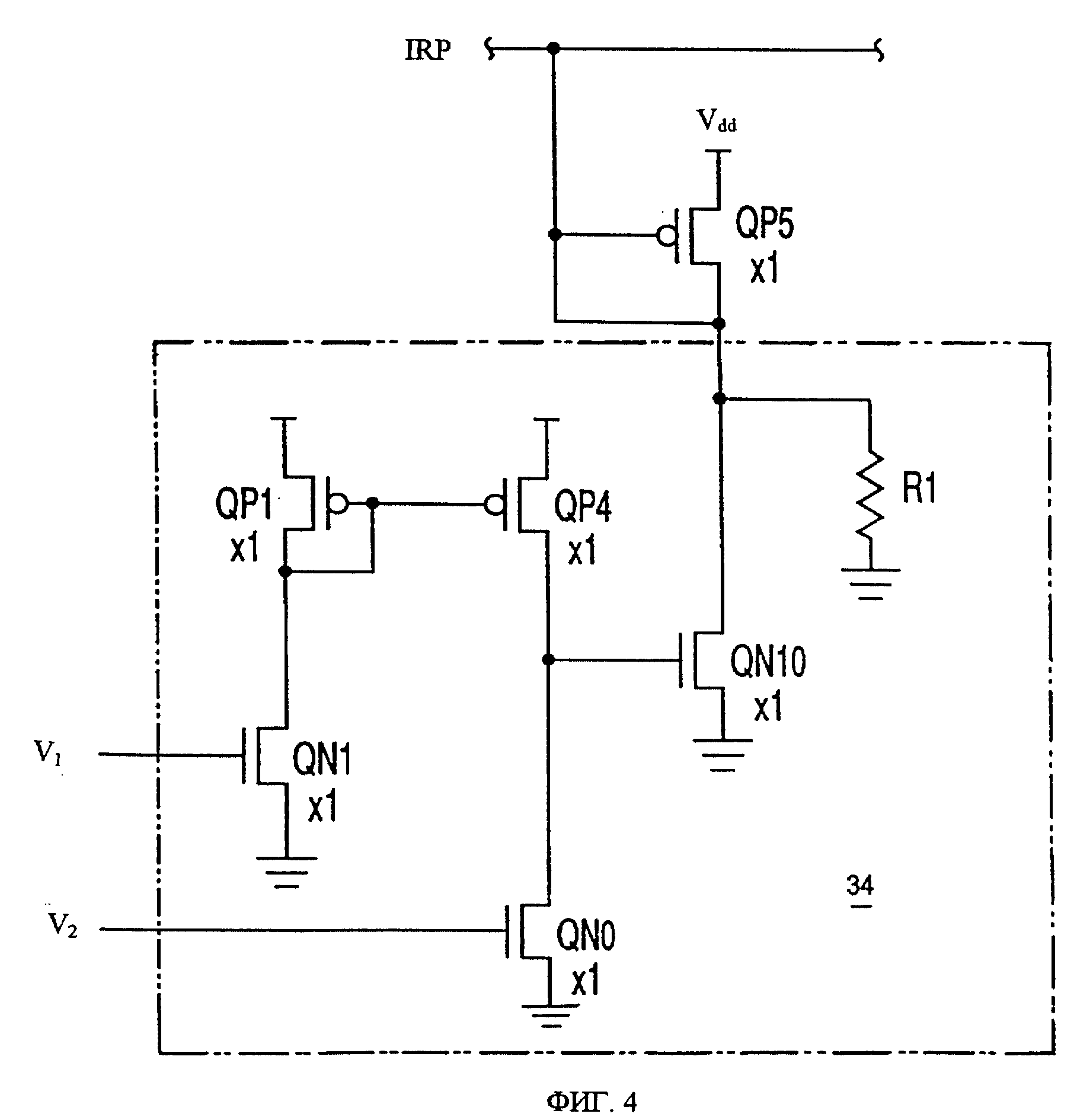

На Фиг. 4 показана схема для DVA 34 предпочтительного исполнения настоящего изобретения. Полевой транзистор QP5, у которого соединены затвор и сток, последовательно связан с полевым транзистором - QN10. Так как QN10 находится в своей линейной области (т. е. выше точки излома кривой зависимости тока стока от напряжения затвор-исток), то QN10 действует как потребитель тока, управляемый напряжением на затворе QN10 и потребляет фиксированный ток, независимо от падения напряжения сток-исток на полевом транзисторе QP5. Этот фиксированный ток, протекая через QP5, порождает напряжение затвор-исток-QP5 любой необходимой величины для тока, поддерживаемого QP5. Суммарное напряжение на затворе QP5 образует напряжение затвора для всех полевых транзисторов шины IRP. Благодаря тому, что каждый полевой транзистор шины IRP работает в своей линейной области, так как эти полевые транзисторы согласованы с QP5, результирующие токи через эти полевые транзисторы пропорциональны току, протекающему через QP5 в соответствии с их относительными масштабными коэффициентами W/L. В соответствии с фиг. 5 согласованные полевые транзисторы QP0 и QN0 имеют масштабные коэффициенты, равные 21, так что ток i2 через вторую опорную нагрузку 32 в 21 раз превышает ток i1 через первую опорную нагрузку 30. Ток величины 21i1 в нагрузке 32 представляет собой ток величины 20i1, генерируемый источником тока 12 в качестве логического сигнала 1, просуммированный с током величины i1, генерируемым источником тока 12 в качестве тока смещения.

Вновь обратимся к фиг. 4, первый и второй вход DVA 34 подключены таким образом, что на первом входе измеряется напряжение V1, первой опорной нагрузки 30, а на втором входе измеряется напряжение V2 второй опорной нагрузки 32. Первое входное напряжение подается в качестве смещения на полевой транзистор QN8, связанный с затвором полевого транзистора QN10. Второе входное напряжение является смещением полевого транзистора QN1, который отражается полевыми транзисторами QP1 и QP4. Полевой транзистор QP4 тоже связан с затвором полевого транзистора QP10. Благодаря конфигурации связей полевых транзисторов QN1, QN8, QP1, QP4 и QN10, показанных на фиг. 4, если V1 увеличивается, то напряжение затвора QN10 уменьшается, а если увеличивается V2, то напряжение затвора полевого транзистора QN10 увеличивается.

На фиг. 5 показана схема опорных нагрузок 30 и 32 предпочтительного исполнения. Нагрузки 30 и 32 одинаковы за исключением того, что первая нагрузка 30 имеет резистор R0 с сопротивлением 20Z0, где Z0 - известное сопротивление линии передачи 24, а нагрузочные полевые транзисторы в нагрузках 30 и 32 подобраны идентичными. В нагрузке 30 имеется опорный ток величиной i1, а в нагрузке 32 имеется ток величиной 21i1. Так как нагрузки 30 и 32 имеют идентичные полевые транзисторы и токи в них распределяются в пропорции 21/1, то нагрузки 30 и 32 являются статическим сопротивлением двух динамических состояний линии передачи. Источник тока 12 в возбудителе 20A (фиг. 1) представлен переменной величиной 20Z0i1 и статическим смещением, соответствующим току величины i1, в нагрузке 32. Нагрузка 14 в приемнике 20B (фиг. 1) представлена током величины 21i в нагрузке 30. Эти два динамических состояния линии передачи 24 соответствуют (1) состоянию нагрузки 14, когда ток величины i1 протекает через нагрузку 14 и (2) состоянию нагрузки 14, когда ток величины 21i протекает через нагрузку 14. Величина резистора R0 и масштабных множителей может изменяться так, что для резистора сопротивлением NZ0, между током смещения величины i1 и током сигнала величины Ni1 получается соотношение N: 1. Величина N произвольна, но как правило будет выбираться соответствующим образом, для более удобного исполнения схемы, например, N= 10, N= 10 и т.д.

Описывая вторую опорную нагрузку 32 в качестве примера предположим, что нагрузочное полевое сопротивление устанавливает нагрузочный полевой транзистор QN0. QN7 и QN6 устанавливают нагрузочный полевой транзистор QN0 во включенное и выключенное состояние, а при включенном QN0, QN7 и QN6 представляют собой делитель напряжения и устанавливают напряжение смещения для получения семейства полных нагрузочных сопротивлений сток-исток для тока, протекающего через сток нагрузочного полевого транзистора QN0. То есть для определенного стока устанавливается определенное полевое сопротивление нагрузки из семейства полных сопротивлении, установленных напряжением смещения.

На фиг. 6 показана схема DCA 36 предпочтительного исполнения. Ток i2 через QN0 второй опорной нагрузки 32 (Фиг.5), уменьшенный в 21 раз, отражается в полевом транзисторе QN9 DCA 36 путем согласования характеристик QN9 и QN0, пропорционального уменьшения W/L полевого транзистора QN9 по сравнению с полевым транзистором QN0, а также путем подключения затвора QN9 к затвору QN0. Таким образом, QN9 будет пропускать уменьшенный ток, который согласуется с током в QN0, и при условии, что нагрузка стока QN9 останется а пределах, соответствующих работе QN9 в его линейной области, QN9 будет пропускать этот ток независимо от напряжения, создаваемого этим током на нагрузке QP8.

Благодаря тому, что затвор-QP8 связан с его стоком, ток стока QN9 будет изменять напряжение исток - сток QP8 до величины, необходимой для поддержания транзистором QN8 этого тока, соответствующим образом будет изменяться и напряжение на затворе транзистора QP8. Напряжение на затворе QP8, котрый связан с затвором QP9, будет устанавливать ток через QP9. Так как QP9 согласован с QP8, то ток, протекающий через QP9, будет согласован с током, протекающим через QN9.

В это время QP10 управляется напряжением IRP, устанавливаемым DVA34, как указывалось ранее, для поддержания тока величиной i1, так как этот ток согласуется с током i2, протекающим через QP0 и уменьшенным в 21 раз благодаря согласованию характеристик QP10 и QP0, пропорциональному уменьшению W/L полевого транзистора QN9 по сравнению с полевым транзистором QN0 и подсоединению затвора QP10 к затвору QP0. Совместное соединение затвора и стока транзистора QN12 вызывает протекание через этот транзистор тока i1, поддерживаемого транзистором QP10, соответствующим образом изменяется и напряжение затвора QN12. Напряжение затвора QN12, подаваемое на затвор QN11, вызывает протекание тока i1 через QN11.

Таким образом работа DCA 16 заключается в следующем. Через полевой транзистор QN0 второй опорной нагрузки 32 протекает (1) ток i2, поддерживаемый QP0 и возбуждающий вторую опорную нагрузку 32, который суммируется с (2) током опорной линии. Кроме этого, полевой транзистор QP9 DCA управляется таким образом, чтобы поддерживать ток, согласующийся с пропорционально уменьшенным током, протекающим через полевой транзистор QN0. Полевой транзистор QN11 управляется таким образом, чтобы пропускать ток, согласущийся с пропорционально уменьшенным током, поддерживаемым QP0. Ток, поддерживаемый полевым транзистором QP9, будет равен току, протекающему через полевой транзистор QN11 только в том случае, если через полевой транзистор QN0 будет протекать весь ток, поддерживаемый полевым транзистором QP0. Для достижения этого равенства напряжение Vb на стоках QP9 и QN11 порождает сигнал обратной связи, подаваемый на затвор QN7, который создает смещение для QN0 и настраивает сопротивление QN0.

На фиг. 8 показана схема токового зеркала 40 в задающем генераторе 10 предпочтительного исполнения. Это токовое зеркало 40 подает выходное напряжение IRN на коммутируемый источник тока 12, фиг.9, и приемник 16, фиг.11, для управления другим согласованным полевым транзистором для отражения тока i1. Выходное напряжение токового зеркала 40 устанавливается выходом DVA 34, управляющим согласованным полевым транзистором QP7 по шине IRP для поддержания тока i1. Ток i1 управляет полевым транзистором QN15 для пропускания i1 и соответствующим образом изменяется напряжение затвора полевого транзистора QN15. Это напряжение затвора QN5 является выходным напряжением IRN, подаваемым от опорного токового зеркала 40. Так как QP7 является полевым транзистором р типа, а QN15 является полевым транзистором п типа, то IRP уменьшается, а IRN увеличивается по отношению к земле при увеличении i1.

На фиг. 9 показана схема коммутируемого источника тока 12 предпочтительного исполнения, который отражает ток i1, установленный опорным DVA (фиг. 4), управляемым логической схемой 18. Выходное напряжение IRN опорного токового зеркала 40 (фиг. 8) управляет полевым транзистором QN1 коммутируемого источника тока 12 для поддержания тока i1. Полевой транзистор QP1 принудительно поддерживает некоторый ток для согласования с током i1, протекающим через QN1, так как QP1 подключен таким образом, чтобы поддерживать ток, потребляемый QN1, и так как затвор QP1 связан со стоком. Так как затвор QP1 связан с затвором полевого транзистора QP0, a QP0 имеет согласованные характеристики с масштабным множителем 20х, то QP0 отражает ток, равный i1, умноженному на 20. Таким образом полевой транзистор QP0 пропускает ток величиной 20i1, представляющий логический сигнал 1. Кроме этого, полевым транзистором QP100, который управляется напряжением IRP, подаваемым от задающего генератора 10 DVA 34, создается ток смещения величиной i1.

Так как QP0 крупный, то он имеет большую заряжающуюся емкость затвор - исток, которая заряжается медленно и вызывает задержку коммутации QP1. Так как время коммутации для полевого транзистора зависит от уровня напряжения коммутации, подаваемого на затвор полевого транзистора, то один из путей быстрого заряда емкости затвор-исток и уменьшения времени коммутации заключается в непосредственном соединении затвора полевого транзистора с шиной. Обычно такой путь подходит, когда уровни логических сигналов не изменяются и устанавливаются равными полному напряжению питания. Однако в соответствии с настоящей заявкой желательно изменять уровень логического сигнала и полных сопротивлений связанных линией устройств. Поэтому для быстрой коммутации QP0 используется показанная на фиг. 9 схема, поддерживающая выбранный уровень тока, протекающий через QP0, который меньше уровня тока, возникающего под воздействием полного напряжения питания.

QN1 и QN2 имеют постоянные входные "IRN" для Vgs, получаемые от задающего генератора 10 (фиг.3). IRN устанавливает режим QN1 и QN2, обеспечивая протекание необходимого тока. Так как QP0 пропорционально отражает ток QP1, то ток в QN1 устанавливает логический уровень сигнала в QP0, когда QP1 поддерживает ток, протекающий через QN1, при условии, однако, что на затвор N0R0 будет подаваться "CS" высокого уровня, чтобы на выходе N0R0 имелся сигнал низкого уровня, благодаря чему QN8 будет отключен. Если на N0R0 будет подаваться CS, установленное на низкий уровень, то сигнал тока, поддерживаемый QP0, вместо того, чтобы быть установленным IRN, будет установлен напряжением питания на максимальное значение.

Теперь описывается режим работы с переменным током, когда на входе CS установлен высокий уровень, причем в исходном состоянии, на входе CS - высокий уровень, а источник тока - вход "данные" имеет низкий уровень, QP3 насыщен, т.е. затвор QP3 подключен непосредственно к шине так, что QP3 поддерживает ток для QN1 и отключает QP0, QP1 и QP2. При отключении QP2 Vd для QN2 имеет низкое значение. Затвор N0R1 при низком уровне Vd на входе QN2 и при высоком уровне на входе инвертируемых "данных" имеет низкий выходной уровень, отключающий QN4.

Вход данных устанавливается в высокий уровень для управления QP0 таким образом, чтобы поддерживать ток,установленный путем подачи IRN. Возникающий высокий уровень на входе данных сразу же выключает QP3 и устанавливает высокий уровень на выходе N0R1. Высокий уровень N0R1 включает и переводит в насыщение QN4. То есть с выхода N0R1 на затвор QN4 подается полное напряжение питания, что позволяет включать QN4 быстрее, чем это происходит при подаче на затвор QN4 более низкого уровня напряжения IRN. Таким образом происходит быстрое включение QP0, QP1 и QP2 через QN4 и токи стоков QP0, QP1 и QP2 начинают увеличиваться. Как только токи достигнут и превысят уровень, установленный IRN, напряжение на стоке QN2 начнет увеличиваться, устанавливая низкий уровень выхода N0R1, что приводит к отключениям QN4. Так как QN4 перестает подавать ток через QP0, QP1 и QP2, то ток перестает увеличиваться и устанавливается на уровне, установленном согласованными полевыми транзисторами QN1 и QN2 в соответствии с IRN.

После установки высокого уровня тока сигнала он может быть переключен в низкий уровень путем установки низкого уровня входа данных. Низкий уровень входа данных немедленно переводит в насыщение QP3, в результате чего быстро отключаются QP0, QP1 и QP2. После выключения QP2 понижается напряжение на входе N0R1, снимаемое со стока QN2.

Повторив приведенный выше анализ для случая, когда установлен низкий уровень входа CS, можно сделать вывод, что установка низкого уровня на входе CS вызовет переключение источника тока от шины к шине, вместо подачи выбранного уровня тока, определенного IRN. Вначале, при низком уровне на входе CS и на выходе "данных", QP3 насыщен, т.е. его затвор подключен непосредственно к шине так, что QP3 поддерживает ток для QN1 и шунтирует QP0, QP1 и QP2. При отключении QP2 устанавливается низкий уровень Vd для QN2. При низком уровне Vd QN2 и высоком уровне на входе инвертированных "данных" на затворе N0R1 имеется низкий выходной уровень, отключающий QN4. Аналогичным образом, при низком уровне на входе CS и высоком уровне на входе инвертированных "данных", на затворе N0R0 имеется низкий выходной уровень, отключающий QN8.

Вход данных устанавливается в высокий уровень для возбуждения QP0, чтобы поддерживать ток. После установки высокого уровня на входе данных QP3 немедленно отключается, что вызывает появление выского уровня на выходах N0R0 и N0R1. Высокий уровень на выходе N0R1 включает и переводит в насыщение QN4. Высокий уровень на выходе N0R0 включает и переводит в насыщение QN8. Таким образом QP0, QP1 и QP2 быстро включаются через QN4 и QN8 и токи стоков QP0, QP1 и QP2 начинают увеличиваться. После того, как эти токи достигнут и превысят уровень, установленный IRN, увеличенное напряжение стока QN2 устанавливает низкий уровень выхода N0R1, отключая QN4. В результате работы с переменным уровнем тока сигнала, описанном выше, когда QN4 прекращает подавать ток через QP0, QP1 и QP2, ток прекращает увеличиваться и фиксируется на уровне, установленном QN1 и QN2, который определяется IRN. Однако в режиме переключения от одного граничного значения к другому граничному значению на QN8 не воздействует уровень тока, установленный IRN. Вместо этого, в режиме переключения от одного граничного значения к другому граничному значению QN8 остается во включенном состоянии до тех пор, пока на входе данных имеется высокий уровень, так что ток через QP0, QP1 и QP2 продолжает увеличиваться до уровня, установленного напряжением питания.

Если установлен высокий уровень тока сигнала, то его можно переключить в низкий уровень, установив низкий уровень входа данных. Низкий уровень на входе данных немедленно устанавливает низкий уровень выхода N0R0, отключая QN8. Кроме этого, низкий уровень на входе данных немедленно переводит QP3 в насыщение, в результате чего происходит быстрое QP0, QP1 и QP2. После выключения QP2 уменьшается напряжение на входе N0R1, подаваемое со стока QN2.

На фиг. 10 показана схема активной нагрузки 14 предпочтительного исполнения. Активная нагрузка 14 приемника 20B (фиг. 1) имеет полевой транзистор QN0, который согласован с полевым транзистором QP0 источника тока 12 возбудителя 20A (фиг. 1) для приема тока, поддерживаемого QP0 возбудителя 20A, при условии, что сток и затвор QN0 взаимосвязаны через включенный QN6. Полевой транзистор QN5 связан с затвором полевого транзистора QN0 и принимает напряжение его затвора с выхода Vd DCA 36 (фиг. 6). Как и в опорных нагрузках 30 и 32 фиг. 5, Vb смещает сопротивление нагрузочного полевого транзистора. В случае активной нагрузки 14, фиг. 10, нагрузочным полевым транзистором является полевой транзистор QN0.

В детектирующей части нагрузки 14 затвор полевого транзистора QM1 связан с затвором нагрузочного полевого транзистора QN0 для отражения тока через QN0. Полевой транзистор QP101 подключен для поддержания любого тока, возникающего и протекающего через QM1, а напряжение затвора QP101 подается на полевые транзисторы QP102 и QP103 так, что QP102 и QP103 тоже отражают ток в соответствии с их калибровкой. QP103 и QN103 выбраны таким образом, что когда ток величины 21i1/2 протекает через QN0 нагрузки, то QP103 перевозбуждает QN103 так, что напряжение стока QN103 увеличивается. Это напряжение стока QN103 используется в качестве выходного сигнала для индикации, что получен логический сигнал 1. QP102 и QN102 выбраны таким образом, что когда через нагрузочный полевой транзистор QN0 протекает ток величиной 21i1, что соответствует приему двух логических сигналов 1 одновременно, то QP102 перевозбуждает QN102 и напряжение стока QN102 повышается. Напряжение стока QN102 используется в качестве выходного сигнала для индикации, что было получено одновременно два логических сигнала 1.

На фиг. 7 показана схема эталонной схемы приемника 38 предпочтительного исполнения. Эталонная схема приемника 38

принимает ток, установленный на выходе DVA 34, который подается на затвор согласованного полевого транзистора QP6 так, что входной ток irr эталонной схемы согласуется с входным током i2 второй опорной нагрузки 32. Ток irr возбуждает полевой транзистор QN13, в то время как напряжение V2 на второй опорной нагрузке 32, подаваемое в качестве второго входного

сигнала на DVA 34, подается на затвор QN13. Ток irr, возбуждающий полевой транзистор QN13, протекает через полевой транзистор QN14, образующий каскадную пару с QN13. Затвор полевого

транзистора QN14 связан со стоком QN13 и подает опорное напряжение Vrecref, подача этого напряжения на затвор одного из полевых транзисторов каскадной пары необходима для поддержания тока

irr, при этом напряжение на затворе другого полевого транзистора этой пары равно напряжению V2 на второй опорной нагрузке 32. Напряжение Vrecref используется схемой

приемника 16 для установки передаточной функции QN9 и QN10 так, что подача напряжения на Vin будет вызывать прохождение известного тока через QP5. Величина этого тока равна i1

при напряжении линии передачи 24, равном Nfinal. Полевые транзисторы QP6 и QN11 образуют компаратор тока, который генерирует напряжение величиной Vdd, указывающее на логический

сигнал 1, когда ток через QP5 превышает

величину i1/2. QN11 выбирается таким образом, что потребляет ток, величиной i1/2, при напряжении IRN.

На фиг.11 показана схема многоотводного приемника 16. Многоотводный приемник 16 имеет пару полевых транзисторов QN9 и QN10, которые согласованы с полевыми транзисторами QN13 и QN14 эталонной схемы приемника 38. Опорное напряжение Vrecref, которое генерируется эталонной схемой приемника 38, подается на затвор полевого транзистора QN10 в приемнике 16. Напряжение Vin линии передачи 24 подается на затвор полевого транзистора QN9 приемника 16. Так как полевые транзисторы QN9 и QN10 согласуются с каскадной парой QN13 и QN14 эталонной схемы 16 приемника, а на затвор QN10 подается напряжение Vrecref, то через полевые транзисторы QN9 и QN10 будет протекать ток, который будет согласован с током i1, когда подаваемое на затвор QN9 напряжение будет совпадать с напряжением V1, подаваемым на опорные нагрузки 30 и 32. Ток сигнала, передаваемый передатчиком/приемником 20, устанавливается механизмами обратной связи передатчика/приемника так, чтобы логический сигнал, имеющий ток величиной 20i1, соответствующий логической величине 1 после суммирования с током смещения, равным i1, генерировал напряжение, равное V1 на затворе QN9.

Полевой транзистор QP5 связан последовательно с полевыми транзисторами QN9 и QN10, причем затвор QP5 связан с его стоком так, чтобы QP5 поддерживал ток, протекающий через QN9 и QN10. Полевой транзистор QP6 подключается для отражения тока, поддерживаемого полевым транзистором QP5. Полевой транзистор QP6 включен последовательно с полевым транзистором QN11, который возбуждается напряжением, подаваемым от токового зеркала 40 задающего генератора 10. Полевой транзистор QN11 настроен таким образом, что пропускает ток величиной 0,5i1, когда на его затвор подается напряжение от токового зеркала 40, соответствующее току величиной i1 токового зеркала 40.

Напряжение Vin будет изменяться от малой величины, создаваемой током смещения величиной i1, когда на приемник 16 не посылается никакого сигнала тока, до большей величины (обозначаемой как Vfinal) во время приема дополнительного сигнала тока, величиной 20i1 (который соответствует логическому сигналу 1). После такого изменения Vin QP6 будет перевозбуждать QN11 и напряжение в узле между QP6 и QN11 будет повышаться до Vdd. Это напряжение в узле является выходным сигналом Rout и передает сигнал детектора на логическую схему 18, который указывает, что приемником 16 был принят логический сигнал 1.

Описание работы

Работа выполняется следующим образом. DVA 34 (фиг. 3) устанавливает опорные токи величиной i1 через первую опорную нагрузку 30 и, если нагрузка

14 линии передачи включена, то в качестве смещения ток через нагрузку 14 линии передачи, которая нагружает полевой транзистор QN0 (фиг.10). Кроме этого DVA 34 устанавливает ток величиной 20i1, в качестве тока сигнала через источник тока 12 - полевой транзистор QP0 (фиг. 9). Этот ток 20i1 + i2 подается в линию передачи 24 и, если нагрузка 14 включена, то этот

ток распределяется между нагрузкой 14 и линией передачи 24. DVA 34, кроме этого, устанавливает ток величиной 21i1 в узле, между второй опорной нагрузкой 32 и опорной линией 22. Величина

тока i1 устанавливается DVA 34 таким образом, чтобы токи в опорных нагрузках 30 и 32 создавали существенно равное падение напряжения.

Далее, DCA 36 (фиг. 3) создает напряжение смещения Vd, подаваемое на опорные нагрузки 30 и 32 и на нагрузку линии передачи 14, которая влияет на крутизну (и сопротивление) нагрузочных полевых транзисторов QN0 и QN3 в первой и второй опорных нагрузках и на крутизну нагрузочного полевого транзистора QN0 в нагрузке 14 линии передачи (фиг. 10) так, чтобы ток, величиной 21i1, установленный DVA, протекал бы через вторую опорную нагрузку 32 (т.е. ток не протекает через опорную линию 22).

DVA 34 и DCA 36 взаимодействуют таким образом, что величины тока, установленные DVA 34, влияют на ток,

протекающий через опорные нагрузки 30 и 32, на который реагирует DCA 36, в то время как напряжение смещения, установленное DCA 36, влияет на напряжение, создаваемое на опорных нагрузках 30 и 32, на

которое реагирует DVA 34. Взаимодействие DVA 34 и DCA 36 совместно с характеристиками согласования полевых транзисторов устройств 20 и с выбором коэффициентов масштабирования для полевых транзисторов

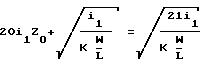

и резисторов в устройствах 20, создает равновесие, когда опорный ток i1 и крутизна полевого транзистора QN0 удовлетворяет равенству:

что приводит к согласованию сопротивления линии передачи, 24 с сопротивлением нагрузки 14 линии передачи нагружающей полевой транзистор QN0 током величиной 21i1, протекающим через полевой транзистор QN0.

Ток смещения переменной величины может поддерживаться QP100 после установки посредством IRP, подаваемым от задающего генератора 10 (фиг.3). После включения ток сигнала переменного уровня, протекая через QP0, суммируется с током смещения в узле приемопередатчика/линии (обозначенном как Iout на фиг. 9). Со ссылкой на фиг.1 отмечается, что если не имеется действующей нагрузки 14 линии передачи в передающем устройстве 20A с источником тока 12, то весь суммарный ток передается по линии 24 на принимающее устройство 20B. Со ссылкой на фиг. 2 отмечается, что если имеется включенная нагрузка 14 линии передачи, то суммарный ток устройства передачи 20A делится, часть тока передается по линии, а остальная часть передается в нагрузку 14 (не показана) устройства передачи 20A. Независимо от того, используется ли нагрузка 14 линии передачи в каком-либо конкретном исполнении настоящего изобретения или включена ли какая-либо из таких нагрузок 14, многоотводный приемник 16 может быть включен в каждый из приемопередатчиков, так как приемник 16 связан с линией посредством затвора своего полевого транзистора QN9 и, следовательно, не нагружает линию.

Посредством нагрузочных полевых транзисторов QN0 в нагрузках 14 в каждом из двух устройств 20A и 20B линии 24, а также посредством нагрузочных полевых транзисторов, нагрузки которых согласованы с сопротивлением линии и с уровнями током передачи, ток в передающем устройстве 20 распределяется равномерно между нагрузкой 14 и линией 24. Таким образом, когда половина передаваемого тока передается от первого устройства 20A на второе устройство 20B, то вторая половина тока перелается на собственную нагрузку 14 первого устройства 20A, если же половина передаваемого тока передается от второго устройства 20B на первое устройство 20A, то вторая половина тока передается на нагрузку 14 второго устройства 20B, когда оба устройства 20A и 20B передают ток одинакового определенного уровня равный, скажем, 21i1, то нагрузка 14 устройств будет принимать тот же уровень 21i1. Когда только одно устройство 20 передает ток 21i, то каждое из устройств 20 принимает 0,5•21i1, независимо от того, какое из устройств 20 передает. И, разумеется, если ни одно из устройств 20 не передает ток сигнала, то только ток смещения, равный 0,5i1 принимается каждым из устройств 20.

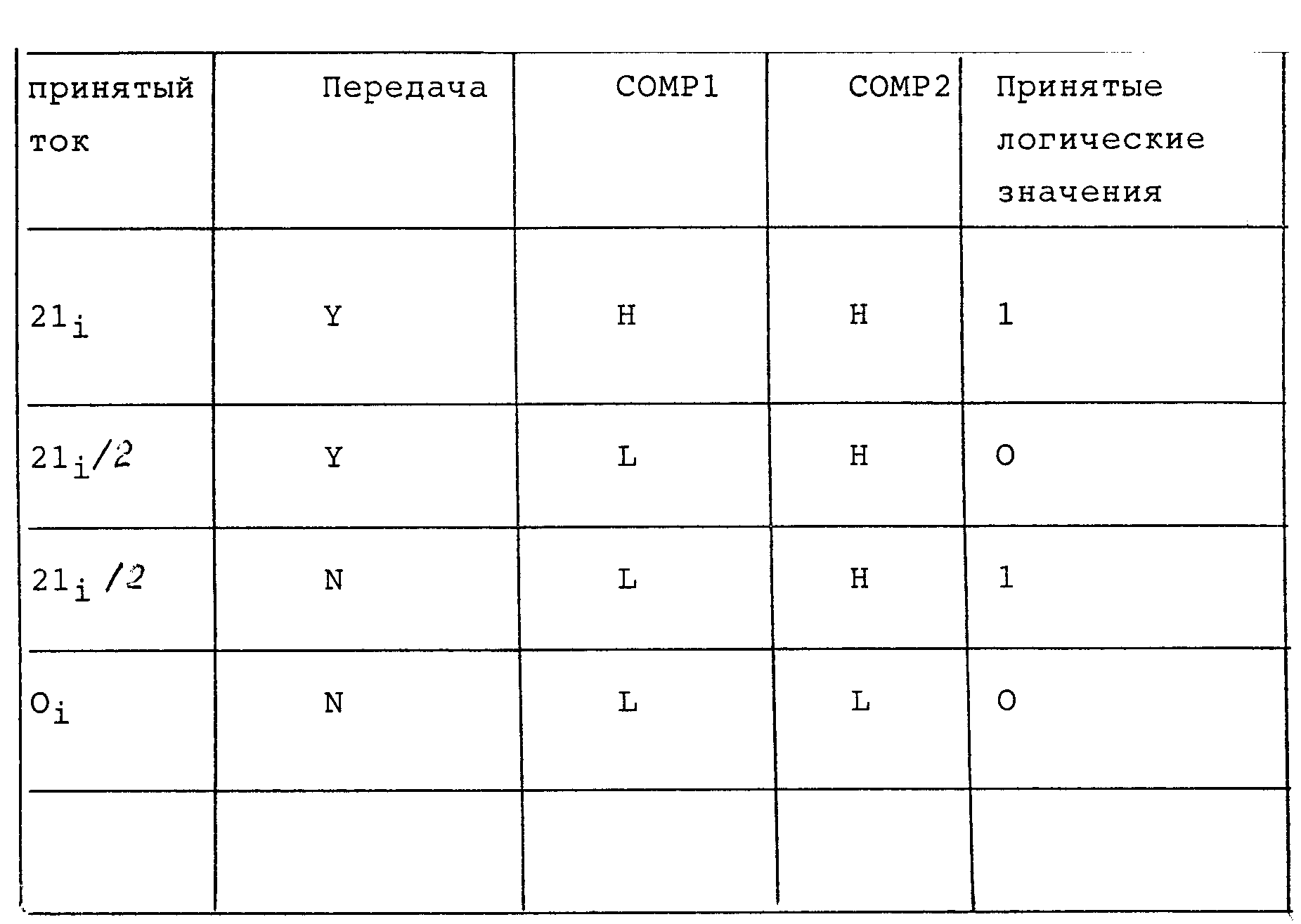

Со ссылкой на фиг. 10 отмечается, что нагрузочный полевой транзистор QN0 нагрузки линии передачи 14 подключается и отключается от схемы логическим сигналом, подаваемым на затвор QN6. После отключения QN6 (под управлением логической схемы 18 фиг. 2) отключается и QN0, разгружая линию и блокируя нагрузку 14. После включения QN6 включается нагрузка 14 и QN0 образует сток с переменным сопротивлением, регулируемый напряжением смешения Vb, подаваемым на затвор QN5 для поддержания тока, подаваемого на узел приемопередатчика/линии ("Iout" на фиг.10). Ток, принимаемый QN0, отражается на полевой транзистор QM1 и преобразуется в логические данные схемой детектора, сформированной полевыми транзисторами QM1, QP101, QN102, QP103 и QN103 в соответствии с приведенным описанием так, что оба выхода COMP1 и COMP2 имеют высокий уровень, когда принимается ток уровня 21i, высокий уровень имеет один из выходов, когда принимается ток уровня 0,5•21i, и ни один из выходов не имеет высокий уровень, когда ток не поступает. Эти данные могут объединяться с данными от приниающего устройства, указывая, передало ли устройство часть принятого сигнала для определения, какая часть принятого сигнала была передана от внешнего источника. Это может быть описано посредством таблицы.

Как показывает приведенный выше анализ, в соответствии с настоящим изобретением два приемопередатчика 20 с подключенными нагрузками 14 линии передачи могут одновременно передавать и принимать данные, передаваемые между этой парой приемопередатчиков 20 по одной линии 24. И, кроме этого, в соответствии с настоящим изобретением сопротивление нагрузки первого приемопередатчика 20 и уровень тока Tout логического сигнала могут управляться для согласования с полным сопротивлением линии 24, с нагрузочным полным сопротивлением и с текущим уровнем логики второго приемопередатчика 20 посредством только одной опорной линии 22. И независимо от того, имеется ли нагрузка 14 линии передачи, режим работы источника тока 12 настоящего изобретения может выбираться как режим возбуждения тока, изменяющегося от одного предельного уровня до другого предельного уровня, или как режим с током переменного уровня. В переменном режиме может быть согласован уровень сигнала нескольких приемопередатчиков 20 посредством одной опорной линии 22 между устройствами 20.

Реферат

Способ и устройство для передачи и приема предназначены для передачи и приема логических сигналов в ответ на ввод внешних цифровых данных и сигналов управления. Технический результат - повышение точности приема сигнала. Эталонная схема, передающая первый и второй опорные сигналы, является общей для схем генерации и приема сигнала. Схема генерации сигнала имеет источник сигнала, связанный с линией передачи для генерации цифрового сигнала с переменным уровнем, а также схему согласования и коммутации опорного уровня (схема RLA /S), которая реагирует на ввод цифровых данных и первый опорный сигнал. Схема RLA/S связана с источником сигнала для выбора уровня цифрового сигнала переменного уровня и для подачи сигнала коммутации. Выход источника сигнала согласуется и коммутируется таким образом, что источник сигнала генерирует цифровой сигнал в линию передачи, после чего вводятся цифровые данные с выбранным уровнем выходного сигнала. Схема приема сигнала имеет связанную с линией передачи схему с переменным входным сопротивлением, которая реагирует на второй опорный сигнал для приема цифровых сигналов с переменным уровнем от линии передачи. Она, кроме этого, содержит схему детектирования, подключенную для приема цифровых сигналов переменного уровня от схемы с переменным входным полным сопротивлением. Схема детектирования реагирует на первый опорный сигнал и детектирует логические состояния цифровых сигналов переменного уровня в соответствии с первым опорным сигналом. Кроме этого, схема детектирования преобразует продетектированные логические состояния в соответствующие сигналы заранее определенных выходных уровней. 4 с. и 10 з. п.ф-лы, 11 ил., 1 табл.

Комментарии