Устройство селекции большего из двоичных чисел - RU2676891C1

Код документа: RU2676891C1

Чертежи

Описание

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны устройства селекции большего из двоичных чисел (см., например, патент РФ 2363034, кл. G06F 7/02, 2009 г.), выполняющие селекцию большего из двух n-разрядных двоичных чисел, задаваемых двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных устройств селекции большего из двоичных чисел, относятся ограниченные функциональные возможности, обусловленные тем, что не допускается обработка трех n-разрядных двоичных чисел, задаваемых двоичными сигналами.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятое за прототип устройство селекции большего из двоичных чисел (патент РФ 2300135, кл. G06F 7/02, 2007 г.), которое содержит 2×(n-2) элементов 2И и выполняет селекцию большего из двух n-разрядных двоичных чисел, задаваемых двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности, обусловленные тем, что не допускается обработка трех n-разрядных двоичных чисел, задаваемых двоичными сигналами.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения селекции большего из трех n-разрядных двоичных чисел, задаваемых двоичными сигналами.

Указанный технический результат при осуществлении изобретения достигается тем, что в устройстве селекции большего из двоичных чисел, содержащем 2×(n-2) элементов 2И, особенность заключается в том, что в него дополнительно введены n+1 элементов 2И, n элементов 3ИЛИ, n-1 элементов НЕ и 3×(n-1) мажоритарных элементов, причем все элементы сгруппированы в n групп так, что k-я (

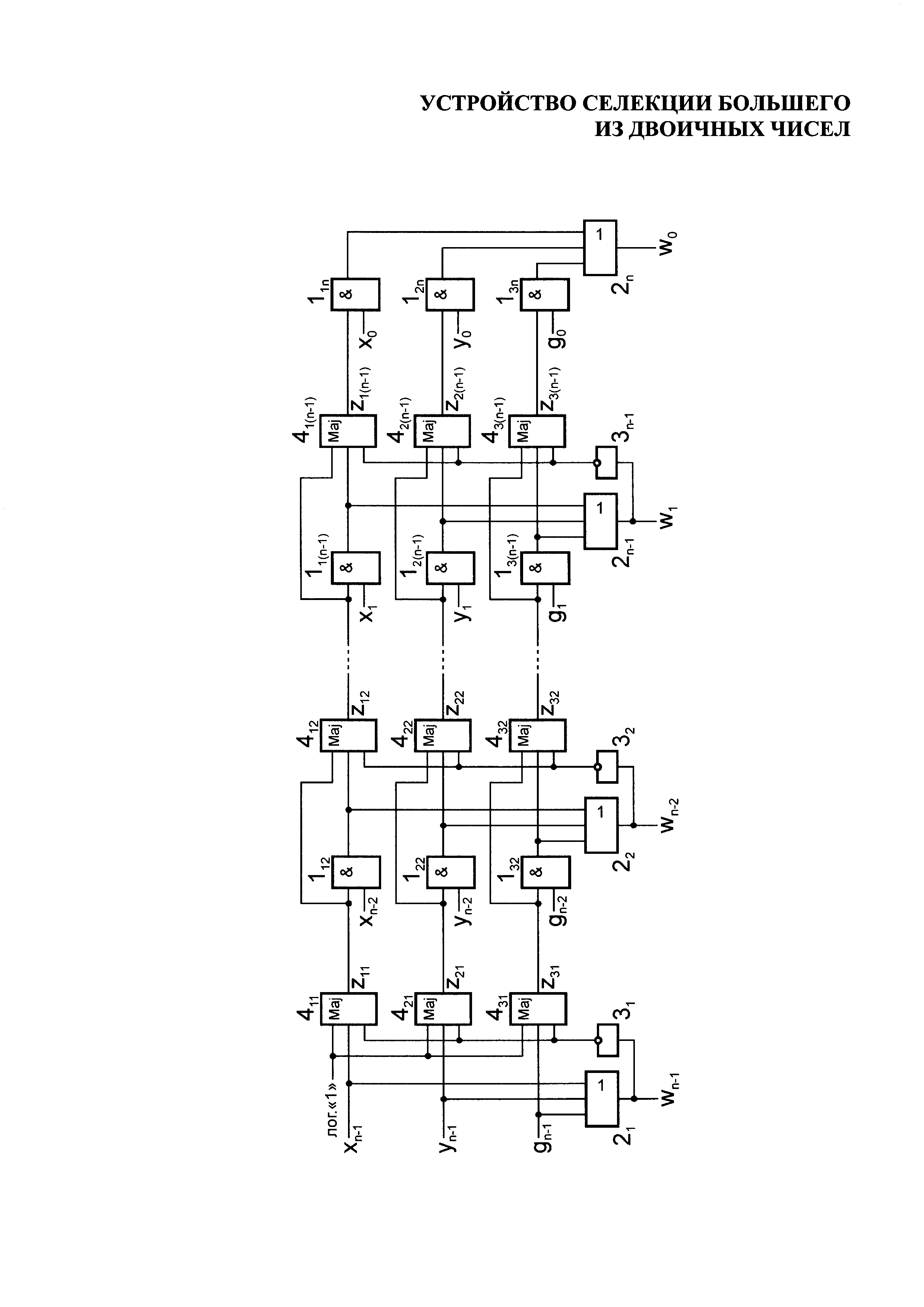

На фиг. представлена схема предлагаемого устройства селекции большего из двоичных чисел.

Устройство селекции большего из двоичных чисел содержит элементы 2И 112,…,13n, элементы 3ИЛИ 21,…,2n, элементы НЕ 31,…,3n-1, мажоритарные элементы 411,…,43(n-1), причем все элементы сгруппированы в n групп так, что k-я (

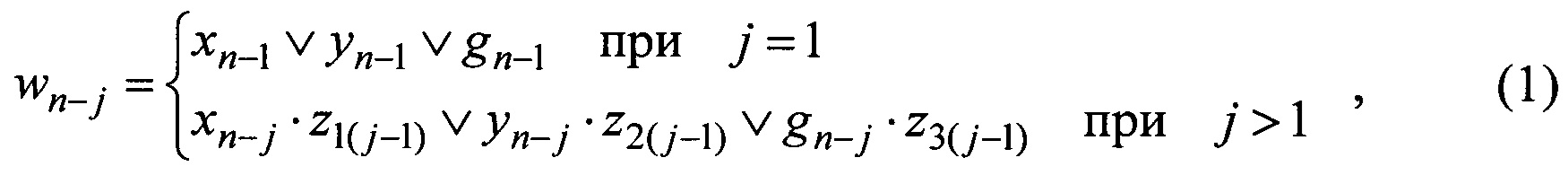

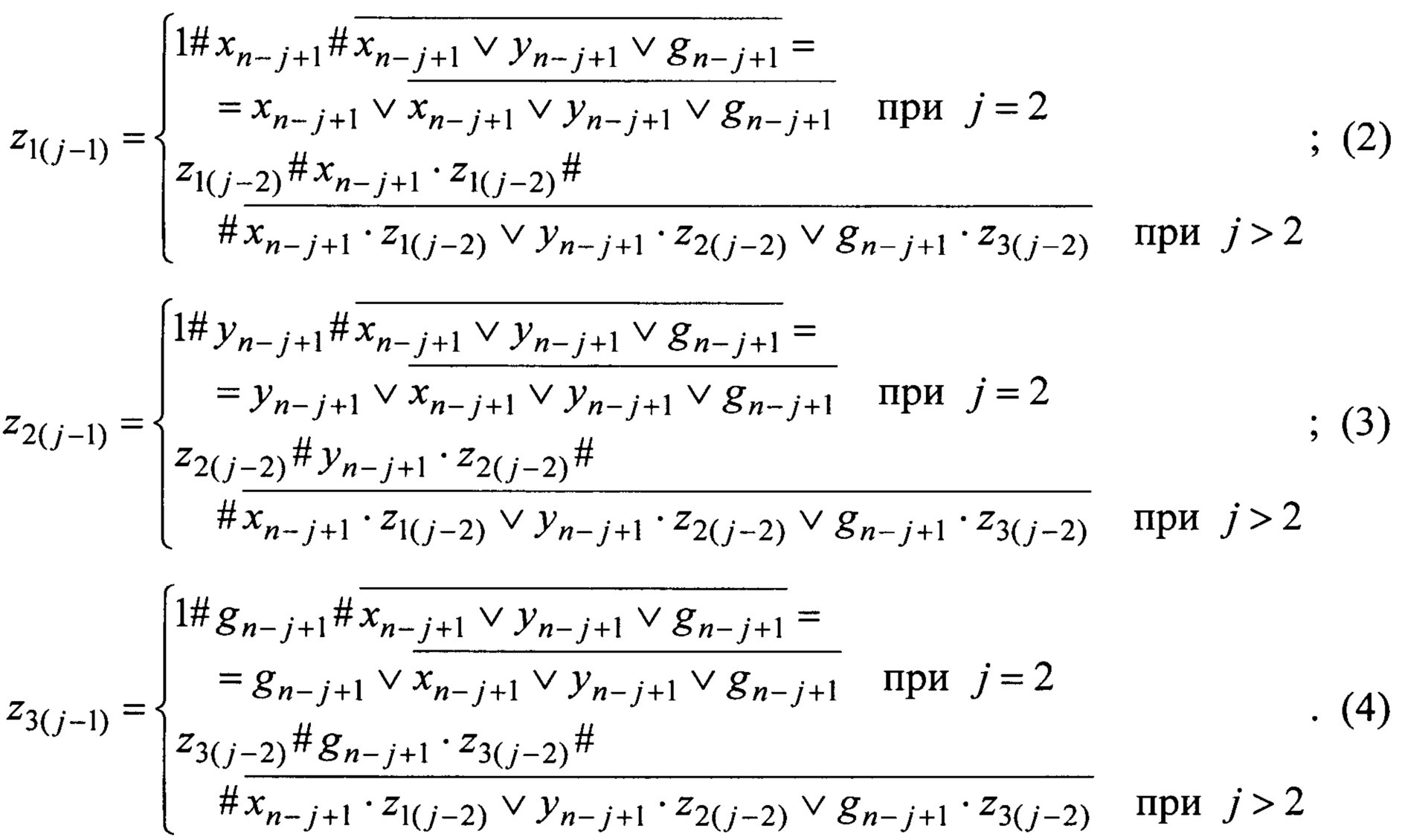

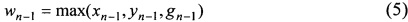

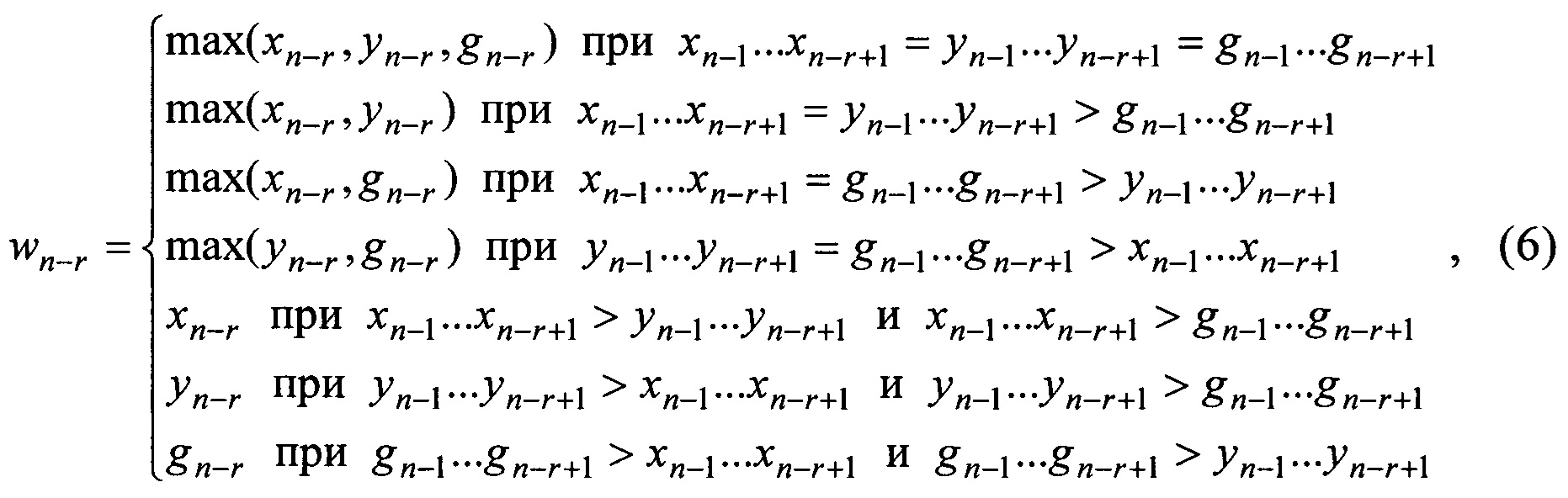

Работа предлагаемого устройства селекции большего из двоичных чисел осуществляется следующим образом. На его первый,…,n-й, (n+1)-й,…, (2×n)-й, (2×n+1)-й,…, (3×n)-й входы подаются соответственно произвольные двоичные сигналы xn-1,…,х0∈{0,1}, yn-1,…,у0∈{0,1}, gn-1,…,g0∈{0,1}, которые задают подлежащие обработке n-разрядные двоичные числа xn-1…х0, yn-1…у0, gn-1…g0 (xn-1, yn-1, gn-1 и х0, y0, g0 определяют значения старших и младших разрядов соответственно). Тогда сигнал на j-ом (

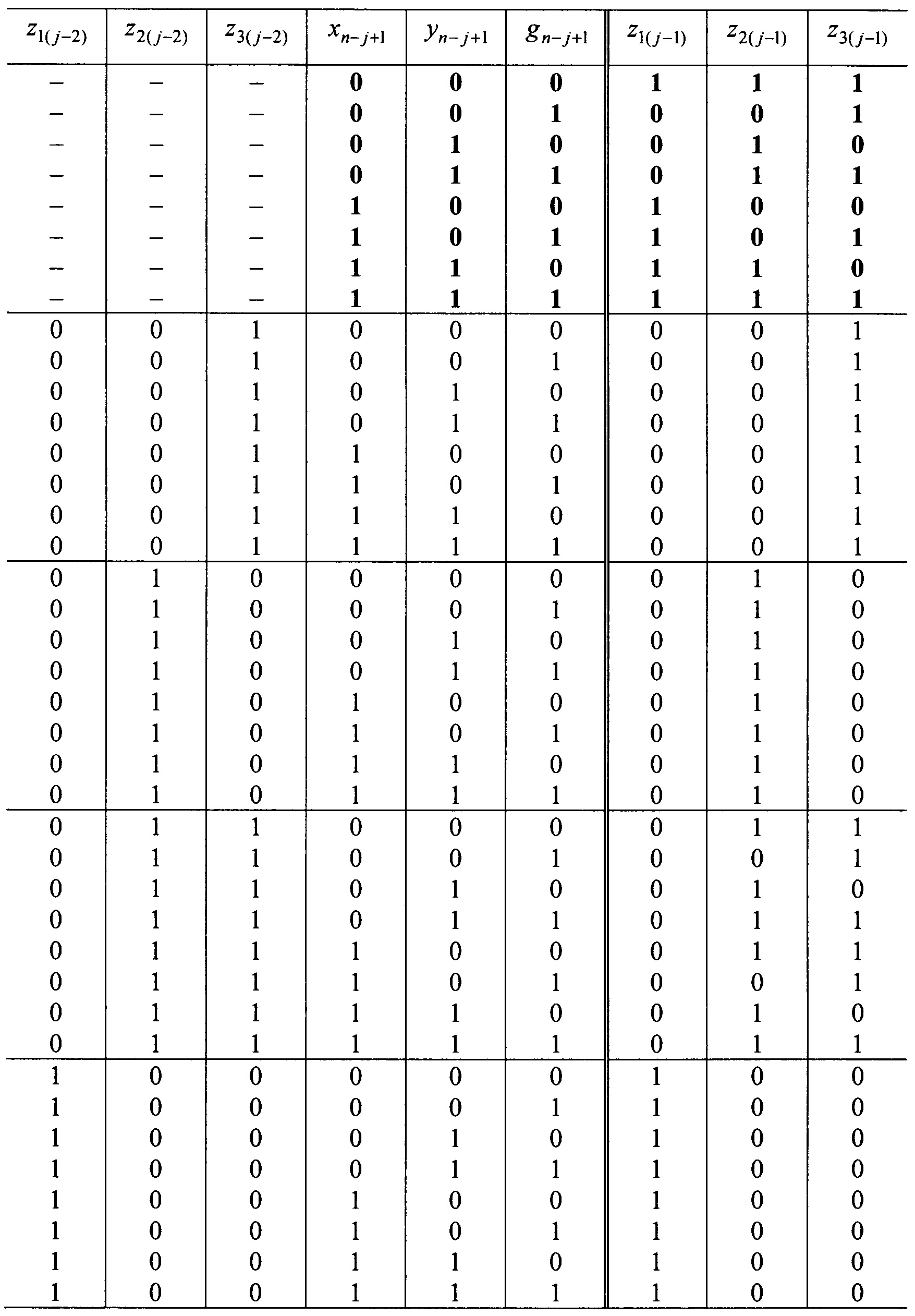

где

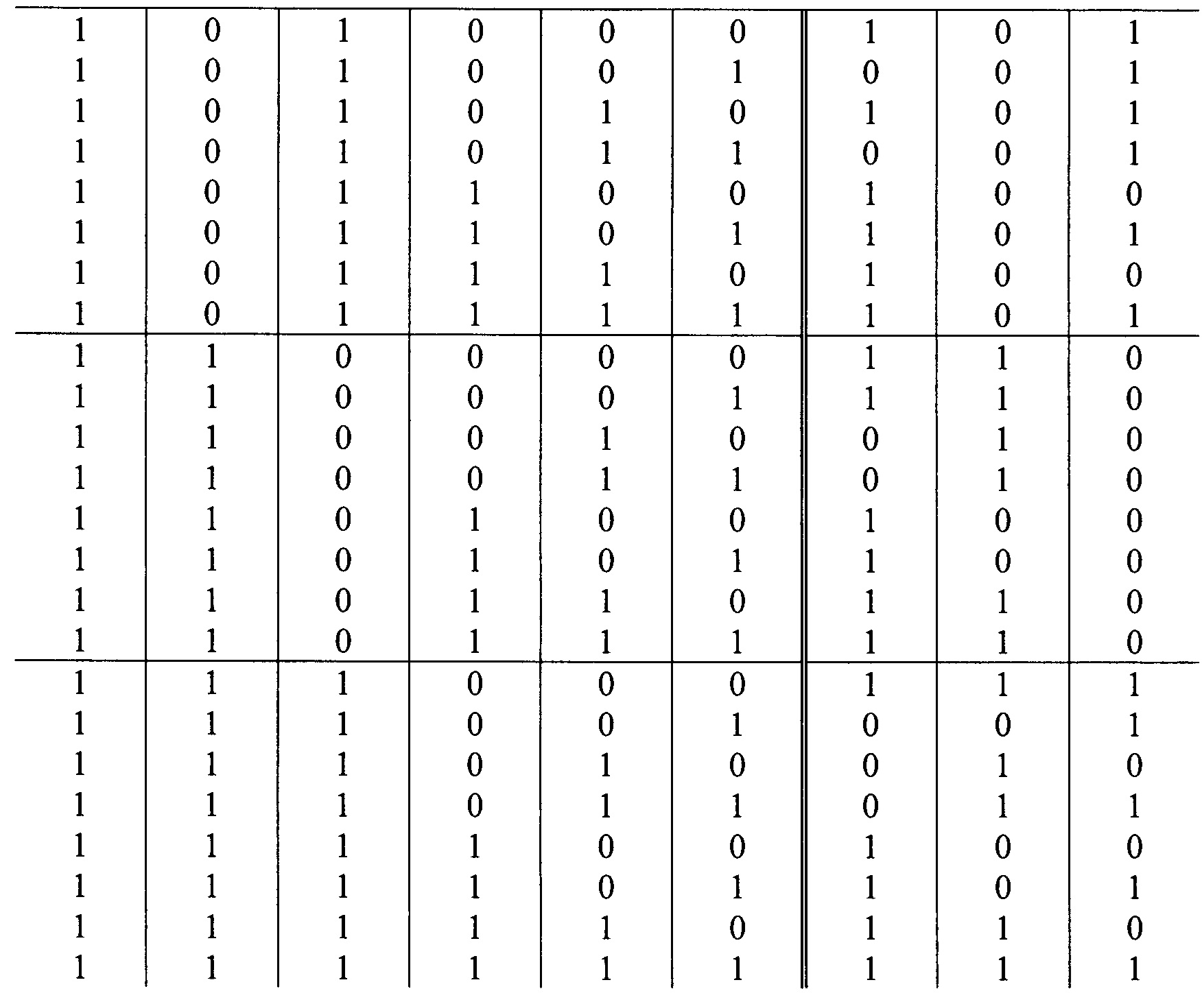

Здесь ∨, ⋅,⎯, # есть символы операций ИЛИ, И, НЕ, Maj. Отметим, что сигнал на выходе трехвходового мажоритарного элемента равен 1 (0) только тогда, когда на двух или на трех входах этого элемента действуют сигналы, равные 1 (0). В представленной ниже таблице приведены значения реализуемых выражениями (2), (3), (4) функций на всех возможных наборах значений их аргументов. Жирным в таблице выделены значения функций и их аргументов при j=2.

Анализ данных, приведенных в таблице, позволяет заключить, что:

1) если xn-1=yn-1=gn-1 либо xn-1>yn-1=gn-1 либо yn-1>xn-1=gn-1 либо gn-1>xn-1=yn-1 либо xn-1=yn-1>gn-1 либо xn-1=gn-1>yn-1 либо yn-1=gn-1>xn-1, то соответственно z11=z21=z31=1 либо z11=1, z21=z31=0 либо z21=1, z11=z31=0 либо z31=1, z11=z21=0 либо z11=z21=1, z31=0 либо z11=z31=1, z21=0 либо z21=z31=1, z11=0;

2) если z1(j-2)=z2(j-2)=z3(j-2)=1 и xn-j+1=yn-j+1=gn-j+1, либо z1(j-2)=z2(j-2)=z3(j-2)=1 и xn-j+1>yn-j+1=gn-j+1 либо z1(j-2)=z2(j-2)=z3(j-2)=1 и yn-j+1>xn-j+1=gn-j+1 либо z1(j-2)=z2(j-2)=z3(j-2)=1 и gn-j+1>xn-j+1=yn-j+1 либо z1(j-2=z2(j-2)=z3(j-2)=1 и xn-j+1=yn-j+1>gn-j+1 либо z1(j-2)=z2(j-2)=z3(j-2)=1 и xn-j+1=gn-j+1>yn-j+1 либо z1(j-2)=z2(j-2)=z3(j-2)=1 и yn-j+1=gn-j+1>xn-j+1, то соответственно z1(j-1)=z2(j-1)=z3(j-1)=1 либо z1(j-1)=1, z2(j-1)=z3(j-l)=0 либо z2(j-1)=1, z1(j-1)=z3(j-1)=0 либо z3(j-1)=1, z1(j-1)=z2(j-1)=0 либо z1(j-1)=z2(j-1)=1, z3(j-1)=0 либо z1(j-1)=z3(j-1)=1, z2(j-1)=0 либо z2(j-1)=z3(j-1)=1, z1(j-1)=0;

3) если z1(j-2)=1 и z2(j-2)=z3(j-2)=0 либо z2(j-2)=1 и z1(j-2)=z3(j-2)=0 либо z3(j-2)=1 и z1(j-2)=z2(j-2)=0, то соответственно z1(j-1)=1, z2(j-1)=z3(j-1)=0 либо z2(j-1), z1(j-1)=z3(j-1)=0 либо z3(j-1)=1, z1(j-1)=z2(j-1)=0;

4) если z1(j-2)=z2(j-2)=1, z3(j-2)=0 и xn-j+1=yn-j+1 либо z1(j-2)=z2(j-2)=1, z3(j-2)=0 и xn-j+1>yn-j+1 либо z1(j-2)=z2(j-2)=1, z3(j-2)=0 и xn-j+1

5) если z1(j-2)=z3(j-2)=1, z2(j-2)=0 и xn-j+1=gn-j+1 либо z1(j-2)=z3(j-2)=1, z2(j-2)=0 и xn-j+1>gn-j+1 либо z1(j-2)=z3(j-2)=1, z2(j-2)=0 и xn-j+1

6) если z2(j-2)=z3(j-2)=1, z1(j-2)=0 и yn-j+1=gn-j+1 либо z2(j-2)=z3(j-2)=1, z1(j-2)=0 и yn-j+1>gn-j+1 либо z2(j-2)=z3(j-2)=1, z1(j-2)=0 и yn-j+1

Таким образом, на первом и r-ом (

и

где xn-1…xn-r+1, yn-1…yn-r+1, gn-1…gn-r+1 - фрагменты n-разрядных двоичных чисел xn-1…x0, yn-1…y0, gn-1…g0. Следовательно, с учетом (5), (6) имеем wn-1…w0=max(xn-1…x0, yn-1…y0, gn-1…g0), где wn-1…w0 есть n-разрядное двоичное число, задаваемое двоичными сигналами w0,…,wn-1∈{0,1} (wn-1 и w0 определяют значения старшего и младшего разрядов соответственно).

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство обладает более широкими по сравнению с прототипом функциональными возможностями, так как обеспечивает селекцию большего из трех n-разрядных двоичных чисел, задаваемых двоичными сигналами.

Реферат

Изобретение относится к области вычислительной техники и может быть использовано для селекции большего из n-разрядных двоичных чисел. Техническим результатом является обеспечение обработки трех n-разрядных двоичных чисел. Устройство содержит 3×(n-1) элементов 2И, n элементов 3ИЛИ, n-1 элементов НЕ и 3×(n-1) мажоритарных элементов. 1 ил., 1 табл.

Формула

Комментарии