Мажоритарный модуль для отказоустойчивых систем - RU2626347C1

Код документа: RU2626347C1

Чертежи

Описание

Изобретение относится к вычислительной технике и может быть использовано для построения отказоустойчивых средств автоматики, функциональных узлов систем управления и др.

Известны мажоритарные модули (например, патент РФ 2300137, кл. G06F 7/38, 2007 г.), которые содержат элементы 2И, трехвходовые мажоритарные элементы и реализуют мажоритарную функцию n аргументов.

К причине, препятствующей достижению указанного ниже технического результата при использовании известного мажоритарного модуля для реализации мажоритарной функции n аргументов - входных двоичных сигналов, относятся ограниченные функциональные возможности, т.к. устройство не может быть использовано в асинхронных схемах, высокая сложность и низкое быстродействие, т.к. устройство содержит 2×m+N-1 трехвходовых мажоритарных элементов, где m=0,5×(n+1),

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип мажоритарный модуль (патент РФ 2533079, МПК H03K 19/23, G06F 7/57, 2014 г.), который содержит n информационных входов (n=2m+1, m=1, 2, …), первый выход устройства, n элементов И, два элемента ИЛИ, причем i-ый информационный вход соединен с первым входом i-го элемента И, (i=1, …, n), реализующий мажоритарную функцию n аргументов.

К причине, препятствующей достижению указанного ниже технического результата при использовании известного мажоритарного модуля для реализации мажоритарной функции n аргументов - входных двоичных сигналов, относятся ограниченные функциональные возможности, т.к. устройство не может быть использовано в асинхронных схемах, высокая сложность и низкое быстродействие, т.к. все мажоритарные элементы сгруппированы в три группы так, что в первой и второй группах содержится по m-1 (m=0,5×(n+1), n≠1 есть любое нечетное натуральное число) мажоритарных элементов, а в каждой группе выход предыдущего мажоритарного элемента соединен с вторым входом последующего мажоритарного элемента, все элементы 2И сгруппированы в

Техническим результатом изобретения является расширение функциональных возможностей устройства за счет возможности его использования как в синхронных, так и в асинхронных дискретных схемах, уменьшение сложности устройства и повышение его быстродействия.

Указанный технический результат при осуществлении изобретения достигается тем, что в мажоритарный модуль для отказоустойчивых систем, содержащий n информационных входов (n=2m+1, m=1, 2, …), первый выход устройства, n элементов И, два элемента ИЛИ, причем i-ый информационный вход соединен с первым входом i-го элемента И, (i=1, …, n), дополнительно введены вход запуска, второй выход устройства, n+1 элементов задержки, регистр сдвига, причем выход i-го элемента И соединен через i-ый элемент задержки с i-ым входом первого элемента ИЛИ, (i=1, …, n), вход запуска соединен со вторыми входами всех элементов И, с первым тактовым входом и управляющим входом регистра сдвига и через (n+1)-ый элемент задержки с первым входом второго элемента ИЛИ, выход первого элемента ИЛИ соединен со вторым тактовым входом регистра сдвига, (m+2)-ой выход регистра сдвига соединен с первым выходом устройства и вторым входом второго элемента ИЛИ, выход второго элемента ИЛИ соединен со вторым выходом устройства, первый вход данных регистра сдвига соединен с шиной «логическая 1», j-ый вход данных регистра сдвига соединен с шиной «логический 0», j=2, …, m+2.

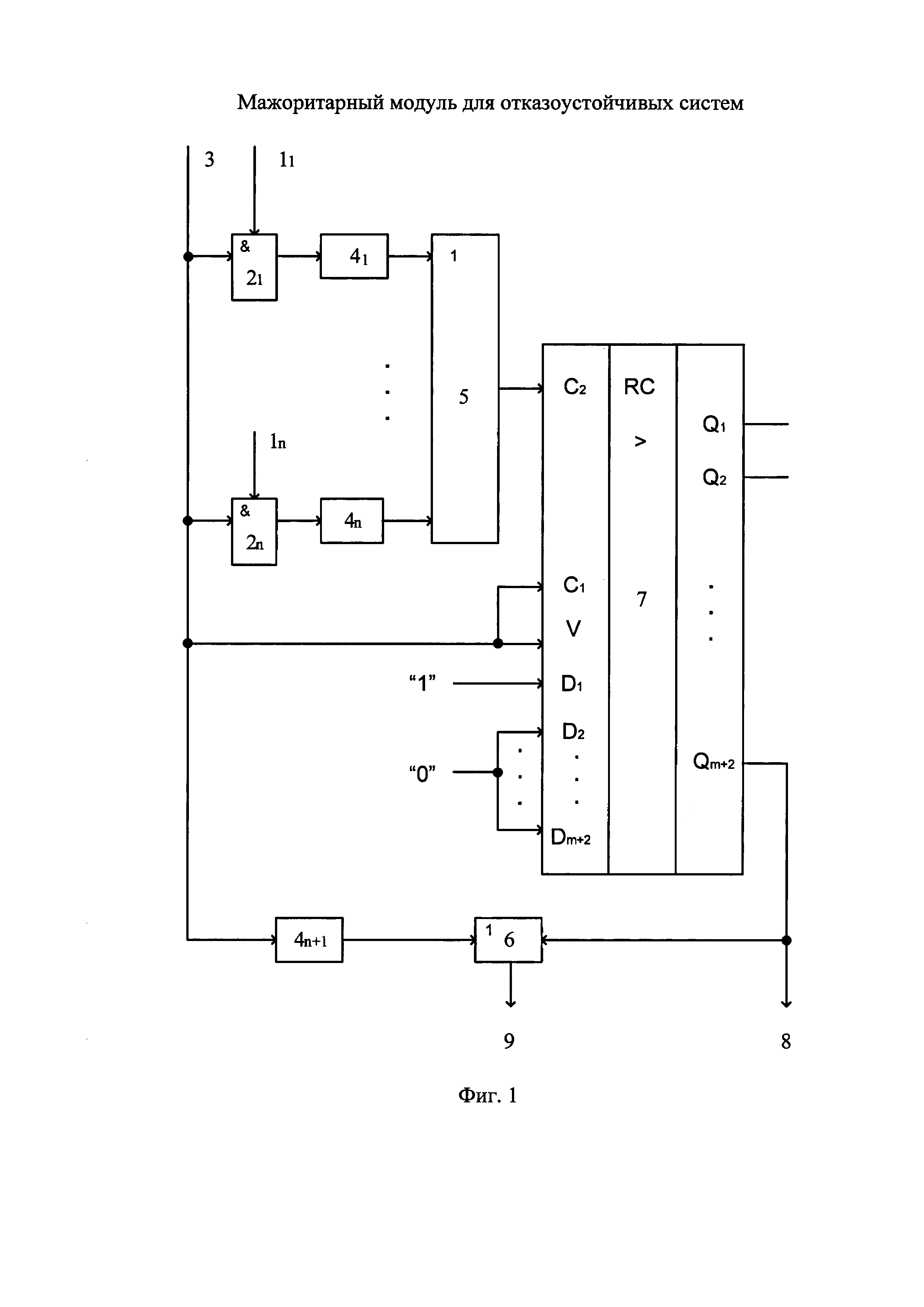

На чертеже представлена схема устройства. Мажоритарный модуль для отказоустойчивых систем содержит n информационных входов (n=2m+1, m=1, 2, …), 11-1n, n элементов И 21-2n, вход запуска 3, n+1 элементов задержки 41-4n+1, первый элемент ИЛИ 5, второй элемент ИЛИ 6, регистр сдвига 7, первый выход устройства 8, второй выход устройства 9. Элементы схемы соединены следующим образом, i-ый информационный вход 1i соединен с первым входом i-го элемента И 2i, (i=1, …, n). Выход i-го элемента И 2i соединен через i-ый элемент задержки 4i с i-ым входом первого элемента ИЛИ 5, (i=1, …, n). Вход запуска 3 соединен со вторыми входами всех элементов И 2i-2n, с первым тактовым входом (C1) и управляющим входом (V) регистра сдвига 7 и через n+1-ый элемент задержки 4n+1 с первым входом второго элемента ИЛИ 6. Выход первого элемента ИЛИ 5 соединен со вторым тактовым входом (С2) регистра сдвига 7. (m+2)-ой выход (Qm+2) регистра сдвига 7 соединен с первым выходом 8 устройства и вторым входом второго элемента ИЛИ 6. Выход второго элемента ИЛИ 6 соединен со вторым выходом устройства 9. Первый вход данных (D1) регистра сдвига 7 соединен с шиной «логическая 1». j-ый вход данных (Dj) регистра сдвига 7 соединен с шиной «логический 0», j=2, …, m+2.

Работает устройство следующим образом.

На информационные входы 11-1n подаются значения аргументов X1-Xn, n - нечетное число, n=2m+1, m=1, 2, ….

На вход запуска 3 подается единичный импульс, который поступает:

- на первый тактовый вход (C1) и управляющий вход (V) регистра сдвига 7, при этом в регистр сдвига 7 записывается с входов данных D1-Dm+2 двоичное число 10…0, которое и появляется на выходах Q1-Qm+2 регистра сдвига 7;

- на вторые входы всех элементов И 21-2n, при этом если значение i-го аргумента Xi=1, то импульс с входа запуска 3 проходит на выход элемента И 2i, и через элемент задержки 4i с временем задержки i×Tc, (Тс - время сдвига на один разряд в регистре сдвига), поступает на i-ый вход первого элемента ИЛИ 5. Сигнал с выхода первого элемента ИЛИ 5 поступает на второй тактовый вход (С2) регистра сдвига 7, при этом происходит сдвиг содержимого регистра сдвига 7 вправо;

- через (n+1)-ый элемент задержки 4n+1 со временем задержки Ти+Тили+(n+1)×Тс (Ти - время задержки в элементе И 2, Тили - время задержки в элементе ИЛИ) поступает на первый вход второго элемента ИЛИ 6 и проходит на второй выход устройства 8.

В процессе работы устройства возможны два случая:

1. Количество значений «1» среди значений аргументов не менее чем m+1. В этом случае, как только поступит на выход первого элемента ИЛИ 5 (m+1)-ый импульс, то на выходе Qm+2 регистра сдвига 7 появится сигнал «1», который поступит на первый выход устройства 8, указывая на значение мажоритарной функции, и через второй элемент ИЛИ 6 на выход 9, указывая, что результат вычисления мажоритарной функции готов.

2. Количество значений «1» среди значений аргументов меньше чем m+1. В этом случае на выходе Qm+2 регистра сдвига 7 все время будет сигнал «0». После окончания опроса значений аргументов на первом входе второго элемента ИЛИ 6 появляется сигнал «1», который проходит на второй выход устройства 9, указывая, что результат вычисления мажоритарной функции готов и его значение «0» сформировано на первом выходе 8 устройства.

Особенностью предложенного устройства является то, что как только будет выявлено, что значение мажоритарной функции «1», то оно сразу же поступает на первый выход 8 устройства и на второй выход устройства 9, указывая, что данные готовы. Для большинства двоичных наборов время вычисления единичного значения мажоритарной функции будет меньше времени опроса всех значений аргументов. Это позволяет использовать устройство в асинхронных схемах. Т.е. заявленное устройство имеет более широкие функциональные возможности.

Сравним характеристики обоих устройств.

Максимальная задержка сигнала от подачи сигнала запуска на вход запуска 3 в заявленном устройстве

Тзаяв=Ти+2Тили+(n+1)×Tc

и растет линейно от количества аргументов.

Заявленный мажоритарный модуль содержит n информационных входов (n=2m+1, m=1, 2, …), 11-ln, n элементов И 21-2n, вход запуска 3, n+1 элементов задержки 41-4n+1. Первый элемент ИЛИ 5 имеет n входов. Количество разрядов регистра сдвига 7 равно (n+1)/2.

Таким образом, сложность заявленного устройства растет линейно от количества аргументов.

В прототипе все мажоритарные элементы сгруппированы в три группы так, что в первой и второй группах содержится по m-1 (m=0,5×(n+1), n≠1 есть любое нечетное натуральное число) мажоритарных элементов, а в каждой группе выход предыдущего мажоритарного элемента соединен с вторым входом последующего мажоритарного элемента, все элементы 2И сгруппированы в

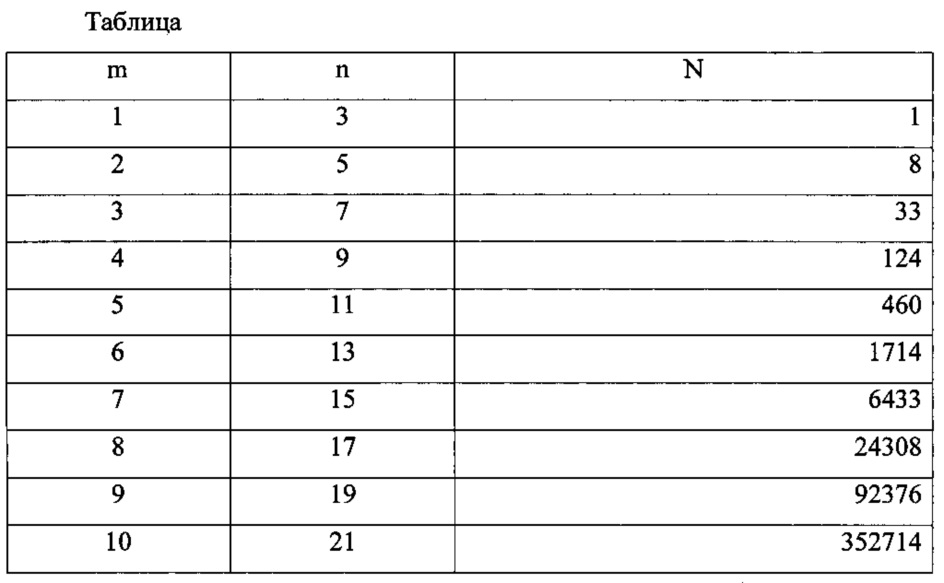

В таблице приведены значения количества групп N, рассчитанные по приведенной выше формуле, в зависимости от m и n.

Анализ приведенных значений показывает, что в прототипе сложность и задержка растет не по линейному закону, а значительно сильнее.

Сравнение характеристик прототипа и заявляемого устройства показывает, что заявленное устройство имеет более широкие функциональные возможности, меньшую сложность и большее быстродействие и эффективность его применения растет с количеством аргументов.

Реферат

Изобретение относится к вычислительной технике и может быть использовано для построения отказоустойчивых средств автоматики, функциональных узлов систем управления и др. Техническим результатом изобретения является расширение функциональных возможностей за счет возможности его использования как в синхронных, так и в асинхронных дискретных схемах, уменьшение сложности устройства и повышение его быстродействия. Мажоритарный модуль для отказоустойчивых систем содержит n информационных входов (n=2m+1, m=1, 2, …), n элементов И, вход запуска, n+1 элементов задержки, первый элемент ИЛИ, второй элемент ИЛИ, регистр сдвига, первый выход устройства, второй выход устройства. 1 ил., 1 табл.

Комментарии