Многофункциональное логическое устройство - RU2610247C1

Код документа: RU2610247C1

Чертежи

Описание

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известен логический модуль (табл. 18.2, стр. 312 в книге Каяцкас А.А. Основы радиоэлектроники: Учеб. пособие для студентов вузов по спец. «Констр. и производство радиоаппаратуры». М.: Высш. шк., 1988 г.), который содержит выход и реализует логическую функцию «Исключающее ИЛИ», зависящую от двух аргументов - входных двоичных сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании известного логического модуля, относятся ограниченные функциональные возможности, обусловленные тем, что он реализует булевую функцию «Исключающее ИЛИ», зависящую только от двух аргументов, и не реализует симметричные булевые функции.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип логический модуль (патент РФ 2546316, кл. G06F 7/57, 2015 г.), содержащий четыре информационных входа, два настроечных входа, выход устройства и реализующий при настройках булевые функции вида Х1~…~Х4, Х1⊕…⊕X4 для четырех аргументов.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности, обусловленные тем, что он реализует булевые функции вида Х1~…~Х4, Х1⊕…⊕X4 только для четырех аргументов и не реализует симметричные булевые функции.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения реализации для любого количества аргументов булевых функций вида Х1~…~Xn, Х1⊕…⊕Xn, симметричных булевых функций с прямым и инверсным вхождением аргументов в конъюнкцию.

Указанный технический результат при осуществлении изобретения достигается тем, что в многофункциональном логическом устройстве, содержащем информационные входы, два настроечных входа, выход устройства, особенность заключается в том, что оно содержит входы задания ранга, вход задания количества переменных, сумматор, элемент РАВНОЗНАЧНОСТЬ, схему сравнения, элемент НЕ, мультиплексор, причем информационные входы соединены с соответствующими входами сумматора, первый выход сумматора соединен со вторым информационным входом мультиплексора, первым входом элемента РАВНОЗНАЧНОСТЬ и первым входом первой группы входов схемы сравнения, i-й выход сумматора соединен с i-м входом первой группы входов схемы сравнения (i=2,…, k), входы задания ранга соединены с соответствующими входами второй группы входов схемы сравнения, выход «меньше» схемы сравнения соединен с третьим информационным входом мультиплексора и через элемент НЕ соединен с четвертым информационным входом мультиплексора, вход задания количества переменных соединен со вторым входом элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с первым информационным входом мультиплексора, первый настроечный вход соединен с первым адресным входом мультиплексора, второй настроечный вход соединен со вторым адресным входом мультиплексора, выход мультиплексора соединен с выходом устройства.

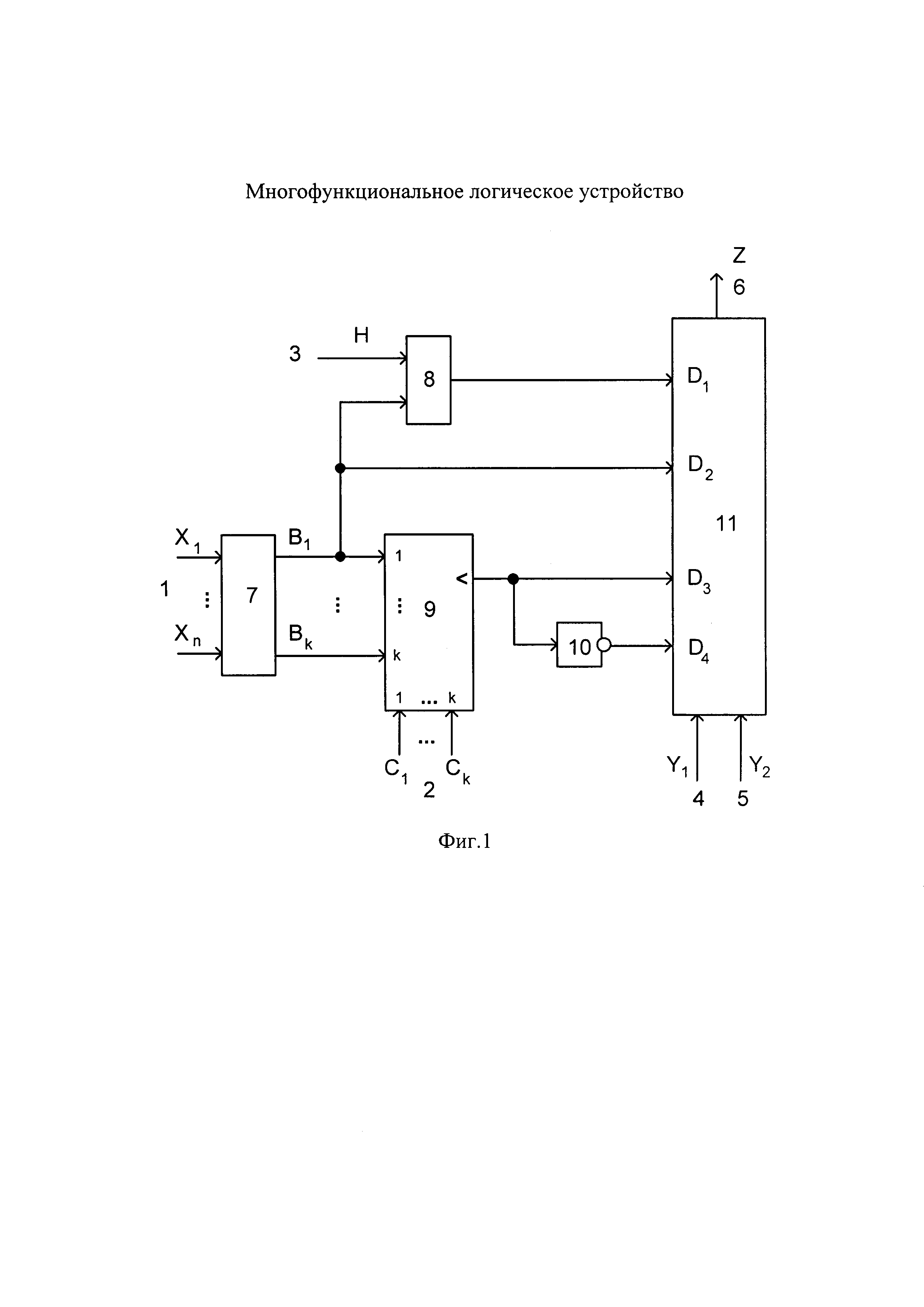

На чертеже представлена схема предлагаемого многофункционального логического устройства.

Многофункциональное логическое устройство содержит информационные входы 1, входы задания ранга 2, вход задания количества переменных 3, два настроечных входа 4 и 5, выход устройства 6, сумматор 7, элемент РАВНОЗНАЧНОСТЬ 8, схему сравнения 9, элемент НЕ 10, мультиплексор 11, причем информационные входы 1 соединены с соответствующими входами сумматора 7, первый выход сумматора 7 соединен со вторым информационным входом мультиплексора 11, первым входом элемента РАВНОЗНАЧНОСТЬ 8 и первым входом первой группы входов схемы сравнения 9, i-ый выход сумматора 7 соединен с i-ым входом первой группы входов схемы сравнения (i=2, …, k) 9, входы задания ранга соединены с соответствующими входами второй группы входов схемы сравнения 9, выход «меньше» схемы сравнения 9 соединен с третьим информационным входом мультиплексора 11 и через элемент НЕ соединен с четвертым информационным входом мультиплексора 11, вход задания количества переменных 3 соединен со вторым входом элемента РАВНОЗНАЧНОСТЬ 8, выход которого соединен с первым информационным входом мультиплексора 11, первый настроечный вход 4 соединен с первым адресным входом мультиплексора 11, второй настроечный вход 5 соединен со вторым адресным входом мультиплексора 11, выход мультиплексора 11 соединен с выходом устройства 6.

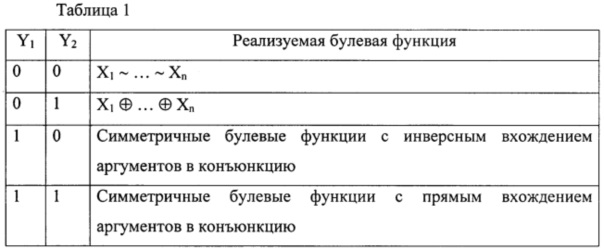

Многофункциональное логическое устройство в зависимости от значения настроечных сигналов Y1 и Y2 реализует следующие булевые функции, приведенные в табл. 1.

Выводы и элементы схемы многофункционального логического устройства решают следующие задачи.

На информационные входы 1 подаются значения аргументов X1,…, Xn; Xi∈{0,1}, i=1,…, n.

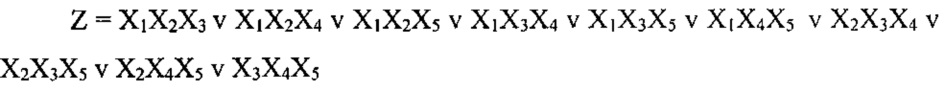

Входы задания ранга 2 используются при реализации симметричных булевых функций (настройка Y1=1, Y2=0 или Y1=1, Y2=1) ранга r. Рангом симметричной булевой функции называется количество аргументов, входящих в конъюнкции в дизъюнктивной нормальной форме. Например, для n=5 и

значение r=3.

На входы задания ранга 2 подается двоичный код C1, …, Ck, (C1 - младший разряд), который соответствует десятичному значению ранга г при прямом вхождении аргументов в реализуемую симметричную булевую функцию или значению n-r+1 при инверсном вхождении аргументов в реализуемую симметричную булевую функцию.

Значение k=]log2n[, где ]…[ означает ближайшее целое, не меньшее, чем выражение в скобках. Например, для n=4 значение k=2, а для n=5 значение k=3.

На вход задания количества переменных 3 подается значение Н, которое описывает количество переменных с точки зрения их четности. Если количество переменных четное, то Н=0, если нечетное, то Н=1.

На два настроечных входа 4 и 5 подаются сигналы в соответствии с таблицей настроек (табл. 1).

На выходе устройства 6 формируется булевая функция в соответствии с заданной настройкой.

Сумматор 7 определяет количество единиц среди множества значений аргументов X1, …, Xn. Сумматор имеет n входов и k выходов. Значения выходных сигналов обозначены B1, …, Bk, (разряд B1 - младший).

Элемент РАВНОЗНАЧНОСТЬ 8 производит сравнение значений сигналов Н и B1 и при их равенстве формирует на входе D1 мультиплексора 11 булевую функцию Z=X1~…~Xn.

Схема сравнения 9 производит сравнение двоичных кодов B1…Bk и С1…Ck. Если значение кода B1…Bk меньше значения кода C1…Ck, то на выходе «меньше» формируется значение «1», а на выходе элемента НЕ 10 значение «0» и наоборот.

Мультиплексор 11 в зависимости от значений настроечных сигналов Y1 и Y2 формирует на выходе устройства 6 значение соответствующей булевой функции Z.

Рассмотрим примеры реализации булевых функций.

Пусть n=5. Поскольку значение количества переменных нечетное, подаем на вход 3 значение Н=1.

Для реализации булевой функции вида X1~…~Xn на настроечные входы 4 и 5 подаются сигналы Y1=0 и Y2=0. При этом на вход D1 мультиплексора 11 с выхода элемента РАВНОЗНАЧНОСТЬ 8 поступает значение функции X1~…~Xn для соответствующих значений аргументов, которое передается на выход устройства 6.

Для реализации булевой функции вида Х1⊕…⊕Xn на настроечные входы 4 и 5 подаются сигналы Y1=0 и Y2=1. При этом на вход D2 мультиплексора 11 с выхода сумматора 7 поступает значение В1, которое при четном количестве единиц во входном наборе информационных сигналов равно «0», а при нечетном - равно «1». Это значение передается мультиплексором 11 на выход устройства 6.

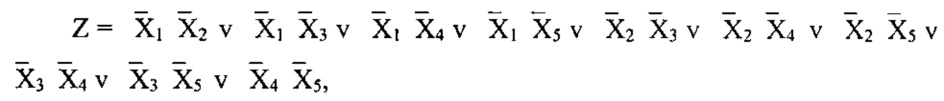

Для реализации симметричной булевой функции с инверсным вхождением аргументов в конъюнкцию, например, для ранга r=2 вида

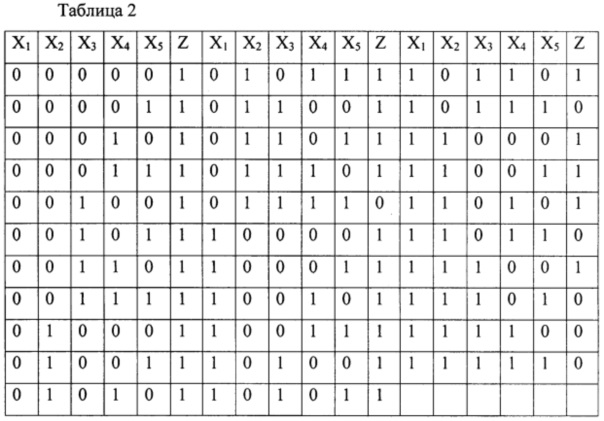

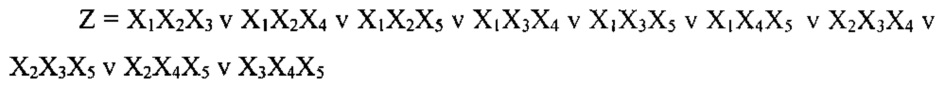

на настроечные входы 4 и 5 подаются сигналы Y1=1 и Y2=0, на входы задания ранга 2 подается двоичный код С1С2С3 вида 0,0,1 и соответствующий значению n-r+1=5-2+1=4. Значения реализуемой симметричной булевой функции поступают с выхода «меньше» схемы сравнения 9 на вход D3 мультиплексора 11 и передаются на выход устройства 6. Таблица истинности реализуемой симметричной булевой функции с инверсным вхождением аргументов в конъюнкцию приведена в табл. 2.

Для реализации симметричной булевой функции с прямым вхождением аргументов в конъюнкцию, например, для ранга r=3 вида

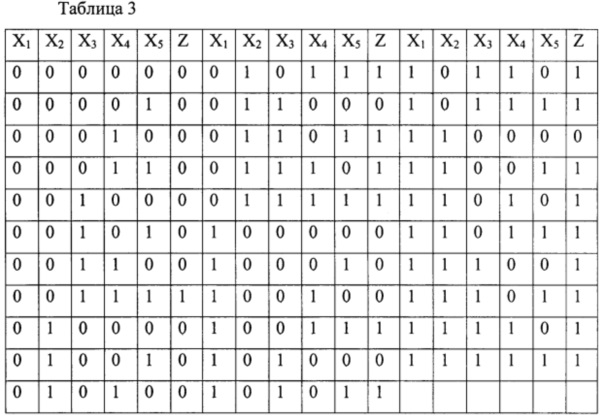

на настроечные входы 4 и 5 подаются сигналы Y1=1 и Y2=1, на входы задания ранга 2 подается двоичный код С1С2С3 вида 1,1,0 и соответствующий значению r=3. Значения реализуемой симметричной булевой функции поступают с выхода «меньше» схемы сравнения 9 через элемент НЕ 10 на вход D4 мультиплексора 11 и передаются на выход устройства 6. Таблица истинности реализуемой симметричной булевой функции с прямым вхождением аргументов в конъюнкцию приведена в табл. 3.

Сравнение прототипа и предлагаемого устройства показывает, что многофункциональное логическое устройство имеет более широкие функциональные возможности, т.к. реализует для любого количества аргументов (в прототипе для четырех) следующие булевые функции:

1. Х1~…~Xn.

2. X1⊕…⊕Xn.

3. Симметричные булевые функции с инверсным вхождением аргументов в конъюнкцию.

4. Симметричные булевые функции с прямым вхождением аргументов в конъюнкцию.

Использованные источники

1. Каяцкас А.А. Основы радиоэлектроники: Учеб. пособие для студентов вузов по спец. «Констр. и производство радиоаппаратуры». М.: Высш. шк., 1988 г.

2. Логический модуль (RU №2546316 С1, МПК G06F 7/57, заявлено 03.12.2013, опубликовано 10.04.2015).

Реферат

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики и функциональных узлов систем управления. Технический результат заключается в обеспечение реализации для любого количества аргументов булевых функций вида X~…~X, X⊕…⊕X, симметричных булевых функций с прямым и инверсным вхождением аргументов в конъюнкцию. Технический результат достигается за счет многофункционального логического устройства, которое содержит информационные входы, входы задания ранга, вход задания количества переменных, два настроечных входа, выход устройства, сумматор, элемент РАВНОЗНАЧНОСТЬ, схему сравнения, элемент НЕ и мультиплексор. 1 ил., 3 табл.

Формула

Документы, цитированные в отчёте о поиске

Итерационное арифметико-логическое устройство с контролируемой точностью

Комментарии