Гистерезисный триггер - RU2616874C2

Код документа: RU2616874C2

Чертежи

Описание

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении отказо- и сбоеустойчивых, радиационностойких самосинхронных схем.

Известен С-элемент Маллера, функциональный аналог гистерезисного триггера, содержащий три элемента два инвертера и цепи подключения шины «+» питания и шины «Ноль вольт» [1].

Недостатком такого устройства является низкая отказо- и сбоеустойчивость в условиях радиации.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков и принятым в качестве прототипа является гистерезисный триггер [2], в котором вместо ‘слабых’ транзисторов, используемых в С-элементе Маллера используются только традиционные, ‘сильные’ транзисторы, что повышает его сбоеустойчивость по сравнению с аналогом.

Недостатком прототипа, является низкая надежность относительно отказов и сбоев транзисторов, отказов источника питания и обрывов входов-выходов. Технические средства прототипа теряют работоспособность при необратимых отказах, либо сбое хотя бы одного любого транзистора, отказах или сбоях источника питания, а также обрыве входов-выходов.

Первой задачей изобретения является повышение надежности относительно отказов и сбоев транзисторов.

Это задача достигается тем, что в гистерезисный триггер (см. фиг. 1), содержащий группу (1) из шести транзисторов p-проводимости - первого (1.1), второго (1.2), третьего (1.3), четвертого (1.4), пятого (1.5) и шестого (1.6), группу (2) из шести транзисторов n-проводимости - первого (2.1), второго (2.2), третьего (2.3), четвертого (2.4), пятого (2.5) и шестого (2.6), вход подключения шины «+» питания (6.1), вход подключения шины «Ноль вольт» (7.1), первый (3.0) и второй (4.0) входы триггера, выход триггера (5.0), причем первый вход триггера (3.0) подключен к затворам первого (1.1) и третьего (1.3) транзисторов группы (1) из шести транзисторов p-проводимости и к затворам первого (2.1) и третьего (2.3) транзисторов группы (2) из шести транзисторов n-проводимости, истоки первого (1.1), третьего (1.3), четвертого (1.4) и шестого (1.6) транзисторов группы (1) из шести транзисторов p-проводимости подключены к входу подключения шины «+» (6.1), подложки первого (1.1), второго (1.2), третьего (1.3), четвертого (1.4), пятого (1.5) и шестого (1.6) транзисторов группы (1) из шести транзисторов p-проводимости подключены к входу подключения шины «+» (6.1), подложки первого (2.1), второго (2.2), третьего (2.3), четвертого (2.4), пятого (2.5) и шестого (2.6) транзисторов группы (2) из шести транзисторов n-проводимости подключены к входу подключения шины «Ноль вольт» (7.1), истоки первого (2.1), третьего (2.3), четвертого (2.4) и шестого (2.6) транзисторов группы (2) из шести транзисторов n-проводимости подключены к входу подключения шины «Ноль вольт» (7.1), второй вход триггера (4.0) подключен к затворам второго (1.2) и четвертого (1.4) транзисторов группы (1) из шести транзисторов p-проводимости и к затворам второго (2.2) и четвертого (2.4) транзисторов группы (2) из шести транзисторов n-проводимости, затворы пятого (1.5) транзистора группы (1) из шести транзисторов p-проводимости и пятого (2.5) транзистора группы (2) из шести транзисторов n-проводимости подключены к выходу триггера (5.0), затворы шестого (1.6) транзистора группы (1) из шести транзисторов p-проводимости и шестого (2.6) транзистора группы (2) из шести транзисторов n-проводимости объединены, отличающийся тем, что введена вторая группа транзисторов p-проводимости (8), состоящая из шести подгрупп i=1…6, в каждой подгруппе (8.i), три транзистора p-проводимости (8.i.1), (8.i.2), (8.i.3), вторая группа транзисторов n-проводимости (9), состоящая из шести подгрупп i=1…6, в каждой подгруппе (9.i), три транзистора n-проводимости (9.i.1), (9.i.2), (9.i.3), причем каждая подгруппа второй группы транзисторов p-проводимости (8.i) подключается к соответствующему транзистору группы из шести транзисторов p-проводимости (1.i), исток первого транзистора i-ой подгруппы второй группы транзисторов p-проводимости (8.i.1) объединяется с истоком транзистора групп из шести транзисторов p-проводимости (1.i), исток второго (8.i.2) транзистора i-ой подгруппы второй группы транзисторов p-проводимости подключен к стоку первого транзистора i-ой подгруппы второй группы транзисторов p-проводимости, исток третьего транзистора i-ой подгруппы второй группы транзисторов p-проводимости подключен к стоку i-го транзистора группы из шести транзисторов p-проводимости, стоки второго (8.i.2) и третьего (8.i.3) транзисторов i-ой подгруппы второй группы транзисторов p-проводимости объединены, затворы i-ой подгруппы второй группы транзисторов p-проводимости (8.i) подключаются к затвору i-го транзистора из группы шести транзисторов p-проводимости (1.i), каждая i-ая подгруппа второй группы транзисторов n-проводимости (9.i) подключается к соответствующему транзистору группы из шести транзисторов n-проводимости (2.i), исток первого транзистора i-ой подгруппы второй группы транзисторов n-проводимости (9.i.1) объединяется с i-ым истоком транзистора групп из шести транзисторов n-проводимости (2.i), исток второго (9.i.2) транзистора i-ой подгруппы второй группы транзисторов n-проводимости подключен к стоку первого транзистора i-ой подгруппы второй группы транзисторов n-проводимости, исток третьего транзистора i-ой подгруппы второй группы транзисторов n-проводимости подключен к стоку i-го транзистора группы из шести транзисторов p-проводимости, стоки второго (9.i.2) и третьего (9.i.3) транзисторов i-ой подгруппы второй группы транзисторов n-проводимости объединены, затворы i-ой подгруппы второй группы транзисторов n-проводимости (9.i) подключаются к затвору i-го транзистора из группы шести транзисторов n-проводимости (2.i), подложки всех транзисторов второй группы транзисторов p-проводимости (8) подключены к входу подключения шины питания «+», подложки всех транзисторов второй группы транзисторов n-проводимости (9) подключены к входу подключения шины питания «Ноль вольт», исток второго транзистора (1.2) группы из шести транзисторов p-проводимости подключен к стоку третьего транзистора (8.1.3) первой подгруппы второй группы транзисторов p-проводимости, исток пятого транзистора (1.5) группы из шести транзисторов p-проводимости подключен к стоку третьего транзистора (8.3.3) третьей подгруппы второй группы транзисторов p-проводимости и к стоку третьего транзистора (8.4.3) четвертой подгруппы второй группы транзисторов p-проводимости, исток второго транзистора (2.2) группы из шести транзисторов n-проводимости подключен к стоку третьего транзистора (9.1.3) первой подгруппы второй группы транзисторов n-проводимости, исток пятого транзистора (2.5) группы из шести транзисторов n-проводимости подключен к стоку третьего транзистора (9.3.3) третьей подгруппы второй группы транзисторов n-проводимости и к стоку третьего транзистора (9.4.3) четвертой подгруппы второй группы транзисторов n-проводимости, стоки третьих транзисторов второй и пятой подгруппы второй группы транзисторов p-проводимости и стоки третьих транзисторов второй и пятой подгруппы второй группы транзисторов n-проводимости объединены и подключены к объединенным затворам шестого транзистора группы из шести транзисторов p-проводимости и шестого транзистора группы из шести транзисторов n-проводимости, стоки третьих транзисторов шестой подгруппы второй группы транзисторов p-проводимости и стоки третьих транзисторов шестой подгруппы второй группы транзисторов n-проводимости объединены и подключены к выходу триггера.

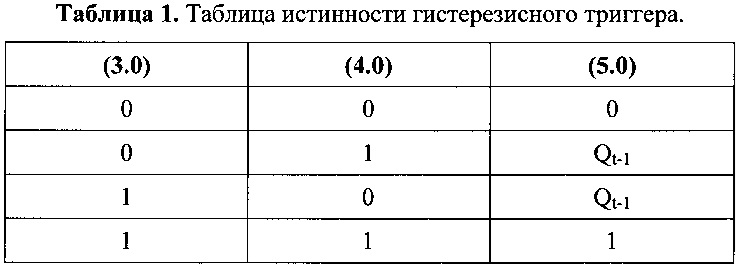

При отсутствии отказов и сбоев в транзисторах схема работает следующим образом. Низкий уровень на двух входах гистерезисного триггера (вход 3.0 = вход 4.0 = 0) переводит триггер в состояние нуля (выход 5.0 = 0). Высокий уровень на обоих входах (вход 3.0 = вход 4.0 = 1) переводит триггер в состояние единицы (выход 5.0=1). В остальных случаях триггер обеспечивает хранение информации.

Особенности данной схемы по сравнению с прототипом следующие.

Для реализации логической функции триггера используются не единичные транзисторы, а транзисторные цепочки, составленные по функционально-полным толерантным базисам вида (по методу учетверенной логики):

где fji - функция, реализуемая j-ым транзистором из группы транзисторов p- или n-проводимости.

Такая функция сохраняет свое значение при отказах и сбоях только одного транзистора в каждой цепочке, то есть при изменении fj1, fj2, fj3, fj4,: замене на константу нуля, замене на константу единицы, инверсия, замене на произвольную функцию. Для этого к каждому транзистору прототипа вводится дополнительно три транзистора.

Таким образом, предлагаемое устройство обеспечивает повышение надежности за счет появления устойчивости к отказам и сбоям транзисторов. Цель изобретения достигнута.

Второй задачей изобретения является повышение надежности не только относительно отказов и сбоев транзисторов, но и относительно обрывов проводов.

Это задача достигается тем, что в гистерезисный триггер (см. фиг. 2), в котором элементы и связи прототипа (доотличительная часть п. 1 формулы) полностью совпадающие с их описанием в соответствии с фиг. 1 дополнены введением второй группы транзисторов p-проводимости (8), состоящей из шести подгрупп (8.1), (8.2), (8.3), (8.4), (8.5), (8.6), в каждой подгруппе (8.i), i=1…6 три транзистора p-проводимости (8.i.1), (8.i.2), (8.i.3), второй группы транзисторов n-проводимости (9), состоящей из шести подгрупп (9.1), (9.2), (9.3), (9.4), (9.5), (9.6), в каждой подгруппе (9.i), i=1…6 три транзистора n-проводимости (9.i.1), (9.i.2), (9.i.3), трех резервных входов для первого входа триггера (3.1), (3.2), (3.3), трех резервных входов для второго входа триггера (4.1), (4.2), (4.3) и трех резервных выходов триггера (5.1), (5.2), (5.3), причем первый резервный вход для первого входа триггера (3.1) подключен к затворам первых транзисторов первой и третьей подгруппы второй группы транзисторов p-проводимости (8.1.1), (8.3.1) и к затворам первых транзисторов первой и третьей подгруппы второй группы транзисторов n-проводимости (9.1.1), (9.3.1), второй резервный вход для первого входа триггера (3.2) подключен к затворам вторых транзисторов первой и третьей подгруппы второй группы транзисторов p-проводимости (8.1.2), (8.3.2) и к затворам вторых транзисторов первой и третьей подгруппы второй группы транзисторов n-проводимости (9.1.2), (9.3.2), третий резервный вход для первого входа триггера (3.3) подключен к затворам третьих транзисторов первой и третьей подгруппы второй группы транзисторов p-проводимости (8.1.3), (8.3.3) и к затворам третьих транзисторов первой и третьей подгруппы второй группы транзисторов n-проводимости (9.1.3), (9.3.3), первый резервный вход для второго входа триггера (4.1) подключен к затворам первых транзисторов второй и четвертой подгруппы второй группы транзисторов p-проводимости (8.2.1), (8.4.1) и к затворам первых транзисторов второй и четвертой подгруппы второй группы транзисторов n-проводимости (9.2.1), (9.4.1), второй резервный вход для второго входа триггера (4.2) подключен к затворам вторых транзисторов второй и четвертой подгруппы второй группы транзисторов p-проводимости (8.2.2), (8.4.2) и к затворам вторых транзисторов второй и четвертой подгруппы второй группы транзисторов n-проводимости (9.2.2), (9.4.2), третий резервный вход для второго входа триггера (4.3) подключен к затворам третьих транзисторов второй и четвертой подгруппы второй группы транзисторов p-проводимости (8.2.3), (8.4.3) и к затворам третьих транзисторов второй и четвертой подгруппы второй группы транзисторов n-проводимости (9.2.3), (9.4.3), первый резервный выход триггера (5.1) подключен к затвору первого транзистора пятой подгруппы второй групп транзисторов p-проводимости (8.5.1) и к затвору первого транзистора пятой подгруппы второй группы транзисторов n-проводимости (9.5.1), второй резервный выход триггера (5.2) подключен к затвору второго транзистора пятой подгруппы второй групп транзисторов p-проводимости (8.5.2) и к затвору второго транзистора пятой подгруппы второй группы транзисторов n-проводимости (9.5.2), третий резервный выход триггера (5.3) подключен к затвору третьего транзистора пятой подгруппы второй групп транзисторов p-проводимости (8.5.3) и к затвору третьего транзистора пятой подгруппы второй группы транзисторов n-проводимости (9.5.3), каждая подгруппа второй группы транзисторов p-проводимости (8.i) подключается к соответствующему транзистору группы из шести транзисторов p-проводимости (1.i), исток первого транзистора i-ой подгруппы второй группы транзисторов p-проводимости (8.i.1) объединяется с истоком транзистора групп из шести транзисторов p-проводимости (1.i), исток второго (8.i.2) транзистора i-ой подгруппы второй группы транзисторов p-проводимости подключен к стоку первого транзистора i-ой подгруппы второй группы транзисторов p-проводимости, исток третьего транзистора i-ой подгруппы второй группы транзисторов p-проводимости подключен к стоку i-го транзистора группы из шести транзисторов p-проводимости, стоки второго (8.i.2) и третьего (8.i.3) транзисторов i-ой подгруппы второй группы транзисторов p-проводимости объединены, каждая подгруппа второй группы транзисторов n-проводимости (9.i) подключается к соответствующему транзистору группы из шести транзисторов n-проводимости (2.i), исток первого транзистора i-ой подгруппы второй группы транзисторов n-проводимости (9.i.1) объединяется с истоком транзистора групп из шести транзисторов n-проводимости (2.i), исток второго (9.i.2) транзистора i-ой подгруппы второй группы транзисторов n-проводимости подключен к стоку первого транзистора i-ой подгруппы второй группы транзисторов n-проводимости, исток третьего транзистора i-ой подгруппы второй группы транзисторов n-проводимости подключен к стоку i-го транзистора группы из шести транзисторов p-проводимости, стоки второго (9.1.2) и третьего (9.i.3) транзисторов i-ой подгруппы второй группы транзисторов n-проводимости объединены, подложки всех транзисторов второй группы транзисторов p-проводимости (8) подключены к входу подключения шины питания «+», подложки всех транзисторов второй группы транзисторов n-проводимости (9) подключены к входу подключения шины питания «Ноль вольт», исток второго транзистора (1.2) группы из шести транзисторов p-проводимости подключен к стоку третьего транзистора (8.1.3) первой подгруппы второй группы транзисторов p-проводимости, исток пятого транзистора (1.5) группы из шести транзисторов p-проводимости подключен к стокам третьего транзистора (8.3.3) третьей подгруппы второй группы транзисторов p-проводимости и третьего транзистора (8.4.3) четвертой подгруппы второй группы транзисторов p-проводимости, исток второго транзистора (2.2) группы из шести транзисторов n-проводимости подключен к стоку третьего транзистора (9.1.3) первой подгруппы второй группы транзисторов n-проводимости, исток пятого транзистора (2.5) группы из шести транзисторов n-проводимости подключен к стокам третьего транзистора (9.3.3) третьей подгруппы второй группы транзисторов n-проводимости и третьего транзистора (9.4.3) четвертой подгруппы второй группы транзисторов n-проводимости, стоки третьих транзисторов второй (8.2.3) и пятой (8.5.3) подгруппы второй группы транзисторов p-проводимости и стоки третьих транзисторов второй (8.2.3) и пятой (8.5.3) подгруппы второй группы транзисторов n-проводимости подключены к затворам шестого транзистора группы (1.6) из шести транзисторов p-проводимости, шестого транзистора (2.6) группы из шести транзисторов n-проводимости, всех транзисторов (8.6) шестой подгруппы второй группы транзисторов p-проводимости, всех транзисторов (9.6) шестой подгруппы второй группы транзисторов n-проводимости, сток третьего транзистора (8.6.3) шестой подгруппы второй группы транзисторов p-проводимости и сток третьего транзистора (9.6.3) шестой подгруппы второй группы транзисторов n-проводимости объединены, сток второго транзистора (8.6.2) шестой подгруппы второй группы транзисторов p-проводимости подключен к первому резервному выходу триггера (5.1), сток третьего транзистора (8.6.3) шестой подгруппы второй группы транзисторов p-проводимости подключен к выходу триггера (5.0), сток второго транзистора (9.6.2) шестой подгруппы второй группы транзисторов n-проводимости подключен к второму резервному выходу триггера (5.2), сток третьего транзистора (9.6.3) шестой подгруппы второй группы транзисторов n-проводимости подключен к третьему резервному выходу триггера (5.3).

Введение дополнительных входов-выходов в дополнение к введению дополнительных транзисторов p и n-проводимости позволяет обеспечить повышение надежности относительно отказов и сбоев транзисторов и обрывов входов-выходов. То есть, учитывая в выражении (1) функцию работоспособности входов-выходов x1, x2, x3, x4 получим выражение (2):

Таким образом, учитывается возможность работы при обрыве одного из четырех входов-выходов x1, x2, x3, x4, в отличие от выражения (1) которое принимает неправильное значение при обрыве соответствующего входа-выхода, учитываемого в функцией fji.

Для этого к каждому транзистору прототипа вводится дополнительно три транзистора и три резервных входа-выхода для каждого входа-выхода триггера.

Таким образом, предлагаемое устройство обеспечивает повышение надежности относительно отказов и сбоев транзисторов и обрывов входов-выходов, за счет появления устойчивости к отказам и сбоям транзисторов, и обрывам входов-выходов. Цель изобретения достигнута.

Третьей задачей изобретения является повышение надежности не только относительно отказов и сбоев транзисторов, но и относительно отказов источника питания.

Это задача достигается тем, что в гистерезисный триггер (см. фиг. 3), в котором элементы и связи прототипа (доотличительная часть п. 1 формулы) полностью совпадающие с их описанием в соответствии с фиг. 1 дополнены введением второй группы транзисторов p-проводимости (8), состоящей из шести подгрупп (8.1), (8.2), (8.3), (8.4), (8.5), (8.6), в каждой подгруппе (8.i), i=1…6 три транзистора p-проводимости (8.i.1), (8.i.2), (8.i.3), второй группы транзисторов n-проводимости (9), состоящей из шести подгрупп (9.1), (9.2), (9.3), (9.4), (9.5), (9.6), в каждой подгруппе (9.i), i=1…6 три транзистора n-проводимости (9.i.1), (9.i.2), (9.i.3), резервным входом для подключения шины питания «+» (6.2) и резервным входом для подключения шины «Ноль вольт» (7.2), причем каждая подгруппа второй группы транзисторов p-проводимости (8.i) подключается к соответствующему транзистору группы из шести транзисторов p-проводимости (1.i), исток второго (8.i.2) транзистора i-ой подгруппы второй группы транзисторов p-проводимости подключен к стоку первого транзистора i-ой подгруппы второй группы транзисторов p-проводимости, исток третьего транзистора i-ой подгруппы второй группы транзисторов p-проводимости подключен к стоку i-го транзистора группы из шести транзисторов p-проводимости, стоки второго (8.i.2) и третьего (8.i.3) транзисторов i-ой подгруппы второй группы транзисторов p-проводимости объединены, затворы i-ой подгруппы второй группы транзисторов p-проводимости (8.i) подключаются к затвору транзистора из группы шести транзисторов p-проводимости (1.i), каждая подгруппа второй группы транзисторов n-проводимости (9.i) подключается к соответствующему транзистору группы из шести транзисторов n-проводимости (2.i), исток второго (9.i.2) транзистора i-ой подгруппы второй группы транзисторов n-проводимости подключен к стоку первого транзистора i-ой подгруппы второй группы транзисторов n-проводимости, исток третьего транзистора i-ой подгруппы второй группы транзисторов n-проводимости подключен к стоку i-го транзистора группы из шести транзисторов p-проводимости, стоки второго (9.i.2) и третьего (9.i.3) транзисторов i-ой подгруппы второй группы транзисторов n-проводимости объединены, затворы i-ой подгруппы второй группы транзисторов n-проводимости (9.i) подключаются к затвору транзистора из группы шести транзисторов n-проводимости (2.i), подложки третьих транзисторов i-ой подгруппы второй группы транзисторов p-проводимости (8) подключены к входу подключения шины питания «+», подложки третьих транзисторов i-ой подгруппы второй группы транзисторов n-проводимости (9) подключены к входу подключения шины питания «Ноль вольт», исток второго транзистора (1.2) группы из шести транзисторов p-проводимости подключен к стоку третьего транзистора (8.1.3) первой подгруппы второй группы транзисторов p-проводимости, исток пятого транзистора (1.5) группы из шести транзисторов p-проводимости подключен к стоку третьего транзистора (8.3.3) третьей подгруппы второй группы транзисторов p-проводимости и к стоку третьего транзистора (8.4.3) четвертой подгруппы второй группы транзисторов p-проводимости, исток второго транзистора (2.2) группы из шести транзисторов n-проводимости подключен к стоку третьего транзистора (9.1.3) первой подгруппы второй группы транзисторов n-проводимости, исток пятого транзистора (2.5) группы из шести транзисторов n-проводимости подключен к стоку третьего транзистора (9.3.3) третьей подгруппы второй группы транзисторов n-проводимости и к стоку третьего транзистора (9.4.3) четвертой подгруппы второй группы транзисторов n-проводимости, стоки третьих транзисторов второй и пятой подгруппы второй группы транзисторов p-проводимости и стоки третьих транзисторов второй и пятой подгруппы второй группы транзисторов n-проводимости объединены и подключены к объединенным затворам шестого транзистора группы из шести транзисторов p-проводимости и шестого транзистора группы из шести транзисторов n-проводимости, сток третьего транзистора шестой подгруппы второй группы транзисторов p-проводимости и сток третьего транзистора шестой подгруппы второй группы транзисторов n-проводимости объединены и подключены к выходу триггера (5.0), подложки первых (8.i.1) и вторых (8.i.2) транзисторов i-ой подгруппы второй группы транзисторов p-проводимости подключены к резервному входу подключения шины питания «+», истоки первых транзисторов первой, третьей, четвертой и шестой подгруппы второй группы транзисторов p-проводимости подключаются к резервному входу (6.2) для подключения шины питания «+», подложки первых (9.i.1) и вторых (9.i.2) транзисторов i-ой подгруппы второй группы транзисторов n-проводимости подключены к резервному входу (7.2) подключения шины питания «Ноль вольт», истоки первых транзисторов первой, третьей, четвертой и шестой подгруппы второй группы транзисторов n-проводимости подключаются к резервному входу для подключения шины питания «Ноль вольт» (7.2), резервный вход для подключения шины «Ноль вольт» (7.2) подключен ко входу для подключения шины «Ноль вольт» (7.1), исток первого транзистора второй подгруппы второй группы транзисторов p-проводимости (8.2.1) объединен с истоком второго транзистора группы из шести транзисторов p-проводимости (1.2), исток первого транзистора второй подгруппы второй группы транзисторов n-проводимости (9.2.1) объединен с истоком второго транзистора группы из шести транзисторов n-проводимости (2.2), исток первого транзистора пятой подгруппы второй группы транзисторов p-проводимости (8.5.1) объединен с истоком пятого транзистора группы из шести транзисторов p-проводимости (1.5), исток первого транзистора пятой подгруппы второй группы транзисторов n-проводимости (9.5.1) объединен с истоком пятого транзистора группы из шести транзисторов n-проводимости (2.5).

Для реализации настоящей цели изобретения к каждому транзистору прототипа вводится дополнительно три транзистора и резервные входы источника подключения шин питания «+» и «Ноль вольт».

Введение дополнительных резервных входов подключения шин питания «+» и «Ноль вольт» в дополнение к введению дополнительных транзисторов p- и n-проводимости позволяет обеспечить повышение надежности относительно отказов и сбоев транзисторов и отказов источника питания. То есть помимо обеспечения работоспособности при отказах и сбоях транзисторов по формуле (1) дополнительно обеспечивается возможность работы схемы при отказе одного из источников питания или обрыве одного из входов «Ноль вольт».

Таким образом, предлагаемое устройство обеспечивает повышение надежности относительно отказов и сбоев транзисторов и отказов источника питания за счет появления устойчивости к отказам и сбоям транзисторов, и отказам источников питания. Цель изобретения достигнута.

Четвертой задачей изобретения является повышение надежности относительно отказов и сбоев транзисторов, обрывов проводов входов-выходов и отказов источника питания.

Это задача достигается тем, что в гистерезисный триггер (см. фиг. 4), в котором элементы и связи прототипа (доотличительная часть п. 1 формулы) полностью совпадающие с их описанием в соответствии с фиг. 1 дополнены введением второй группа транзисторов p-проводимости (8), состоящей из шести подгрупп (8.1), (8.2), (8.3), (8.4), (8.5), (8.6), в каждой подгруппе (8.i), i=1…6 три транзистора p-проводимости (8.i.1), (8.i.2), (8.i.3), второй группы транзисторов n-проводимости (9), состоящей из шести подгрупп (9.1), (9.2), (9.3), (9.4), (9.5), (9.6), в каждой подгруппе (9.i), i=1…6 три транзистора n-проводимости (9.i.1), (9.i.2), (9.i.3), резервного входа для подключения шины питания «+» (6.2), резервного входа для подключения шины «Ноль вольт» (7.2), трех резервных входов для первого входа триггера (3.1), (3.2), (3.3), трех резервных входа для второго входа триггера (4.1), (4.2), (4.3) и трех резервных выходов триггера (5.1), (5.2), (5.3), причем, каждая подгруппа второй группы транзисторов p-проводимости (8.i) подключается к соответствующему транзистору группы из шести транзисторов p-проводимости (1.i), исток второго (8.i.2) транзистора i-ой подгруппы второй группы транзисторов p-проводимости подключен к стоку первого транзистора i-ой подгруппы второй группы транзисторов p-проводимости, исток третьего транзистора i-ой подгруппы второй группы транзисторов p-проводимости подключен к стоку i-го транзистора группы из шести транзисторов p-проводимости, стоки второго (8.i.2) и третьего (8.i.3) транзисторов i-ой подгруппы второй группы транзисторов p-проводимости объединены, каждая подгруппа второй группы транзисторов n-проводимости (9.i) подключается к соответствующему транзистору группы из шести транзисторов n-проводимости (2.i), исток второго (9.i.2) транзистора i-ой подгруппы второй группы транзисторов n-проводимости подключен к стоку первого транзистора i-ой подгруппы второй группы транзисторов n-проводимости, исток третьего транзистора i-ой подгруппы второй группы транзисторов n-проводимости подключен к стоку i-го транзистора группы из шести транзисторов p-проводимости, стоки второго (9.i.2) и третьего (9.i.3) транзисторов i-ой подгруппы второй группы транзисторов n-проводимости объединены, подложки третьих транзисторов i-ой подгруппы второй группы транзисторов p-проводимости (8) подключены к входу подключения шины питания «+», подложки третьих транзисторов i-ой подгруппы второй группы транзисторов n-проводимости (9) подключены к входу подключения шины питания «Ноль вольт», исток второго транзистора (1.2) группы из шести транзисторов p-проводимости подключен к стоку третьего транзистора (8.1.3) первой подгруппы второй группы транзисторов p-проводимости, исток пятого транзистора (1.5) группы из шести транзисторов p-проводимости подключен к стоку третьего транзистора (8.3.3) третьей подгруппы второй группы транзисторов p-проводимости и к стоку третьего транзистора (8.4.3) четвертой подгруппы второй группы транзисторов p-проводимости, исток второго транзистора (2.2) группы из шести транзисторов n-проводимости подключен к стоку третьего транзистора (9.1.3) первой подгруппы второй группы транзисторов n-проводимости, исток пятого транзистора (2.5) группы из шести транзисторов n-проводимости подключен к стоку третьего транзистора (9.3.3) третьей подгруппы второй группы транзисторов n-проводимости и к стоку третьего транзистора (9.4.3) четвертой подгруппы второй группы транзисторов n-проводимости, стоки третьих транзисторов второй и пятой подгруппы второй группы транзисторов p-проводимости и стоки третьих транзисторов второй и пятой подгруппы второй группы транзисторов n-проводимости объединены и подключены к объединенным затворам шестого транзистора группы из шести транзисторов p-проводимости и шестого транзистора группы из шести транзисторов n-проводимости, сток третьего транзистора шестой подгруппы второй группы транзисторов p-проводимости и сток третьего транзистора шестой подгруппы второй группы транзисторов n-проводимости объединены и подключены к выходу триггера, подложки первых (8.i.1) и вторых (8.i.2) транзисторов i-ой подгруппы второй группы транзисторов p-проводимости подключены к резервному входу подключения шины питания «+», истоки первых транзисторов первой, третьей, четвертой и шестой подгруппы второй группы транзисторов p-проводимости подключаются к резервному входу для подключения шины питания «+», подложки первых (9.i.1) и вторых (9.i.2) транзисторов i-ой подгруппы второй группы транзисторов n-проводимости подключены к резервному входу подключения шины питания «Ноль вольт», истоки первых транзисторов первой, третьей, четвертой и шестой подгруппы второй группы транзисторов n-проводимости подключаются к резервному входу для подключения шины питания «Ноль вольт», резервный вход для подключения шины «Ноль вольт» (7.2) подключен ко входу для подключения шины «Ноль вольт» (7.1), первый резервный вход для первого входа триггера (3.1) подключен к затворам первых транзисторов первой и третьей подгруппы второй группы транзисторов p-проводимости (8.1.1), (8.3.1) и к затворам первых транзисторов первой и третьей подгруппы второй группы транзисторов n-проводимости (9.1.1), (9.3.1), второй резервный вход для первого входа триггера (3.2) подключен к затворам вторых транзисторов первой и третьей подгруппы второй группы транзисторов p-проводимости (8.1.2), (8.3.2) и к затворам вторых транзисторов первой и третьей подгруппы второй группы транзисторов n-проводимости (9.1.2), (9.3.2), третий резервный вход для первого входа триггера (3.3) подключен к затворам третьих транзисторов первой и третьей подгруппы второй группы транзисторов p-проводимости (8.1.3), (8.3.3) и к затворам третьих транзисторов первой и третьей подгруппы второй группы транзисторов n-проводимости (9.1.3), (9.3.3), первый резервный вход для второго входа триггера (4.1) подключен к затворам первых транзисторов второй и четвертой подгруппы второй группы транзисторов p-проводимости (8.2.1), (8.4.1) и к затворам первых транзисторов второй и четвертой подгруппы второй группы транзисторов n-проводимости (9.2.1), (9.4.1), второй резервный вход для второго входа триггера (4.2) подключен к затворам вторых транзисторов второй и четвертой подгруппы второй группы транзисторов p-проводимости (8.2.2), (8.4.2) и к затворам вторых транзисторов второй и четвертой подгруппы второй группы транзисторов n-проводимости (9.2.2), (9.4.2), третий резервный вход для второго входа триггера (4.3) подключен к затворам третьих транзисторов второй и четвертой подгруппы второй группы транзисторов p-проводимости (8.2.3), (8.4.3) и к затворам третьих транзисторов второй и четвертой подгруппы второй группы транзисторов n-проводимости (9.2.3), (9.4.3), первый резервный выход триггера (5.1) подключен к затвору первого транзистора пятой подгруппы второй групп транзисторов p-проводимости (8.5.1) и к затвору первого транзистора пятой подгруппы второй группы транзисторов n-проводимости (9.5.1), второй резервный выход триггера (5.2) подключен к затвору второго транзистора пятой подгруппы второй групп транзисторов p-проводимости (8.5.2) и к затвору второго транзистора пятой подгруппы второй группы транзисторов n-проводимости (9.5.2), третий резервный выход триггера (5.3) подключен к затвору третьего транзистора пятой подгруппы второй групп транзисторов p-проводимости (8.5.3) и к затвору третьего транзистора пятой подгруппы второй группы транзисторов n-проводимости (9.5.3), исток первого транзистора (8.2.1) второй подгруппы второй группы транзисторов p-проводимости объединен с истоком второго транзистора (1.2) группы из шести транзисторов p-проводимости, исток первого транзистора (9.2.1) второй подгруппы второй группы транзисторов n-проводимости объединен с истоком второго транзистора (2.2) группы из шести транзисторов n-проводимости, исток первого транзистора (8.5.1) пятой подгруппы второй группы транзисторов p-проводимости объединен с истоком пятого транзистора (1.5) группы из шести транзисторов p-проводимости, исток первого транзистора (9.5.1) пятой подгруппы второй группы транзисторов n-проводимости объединен с истоком пятого (2.5) транзистора группы из шести транзисторов n-проводимости.

Для реализации настоящей цели изобретения помимо введения дополнительных транзисторов p- и n-проводимости (в соответствие с формулой 1) и резервных входов-выходов (в соответствие с формулой 2) вводятся также дополнительно резервные входы подключения шин питания «+» и «Ноль вольт», что позволяет обеспечить повышение надежности как относительно отказов и сбоев транзисторов, так и обрывов входов-выходов, а также относительно отказов источника питания. Цель изобретения достигнута.

На фиг. 1 изображена схема электрическая принципиальная предлагаемого гистерезисного триггера отказоустойчивого относительно отказов или сбоев транзисторов (первая задача изобретения).

На фиг. 2 изображена схема электрическая принципиальная предлагаемого гистерезисного триггера, отказоустойчивого относительно отказов или сбоев транзисторов и обрывов входов-выходов (вторая задача изобретения).

На фиг. 3 изображена схема электрическая принципиальная предлагаемого гистерезисного триггера, отказоустойчивого относительно отказов или сбоев транзисторов и отказов источников питания (третья задача изобретения).

На фиг. 4 изображена схема электрическая принципиальная предлагаемого гистерезисного триггера, отказоустойчивого относительно отказов или сбоев транзисторов, обрывов входов-выходов и отказов источников питания (четвертая задача изобретения).

На фиг. 5 изображена временная диаграмма работы предлагаемого устройства в отсутствии отказов (для первой и третьей задачи изобретения).

На фиг. 6 изображена временная диаграмма работы предлагаемого устройства в условиях работоспособности всех узлов (для второй и четвертой задачи изобретения).

На фиг. 7 изображена временная диаграмма работы предлагаемого устройства при обрыве входа 3.0 на константу нуля.

На фиг. 8 изображены графики изменения вероятности безотказной (бессбойной) работы прототипа P(t)=e-(12)λ⋅t, вероятности безотказной (бессбойной) работы предлагаемого устройства P(t)ftm, троированного прототипа с одним мажоритаром P3 и троированного прототипа с тремя мажоритарами P3.3 при интенсивности отказов (сбоев) λ=10-9 1/час.

На фиг. 9 изображены графики изменения вероятности безотказной (бессбойной) работы прототипа P(t), вероятности безотказной (бессбойной) работы предлагаемого устройства P(t)ftm, троированного прототипа с одним мажоритаром P3 и троированного прототипа с тремя мажоритарами P3.3 при интенсивности отказов (сбоев) λ=10-8 1/час.

На фиг. 10 изображены графики изменения вероятности безотказной (бессбойной) работы прототипа P(t), вероятности безотказной (бессбойной) работы предлагаемого устройства P(t)ftm, троированного прототипа с одним мажоритаром P3 и троированного прототипа с тремя мажоритарами Р33 при интенсивности отказов (сбоев) λ=10-7 1/час.

На фиг. 11 изображены графики изменения вероятности безотказной (бессбойной) работы прототипа P(t), вероятности безотказной (бессбойной) работы предлагаемого устройства P(t)ftm, троированного прототипа с одним мажоритаром P3 и троированного прототипа с тремя мажоритарами P3.3 при интенсивности отказов (сбоев) λ=10-6 1/час.

На фиг. 12 изображены графики изменения вероятности безотказной (бессбойной) работы прототипа P(t), вероятности безотказной (бессбойной) работы предлагаемого устройства P(t)ftm, троированного прототипа с одним мажоритаром P3 и троированного прототипа с тремя мажоритарами Р3.3 при интенсивности отказов (сбоев) λ=10-5 1/час.

На фиг. 13 изображены графики изменения вероятности безотказной (бессбойной) работы прототипа P(t), вероятности безотказной (бессбойной) работы предлагаемого устройства P(t)ftm, троированного прототипа с одним мажоритаром P3 и троированного прототипа с тремя мажоритарами P3.3 при интенсивности отказов (сбоев) λ=10-4 1/час.

На фиг. 14 изображены графики изменения вероятности безотказной (бессбойной) работы прототипа e-(12)λ⋅t, вероятности безотказной (бессбойной) работы предлагаемого устройства P(t)ftm, троированного прототипа с одним мажоритаром P3 и троированного прототипа с тремя мажоритарами P3.3 с учетом интенсивности отказов источника питания 100λ, при интенсивности отказов (сбоев) 1/час.

На фиг. 15 изображены графики изменения вероятности безотказной (бессбойной) работы прототипа e-(12)λ⋅t, вероятности безотказной (бессбойной) работы предлагаемого устройства Р(t)ftm, троированного прототипа с одним мажоритаром P3 и троированного прототипа с тремя мажоритарами Р3.3 с учетом интенсивности отказов источника питания 100λ, при интенсивности отказов (сбоев) λ=10-5 1/час.

На фиг. 16 изображены графики изменения вероятности безотказной (бессбойной) работы прототипа e-(12)λ⋅t, вероятности безотказной (бессбойной) работы предлагаемого устройства Р(t)ftm, троированного прототипа с одним мажоритаром P3 и троированного прототипа с тремя мажоритарами P3.3 с учетом интенсивности отказов источника питания 100λ, при интенсивности отказов (сбоев) λ=10-4 1/час.

На фиг. 17 изображены графики изменения вероятности безотказной (бессбойной) работы прототипа e-(12)λ⋅t, вероятности безотказной (бессбойной) работы предлагаемого устройства P(t)ftm, троированного прототипа с одним мажоритаром P3 и троированного прототипа с тремя мажоритарами P3.3 с учетом интенсивности отказов источника питания 100λ при интенсивности отказов (сбоев) λ=10-7 1/час.

На фиг. 18 изображены графики изменения вероятности безотказной (бессбойной) работы прототипа e-(12)λ⋅t, вероятности безотказной (бессбойной) работы предлагаемого устройства P(t)ftm, троированного прототипа с одним мажоритаром P3 и троированного прототипа с тремя мажоритарами P3.3 с учетом интенсивности отказов источника питания 1000λ, при интенсивности отказов (сбоев) λ=10-7 1/час.

На фиг. 19 изображены графики изменения вероятности безотказной (бессбойной) работы прототипа e-(12)λ⋅t, вероятности безотказной (бессбойной) работы предлагаемого устройства P(t)ftm, троированного прототипа с одним мажоритаром P3 и троированного прототипа с тремя мажоритарами P3.3 с учетом интенсивности отказов источника питания 1000λ при интенсивности отказов (сбоев) λ=10-8 1/час.

На фиг.20 изображены графики изменения вероятности безотказной (бессбойной) работы прототипа e-(12)λ⋅t, вероятности безотказной (бессбойной) работы предлагаемого устройства P(t)ftm, троированного прототипа с одним мажоритаром P3 и троированного прототипа с тремя мажоритарами P3.3 с учетом интенсивности отказов источника питания 1000λ при интенсивности отказов (сбоев) λ=10-9 1/час.

УСТРОЙСТВО РАБОТАЕТ СЛЕДУЮЩИМ ОБРАЗОМ

1. Работа устройства при отсутствии отказов

В этом случае работоспособны все транзисторы, входы, выходы и источники питания из групп (1), (2), (3), (4), (5), (6), (7), (8), (9) и устройство работает аналогично прототипу.

Когда все входы (3), (4) триггера принимают одинаковое значение логического нуля или логической единицы, то на выходы триггера (5) транзисторами из групп (1), (8) или (2), (9) подключается шина питания «+» от источников (6.1) и (6.2) или шина «Ноль вольт» от источников (7.1) и (7.2) соответственно. Если входы (3), (4) имеют разные логические уровни, то на выходах триггера (5) сохраняется текущее состояние. Такое поведение достигается за счет использования обратной связи, выходы триггера подключаются к пятому транзистору из групп (1) и (2), а также к пятой дополнительной подгруппы транзисторов (8.5), (9.5) - см. фиг. 1. Временная диаграмма работы устройства при отсутствии отказов для первой задачи изобретения представлена на фиг. 5, таблица истинности устройства представлена в таблице 1, где Qt - текущее состояние триггера, а Qt-1 это состояние триггера в предыдущий момент времени:

Относительно фиг. 2 для второй задачи изобретения дополнительно к вышеописанному работоспособны резервные входы (3.1), (3.2), (3.3), (4.1), (4.2), (4.3), (5.1), (5.2), (5.3). Временная диаграмма работы устройства при отсутствии отказов для второй задачи изобретения представлена на фиг. 6.

Для фиг. 3 и третьей задачи изобретения дополнительно к описанному для фиг. 1 работоспособны резервные входы подключения шины питания «+» (6.2) и шины «Ноль вольт» (7.2). Временная диаграмма работы устройства при отсутствии отказов для третьей задачи изобретения соответствует фиг. 5.

Для фиг. 4 и четвертой задачи изобретения дополнительно к описанному для фиг. 2 работоспособны резервные входы подключения шины питания «+» (6.2) и шины «Ноль вольт» (7.2). Временная диаграмма работы устройства при отсутствии отказов для четвертой задачи изобретения аналогична фиг. 6.

2. Работа устройства при наличии отказов

2.1. Работа устройства при отказах и сбоях транзисторов p и n-проводимостей для первой задачи изобретения (фиг. 1)

В этом случае допускается отказ (сбой) одного транзистора в каждой четверке транзисторов получаемой в результате объединения транзисторов из групп (1) и (8) или отказ одного из транзисторов в каждой четверке транзисторов получаемой в результате объединения транзисторов из групп (2) и (9).

Соединения каждой группы транзисторов (1.i), (2.i) с соответствующей им подгруппой транзисторов (8.i), (9.i) реализует логические функции вида (1).

Такая функция (1) сохраняет свое значение при отказах и сбоях только одного транзистора в каждой цепочке, то есть при изменении fj1, fj2, fj3, fj4,: замене на константу нуля (3), замене на константу единицы (4), инверсии (5), замене на произвольную функцию (6):

При отказе типа “константа нуля” второго транзистора, соответствующего подфункции fj2 (например, транзистора 8.1.3) получаем выражение (3):

Таким образом, функция сохраняет свое значение f в соответствие с законами алгебры логики.

При отказе типа “константа единицы” первого транзистора, соответствующего подфункции fj1 (например, транзистора 1.1) получаем выражение (4):

Таким образом, функция сохраняет свое значение f в соответствие с законами алгебры логики.

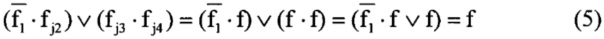

При сбое, когда значение подфункции fj1 соответствующее первому транзистору инвертируется (например, транзистора 1.1) получаем выражение (5):

Таким образом, функция сохраняет свое значение f в соответствие с законами алгебры логики

При отказе типа “произвольная функция” первого транзистора, соответствующего подфункции fj1 (например, транзистора 1.1) получаем выражение (6):

Таким образом, функция сохраняет свое значение f в соответствие с законами алгебры логики

То есть при отказах или сбоях одного транзистора в каждой «четверке», за счет оставшихся трех транзисторов, в которых нет отказа, в соответствие с законами булевой алгебры логики требуемая функция «четверки» f сохраняется, что обеспечивает получение правильных логических уровней на выходе (5). Таким образом, реализуется та же самая временная диаграмма фиг. 5.

2.2. Работа устройства при обрыве входов-выходов для второй задачи изобретения (фиг. 2)

В этом случае допускается обрыв одного входа-выхода из каждой четверки входов-выходов (3), (4), (5).

Например, при обрыве четвертого входа-выхода (x4=0, x1=1, x2=1, x3=1) из формулы (2) получаем выражение (7):

Аналогично при любом другом обрыве одного из четырех входов функция сохраняется и реализуется временная диаграмма фиг. 7.

2.3 Работа устройства при отказах источника питания для третьей задачи изобретения (фиг. 3)

В этом случае введение дополнительных резервных входов подключения шин питания «+» (6.2) и «Ноль вольт» (7.2) совместно с дополнительными транзисторами p и n-проводимости обеспечивает реализацию функции работоспособности вида (8):

То есть при отказе одного из источников питания, например, (s1=0, s2=1, где s - функция работоспособности соответствующего источника питания).

Таким образом, реализуется та же самая временная диаграмма фиг. 5.

Относительно четвертой задачи изобретения (фиг. 4) реализуются временные диаграммы фиг. 6-7.

3. Оценка технико-экономической эффективности

Оценим вероятность безотказной (бессбойной) работы прототипа, имеющего в своем составе 2 группы по 6 транзисторов для экспоненциальной модели отказов:

Для предлагаемого устройства с учетом того, что обеспечивается, как показано выше работоспособность при отказе одного из трех транзисторов в каждой дополнительной подгруппе транзисторов p-проводимости (8.1), (8.2), (8.3), (8.4), (8.5), (8.6) при условии, что нет отказов в соответствующих транзисторах в группе транзисторов p-проводимости; одного из трех транзисторов в каждой дополнительной подгруппе транзисторов n-проводимости (9.1), (9.2), (9.3), (9.4), (9.5), (9.6) при условии, что нет отказов в соответствующих транзисторах в группе транзисторов n-проводимости; одного из транзисторов в группе транзисторов p-проводимости (1); одного из транзисторов в группе транзисторов n-проводимости (2), одного из входов (3), (4), одного из выходов (5), одного из источников питания (6) или (7):

Так, при интенсивности отказов (сбоев) λ=10-5 1/час (здесь и далее в значении λ учитываются, как показатели отказов и сбоев транзисторов, так и линий связей) на допустимом временном интервале при t=2000 часов выигрыш δ(t) составляет:

Сравним выражения (10) и (11) с выражением, описывающим троирование прототипа с одним мажоритаром (всего 12⋅3+10=46 транзисторов, на два меньше, чем в предлагаемом устройстве):

а также с выражением, описывающим троирование прототипа с тремя мажоритарами (всего 12⋅3+10⋅3=66 транзисторов, на 18 больше, чем в предлагаемом устройстве):

Графики сравнения вероятностей (2), (3), (4), (5) для различных интенсивностей отказов (сбоев) представлены на фиг. 8-13.

Так, при интенсивности отказов (сбоев) λ=10-4 1/час при t=100 часов выигрыш δ(t) составляет:

Это более 67% от максимально возможного выигрыша, причем троирование прототипа с одним мажоритаром даже хуже не троированной схемы уже на начале временного интервала, а в его конце хуже становится и троированная схема с тремя мажоритарами.

Оценим вероятности безотказной работы с учетом возможных отказов ИП. При мажоритировании отказ источника питания приводит к отказу всего канала, следовательно, мы можем учесть интенсивность сбоев ИП в общей интенсивности отказов (сбоев) всего канала:

Графики сравнения вероятностей безотказной работы представлены на фиг. 11-17.

Достижение технического результата изобретения подтверждается приведенными оценками.

Список литературы

[1] Yancey S., Smith S. С.A differential design for C-elements and NCL gates // Circuits and Systems (MWSCAS), 2010 53rd IEEE International Midwest Symposium on, vol., no. - 2010. - T. 632. - P. 1-4.

[2] Ю.А. Степченков, A.H. Денисов, Ю.Г. Дьяченко, Ф.И. Гринфельд, О.П. Филимоненко, Н.В. Морозов, Д.Ю. Степченков. Библиотека элементов для проектирования самосинхронных полузаказных микросхем серий 5503/5507 и 5508/5509 - М.: ИПИ РАН, 2008. - 238 с. (функциональная схема гистерезисного триггера представлена на стр. 91).

Реферат

Изобретение относится к области автоматики и вычислительной техники. Технический результат - повышение надежности гистерезисного триггера, используемого в самосинхронных схемах для построения индикатора окончания в них переходных процессов за счет реализации отказо- и сбоеустойчивости; относительно отказов и сбоев транзисторов; относительно обрывов проводов входов-выходов; относительно отказов источника питания, а также за счет интегрированной отказо- и сбоеустойчивость относительно отказов и сбоев транзисторов, обрывов проводов входов-выходов и отказов источника питания. Поставленная цель достигается тем, что гистерезисный триггер содержит группы из транзисторов p-проводимости, группы из транзисторов n-проводимости, вход подключения шины «+» питания, вход подключения шины «Ноль вольт», резервный вход для подключения шины питания «+», резервный вход для подключения шины «Ноль вольт», три резервных входа для первого входа триггера и три резервных входа для второго входа триггера, три резервных выхода триггера. 4 н.п. ф-лы, 1 табл., 20 ил.

Комментарии