Способ передачи и приема дискретных сообщений и устройство для его осуществления - RU2014736C1

Код документа: RU2014736C1

Чертежи

Описание

Изобретение относится к электросвязи и может быть использовано при передаче дискретной информации по волоконно-оптическим линиям связи.

Цель изобретения - уменьшение времени передачи и приема дискретных сообщений путем использования безизбыточного линейного кода.

Сущность способа передачи и приема дискретных сообщений состоит в том, что на передающей и приемной сторонах подсчитывается текущая цифровая сумма D, определяемая как алгебраическая сумма амплитуд символов, передаваемых в канал, причем нулю соответствует минус единица, а единице - плюс единица, при D= -1, 0 +1 входной информационный сигнал передается в канал без изменений, при D= -2 входной информационный сигнал передается в канал инверсно, причем если в канал передан ноль, то цифровая текущая сумма обнуляется D=0, при D=+2 информационный сигнал передается также инверсно, но текущая цифровая сумма обнуляется D=0, если в канал была передана единица, а на приемной стороне преобразование входного сигнала осуществляют также, как и на передающей стороне, только преобразованный сигнал передается не в канал, а потребителю.

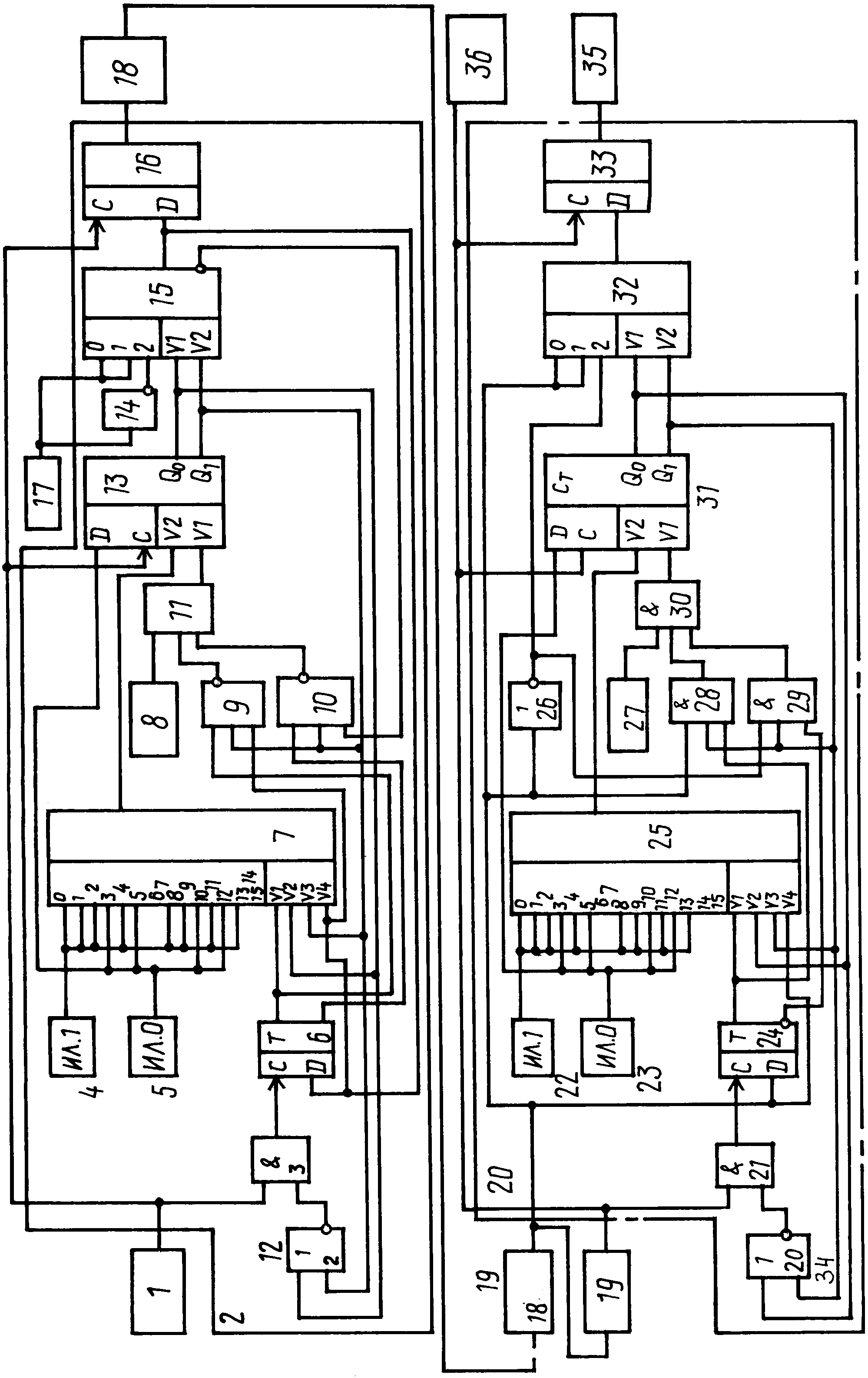

На чертеже представлена структурная электрическая схема устройства, реализующего способ передачи и приема дискретных сообщений.

Устройство для реализации способа передачи и приема дискретных сообщений содержит на передающей стороне источник синхросигнала 1, кодер 2, в состав которого входят элемент 2И 3, источники 4 и 5 логической единицы и логического нуля (лог. "1" и "0") триггер знака 6, мультиплексор 7 управления реверсом, блок начальной установки 8, первый и второй элементы 3И - НЕ 9, 10, элемент 3И 11, элемент 2ИЛИ-НЕ 12, реверсивный счетчик 13, инвертор 14, информационный мультиплексор 15 и D-триггер 16, а также источник 17 цифрового сигнала и согласующий блок 18, а на приемной стороне - согласующий блок 19, декодер 20, в состав которого входят элемент 2И 21, источники 22 и 23 лог. "1" и "0", триггер знака 24, мультиплексор 25 управления реверсом, инвертор 26, блок начальной установки 27, первый и второй элементы 3И-НЕ 28, 29, элемент 3И 30, реверсивный счетчик 31, информационный мультиплексор 32, D-триггер 33 и элемент 2ИЛИ-НЕ 34, а также потребитель 35 цифрового сигнала и потребитель 36 синхросигнала.

Устройство для осуществления способа работает следующим образом.

После включения питания блоки начальной установки 8 и 27 на передающей и приемной сторонах вырабатывают отрицательные импульсы, которые обнуляют посредством параллельной загрузки с входа нуля реверсивные счетчики 13 и 31, после этого устройство устанавливается в рабочий режим. Триггеры знака 6 и 24 при нулевом состоянии реверсивных счетчиков 13 и 31 получают разрешение на запись от дешифраторов, собранных на элементах 2ИЛИ-НЕ 12 и 34. Первый бит, который прошел после нулевой суммы D, устанавливает триггеры знака 13 и 31, которые управляют мультиплексорами 7 и 25. Если второй бит не совпал с первым, то мультиплексоры 7 и 25 выдадут на вторые входы управления реверсивных счетчиков 13 и 31 нули, что означает реверсивный счет, т. е. вычитание, а если второй бит совпал с первым, то на вторых управляющих входах реверсивных счетчиков 13 и 31 появится единица, что означает суммирование. Если после нулевой текущей суммы прошла комбинация в канале "00", то при появлении третьего нуля в канале в передающей части во втором элементе 3И-НЕ 10 вырабатывается отрицательный импульс, который подается на первый вход управления реверсивного счетчика 13, а на его второй вход управления с выхода мультиплексора 7 подается единица, что означает обнуление счетчика 13. На приемной стороне в этой ситуации отрицательный импульс сформируется на выходе второго элемента 3И-НЕ 29. Если после нулевой текущей суммы в канале прошла комбинация "11", то при появлении третьей единицы на передающей стороне обнуляющий импульс выдаст первый элемент 3И-НЕ 9, а на приемной стороне - первый элемент 3И-НЕ 28.

Информационные входы мультиплексоров 7 и 25 "зашиты" таким образом, что они учитывают текущее состояние реверсивных счетчиков 13 и 31, их знак суммы на триггерах знака 6 и 24 и бит информации, который находится в канале. Таким образом, благодаря "зашивке" мультиплексоры 7 и 25 управляют реверсивными счетчиками 13 и 31 согласно способу, который реализует данное устройство. Реверсивные счетчики 13 и 31 в свою очередь управляют информационными мультиплексорами 15 и 32, которые кодируют на передающей стороне и раскодируют на приемной стороне.

Реферат

Изобретение относится к электросвязи и может быть использовано при передаче дискретной информации по волоконно-оптическим линиям связи. Сущность изобретения: осуществляется кодирование одного бита входного сообщения одним битом канального сигнала, причем на передающей и приемной сторонах ведется подсчет текущей цифровой суммы Д и в зависимости от ее значения осуществляется преобразование каждого бита входной информации для выдачи в канал или потребителю цифровой информации. Изобретение позволяет обеспечить уменьшение времени передачи и приема дискретных сообщений путем использования безызбыточного линейного кода. 2 с.п.ф-лы, 1 ил.

Комментарии