Твердотельное устройство фиксации изображений, система фиксации изображений и способ возбуждения твердотельного устройства фиксации изображений - RU2420019C1

Код документа: RU2420019C1

Чертежи

Описание

Уровень техники

Область техники, к которой относится изобретение

Настоящее изобретение относится к твердотельным устройствам фиксации изображений, используемым в сканерах, цифровых фотоаппаратах, цифровых видеокамерах и т.д.

Описание предшествующего уровня техники

В последние годы CMOS-датчики изображений широко использовались в цифровых фотоаппаратах, цифровых видеокамерах и модулях камеры, включенных в мобильные телефоны. Технология для интеграции схем аналогово-цифрового преобразования в CMOS-датчик изображений создана с тем, чтобы сокращать число компонентов и потребление энергии. Предложены различные типы CMOS-датчиков изображений, включающих в себя схемы аналогово-цифрового преобразования, и они включают в себя CMOS-датчик изображений со схемой аналогово-цифрового преобразования, предоставляемой для каждого столбца пикселов, называемой столбчатой схемой аналогово-цифрового преобразования.

Эта схема аналогово-цифрового преобразования сравнивает аналоговый сигнал с опорным сигналом. Выложенный патент (Япония) номер 2005-348324 раскрывает технологию для приложения напряжения, имеющего фиксированное значение, к схемам аналогово-цифрового преобразования в качестве опорного сигнала. В этом случае, поскольку стабилизированный ток проходит через оба конца резистивного элемента, включенного в каждую из схем аналогово-цифрового преобразования, которые предусмотрены по отдельности для столбцов, есть простая возможность повышать скорость по сравнению со случаем, в котором опорное напряжение изменяется со временем.

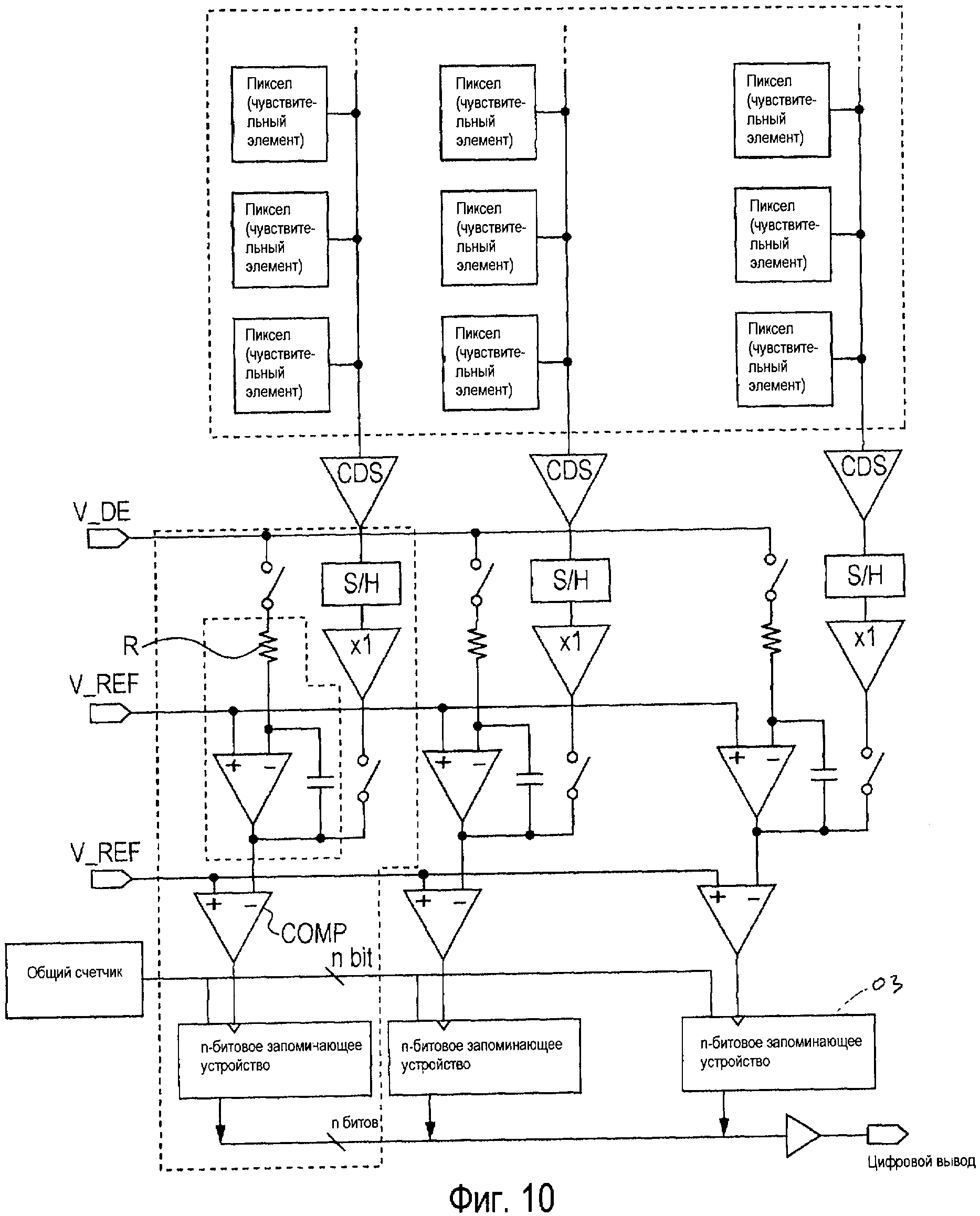

Фиг.10 - это принципиальная схема, иллюстрирующая конфигурацию твердотельного устройства фиксации изображений в предшествующем уровне техники, и она ссылается на фиг.1 выложенного патента (Япония) номер 2005-348324. Для пояснения используются ссылки с номером, отличные от используемых в выложенном патенте (Япония) номер 2005-348324.

Опорное напряжение V_DE, имеющее фиксированное значение, вводится в схемы аналогово-цифрового преобразования, которые предоставляются по отдельности для столбцов. Когда эти схемы аналогово-цифрового преобразования начинают операцию преобразования, стабилизированный ток проходит через оба конца резистора R, включенного в каждую из схем аналогово-цифрового преобразования. Тем не менее, поскольку линии CL для подачи опорного напряжения, имеющего фиксированное значение, имеют значение сопротивления, градиент потенциала возникает в линии CL. Таким образом, поскольку напряжение через оба конца резистора R отличается между столбцами, ток, проходящий через оба конца резистора R, отличается между столбцами.

Даже если операции интеграции по отдельности начинаются в столбцах одновременно и значения аналоговых сигналов, которые должны быть преобразованы в цифровые сигналы в столбцах, являются идентичными, период времени, используемый для инверсии выводов модуля COMP сравнения, может отличаться между столбцами, поскольку значение тока, проходящего через схему аналогово-цифрового преобразования, отличается между столбцами. Соответственно, возникает затенение в направлении вдоль одной строки, из которой выводятся сигналы, которые преобразованы одновременно. Если число столбцов пикселов в твердотельном устройстве фиксации изображений и протяженность линии для подачи опорного напряжения возрастает, это явление становится более явным.

Сущность изобретения

Устройство включает в себя: матрицу пикселов, в которой множество пикселов для вывода аналогового сигнала размещаются в матрице; множество вертикальных выходных линий, каждая из которых подключается к соответствующим из множества пикселов в одном столбце матрицы пикселов; множество модулей аналого-цифрового преобразования, которые по отдельности подключаются к множеству вертикальных выходных линий, выполненных с возможностью преобразовывать аналоговый сигнал в цифровой сигнал; и модуль стабилизированного источника тока, выполненный с возможностью подавать стабилизированный ток во множество модулей аналого-цифрового преобразования. Каждый из множества модулей аналого-цифрового преобразования включает в себя модуль интеграции, выполненный с возможностью интегрировать стабилизированный ток, модуль сравнения, выполненный с возможностью сравнивать интегрированный стабилизированный ток с аналоговым сигналом и выводить сигнал сравнения, и модуль хранения цифровых сигналов, выполненный с возможностью сохранять цифровой сигнал, соответствующий сигналу сравнения. Модуль интеграции включает в себя входной конденсатор, выполненный с возможностью принимать стабилизированный ток от одного своего контактного вывода. Модуль сравнения подключается к модулю стабилизированного источника тока через входной конденсатор.

Дополнительные признаки настоящего изобретения должны стать очевидными из последующего описания примерных вариантов осуществления со ссылкой на прилагаемые чертежи.

Краткое описание чертежей

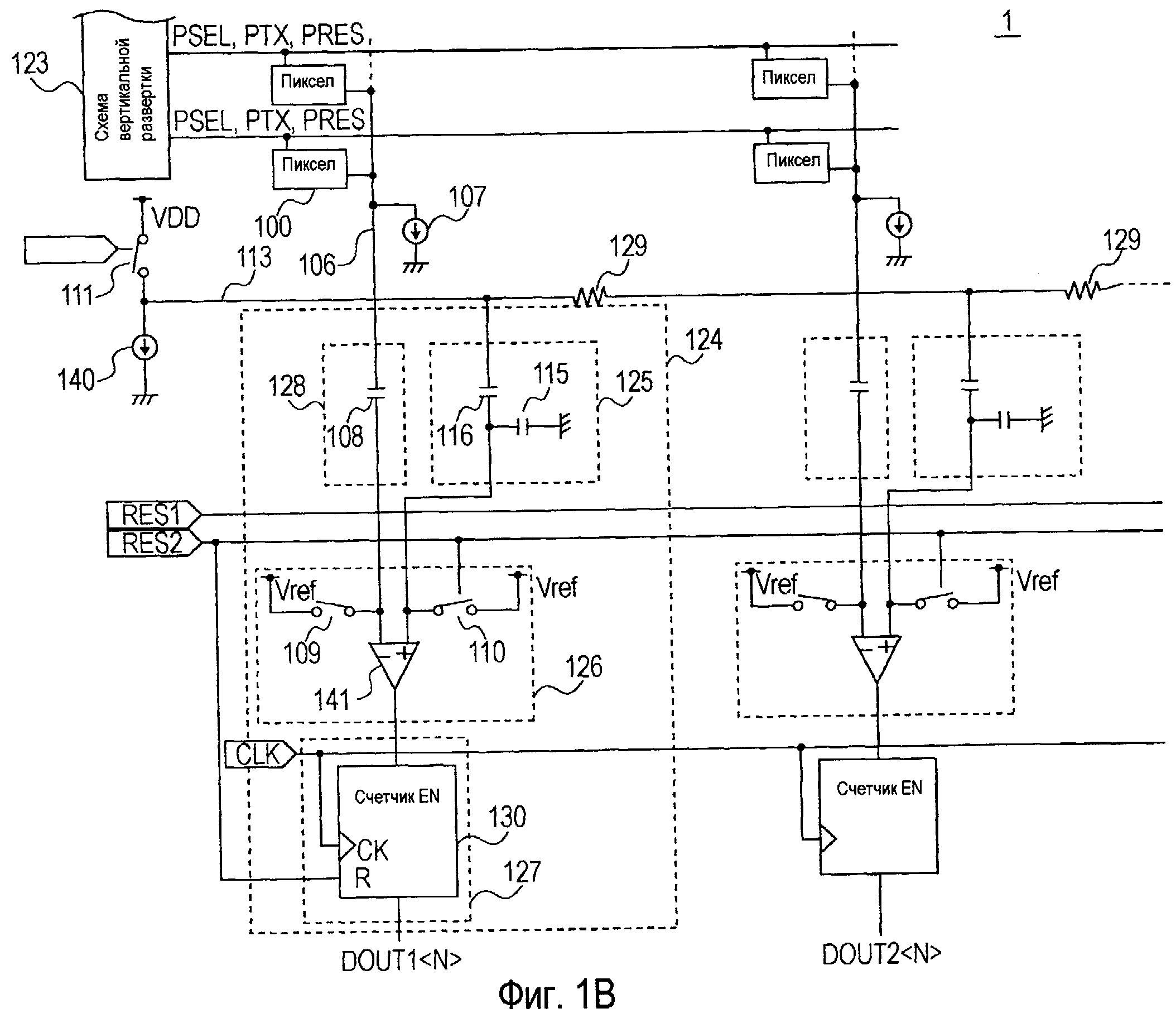

Фиг.1A и 1B являются принципиальными схемами твердотельного устройства фиксации изображений согласно первому варианту осуществления настоящего изобретения.

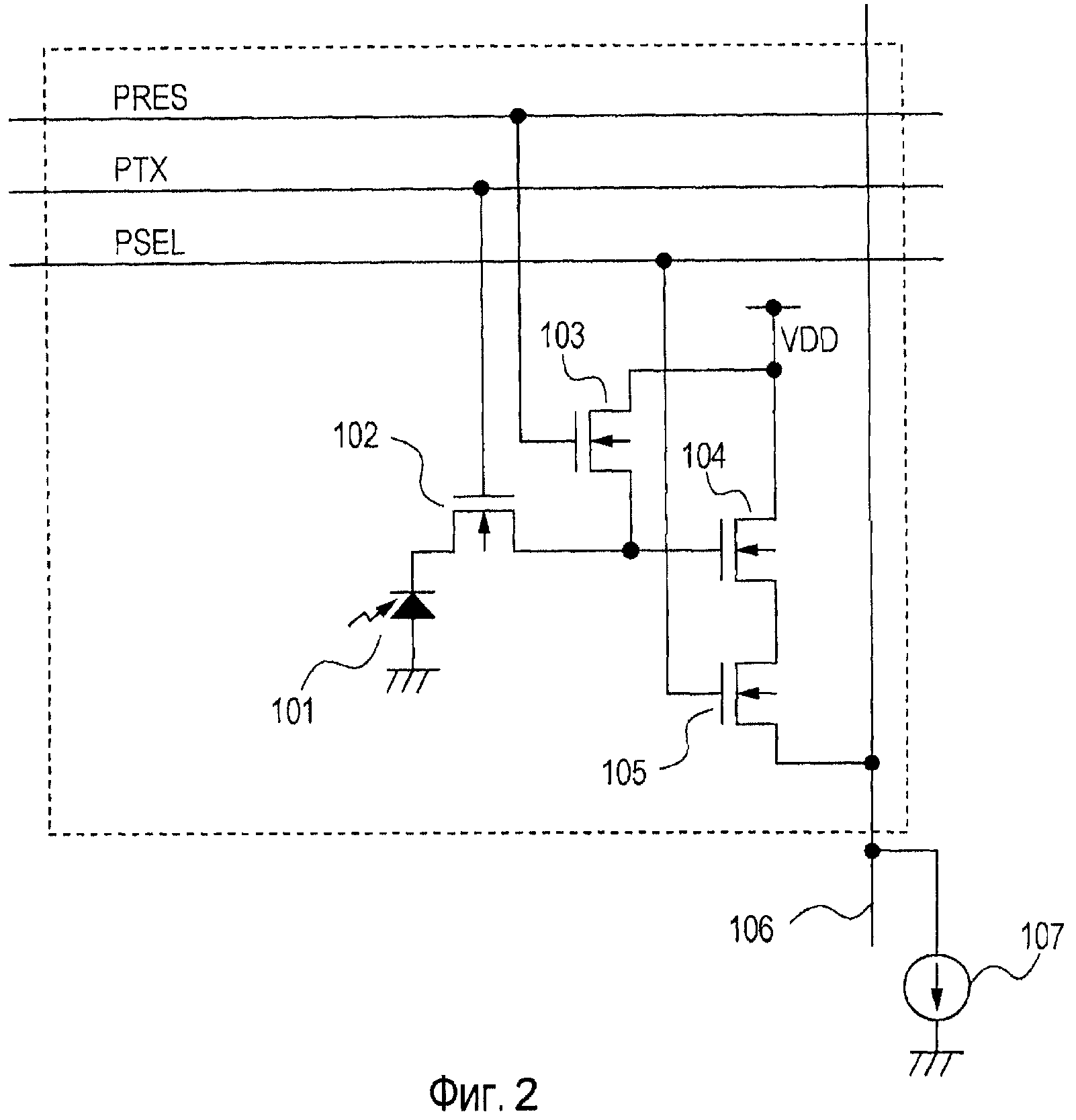

Фиг.2 - это схема, иллюстрирующая примерную конфигурацию пиксела согласно варианту осуществления настоящего изобретения.

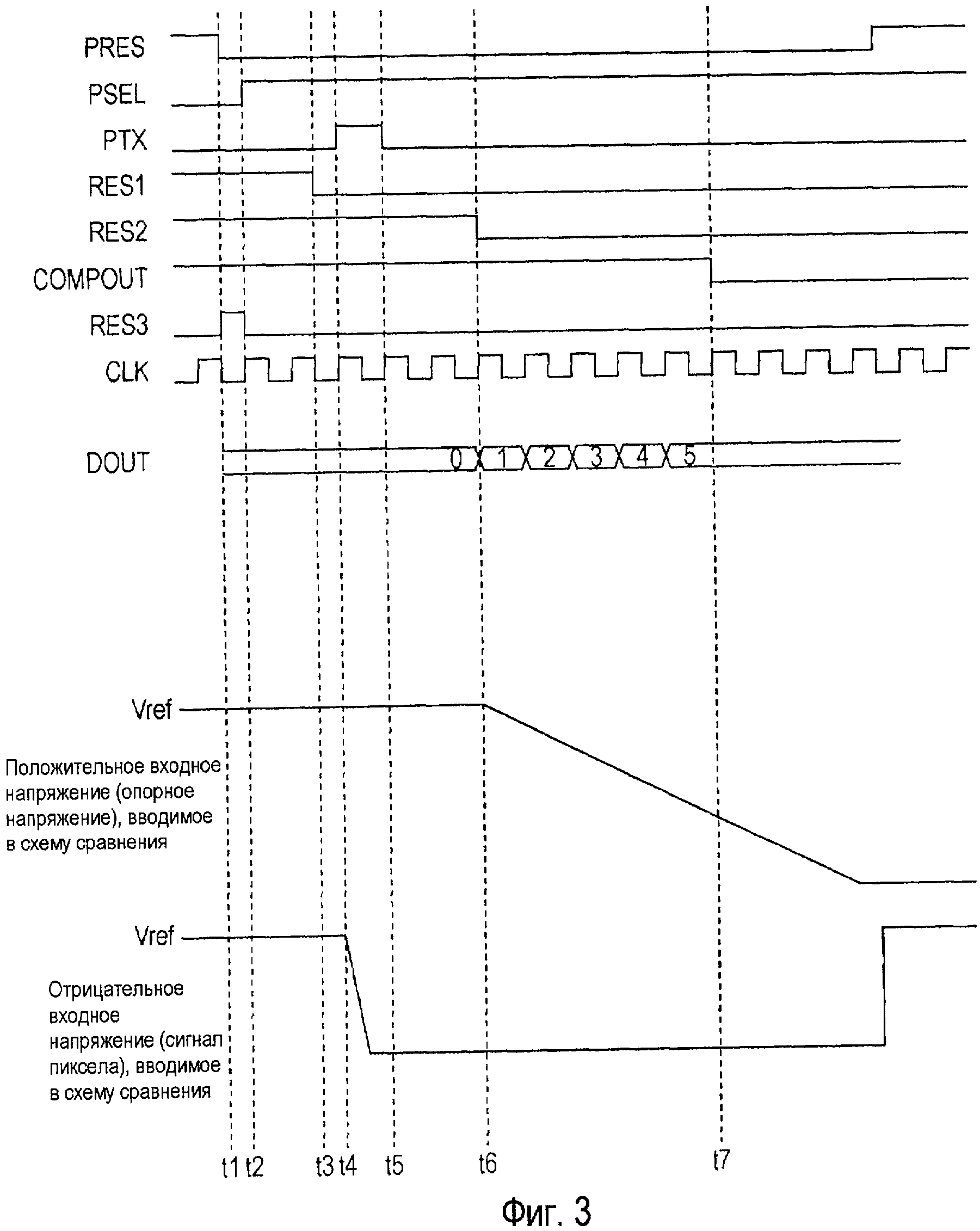

Фиг.3 - это временная диаграмма твердотельного устройства фиксации изображений согласно первому варианту осуществления.

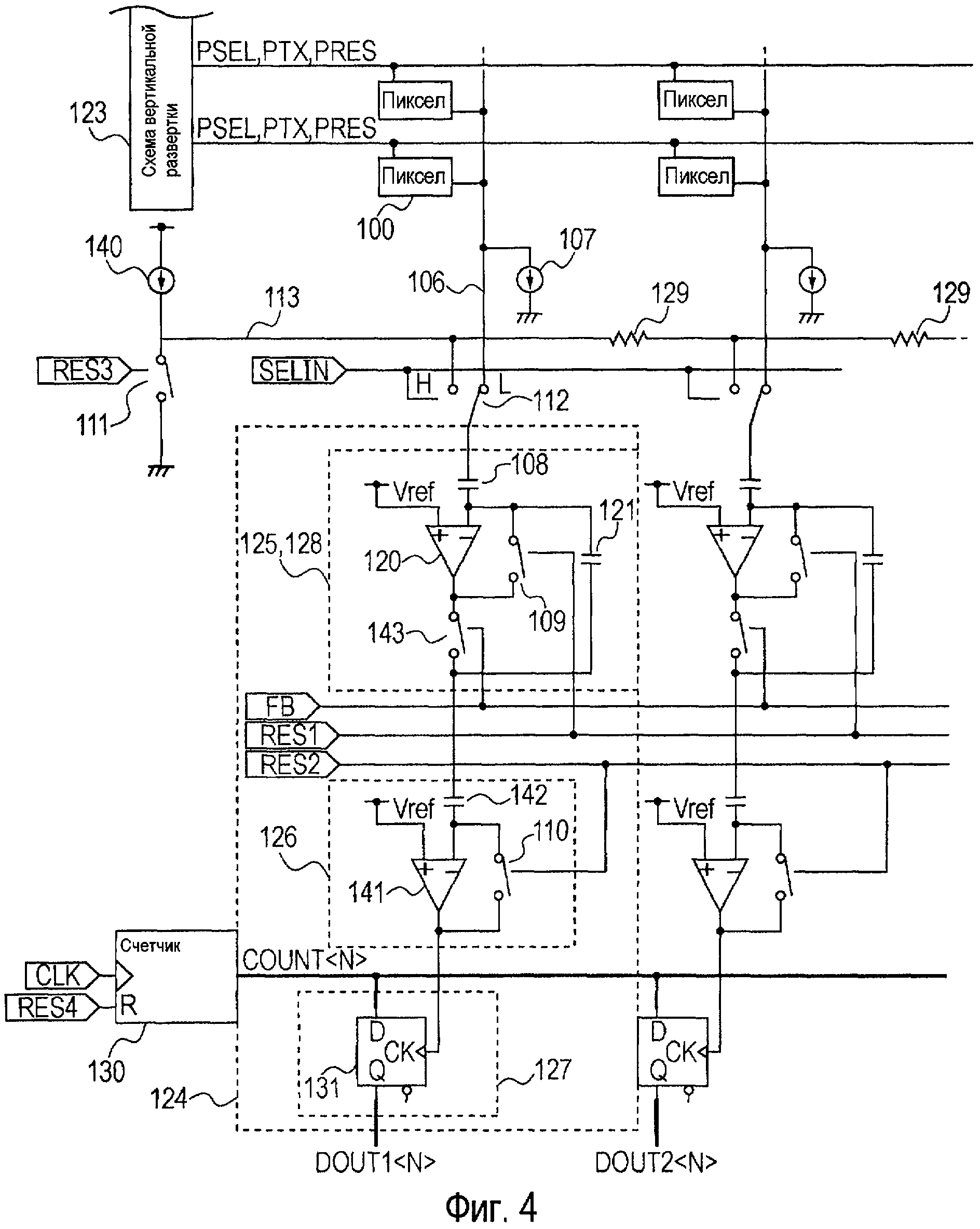

Фиг.4 - это схема, иллюстрирующая примерную конфигурацию твердотельного устройства фиксации изображений согласно второму варианту осуществления настоящего изобретения.

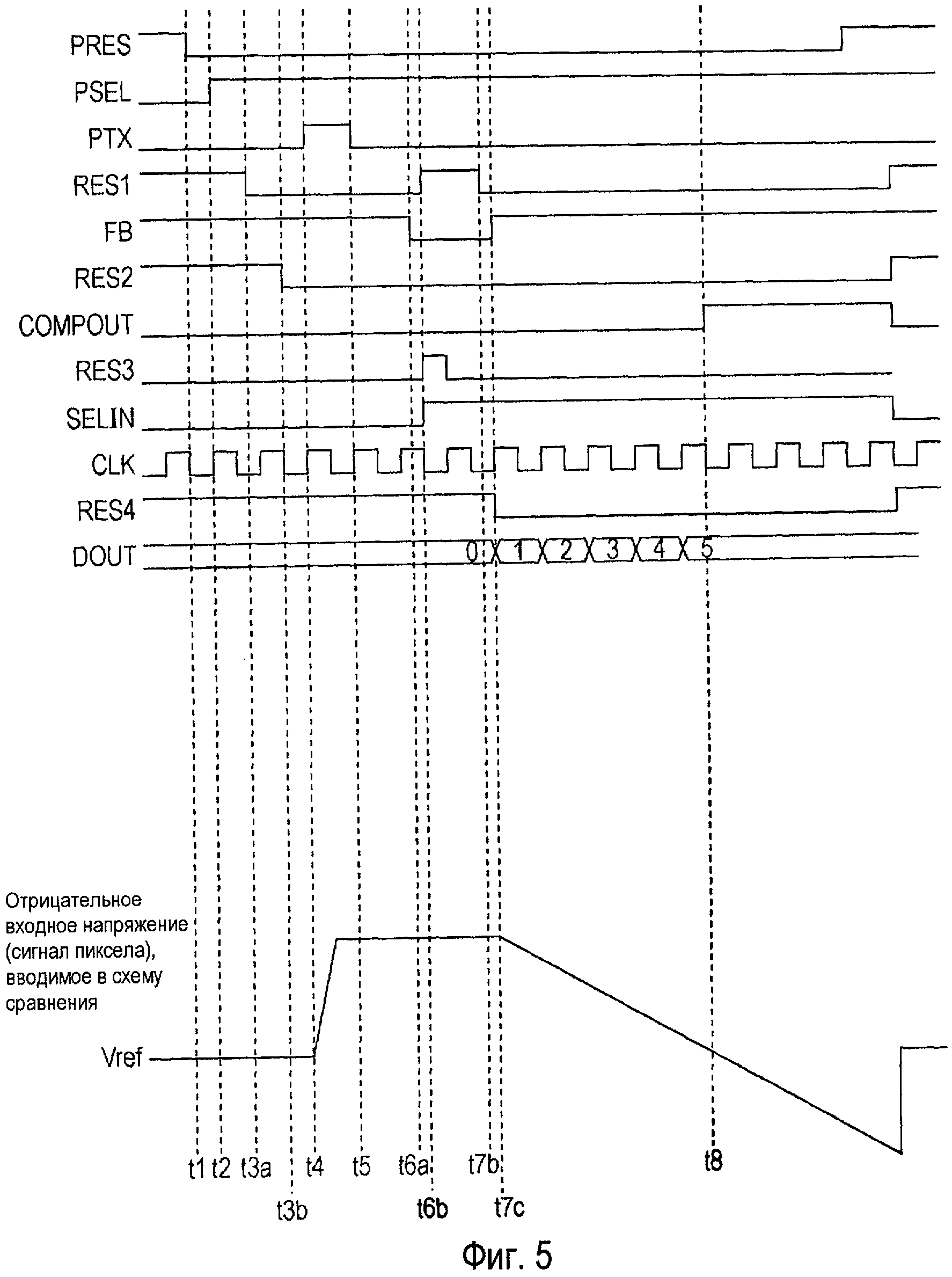

Фиг.5 - это временная диаграмма твердотельного устройства фиксации изображений согласно второму варианту осуществления.

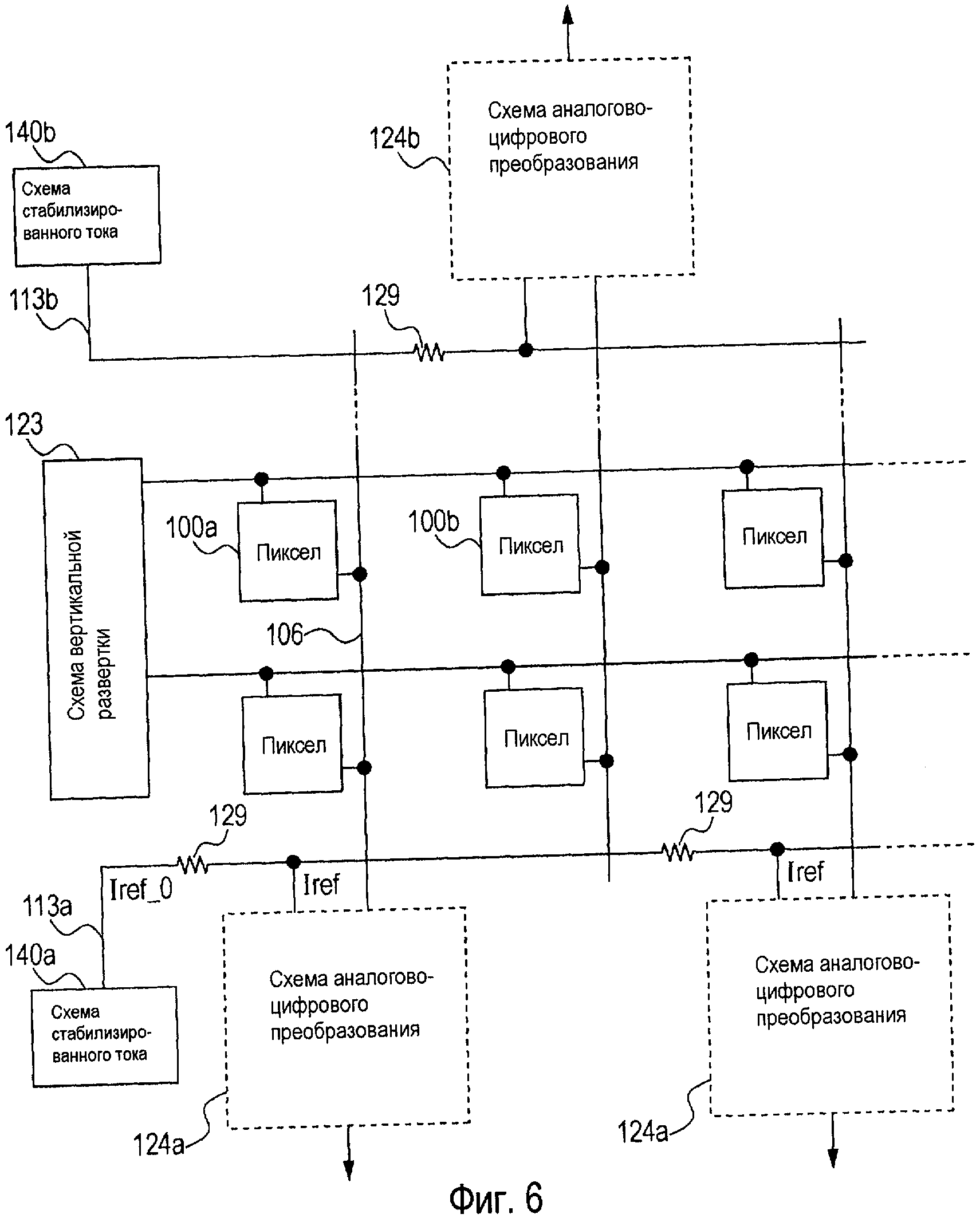

Фиг.6 - это принципиальная схема твердотельного устройства фиксации изображений согласно третьему варианту осуществления настоящего изобретения.

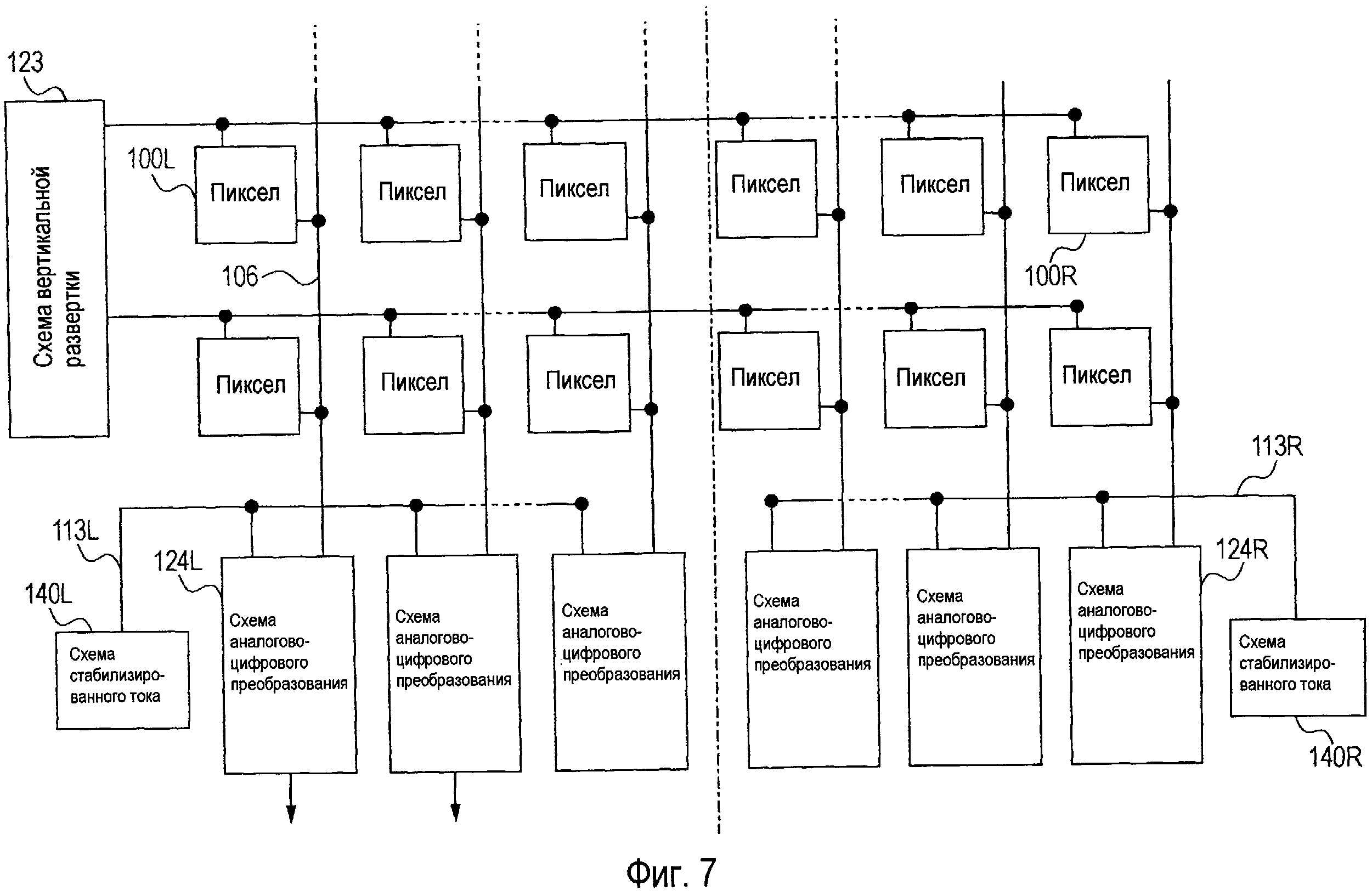

Фиг.7 - это принципиальная схема твердотельного устройства фиксации изображений согласно четвертому варианту осуществления настоящего изобретения.

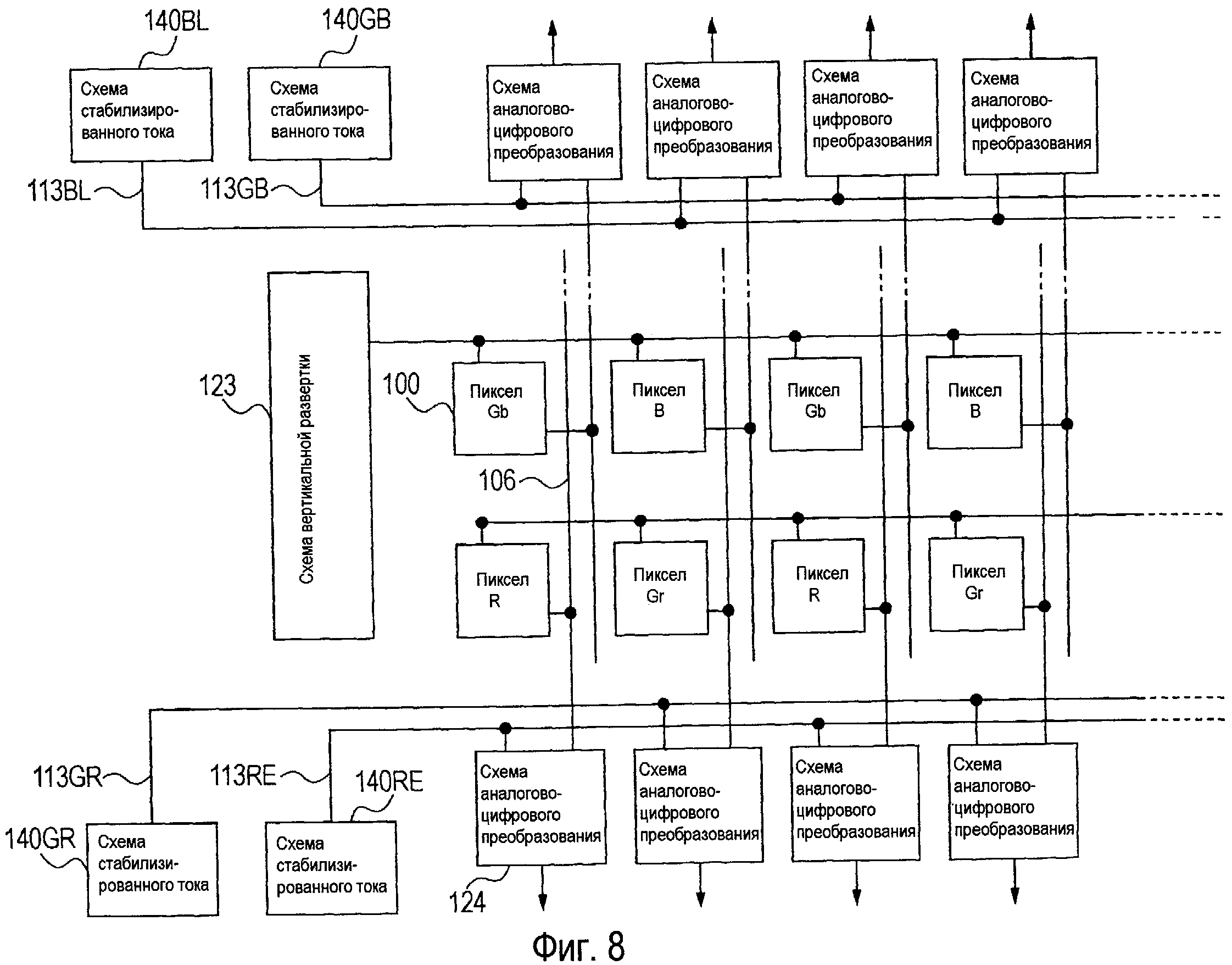

Фиг.8 - это принципиальная схема твердотельного устройства фиксации изображений согласно пятому варианту осуществления настоящего изобретения.

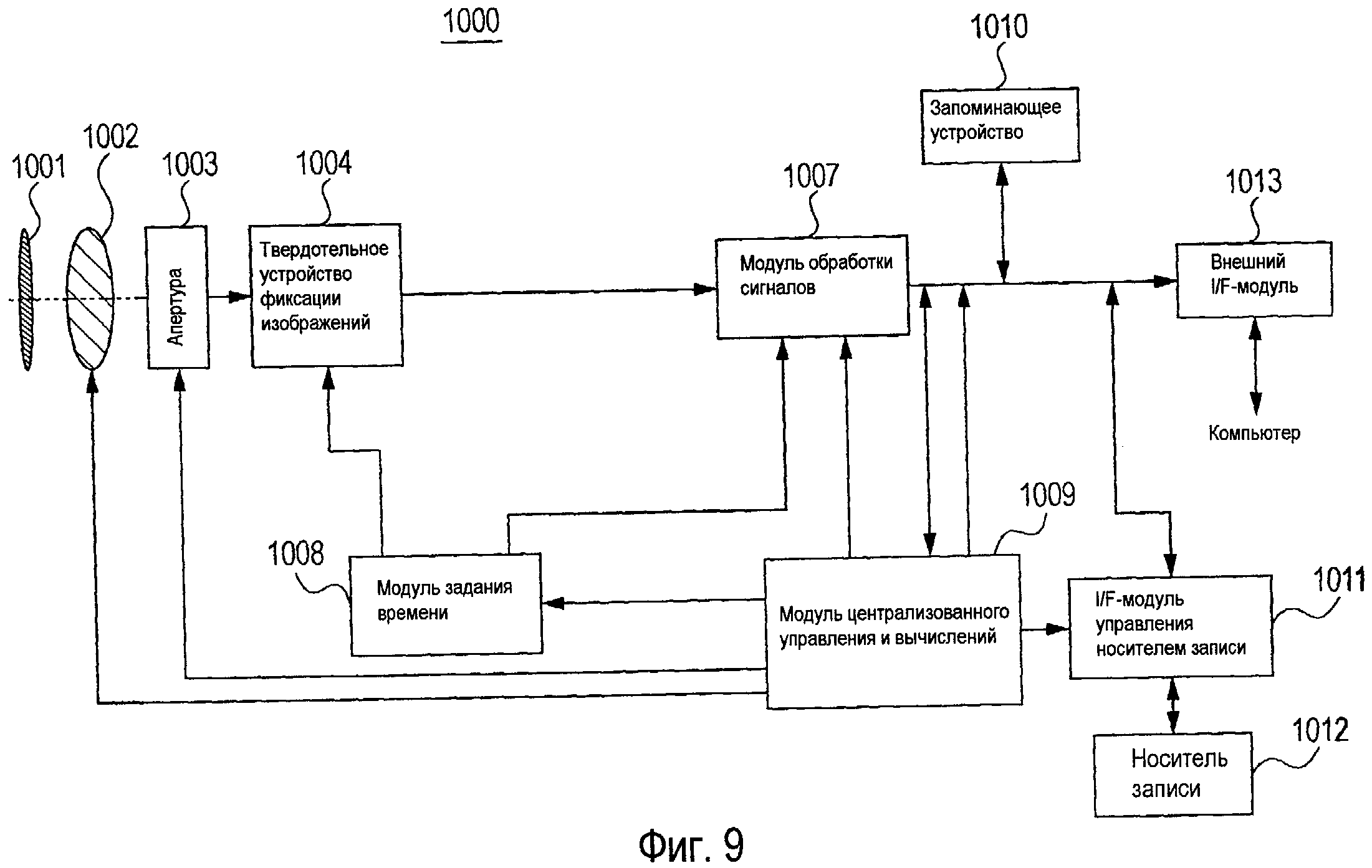

Фиг.9 - это схема, иллюстрирующая примерную конфигурацию твердотельной системы фиксации изображений согласно шестому варианту осуществления настоящего изобретения.

Фиг.10 - это схема, взятая по ссылке из фиг.1 выложенного патента (Япония) номер 2005-348324.

Подробное описание вариантов осуществления

Первый вариант осуществления настоящего изобретения описывается со ссылкой на прилагаемые чертежи.

Фиг.1A - это принципиальная блок-схема твердотельного устройства 1 фиксации изображений согласно первому варианту осуществления настоящего изобретения. Твердотельное устройство 1 фиксации изображений имеет матрицу PA пикселов, в которой пикселы 100 размещаются в матрице. Ссылаясь на фиг.1A, пикселы 100, размещаемые в одном столбце, подключаются к вертикальной выходной линии 106. Схема 123 вертикальной развертки подает общий управляющий сигнал в пикселы 100, размещаемые в одной строке. В ответ на управляющий сигнал, подаваемый из схемы 123 вертикальной развертки, пикселы 100 по отдельности выводят аналоговые сигналы в вертикальные выходные линии 106.

Каждая из вертикальных выходных линий 106 подключается к первому входному контактному выводу схемы 124 аналогово-цифрового преобразования, которая является модулем аналого-цифрового преобразования. Схема 128 обработки аналоговых сигналов для выполнения обработки, такой как уменьшение шума и усиление для аналогового сигнала, выводимого из пиксела 100 в вертикальную выходную линию 106, подключается к первому контактному выводу схемы 124 аналогово-цифрового преобразования. Схема 128 обработки аналоговых сигналов может быть схемой с входным контактным выводом и выходным контактным выводом, замкнутыми накоротко. Выходной контактный вывод схемы 128 обработки аналоговых сигналов подключается к одному входному контактному выводу схемы 126 сравнения, которая является модулем сравнения. Второй входной контактный вывод каждой из схем 124 аналогово-цифрового преобразования подключается к схеме 140 стабилизированного тока, которая является модулем стабилизированного источника тока, через линию 113 подачи опорных сигналов. Кроме того, второй входной контактный вывод каждой из схем 124 аналогово-цифрового преобразования подключается к схеме 125 интеграции, которая является модулем интеграции. Схема 125 интеграции интегрирует ток, подаваемый из схемы 140 стабилизированного тока, и выводит напряжение, которое является результатом интеграции, из своего выходного контактного вывода. Выходной контактный вывод схемы 125 интеграции подключается к другому входному контактному выводу схемы 126 сравнения. Выходной контактный вывод схемы 126 сравнения подключается к схеме 127 хранения цифровых сигналов, которая является модулем хранения цифровых сигналов. После приема сигнала сравнения, выводимого из схемы 126 сравнения, схема 127 хранения цифровых сигналов сохраняет цифровой сигнал. Схема 127 хранения цифровых сигналов выводит из своего выходного контактного вывода цифровой сигнал как результат аналогово-цифрового преобразования, выполняемого посредством схемы 124 аналогово-цифрового преобразования. Цифровые сигналы, выводимые из схем 127 хранения цифровых сигналов, могут выводиться из твердотельного устройства 1 фиксации изображений через общий контактный вывод или различные выходные контактные выводы.

Резистор 129 является паразитным резистором на линии 113 подачи опорных сигналов.

Фиг.2 - это эквивалентная принципиальная схема, иллюстрирующая примерную конфигурацию пиксела 100.

Фотодиод 101 выполняет фотоэлектрическое преобразование в соответствии с падающим светом, и накапливает генерируемый электрический заряд, и имеет катод, подключенный к одному рабочему электроду MOS-транзистора 102 переноса. Другой рабочий электрод MOS-транзистора 102 переноса подключается к одному рабочему электроду MOS-транзистора 103 сброса, а также подключается к управляющему электроду MOS-транзистора 104 усиления. Вывод затвора MOS-транзистора 104 усиления подключается к конденсатору (в дальнейшем называемому FD-конденсатором) плавающего диффузионного (FD) слоя (не проиллюстрирован) (в дальнейшем называемого FD-модулем). Другой рабочий электрод MOS-транзистора 103 сброса подключается к одному рабочему электроду MOS-транзистора 104 усиления, а также подключается к источнику VDD питания. Источник VDD питания и переключатель 111 формируют модуль подачи напряжения. Другой рабочий электрод MOS-транзистора 104 усиления подключается к вертикальной выходной линии 106 через MOS-транзистор 105 выбора. Вертикальная выходная линия 106 подключается к источнику 107 стабилизированного тока.

Когда MOS-транзистор 102 переноса включается в ответ на сигнал PTX, электрический заряд, накопленный в фотодиоде 101, переносится в управляющий электрод MOS-транзистора 104 усиления. Когда MOS-транзистор 103 сброса включается в ответ на сигнал PRES, он сбрасывает потенциал управляющего электрода MOS-транзистора 104 усиления в соответствии с напряжением, подаваемым посредством источника VDD питания. Когда MOS-транзистор 105 выбора включается в ответ на сигнал PSEL, MOS-транзистор 104 усиления и источник 107 стабилизированного тока электрически подключаются друг к другу и управляются как схема истокового повторителя. Когда схема истокового повторителя находится в рабочем режиме, потенциал вертикальной выходной линии 106 изменяется в соответствии с потенциалом затвора MOS-транзистора 104 усиления. Сигналы PTX, PRES и PSEL подаются, например, из схемы 123 вертикальной развертки.

Фиг.1B - это схема, иллюстрирующая подробности твердотельного устройства фиксации изображений, проиллюстрированного на фиг.1A. Схема 128 обработки аналоговых сигналов, проиллюстрированная на фиг.1B, является модулем обработки аналоговых сигналов и включает в себя схему фиксации уровня, включающую в себя фиксирующий конденсатор 108, имеющий один контактный вывод, подключенный к первому контактному выводу схемы 124 аналогово-цифрового преобразования. Схема 125 интеграции включает в себя входной конденсатор 116, имеющий один контактный вывод, подключенный ко второму входному контактному выводу схемы 124 аналогово-цифрового преобразования, и накопительный конденсатор 115, имеющий один контактный вывод, подключенный к другому контактному выводу входного конденсатора 116, и другой контактный вывод, подключенный к земле. Накопительный конденсатор 115 является емкостной нагрузкой в этом узле. Накопительный конденсатор 115 может подключаться к выделенному емкостному элементу или может быть паразитным конденсатором, включающим в себя входной конденсатор модуля 141 сравнения.

Схема 126 сравнения, проиллюстрированная на фиг.1B, включает в себя переключатели 109 и 110 и модуль 141 сравнения. Один контактный вывод модуля 141 сравнения подключается к другому контактному выводу фиксирующего конденсатора 108, а также подключается к источнику Vref опорного напряжения через переключатель 109. Другой контактный вывод модуля 141 сравнения подключается к другому контактному выводу входного конденсатора 116, а также подключается к источнику Vref опорного напряжения через переключатель 110. Переключатель 109 переключается между проводящим состоянием и непроводящим состоянием в ответ на сигнал RES1. Переключатель 110 переключается между проводящим состоянием и непроводящим состоянием в ответ на сигнал RES2. Логическое пороговое значение модуля 141 сравнения является отрицательным значением немного ниже нуля. Соответственно, последующее описание выполняется при допущении, что модуль 141 сравнения с двумя входными контактными выводами, имеющими одинаковый потенциал, выводит сигнал с высоким уровнем.

Схема 127 хранения цифровых сигналов, проиллюстрированная на фиг.1B, включает в себя счетчик 130. Счетчик 130 выполняет операцию счета в синхронизации с опорным тактовым сигналом CLK и завершает или начинает операцию счета в соответствии с сигналом, который выводится из модуля 141 сравнения, и затем вводится во входной контактный вывод EN активации. В ответ на сигнал RES2 счетчик 130 сбрасывает значение счета, сохраненное в нем.

Линия 113 подачи опорных сигналов, проиллюстрированная на фиг.1B, подключается к схеме 140 стабилизированного тока и переключателю 111. Когда переключатель 111 включается в ответ на сигнал RES3, напряжение линии 113 подачи опорных сигналов сбрасывается к напряжению VDD источника питания.

Далее описывается работа твердотельного устройства фиксации изображений, проиллюстрированного на фиг.1B, со ссылкой на фиг.3. Ссылки с номером, предусмотренные для сигнальных импульсов, соответствуют ссылкам, предусмотренным для контактных выводов, проиллюстрированных на фиг.1B и 2. Каждый переключатель, проиллюстрированный на фиг.1B и 2, включается или переводится в проводящее состояние, когда сигнал с высоким уровнем передается в него, и выключается или переводится в непроводящее состояние, когда сигнал с низким уровнем передается в него.

Предполагается, что заранее определенный период времени экспозиции прошел до времени t3, проиллюстрированного на фиг.3, и электрический заряд, полученный из фотоэлектрического преобразования, накапливается в фотодиоде 101. Ссылаясь на фиг.3, COMPOUT обозначает вывод модуля 141 сравнения.

Во время t1 уровень сигнала PRES изменяется с высокого на низкий, так что операция для сброса вывода затвора MOS-транзистора 104 усиления, т.е. FD-модуля, завершается. Как результат, FD-конденсатор, который является конденсатором, включенным в FD-модуль, накапливает напряжение, генерируемое во время сброса FD-модуля, т.е. напряжение темного состояния.

Кроме того, во время t1 уровень сигнала RES3 изменяется на высокий, так что напряжение линии 113 подачи опорных сигналов сбрасывается к напряжению VDD источника питания, которое является фиксированным напряжением. Как результат, напряжение одного контактного вывода входного конденсатора 116, предоставляемого в каждом столбце, сбрасывается к напряжению VDD источника питания.

Во время t2 уровень сигнала RES3 изменяется на низкий. В это время, поскольку линия 113 подачи опорных сигналов подключается только к схеме 140 стабилизированного тока, начинается разрядка из одного контактного вывода входного конденсатора 116, предоставляемого в каждом столбце. Затем, после того как период времени, соответствующий постоянной времени, которая определяется посредством общей суммы значений сопротивления паразитных резисторов 129 на линии 113 подачи опорных сигналов и общей суммы значений емкости входных конденсаторов 116, прошел, ток разрядки, выводимый из одного контактного вывода входного конденсатора 116, предоставляемого в каждом столбце, стабилизируется в установившемся состоянии. В установившемся состоянии градиент потенциала возникает в линии 113 подачи опорных сигналов вследствие паразитных резисторов 129. Тем не менее, если значения емкости входных конденсаторов 116, которые по отдельности предоставляются в столбцах, являются идентичными, идентичная величина тока вытекает из контактных выводов входных конденсаторов 116.

Кроме того, во время t2 уровень сигнала PSEL изменяется на высокий, так что MOS-транзистор 105 выбора переводится в проводящее состояние, и MOS-транзистор 104 усиления, и источник 107 стабилизированного тока формируют схему истокового повторителя. Как результат, вывод в темном состоянии уровня, соответствующего тому факту, что FD-модуль сброшен во время t1, появляется в вертикальной выходной линии 106 и затем вводится в один контактный вывод фиксирующего конденсатора 108.

Во время t3, когда уровень сигнала RES1 изменяется на низкий, переключатель 109 выключается, и уровень, появляющийся в вертикальной выходной линии 106, фиксируется в фиксирующем конденсаторе 108. Поскольку период от времени t1 до времени t3 является достаточно коротким, уровень, зафиксированный во время t3, может обрабатываться как уровень, соответствующий сбросу FD-модуля во время t1.

В период от времени t4 до времени t5 сигнал PTX имеет высокий уровень, тем самым MOS-транзистор 102 переноса включается, и электрический заряд, накопленный в фотодиоде 101, переносится в FD-модуль. Потенциал FD-модуля изменяется в соответствии с величиной перенесенного электрического заряда. Уровень, появляющийся в вертикальной выходной линии 106, изменяется в соответствии с изменением потенциала FD-модуля. В это время, поскольку другой контактный вывод фиксирующего конденсатора 108 находится в электрически плавающем состоянии, только величина изменения от вывода в темном состоянии, который зафиксирован во время t3, вводится в один контактный вывод модуля 141 сравнения. Таким образом, сигнал с пониженным шумом, вызываемым посредством MOS-транзисторов, включенных в каждый из пикселов 100, и пониженным хаотическим шумом, вызываемым посредством сброса FD-модуля, вводится в один контактный вывод модуля 141 сравнения.

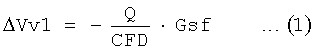

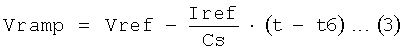

Вышеописанное изменение потенциала описывается с помощью уравнения. Если электрический заряд, перенесенный из фотодиода 101 в FD-модуль, является электроном, абсолютное значение величины электрического заряда составляет Q, а значение емкости FD-модуля составляет CFD, то потенциал FD-модуля понижается на Q/CFD. В ответ на это уровень вертикальной выходной линии 106 изменяется и затем прикладывается к одному контактному выводу фиксирующего конденсатора 108 как вывод светлого состояния. Если усиление схемы истокового повторителя, формируемой посредством MOS-транзистора 104 усиления и источника 107 стабилизированного тока, составляет Gsf, величина изменения ΔVv1 потенциала Vv1 вертикальной выходной линии 106 от вывода в темном состоянии может представляться посредством следующего уравнения:

Поскольку величина изменения потенциала ΔVv1 отправляется в один контактный вывод, т.е. в отрицательный входной контактный вывод модуля 141 сравнения, потенциал отрицательного входного контактного вывода - это значение, полученное из следующего уравнения:

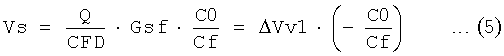

Затем, во время t6, начинается работа аналогово-цифрового преобразования. Во время t6 уровень сигнала RES2 изменяется на низкий, так что переключатель 110 выключается. Как результат, электрический заряд, накопленный в накопительном конденсаторе 115, выводится посредством тока Iref разрядки через входной конденсатор 116 и линию 113 подачи опорных сигналов. Это можно трактовать как имеющее такой же смысл, как интегрирование во времени тока Iref разрядки. Если значения емкости накопительных конденсаторов 115, которые по отдельности предоставляются в столбцах, имеют идентичное значение Cs, потенциал Vramp другого входного контактного вывода, т.е. положительного входного контактного вывода модуля 141 сравнения, понижается на постоянный градиент Iref/Cs. Это означает, что опорный сигнал с градиентом Iref/Cs вводится в модуль 141 сравнения. Потенциал Vramp положительного входного контактного вывода модуля 141 сравнения в определенное время t (время t является временем после времени t6) представляется посредством следующего уравнения как функция от времени t. Далее, Vramp также упоминается как опорное напряжение:

Важным здесь является то, что одинаковый начальный потенциал Vref прикладывается к положительным входным контактным выводам модулей 141 сравнения, которые по отдельности предоставляются в столбцах, во время t6, и одинаковая величина изменения Iref/Cs потенциала положительного входного контактного вывода во времени возникает в этих столбцах. Даже если градиент потенциала возникает в одном контактном выводе входного конденсатора 116 в каждом столбце после того, как уровень сигнала RES3 изменился на низкий во время t2, потенциал, приложенный к положительному входному контактному выводу каждого модуля сравнения как опорный сигнал, не затрагивается посредством градиента потенциала. Соответственно, возникновение затенения в направлении вдоль строки, которое может быть проблемой в предшествующем уровне техники, может подавляться.

Как проиллюстрировано на фиг.1B, сигнал RES2 вводится в контактный вывод R сброса счетчика 130. Соответственно, если уровень сигнала RES2 изменяется на низкий во время t6, исходное состояние счетчика 130 размыкается, и счетчик 130 начинает операцию счета в синхронизации с опорным тактовым сигналом CLK.

Здесь, если период от времени t2, в которое разрядка из одного контактного вывода входного конденсатора 116, т.е. операция интеграции начинается, до времени, в которое операция аналогово-цифрового преобразования начинается, варьируется с периода, соответствующего одному опорному тактовому сигналу CLK, до периода, который примерно в десять раз превышает постоянную времени, представляемую посредством значения равного (общая сумма значений паразитных резисторов на линии 113 подачи опорных сигналов) × (общая сумма значений входных конденсаторов 116), токи, разряжаемые из входных конденсаторов 116, становятся достаточно равномерными. Соответственно, период от времени, в которое начинается операция интеграции посредством схемы 125 интеграции, до времени, в которое начинается операция аналогово-цифрового преобразования, задается равным периоду, который равен или меньше чем в десять раз превышает постоянную времени линии 113 подачи опорных сигналов, которая включает в себя общую сумму значений входных конденсаторов 116.

Во время t7, уровень опорного напряжения Vramp, приложенного к положительному входному контактному выводу модуля 141 сравнения, становится ниже уровня сигнала Vsig, вводимого в отрицательный входной контактный вывод модуля 141 сравнения, уровень сигнала COMPOUT сравнения, который является выводом модуля 141 сравнения, изменяется с высокого на низкий. Сигнал COMPOUT сравнения вводится во входной контактный вывод EN активации счетчика 130. Соответственно, если уровень сигнала COMPOUT сравнения изменяется на низкий, счетчик 130 прекращает операцию счета при сохранении последнего значения счетчика. В это время вывод DOUT счетчика, полученный из счетчика 130, является значением счетчика, соответствующим сигналу, представляемому посредством Уравнения (1). Таким образом, счетчик 130 имеет функцию сохранения цифрового сигнала, соответствующего аналоговому сигналу, выводимому из пиксела 100.

Как описано ранее, в твердотельном устройстве фиксации изображений согласно первому варианту осуществления настоящего изобретения можно подавать равномерный опорный сигнал в модули 141 сравнения, которые по отдельности предоставляются в столбцах, без воздействия от градиента потенциала, который возникает в линии 113 подачи опорных сигналов. Соответственно, можно подавлять возникновение затенения в направлении вдоль строки, которое может быть проблемой в предшествующем уровне техники.

В этом варианте осуществления описывается примерный случай, в котором шесть пикселов 100 размещаются в матрице, имеющей две строки и три столбца. Тем не менее, число пикселов 100, включенных в матрицу PA пикселов, не ограничено таким образом. Кроме того, конфигурация пикселов 100 не ограничена конфигурацией, представленной посредством примерной схемы замещения, проиллюстрированной на фиг.2.

Кроме того, в этом варианте осуществления напряжение линии 113 подачи опорных сигналов сбрасывается к напряжению VDD источника питания, которое является фиксированным напряжением, и затем потенциал линии 113 подачи опорных сигналов понижается посредством схемы 140 стабилизированного тока. Тем не менее, полярность линии 113 подачи опорных сигналов может быть инвертирована. Таким образом, напряжение линии 113 подачи опорных сигналов может быть сброшено к GND, которое является фиксированным напряжением, и затем потенциал линии 113 подачи опорных сигналов может увеличиваться посредством схемы 140 стабилизированного тока.

Далее поясняется второй вариант осуществления настоящего изобретения со ссылкой на фиг.4 и 5.

Фиг.4 - это эквивалентная принципиальная схема, иллюстрирующая примерную конфигурацию твердотельного устройства фиксации изображений согласно второму варианту осуществления настоящего изобретения. Отличие между вторым вариантом осуществления и первым вариантом осуществления состоит в том, что схема 125 интеграции и схема 128 обработки аналоговых сигналов являются интегрированными. Кроме того, схема 127 хранения цифровых сигналов включает в себя N-битовый мультивибратор 131. Счетчик 130 подает общий N-битовый сигнал счетчика в мультивибраторы 131, которые по отдельности предоставляются в столбцах. В первом варианте осуществления напряжение VDD источника питания прикладывается к линии 113 подачи опорных сигналов и затем потенциал линии 113 подачи опорных сигналов понижается посредством схемы 140 стабилизированного тока. В отличие от этого, в этом варианте осуществления, потенциал линии 113 подачи опорных сигналов сбрасывается к GND и затем увеличивается посредством схемы 140 стабилизированного тока. Кроме того, входная секция модуля интеграции подключается к вертикальной выходной линии 106 или линии 113 подачи опорных сигналов через переключатель 112.

Хотя логическое пороговое значение модуля 141 сравнения является отрицательным значением немного ниже нуля в первом варианте осуществления, оно является положительным значением немного больше нуля в этом варианте осуществления. Если потенциалы двух входных контактных выводов модуля 141 сравнения являются идентичными, модуль 141 сравнения выводит сигнал с низким уровнем. Если потенциал положительного входного контактного вывода модуля 141 сравнения выше потенциала его отрицательного входного контактного вывода, модуль 141 сравнения выводит сигнал с высоким уровнем.

Работа согласно этому варианту осуществления описывается со ссылкой на фиг.5. Конфигурация пиксела 100 согласно этому варианту осуществления является идентичной конфигурации пиксела 100 согласно первому варианту осуществления, которая проиллюстрирована в эквивалентной принципиальной схеме на фиг.2. Предполагается, что заранее определенный период времени экспозиции прошел до времени t4, и электрический заряд, полученный из фотоэлектрического преобразования, накапливается в фотодиоде 101. Ссылаясь на фиг.5, COMPOUT обозначает выход модуля 141 сравнения.

Во время t1 уровень сигнала PRES изменяется с высокого на низкий, так что операция для сброса вывода затвора MOS-транзистора 104 усиления, т.е. FD-модуля, завершается. Как результат, FD-конденсатор, который является конденсатором, включенным в FD-модуль, накапливает напряжение, генерируемое во время сброса FD-модуля, т.е. напряжение темного состояния.

Кроме того, во время t1, поскольку уровни сигнала RES1 и сигнала FB являются высокими, оба конца конденсатора 121 обратной связи замкнуты накоротко, и напряжение через конденсатор 121 обратной связи становится нулем.

Во время t2 уровень сигнала PSEL изменяется на высокий, так что MOS-транзистор 105 выбора переводится в состояние проведения, и MOS-транзистор 104 усиления, и источник 107 стабилизированного тока формируют схему истокового повторителя. Как результат, вывод в темном состоянии уровня, соответствующего тому факту, что FD-модуль сброшен во время t1, появляется в вертикальной выходной линии 106 и затем вводится в один контактный вывод фиксирующего конденсатора 108.

Во время t3a уровень сигнала RES1 изменяется на низкий, так что переключатель 109 выключается, и уровень, появляющийся в вертикальной выходной линии 106, фиксируется в фиксирующем конденсаторе 108. Поскольку период от времени t1 до времени t3a является достаточно коротким, уровень, зафиксированный во время t3a, может обрабатываться как уровень, соответствующий сбросу FD-модуля во время t1.

Во время t3b уровень сигнала RES2 изменяется на низкий, так что переключатель 110 выключается, и смещение схемы 125 интеграции фиксируется в конденсаторе 142 подключения.

В период от времени t4 до времени t5 сигнал PTX имеет высокий уровень, тем самым MOS-транзистор 102 переноса включается, и электрический заряд, накопленный в фотодиоде 101, переносится в FD-модуль. Потенциал FD-модуля изменяется в соответствии с величиной перенесенного электрического заряда. Уровень, появляющийся в вертикальной выходной линии 106, изменяется в соответствии с изменением потенциала FD-модуля. В это время, поскольку контактный вывод фиксирующего конденсатора 108, который подключается к инвертирующему входному контактному выводу усилителя 120 вычисления, который является дифференциальным усилителем, находится в электрически плавающем состоянии, только величина изменения от вывода в темном состоянии, который зафиксирован во время t3a, вводится в инвертирующий входной контактный вывод усилителя 120 вычисления. Таким образом, сигнал с пониженным шумом, вызываемым посредством MOS-транзисторов, включенных в каждый из пикселов 100, и пониженным хаотическим шумом, вызываемым посредством сброса FD-модуля, вводится в инвертирующий входной контактный вывод усилителя 120 вычисления.

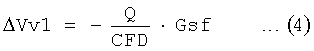

Вышеописанное изменение потенциала подробно описывается с помощью уравнения. Если электрический заряд, перенесенный из фотодиода 101 в FD-модуль, является электроном, абсолютное значение величины электрического заряда составляет Q, а значение емкости FD-модуля составляет CFD, то потенциал FD-модуля понижается на Q/CFD. В ответ на это уровень вертикальной выходной линии 106 изменяется и затем прикладывается к одному контактному выводу фиксирующего конденсатора 108 как вывод светлого состояния. Если усиление схемы истокового повторителя, формируемой посредством MOS-транзистора 104 усиления и источника 107 стабилизированного тока, составляет Gsf, величина изменения ΔVv1 потенциала Vv1 вертикальной выходной линии 106 от вывода в темном состоянии может представляться посредством следующего уравнения:

Величина изменения потенциала ΔVv1 усиливается посредством инвертирующей схемы усиления, формируемой посредством усилителя 120 вычисления, фиксирующего конденсатора 108 и конденсатора 121 обратной связи, и усиленный сигнал Vs накапливается в конденсаторе 121 обратной связи. Усиленный сигнал Vs представляется посредством следующего уравнения:

В Уравнении (5), C0 обозначает значение емкости фиксирующего конденсатора 108, а Cf обозначает значение емкости конденсатора 121 обратной связи. Как очевидно из Уравнения (5), усиление инвертирующей схемы увеличения равно -C0/Cf.

Уровень сигнала FB изменяется на низкий во время t6a, и уровень сигнала RES1 изменяется на высокий во время t6b, так что переключатель 109 включается, и усилитель 120 вычисления управляется как повторитель напряжения. В это время, поскольку выходной контактный вывод усилителя 120 вычисления подключается к узлу A, к которому подключены фиксирующий конденсатор 108, конденсатор 121 обратной связи и инвертирующий входной контактный вывод усилителя 120 вычисления, смещение усилителя 120 вычисления подавляется в узле A. Кроме того, напряжение узла A может быть сброшено к опорному напряжению Vref.

Во время t6b уровень сигнала SELIN изменяется на высокий, так что один контактный вывод фиксирующего конденсатора 108 подключается к линии 113 подачи опорных сигналов через переключатель 112, который является модулем переключателя. Кроме того, во время t6b уровень сигнала RES3 изменяется на высокий, так что линия 113 подачи опорных сигналов и один контактный вывод фиксирующего конденсатора 108 сбрасываются к GND. Когда уровень сигнала RES3 изменяется на низкий и переключатель 111 выключается, начинается процесс зарядки для зарядки фиксирующих конденсаторов 108, которые по отдельности предоставляются в столбцах, с помощью схемы 140 стабилизированного тока. После того как уровень сигнала RES3 изменился на низкий и период, соответствующий постоянной времени, которая определяется посредством произведения общей суммы значений паразитных резисторов 129 на линии 113 подачи опорных сигналов и общей суммы значений фиксирующих конденсаторов 108, прошел, процесс зарядки выполняется в установившемся состоянии. Как описано в первом варианте осуществления, если период от времени, в которое начинается операция интеграции, до времени, в которое начинается операция аналогово-цифрового преобразования, варьируется с периода, соответствующего одному опорному тактовому сигналу CLK, до периода, который примерно в десять раз превышает постоянную времени, представляемую посредством значения, равного (общая сумма значений паразитных резисторов на линии 113 подачи опорных сигналов) × (общая сумма значений входного конденсатора 116), токи, разряжаемые из входных конденсаторов 116, становятся достаточно равномерными.

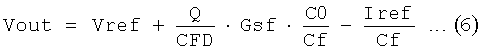

Уровень сигнала RES1 изменяется на низкий во время t7b, и уровень сигнала FB изменяется на высокий во время t7c, переключатель 109 выключается, а переключатель 143 включается. Как результат, схема 140 стабилизированного тока заряжает фиксирующий конденсатор 108 с помощью значения Iref тока постоянно величины. Соответственно, вывод Vout схемы 125 интеграции понижается со временем на постоянный градиент Iref/Cs. Вывод Vout во время t (время t является временем после времени t7c) представляется посредством следующего уравнения:

Во время t7c уровень сигнала RES4 изменяется на низкий, так что исходное состояние счетчика 130 размыкается, и счетчик 130 начинает операцию счета. Значение счетчика, выводимое из счетчика 130, вводится в мультивибраторы 131, которые по отдельности предоставляются в столбцах.

Во время t8 уровень выходного сигнала Vout схемы 125 интеграции понижается ниже уровня источника Vref опорного напряжения, так что уровень выходного сигнала модуля 141 сравнения изменяется с низкого на высокий. Выходной сигнал модуля 141 сравнения вводится в контактный вывод синхросигнала CK мультивибратора 131, и значение счетчика для счетчика 130, получаемое, когда уровень выходного сигнала модуля 141 сравнения изменяется на высокий, защелкивается в мультивибраторе 131. Значение, защелкнутое в мультивибраторе 131 в это время, является цифровым значением, соответствующим аналоговому сигналу, выводимому из пиксела 100.

Согласно этому варианту осуществления, поскольку схема 125 интеграции и схема 128 обработки аналоговых сигналов, которые отдельно расположены в первом варианте осуществления, интегрированы, погрешность усиления между столбцами может уменьшаться. Причина этого заключается в том, что идентичный фиксирующий конденсатор 108 и идентичный конденсатор 121 обратной связи используются в процессе интегрирования тока, подаваемого из схемы 140 стабилизированного тока, и в процессе усиления аналогового сигнала, выводимого из пиксела, и погрешности, вызываемые относительной точностью конденсаторов, следовательно, подавляют друг друга. Соответственно, согласно этому варианту осуществления, может достигаться твердотельное устройство фиксации изображений, допускающее уменьшение погрешности усиления между столбцами и имеющее высокое отношение S/N.

В твердотельном устройстве фиксации изображений согласно этому варианту осуществления, поскольку фиксирующий конденсатор 108 выступает в качестве входного конденсатора 116, описанного в первом варианте осуществления, число элементов, включенных в схему, может уменьшаться. Это является усовершенствованием, в частности, когда столбчатые схемы аналогово-цифрового преобразования включены в твердотельное устройство фиксации изображений, включающее в себя близко расположенные столбцы.

Далее поясняется третий вариант осуществления настоящего изобретения со ссылкой на фиг.6.

Фиг.6 - это принципиальная схема, иллюстрирующая конфигурацию твердотельного устройства фиксации изображений согласно этому варианту осуществления. Твердотельное устройство фиксации изображений согласно третьему варианту осуществления отличается от твердотельных устройств фиксации изображений согласно первому и второму вариантам осуществления тем, что схема 124a аналогово-цифрового преобразования, используемая для пикселов 100a в столбцах с нечетными номерами, включенных в матрицу пикселов, и схема 124b аналогово-цифрового преобразования, используемая для пикселов 100b в столбцах с четными номерами, включенных в матрицу пикселов, располагаются на противоположных сторонах. В этом варианте осуществления доступная область для каждой из схем 124a и 124b аналогово-цифрового преобразования, которые по отдельности предоставляются в столбцах, может в два раза превышать область для каждой схемы аналогово-цифрового преобразования в твердотельных устройствах фиксации изображений согласно первому и второму вариантам осуществления.

Ссылаясь на фиг.6, пикселы 100a в столбцах с нечетными номерами подключаются к соответствующим схемам 124a аналогово-цифрового преобразования, а пикселы 100b в столбцах с четными номерами подключаются к соответствующим из соответствующих схем 124b аналогово-цифрового преобразования. Входные контактные выводы схем 124a аналогово-цифрового преобразования подключаются к схеме 140a стабилизированного тока, а входные контактные выводы схем 124b аналогово-цифрового преобразования подключаются к схеме 140b стабилизированного тока. Таким образом, одна схема стабилизированного тока предоставляется для группы модулей аналого-цифрового преобразования, состоящей из схем 124a аналогово-цифрового преобразования, используемых для пикселов в столбцах с нечетными номерами, и одна схема стабилизированного тока предоставляется для группы модулей аналого-цифрового преобразования, состоящей из схем 124b аналогово-цифрового преобразования, используемых для пикселов в столбцах с четными номерами. Конфигурация схем 124a и 124b аналогово-цифрового преобразования может быть идентична описанной в первом или втором варианте осуществления.

Можно полагать, что линии 113a и 113b подачи опорных сигналов электрически подключаются друг к другу. В этом случае размещается только одна схема стабилизированного тока. Тем не менее, поскольку линия для подключения линий 113a и 113b подачи опорных сигналов предоставлена, постоянные времени этих линий подачи опорных сигналов повышаются.

В отличие от этого, если линии 113a и 113b подачи опорных сигналов отдельно предоставляются и подключаются к схемам 140a и 140b стабилизированного тока соответственно, как проиллюстрировано на фиг.6, постоянные времени этих линий подачи опорных сигналов могут быть понижены. Если постоянные времени понижены, период времени до тех пор, пока процесс зарядки или процесс разрядки не выполнен в установившемся состоянии в схеме интеграции, включенной в схему аналогово-цифрового преобразования, может сокращаться. Это приводит к возрастанию скорости работы.

Фиг.7 - это принципиальная схема, иллюстрирующая конфигурацию твердотельного устройства фиксации изображений согласно четвертому варианту осуществления настоящего изобретения.

В этом варианте осуществления матрица PA пикселов разделена на матрицу пикселов на левой стороне (обозначаемую как "L", например, 100L) и матрицу пикселов на правой стороне (обозначаемую как "R", например, 100R). Таким образом, схема 124L аналогово-цифрового преобразования, используемая для столбца на левой стороне матрицы PA пикселов, и схема 124R аналогово-цифрового преобразования, используемая для столбца справа матрицы PA пикселов, подключаются к различным схемам стабилизированного тока. Как результат, протяженность линии 113 подачи опорных сигналов может уменьшаться приблизительно наполовину по сравнению с первым и вторым вариантами осуществления, и постоянная времени линии подачи опорных сигналов, следовательно, может быть понижена. Соответственно, период времени до тех пор, пока процесс зарядки или процесса разрядки не выполнен в установившемся состоянии посредством схемы стабилизированного тока, может сокращаться. Это приводит к возрастанию скорости работы.

Хотя матрица пикселов разделена на две группы, как проиллюстрировано на фиг.7, она может быть разделена на три или более групп.Кроме того, число схем аналогово-цифрового преобразования, включенных в каждую из групп, на которые разделена матрица пикселов, может варьироваться между группами.

Хотя монохромные твердотельные устройства фиксации изображений описаны в первом-четвертом вариантах осуществления для упрощения пояснения, цветной светофильтр может предоставляться для каждого пиксела.

Фиг.8 - это принципиальная схема, иллюстрирующая конфигурацию твердотельного устройства фиксации изображений согласно пятому варианту осуществления настоящего изобретения.

Ссылаясь на фиг.8, цветной светофильтр Байера предоставляется для пикселов, включенных в матрицу PA пикселов. Gb и Gr указывают, что цветной светофильтр для передачи зеленого света размещен в пикселе, B указывает, что цветной светофильтр для передачи синего света размещен в пикселе, и R указывает, что цветной светофильтр для передачи красного света размещен в пикселе.

В этом варианте осуществления пикселы, в которых размещены цветные светофильтры Gb, Gr, B и R, подключаются к различным схемам аналогово-цифрового преобразования. Фиг.8 иллюстрирует матрицу, включающую в себя две строки. В случае матрицы, включающей в себя три или более строк, пикселы в одном столбце, в котором цветные светофильтры одного цвета по отдельности размещены, подключаются к общей схеме аналогово-цифрового преобразования.

Схемы аналогово-цифрового преобразования, которые по отдельности подключаются к пикселам, в которых размещены цветные светофильтры различных цветов, подключаются к различным схемам стабилизированного тока. Ссылаясь на фиг.8, схема 140GB стабилизированного тока предоставляется для пикселов, в которых размещены цветные светофильтры Gb, и схема 140GR стабилизированного тока предоставляется для пикселов, в которых размещены цветные светофильтры Gr. Кроме того, схема 140BL стабилизированного тока предоставляется для пикселов, в которых размещены цветные светофильтры B, и схема 140RE стабилизированного тока предоставляется для пикселов, в которых размещены цветные светофильтры R. Низкий ток, подаваемый из каждой схемы стабилизированного тока, задается в соответствии с коэффициентом прохождения света, выводимого из эталонного источника света, который задается для цветного светофильтра, размещенного в соответствующем пикселе. Более конкретно, низкий ток, выводимый из каждой схемы стабилизированного тока, регулируется так, чтобы практически одинаковое цифровое значение могло получаться в каждом пикселе, когда фиксируется изображение объекта, освещаемого светом, выводимым из эталонного источника света. Как результат, можно легко обрабатывать сигнал, выводимый из твердотельного устройства фиксации изображений. Это позволяет уменьшать нагрузку на схему обработки сигнала на последующей стадии.

Следует отметить, что линия 113 опорных сигналов обозначается как 113BL, 113GB, 113GR и 113RE для пикселов с цветными светофильтрами B, цветными светофильтрами Gb, цветными светофильтрами Gr и цветными светофильтрами R соответственно.

Фиг.9 - это схема, иллюстрирующая конфигурацию твердотельной системы 1000 фиксации изображений, которая использует твердотельное устройство фиксации изображений согласно любому из вариантов осуществления настоящего изобретения. Шторка 1001 выполняет двойную функцию - как защита для линзы 1002 и основного переключателя. Линза 1002, которая является оптической системой, формирует оптическое изображение объекта на твердотельном устройстве 1004 фиксации изображений. Световой поток, передаваемый через линзу 1002, изменяется посредством апертуры 1003. Твердотельное устройство 1004 фиксации изображений (соответствующее твердотельному устройству фиксации изображений согласно любому из вариантов осуществления) преобразует оптическое изображение, формируемое посредством линзы 1002, в данные изображения. Модуль 1007 обработки сигналов выполняет различные корректировки данных изображения, выводимых из твердотельного устройства 1004 фиксации изображений, и сжимает данные изображения. Модуль 1008 задания времени выводит различные синхронизирующие сигналы в модуль 1007 обработки сигналов. Модуль 1007 обработки сигналов и модуль 1008 задания времени могут быть сформированы на той же микросхеме, на которой сформировано твердотельное устройство 1004 фиксации изображений. Твердотельная система 1000 фиксации изображений включает в себя модуль 1009 централизованного управления и вычислений для выполнения различных вычислений и централизованного управления твердотельной системы 1000 фиксации изображений, запоминающее устройство 1010 для временного сохранения данных изображения и модуль 1011 интерфейса управления носителем записи для записи/считывания данных на/из носителя записи. Кроме того, твердотельная система 1000 фиксации изображений включает в себя носитель 1012 записи, из которого полупроводниковая память и т.п. для записи/считывания данных изображения на/из носителя 1012 записи вынимается, и внешний интерфейсный (I/F) модуль 1013 для обмена данными с внешним компьютером и т.п.

Далее поясняется работа твердотельной системы 1 фиксации изображений, проиллюстрированной на фиг.9. Когда шторка 1001 открыта, основной источник питания, источник питания для системы управления, такой как модуль 1009 централизованного управления и вычислений, и источник питания для схемы системы фиксации изображений, такой как твердотельное устройство 1004 фиксации изображений, включаются в этом порядке.

После этого выполняется операция для управления величиной экспозиции. Модуль 1009 централизованного управления и вычислений открывает апертуру 1003. Сигнал, выводимый из твердотельного устройства 1004 фиксации изображений в это время, вводится в модуль 1007 обработки сигналов. Модуль 1007 обработки сигналов инструктирует модулю 1009 централизованного управления и вычислений выполнять вычисление величины экспозиции на основе сигнала. Модуль 1009 централизованного управления и вычислений обнаруживает яркость объекта на основе результата вычисления и управляет апертурой 1003. Модуль 1009 централизованного управления и вычислений выполняет обнаружение яркости, например, посредством выполнения сравнения с данными, которые сохранены в нем заранее.

Затем, модуль 1009 централизованного управления и вычислений извлекает высокочастотный компонент из сигнала, выводимого из твердотельного устройства 1004 фиксации изображений, вычисляет расстояние до объекта на основе высокочастотного компонента, управляет линзой 1002 и определяет то, находится ли линза 1002 в сфокусированном состоянии. Когда модуль 1009 централизованного управления и вычислений определяет, что линза 1002 не находится в сфокусированном состоянии, это повторно управляет линзой 1002 с тем, чтобы вычислять расстояние. Модуль 1009 централизованного управления и вычислений выполняет определение, например, посредством выполнения сравнения с данными, которые сохранены в нем заранее.

Когда модуль 1009 централизованного управления и вычислений определяет, что линза 1002 находится в сфокусированном состоянии, конечная экспозиция начинается. После того как экспозиция завершена, сигнал изображения, выводимый из твердотельного устройства 1004 фиксации изображений, обрабатывается посредством модуля 1007 обработки сигналов и затем сохраняется в запоминающем устройстве 1010 посредством модуля 1009 централизованного управления и вычислений. Затем данные, сохраненные в запоминающем устройстве 1010, записываются на съемный носитель 1012 записи, такой как полупроводниковая память, через I/F-модуль 1011 управления носителем записи под управлением модуля 1009 централизованного управления и вычислений. Данные могут быть введены напрямую в компьютер и т.п. через внешний I/F-модуль 1013.

Хотя настоящее изобретение описано со ссылкой на примерные варианты осуществления, следует понимать, что изобретение не ограничено раскрытыми примерными вариантами осуществления. Объем нижеприведенной формулы изобретения должен считаться самой широкой интерпретацией, с тем чтобы заключать в себе все модификации, эквивалентные структуры и функции.

Реферат

Изобретение относится к твердотельным устройствам захвата изображений. Техническим результатом является сокращение числа компонентов схем устройства захвата изображений и снижение потребления энергии. Устройство включает в себя матрицу пикселов, в которой пикселы для вывода аналогового сигнала размещаются в матрице, вертикальные выходные линии, каждая из которых подключается к пикселам в одном столбце, модули аналого-цифрового преобразования, которые по отдельности подключаются к вертикальным выходным линиям, для преобразования аналогового сигнала в цифровой сигнал, и модуль стабилизированного источника тока для подачи стабилизированного тока в модули аналого-цифрового преобразования. Каждый из модулей аналого-цифрового преобразования включает в себя модуль интеграции для интеграции стабилизированного тока, модуль сравнения для сравнения интегрированного стабилизированного тока с аналоговым сигналом и вывода сигнала сравнения и модуль хранения цифровых сигналов для хранения цифрового сигнала, соответствующего сигналу сравнения. Модуль интеграции включает в себя входной конденсатор для приема стабилизированного тока. Модуль сравнения подключается к модулю стабилизированного источника тока через входной конденсатор. 4 н. и 9 з.п. ф-лы, 11 ил.

Формула

- матрицу пикселов, в которой множество пикселов для вывода аналогового сигнала размещаются в матрице;

- множество вертикальных выходных линий, каждая из которых подключается к соответствующим из множества пикселов в одном столбце матрицы пикселов;

- множество модулей аналого-цифрового преобразования, которые по отдельности подключаются к множеству вертикальных выходных линий, выполненные с возможностью преобразовывать аналоговый сигнал в цифровой сигнал; и

- модуль стабилизированного источника тока, выполненный с возможностью подавать стабилизированный ток во множество модулей аналого-цифрового преобразования, и

- при этом каждый из множества модулей аналого-цифрового преобразования включает в себя:

- модуль интеграции, выполненный с возможностью интегрировать стабилизированный ток,

- модуль сравнения, выполненный с возможностью сравнивать интегрированный стабилизированный ток с аналоговым сигналом и выводить сигнал сравнения, и

- модуль хранения цифровых сигналов, выполненный с возможностью сохранять цифровой сигнал, соответствующий сигналу сравнения,

- при этом модуль интеграции включает в себя входной конденсатор, выполненный с возможностью принимать стабилизированный ток от одного своего контактного вывода, и

- при этом модуль сравнения подключается к модулю стабилизированного источника тока через входной конденсатор.

- при этом группа модулей аналого-цифрового преобразования предоставляется для соответствующих из множества пикселов, в которых по отдельности размещаются цветные светофильтры одного цвета.

- в котором модуль интеграции начинает операцию интеграции для интеграции стабилизированного тока после того, как модуль подачи напряжения задает напряжение одного контактного вывода входного конденсатора равным фиксированному напряжению, и

- в котором период от времени, в которое начинается операция интеграции, до времени, в которое каждый из множества модулей аналого-цифрового преобразования начинает операцию аналогово-цифрового преобразования,

- это период, который равен или менее чем в десять раз превышает постоянную времени линии подачи опорных сигналов.

- матрицу пикселов, в которой множество пикселов для вывода аналогового сигнала размещаются в матрице;

- множество вертикальных выходных линий, каждая из которых подключается к соответствующим из множества пикселов в одном столбце матрицы пикселов;

- множество модулей аналого-цифрового преобразования, которые по отдельности подключаются к множеству вертикальных выходных линий, выполненных с возможностью преобразовывать аналоговый сигнал в цифровой сигнал; и

- модуль стабилизированного источника тока, выполненный с возможностью подавать стабилизированный ток во множество модулей аналого-цифрового преобразования, и

- в котором каждый из множества модулей аналого-цифрового преобразования включает в себя:

- модуль обработки аналоговых сигналов, подключенный к соответствующей из множества вертикальных выходных линий,

- модуль интеграции, выполненный с возможностью интегрировать стабилизированный ток,

- модуль сравнения, выполненный с возможностью принимать вывод модуля обработки аналоговых сигналов и вывод модуля интеграции, и

- модуль хранения цифровых сигналов, выполненный с возможностью сохранять цифровой сигнал, соответствующий сигналу сравнения, выводимому из модуля сравнения.

- матрицу пикселов, в которой множество пикселов для вывода аналогового сигнала размещаются в матрице;

- множество вертикальных выходных линий, каждая из которых подключается к соответствующим из множества пикселов в одном столбце матрицы пикселов;

- множество модулей аналого-цифрового преобразования, которые по отдельности подключаются к множеству вертикальных выходных линий, выполненных с возможностью преобразовывать аналоговый сигнал в цифровой сигнал;

- модуль стабилизированного источника тока, выполненный с возможностью подавать стабилизированный ток во множество модулей аналого-цифрового преобразования; и

- модуль переключателя, выполненный с возможностью подключать каждый из входных контактных выводов множества модулей аналого-цифрового преобразования к соответствующей из множества вертикальных выходных линий или модулю стабилизированного источника тока, и

- в котором каждый из множества модулей аналого-цифрового преобразования включает в себя модуль интеграции и модуль сравнения, и

- в котором модуль интеграции включает в себя входной конденсатор, имеющий один контактный вывод, подключенный к модулю переключателя, и другой контактный вывод, подключенный к инвертирующему входному контактному выводу дифференциального усилителя.

- устройство по п.1;

- оптическую систему, выполненную с возможностью формировать изображение на матрице пикселов; и

- модуль обработки сигналов, выполненный с возможностью обрабатывать сигнал, выводимый из устройства.

Комментарии