Ранговый фильтр - RU2630395C1

Код документа: RU2630395C1

Чертежи

Описание

Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления, аналоговых процессоров и др.

Известны ранговые фильтры (см., например, фиг. 1 в описании изобретения к патенту РФ 2284650, кл. G06G 7/52, 2006 г.), которые содержат реляторы и реализуют выбор минимального, супраминимального, субмаксимального или максимального из четырех входных аналоговых сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных ранговых фильтров, относятся ограниченные функциональные возможности, обусловленные тем, что не допускается обработка n входных аналоговых сигналов, где n≥4.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип ранговый фильтр (фиг. 1 в описании изобретения к патенту РФ 2284652, кл. G06G 7/52, 2006 г.), который содержит семь реляторов и реализует выбор минимального, супраминимального, субмаксимального или максимального из четырех входных аналоговых сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности, обусловленные тем, что не допускается обработка n входных аналоговых сигналов, где n≥4.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения реализации выбора минимального, супраминимального, субмаксимального или максимального из n входных аналоговых сигналов, где n≥4.

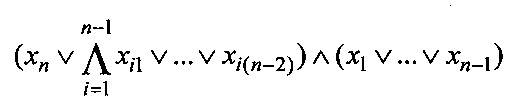

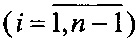

Указанный технический результат при осуществлении изобретения достигается тем, что в ранговом фильтре, содержащем семь реляторов, каждый из которых содержит компаратор, подключенный выходом к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого является входом управления релятора, а выход соединен с управляющим входом замыкающего и размыкающего ключей, выходы которых объединены и образуют выход релятора, первым и вторым входами которого являются соответственно неинвертирующий и инвертирующий входы компаратора, присоединенные соответственно к входам замыкающего и размыкающего ключей, особенность заключается в том, что в него дополнительно введены аналогичные вышеупомянутым реляторы и все реляторы сгруппированы в n+1 (n≥4) групп так, что i-я

На фиг. 1 и фиг. 2 представлены соответственно схема предлагаемого рангового фильтра и схема релятора, использованного при построении указанного фильтра.

Ранговый фильтр содержит реляторы 111,…,1(n+1)n, где n≥4. Каждый релятор содержит компаратор 2, подключенный выходом к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3, второй вход которого является входом управления релятора, а выход соединен с управляющим входом замыкающего и размыкающего ключей 41 и 42, выходы которых объединены и образуют выход релятора, первым и вторым входами которого являются соответственно неинвертирующий и инвертирующий входы компаратора 2, присоединенные соответственно к входам ключей 41 и 42. Все реляторы сгруппированы в n+1 групп так, что i-я

Работа предлагаемого рангового фильтра осуществляется следующим образом. На его первом, втором управляющих входах фиксируются соответственно необходимые управляющие сигналы

где

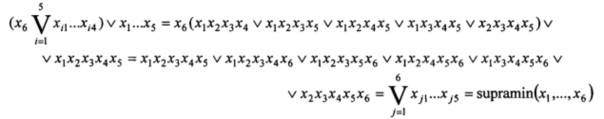

при n=5:

при n=6:

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый ранговый фильтр обладает более широкими по сравнению с прототипом функциональными возможностями, так как реализует выбор минимального, супраминимального, субмаксимального или максимального из n входных аналоговых сигналов, где n≥4.

Реферат

Изобретение относится к автоматике и аналоговой вычислительной технике. Технический результат заключается в расширении функциональных возможностей за счет обеспечения реализации выбора минимального или максимального из n входных аналоговых сигналов, где n≥4. Устройство содержит n×(n-2)+1 реляторов (1,…,1) рангового фильтра, каждый из которых содержит компаратор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, замыкающий и размыкающий ключи. 2 ил.

Формула

Комментарии