Круговой арбитр диспетчера задач - RU2785771C1

Код документа: RU2785771C1

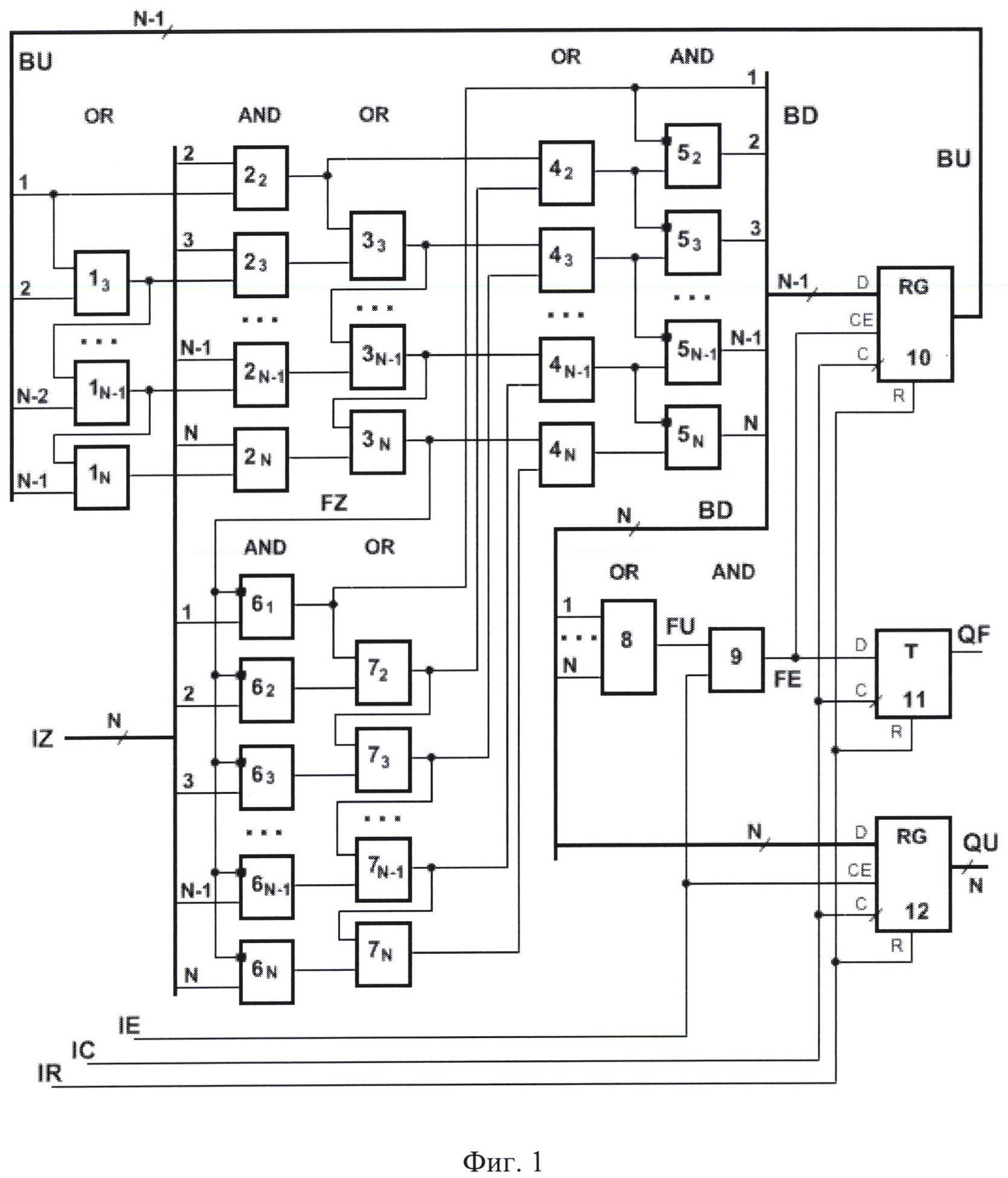

Чертежи

Описание

ОБЛАСТЬ ТЕХНИКИ

Изобретение относится к области вычислительной техники и может быть использовано для арбитража в системах обработки информации при организации обмена данными между устройствами и в многопроцессорных системах обработки информации для распараллеливания потока заявок.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Известен арбитр приоритетов многоранговых запросов (RU №2649948 С1, МПК G06F 13/37, заявлен 15.05.2017, опубликован 05.04.2018, Бюл. №10), содержащий N групп внешних входов запросов IZ1, IZ2,…, IZN, каждая из которых содержит М разрядов ранга приоритета (высший ранг приоритета имеет старший М-ый разряд, старший приоритет имеет старшая группа IZN), первую группу из N внешних выходов указателей группы старшего приоритета U1, U2, …, UN, вторую группу из М внешних выходов указателей высшего ранга приоритета в группе OZ1, OZ2, …, OZM, группу из (N-2) элементов ИЛИ 41, 42, …, 4(N-2), первую группу из (N-1) элементов запрета И с одним инверсным входом 51, 52, …, 5(N-1), группу из М элементов ИЛИ-НЕ 61, 62, …, 6M, вторую группу из (М-1) элементов запрета И с одним инверсным входом 71, 72, …, 7(M-1), инвертор 8 и группу из N блоков каналов анализа приоритета 11, 12, …, 1N, каждый из которых содержит элемент ИЛИ 3 и группу из (М-1) элементов И 21, 22, …, 2(M-1), при этом каждый v-й элемент И 2V (v=1, 2, …, (М-1)) содержит (М-v+l) входов.

В данном устройстве указатель старшей единицы определяется для высшего приоритетного запроса номер ранга и номер группы запросов (канала), соответствующей этому рангу. При анализе запросов ранг запроса имеет высший приоритет и для этого ранга уже определяется соответствующий ему номер канала группы запросов. При этом каждой группе запросов присваивается фиксированный приоритет - старший приоритет присвоен группе запросов со старшим номером IZN, а младший приоритет задан у первой группы запросов IZ1. Кроме того каждая группа запросов содержит М разрядов ранга приоритета. При этом каждому разряду ранга присваивается фиксированный приоритет ранга - высший ранг приоритета присвоен разряду со старшим номером М, а младший ранг приоритета присвоен первому разряду запросов.

Недостатком данного устройства является определение старшинства приоритетов в зависимости от номера ранга приоритета и от номера канала запроса.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятый за прототип, многовыходной указатель старшей единицы (RU №2591017 С1, МПК Н03М 7/22, G06F 13/37, G06F 9/46, заявлен 23.07.2015, опубликован 10.07.2016, Бюл. №19), содержащий группу из N внешних входов запроса Zl, Z2, …, ZN (высший приоритет имеет вход ZN), К каскадов (К - количество формируемых указателей старших единиц) и К групп внешних выходов U указателей старшей единицы, при этом каждый i-й каскад (i=1, 2, …, К) содержит группу из (N-i-1) элементов ИЛИ 1i1, 1i2, …, 1i(N-i-i) и группу из (N-i) элементов запрета И с одним инверсным входом 2i1, 2i2, …, 2i(N-i), а также группу из (N+1-i) входов запроса в i-й каскад Ai1, Ai2, …, Ai(N+1-i) и группу из (N+1-i) внешних выходов указателей старшей единицы i-го ранга Ui1, Ui2, …, Ui(N+1-i) (1-й ранг имеет высший приоритет), каждый из первых (К-1) каскадов, кроме последнего К-го каскада содержит также группу из (N-i) элементов И 3i1, 3i2, …, 3i(N-i) и группу из (N-i) выходов запроса Si1, Si2, …, Si(N-i) в следующий (i+1)-й каскад.

В данном устройстве определяются указатели старшей единицы в К каскадах, при этом каждому входу запроса присваивается фиксированный приоритет - высший приоритет присвоен входу запроса со старшим номером ZN, а младший приоритет задан у первого входа запроса Z1.

Недостатком данного устройства является определение приоритетного указателя старшей единицы для равноранговых запросов в зависимости только от номера текущего запроса в каждом каскаде.

ЗАДАЧА ИЗОБРЕТЕНИЯ

Задача, на решение которой направлено предлагаемое изобретение, заключается в создании устройства предназначенного для выявления приоритетного запроса на основе дисциплины кругового арбитража равноранговых входных запросов.

Техническим результатом изобретения является реализация кругового арбитража для равноранговых входных запросов и указания номера приоритетного запроса в виде унитарного кода «1 из N».

КРАТКОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Указанный технический результат при осуществлении изобретения достигается тем, что круговой арбитр диспетчера задач содержит N разрядные внешнюю шину входных заявок IZ и внешнюю шину выходов указателей приоритета QU, внешний вход разрешения работы IE, внешний тактовый вход IC, внешний вход установки в нулевое состояние IR и внешний флаг запроса QF, а также содержит первую группу из (N-2) элементов ИЛИ 13, 14, …, 1N, первую группу из (N-1) элементов И 22, 23, … 2N, вторую группу из (N-2) элементов ИЛИ 33, 34, …, 3N, третью группу из (N-1) элементов ИЛИ 42, 43, …, 4N, первую группу из (N-1) элементов И с инверсным входом 52, 53, …, 5N, вторую группу из N элементов И с инверсным входом 61, 62, …, 6N, четвертую группу из (N-1) элементов ИЛИ 72, 73, …, 7N, элемент ИЛИ 8, элемент И 9, первый регистр 10, триггер 11, второй регистр 12, внутреннюю N разрядную шину данных BD, внутреннюю (N-1) разрядную шину приоритета BU, внутренний флаг разрешения FE, внутренний флаг запроса FU и внутренний флаг нуля FZ,

причем внешний вход установки в нулевое состояние IR и внешний тактовый вход IC соединены с соответствующими входами R установки в нулевое состояние и тактовыми входами С первого регистра 10, триггера 11 и второго регистра 12, внешний вход разрешения работы IE соединен с входом разрешения работы СЕ второго регистра 12 и вторым входом элемента И 9,

причем все N разрядов внешней шины входных заявок IZ соединены со вторыми прямыми входами одноименных элементов второй группы из N элементов И с инверсным входом 61, 62, …, 6N, а также со второго разряда до N-го разряда внешней шины входных заявок IZ соединены с первыми входами одноименных элементов И первой группы из (N-1) элементов И 22, 23, …, 2N, выходы которых, кроме первого элемента И 22, соединены со вторыми входами одноименных элементов второй группы из (N-2) элементов ИЛИ 33, 34, …, 3N, у которых выходы первых (N-3) элементов ИЛИ 33, 34, …, 3(N-1) соединены с первыми входами соответствующих последующих элементов 34, 35, …, 3N из второй группы элементов ИЛИ, а выход первого элемента И 22 из первой группы из (N-1) элементов И 22, 23, …, 2N соединен с первым входом первого элемента ИЛИ 33 из второй группы элементов ИЛИ и с первым входом первого элемента ИЛИ 42 из третьей группы из (N-1) элементов ИЛИ 42, 43, …, 4N,

кроме того выход последнего N-го элемента ИЛИ 3N из второй группы элементов ИЛИ является внутренним флагом нуля FZ и соединен с первыми инверсными входами всех элементов второй группы из N элементов И с инверсным входом 61, 62, …, 6N, вторые входы элементов четвертой группы из (N-1) элементов ИЛИ 72, 73, …,7N соединены с выходами одноименных элементов 62, 63, …, 6N второй группы элементов И с инверсным входом,

причем выходы первых (N-2) элементов 72, 73, …, 7(N-1) четвертой группы элементов ИЛИ соединены с первыми входами соответствующих последующих элементов 73, 74, …, 7N из четвертой группы элементов ИЛИ, а выход первого элемента И 61 из второй группы из N элементов И 61, 62, …, 6N соединен с первым входом первого элемента ИЛИ 72 из четвертой группы из (N-1) элементов ИЛИ 72, 73, …, 7N и с первым инверсным входом первого элемента И 52 из первой группы из (N-1) элементов И с инверсным входом 52, 53, …, 5N,

кроме того выходы всех элементов четвертой группы из (N-1) элементов ИЛИ 72, 73, …, 7N соединены со вторыми входами соответствующих одноименных элементов ИЛИ 42, 43, …, 4N из третьей группы из (N-1) элементов ИЛИ, а выходы элементов второй группы из (N-2) элементов ИЛИ 33, 34, …, 3N соединены с первыми входами соответствующих одноименных элементов ИЛИ 43, 44, …, 4(N-1) из третьей группы из (N-1) элементов ИЛИ,

причем выходы всех элементов третьей группы из (N-1) элементов ИЛИ 42, 43, …, 4N соединены со вторыми прямыми входами соответствующих одноименных элементов И 52, 53, …, 5N из первой группы из (N-1) элементов И с инверсным входом, а также вторые прямые входы первых (N-2) элементов 52, 53, …, 5(N-1)из первой группы из (N-1) элементов И с инверсным входом соединены с первыми инверсными входами соответствующих последующих элементов И 53, 53, …, 5N из первой группы из (N-1) элементов И с инверсным входом,

кроме того выходы всех элементов И 52, 53, …, 5N первой группы из (N-1) элементов И с инверсным входом являются одноименными разрядами, начиная со второго разряда до N-го разряда, внутренней N разрядной шины данных BD, у которой первый разряд соединен с выходом первого элемента И 61 из второй группы из N элементов И 61, 62, …, 6N,

причем все N разрядов внутренней шины данных BD соединены с соответствующими входами элемента ИЛИ 8 и с группой информационных D-входов второго регистра 12, выходы которого являются N разрядами внешней шины выходов указателей приоритета QU,

причем первые (N-1) разрядов, начиная с первого разряда до (N-l)-го разряда, внутренней шины данных BD соединены с группой информационных D-входов первого регистра 10, выходы которых являются (N-1) разрядами внутренней шины приоритета BU,

кроме того вторые входы всех элементов ИЛИ 13, 14, …, 1N первой группы из (N-2) элементов ИЛИ соединены с соответствующими одноименными разрядами, начиная со второго разряда до (N-l)-го разряда, внутренней шины приоритета BU, а выходы всех элементов ИЛИ 13, 14, …, 1N первой группы из (N-2) элементов ИЛИ соединены со вторыми входами соответствующих одноименных элементов И 23, 24, …, 2N первой группы из (N-1) элементов И 22, 23, …, 2N, а первый разряд внутренней шины приоритета BU соединен со вторым входом первого элемента И 22 из первой группы из (N-1) элементов И 22, 23, …, 2N и соединен с первым входом первого элемента ИЛИ 13 из первой группы из (N-2) элементов 13, 14, …, 1N, а выходы первых (N-3) элементов ИЛИ 13, 14, …, 1(N-1) первой группы элементов ИЛИ соединены с первыми входами соответствующих последующих элементов 14, 15, …, 1N из первой группы элементов ИЛИ,

причем выход элемента ИЛИ 8 является внутренним флагом запроса FU и соединен с первым входом элемента И 9, выход которого является внутренним флагом разрешения FE и соединен с входом разрешения работы СЕ первого регистра 10 и с информационным D-входом триггера 11, выход которого является внешним флагом запроса QF.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

На фиг. 1 представлена схема предлагаемого кругового арбитра диспетчера задач. На фиг. 2 приведена временная диаграмма работы устройства для разрядности N=4 внешней шины входных заявок IZ.

На фиг. 1-2 и в тексте введены следующие обозначения:

IZ - внешняя шина входных заявок, содержащая N разрядов,

IC - внешний тактовый вход,

IE - внешний вход разрешения работы,

IR - внешний вход установки в нулевое состояние,

QF - внешний флаг запроса,

QU - внешняя шина выходов указателей приоритета, содержащая N разрядов,

BD - внутренняя N разрядная шина данных,

BU - внутренняя (N-1) разрядная шина приоритета,

С - тактовый вход,

СЕ - вход разрешения работы,

FE - внутренний флаг разрешения,

FU - внутренний флаг запроса,

FZ - внутренний флаг нуля,

R - вход установки в нулевое состояние,

RG - регистр,

Т - триггер,

13, 14, …, 1N - первая группа из (N-2) элементов ИЛИ (OR),

22, 23, …, 2N - первая группа из (N-1) элементов И (AND),

33, 34, …, 3N - вторая группа из (N-2) элементов ИЛИ (OR),

42, 43, …, 4N - третья группа из (N-1) элементов ИЛИ (OR),

52, 53, …, 5N - первая группа из (N-1) элементов И с инверсным входом (AND),

61, 62, …, 6N - вторая группа из N элементов И с инверсным входом (AND),

72, 73, …, 7N - четвертая группа из (N-1) элементов ИЛИ (OR),

8 - элемент ИЛИ (OR),

9 - элемент И (AND),

10 -первый регистр,

11 - триггер,

12 - второй выходной регистр.

Предлагаемый круговой арбитр диспетчера задач содержит N разрядные внешнюю шину входных заявок IZ и внешнюю шину выходов указателей приоритета QU, внешний вход разрешения работы IE, внешний тактовый вход IC, внешний вход установки в нулевое состояние IR и внешний флаг запроса QF.

Предлагаемый арбитр также содержит первую группу из (N-2) элементов ИЛИ 13, 14, …, 1N, первую группу из (N-1) элементов И 22, 23, …, 2N, вторую группу из (N-2) элементов ИЛИ 33, 34, …, 3N, третью группу из (N-1) элементов ИЛИ 42, 43, …, 4N, первую группу из (N-1) элементов И с инверсным входом 52, 53, …, 5N, вторую группу из N элементов И с инверсным входом 61, 62, …, 6N, четвертую группу из (N-1) элементов ИЛИ 72, 73, …, 7N, элемент ИЛИ 8, элемент И 9, первый регистр 10, триггер 11, второй регистр 12, внутреннюю N разрядную шину данных BD, внутреннюю (N-1) разрядную шину приоритета BU, внутренний флаг разрешения FE, внутренний флаг запроса FU и внутренний флаг нуля FZ.

Причем внешний вход установки в нулевое состояние IR и внешний тактовый вход IC соединены с соответствующими входами R установки в нулевое состояние и тактовыми входами С первого регистра 10, триггера 11 и второго регистра 12. Внешний вход разрешения работы IE соединен с входом разрешения работы СЕ второго регистра 12 и вторым входом элемента И 9.

Причем все N разрядов внешней шины входных заявок IZ соединены со вторыми прямыми входами одноименных элементов второй группы из N элементов И с инверсным входом 61, 62, …, 6N, а также со второго разряда до N-го разряда внешней шины входных заявок IZ соединены с первыми входами одноименных элементов И первой группы из (N-1) элементов И 22, 23, …, 2N, выходы которых, кроме первого элемента И 22, соединены со вторыми входами одноименных элементов второй группы из (N-2) элементов ИЛИ 33, 34, …, 3N. Выходы первых (N-3) элементов ИЛИ 33, 34, …, 3(N-1) соединены с первыми входами соответствующих последующих элементов 34, 35, …, 3N из второй группы элементов ИЛИ. Выход первого элемента И 22 из первой группы из (N-1) элементов И 22, 23, …, 2N соединен с первым входом первого элемента ИЛИ 33 из второй группы элементов ИЛИ и с первым входом первого элемента ИЛИ 42 из третьей группы из (N-1) элементов ИЛИ 42, 43, …, 4N.

Кроме того выход последнего N-го элемента ИЛИ 3N из второй группы элементов ИЛИ является внутренним флагом нуля FZ и соединен с первыми инверсными входами всех элементов второй группы из N элементов И с инверсным входом 61, 62, …, 6N. Вторые входы элементов четвертой группы из (N-1) элементов ИЛИ 72, 73, …, 7N соединены с выходами одноименных элементов 62, 63, …, 6N второй группы элементов И с инверсным входом.

Причем выходы первых (N-2) элементов 72, 73, …, 7(N-1) четвертой группы элементов ИЛИ соединены с первыми входами соответствующих последующих элементов 73, 74, …, 7N из четвертой группы элементов ИЛИ. Выход первого элемента И 61 из второй группы из N элементов И 61, 62, …, 6N соединен с первым входом первого элемента ИЛИ 72 из четвертой группы из (N-1) элементов ИЛИ 72, 73, …, 7N и с первым инверсным входом первого элемента И 52 из первой группы из (N-1) элементов И с инверсным входом 52, 53, …, 5N.

Кроме того выходы всех элементов четвертой группы из (N-1) элементов ИЛИ 72, 73, …, 7N соединены со вторыми входами соответствующих одноименных элементов ИЛИ 43, 43, …, 4N из третьей группы из (N-1) элементов ИЛИ. Выходы элементов второй группы из (N-2) элементов ИЛИ 33, 34, …, 3N соединены с первыми входами соответствующих одноименных элементов ИЛИ 43, 44, …, 4(N-1) из третьей группы из (N-1) элементов ИЛИ.

Причем выходы всех элементов третьей группы из (N-1) элементов ИЛИ 42, 43, …, 4N соединены со вторыми прямыми входами соответствующих одноименных элементов И 52, 53, …, 5N из первой группы из (N-1) элементов И с инверсным входом. Вторые прямые входы первых (N-2) элементов 52, 53, …, 5(N-1) из первой группы из (N-1) элементов И с инверсным входом соединены с первыми инверсными входами соответствующих последующих элементов И 53, 53, …, 5N из первой группы из (N-1) элементов И с инверсным входом.

Кроме того выходы всех элементов И 52, 53, …, 5N первой группы из (N-1) элементов И с инверсным входом являются одноименными разрядами, начиная со второго разряда до N-го разряда, внутренней N разрядной шины данных BD, у которой первый разряд соединен с выходом первого элемента И 61 из второй группы из N элементов И 61, 62, …, 6N.

Причем все N разрядов внутренней шины данных BD соединены с соответствующими входами элемента ИЛИ 8 и с группой информационных D-входов второго регистра 12, выходы которого являются N разрядами внешней шины выходов указателей приоритета QU.

Причем первые (N-1) разрядов, начиная с первого разряда до (N-l)-го разряда, внутренней шины данных BD соединены с группой информационных D-входов первого регистра 10, выходы которых являются (N-1) разрядами внутренней шины приоритета BU.

Кроме того вторые входы всех элементов ИЛИ 13, 14, …, 1N первой группы из (N-2) элементов ИЛИ соединены с соответствующими одноименными разрядами, начиная со второго разряда до (N-l)-го разряда, внутренней шины приоритета BU. Выходы всех элементов ИЛИ 13, 14, …, 1N первой группы из (N-2) элементов ИЛИ соединены со вторыми входами соответствующих одноименных элементов И 23, 24, …, 2N первой группы из (N-1) элементов И 22, 23, …, 2N. Первый разряд внутренней шины приоритета BU соединен со вторым входом первого элемента И 22 из первой группы из (N-1) элементов И 22, 23, …, 2N и соединен с первым входом первого элемента ИЛИ 13 из первой группы из (N-2) элементов 13, 14, …, 1N. Выходы первых (N-3) элементов ИЛИ 13, 14, …, 1(N-1) первой группы элементов ИЛИ соединены с первыми входами соответствующих последующих элементов 14, 15, …, 1N из первой группы элементов ИЛИ.

Причем выход элемента ИЛИ 8 является внутренним флагом запроса FU и соединен с первым входом элемента И 9, выход которого является внутренним флагом разрешения FE и соединен с входом разрешения работы СЕ первого регистра 10 и с информационным D-входом триггера 11, выход которого является внешним флагом запроса QF.

ПОДРОБНОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Принцип работы предлагаемого устройства состоит в следующем.

В устройстве всем сигналам запросов (N разрядам входной шины заявок IZ) установлены равные приоритеты. В начале работы, при инициализации арбитра, высший приоритет установлен для заявки с меньшим номером, поэтому анализ запросов начинается с первого запроса IZ1. Далее арбитр предоставляет приоритет в обслуживании на основе дисциплины круговой диспетчеризации - анализируются запросы с увеличением номеров разрядов шины запросов IZ. При достижении старшего N-го разряда запроса IZN, вновь анализируется первый запрос IZ1 и т.д.

В результате анализа сигналов запросов с шины IZ формируется единичное значение сигнала указателя высшего приоритета, которое по фронту следующего тактового сигнала IC записывается во второй выходной регистр 12 и поступает в виде единичного унитарного кода «1 из N» текущего указателя приоритетного запроса на выходную шину QU. Одновременно формируется единичное значение внешнего флага запроса QF=1 при наличии единичных сигналов запроса. При отсутствии единичных сигналов запроса на шине IZ или нулевом значении на внешнем входе разрешения работы IE=0 нулевые значения устанавливаются во всех N разрядах внешней шины выходов указателей приоритета QU и внешнего флага запроса QF=0.

В процессе работы в первом регистре 10 фиксируется номер последнего разрешенного запроса, а значения с выходов регистра 10 передаются со сдвигом на один разряд в сторону старших разрядов на первую группу 13, 14, …, 1N элементов ИЛИ.

На выходах элементов ИЛИ, объединенных в цепочки, в первой группе 13, 14, …, 1N, второй группе 33, 34, …, 3N и четвертой группе 72, 73, …, 7N коды соответствующих запросов преобразуются в упорядоченную последовательность единичных значений (унитарный позиционный ряд 11…100…0), где правая (младшая) единица соответствует номеру текущего приоритетного запроса. В первой группе 13, 14, …, 1N элементов ИЛИ единичные значения на выходах разрешают передачу следующих запросов, с большими номерами относительно предыдущего приоритетного разряда установленного на первом регистре 10, с входной шины заявок IZ через первую группу элементов И 22, 23, …, 2N, на соответствующие входы второй группы 33, 34, …, 3N элементов ИЛИ.

При отсутствии единичных значений в последующих разрядах, включительно до N-го старшего разряда входной шины заявок IZ, формируется нулевое значение внутреннего флага нуля FZ=0, по которому разрешается передача значений разрядов с шины входных заявок IZ через вторую группу элементов И с инверсным входом 61, 62, …, 6N на соответствующие входы четвертой группе 72, 73, …, 7N элементов ИЛИ. Аналогично в начале работы устройства, когда в первом регистре 10 нулевые значения установлены во всех разрядах, формируется нулевое значение внутреннего флага нуля FZ=0. Поэтому первичная передача значений N разрядов с шины входных заявок IZ осуществляется также через вторую группу элементов И с инверсным входом 61, 62, …, 6N и четвертую группу 72, 73, …, 7N элементов ИЛИ.

Таким образом, через третью группу 42, 43, …, 4N элементов ИЛИ осуществляется передача следующих запросов (в виде унитарного позиционного ряда 11…100…0) с выходов второй группы 33, 34, …, 3N (при FZ=1) или четвертой группы 72, 73, …, 7N элементов ИЛИ (при FZ=0). Далее на выходе только одного элемента из первой группы элементов запрета И с одним инверсным входом 52, 53, …, 5N, на входы которого поданы значения «10», формируется единичное значение, указывающее на следующий приоритетный запрос, а на остальных выходах будет установлено нулевое значение. Значения с выходов первой группы элементов запрета И с одним инверсным входом 52, 53, …, 5N и с выхода первого элемента 61 из второй группы элементов И с инверсным входом 61, 62, …, 6N передаются на соответствующие одноименные N разрядов внутренней шины данных BD в виде единичного унитарного кода «1 из N». При этом младший первый разряд IZ1 с шины входных заявок IZ передается только через вторую группу элементов И с инверсным входом 61, 62, …, 6N и анализируется только в четвертой группе элементов ИЛИ 72, 73, …, 7N.

При наличии единичных значений запросов на шине заявок IZ и формировании единичного унитарного кода «1 из N» на внутренней шине данных BD также формируется единичное значение внутреннего флага запроса FU=1, по которому при единичном значении на внешнем входе разрешения работы IE=1 формируется единичное значение внутреннего флага разрешения FE=1, по которому далее разрешается запись номера разряда текущего приоритета в первый регистр 10 и далее передается на внутреннюю шину приоритета BU. Кроме того значение флага FE записывается в триггер 11 и передается на выход внешнего флага запроса QF, а также при единичном значении на внешнем входе разрешения работы IE=1 значение с внутренней шины данных BD записывается во второй выходной регистр 12 и передается на N разрядов внешней шины выходов указателей приоритета QU.

Предлагаемое устройство работает следующим образом.

На фиг. 2 приведена временная диаграмма работы устройства для разрядности N=4 внешней шины входных заявок IZ.

Устройство начинает работать после подачи единичного сигнала на внешний вход IR установки в нулевое состояние. При этом синхронно по фронту тактового сигнала 1С (момент времени t0, такт 1 на фиг. 2) в нулевое состояние устанавливаются первый 10 и второй 12 регистры и триггер 11. При этом также устанавливаются нулевые значения внешнего флага запроса QF=0, внутреннего флага нуля FZ=0, внутреннего флага запроса FU=0, внутреннего флага разрешения FE=0 и нулевые значения всех разрядов внутренней шины данных BD=0, внутренней шины приоритета BU=0 и внешней шины выходов указателей приоритета QU=0.

Далее на внешнюю шину входных заявок IZ поступают значения N разрядов соответствующих запросов. В момент времени t1 на фиг. 2 поступает код IZ[4-1]=0110, а также устанавливается единичное значение на внешнем входе разрешения работы IE=1. Так как установлено нулевое значение флага нуля FZ=0, то разрешается передача кода IZ[4-1]=0110 через вторую группу элементов И с инверсным входом 61, 62, …, 6N (AND6[4-1]=0110), по которому далее на выходах четвертой группы элементов ИЛИ 72, 73, …, 7N будет установлен код OR7[4-2]=111, который далее через третью группу элементов ИЛИ 42, 43, …, 4N (OR4[4-2]=111) передается на соответствующие входы первой группы элементов И с инверсным входом 52, 53, …, 5N, на выходах которых будет установлен код AND5[4-2]=001, который передается на соответствующие одноименные разряды внутренней шины данных BD, а также в первый разряд передается нулевое значение с выхода первого элемента И 61. Таким образом, на внутренней шине данных BD установлен код BD[4-1]=0010, соответствующий приоритету второго разряда шины входных заявок IZ2. Далее формируется единичное значение внутреннего флага запроса FU=1, по которому при единичном значении на внешнем входе разрешения работы IE=1 формируется единичное значение внутреннего флага разрешения FE=1.

В такте 2 по фронту тактового сигнала IC осуществляется запись с внутренней шины данных BD соответствующего кода в первый регистр 10 и второй регистр 12 и далее передача значений на соответствующие шины BU[3-1]=010 и QU[4-1]=0010, а также при единичном значении флага разрешения FE=1 осуществляется установка в единичное состояние триггера 11 и внешнего флага запроса QF=1. При этом по значениям с внутренней шины приоритета BU[3-1]=010 на выходах первой группы 13, 14, …, 1N элементов ИЛИ устанавливается код 0R1[4-3]=11, по которому разрешается передача значений третьего и четвертого разрядов с шины входных заявок IZ[4-1]=0110 и на выходах первой группы 22, 23, …, 2N элементов И устанавливается код AND2[4-2]=010, в котором установлено нулевое значение запроса от второго разряда IZ2 и единичное значение от третьего разряда IZ3. Далее на выходах второй группы 33, 34, …, 3N элементов ИЛИ устанавливается код OR3[4-3]=ll. При этом устанавливается единичное значение флага нуля FZ=1, по которому запрещается передача значений запросов с шины входных заявок IZ через вторую группу элементов И с инверсным входом 61, 62, …, 6N, на выходах которых устанавливаются нулевые значения (AND6[4-1])=0000 и далее на выходах четвертой группы элементов ИЛИ 72, 73, …, 7N (OR7[4-2]=000). Поэтому на выходах третьей группы элементов ИЛИ 42, 43, …, 4N устанавливается код OR4[4-2]=110 с выходов второй группы 33, 34, …, 3N элементов ИЛИ, по которому на выходах первой группы элементов И с инверсным входом 52, 53, …, 5N устанавливается код (AND5[4-2])=010, который передается на разряды внутренней шины данных BD=0100, соответствующий приоритету следующего третьего разряда шины входных заявок IZ3, так как запрос по второму разряду IZ2 уже был обработан по фронту такта 2. При этом также сохраняются единичные значения внутреннего флага запроса FLN=1 и внутреннего флага разрешения FE=1.

В такте 3 по фронту тактового сигнала IC осуществляется запись с внутренней шины данных BD соответствующих кодов в первый регистр 10 и второй регистр 12 и передача значений на соответствующие шины BU[3-1]=100 и QU[4-1]=0100, а также сохраняется единичное состояние триггера 11 и внешнего флага запроса QF=1. Далее на выходах первой группы 13, 14, …, 1N элементов ИЛИ устанавливается код OR1[4-3]=10, по которому разрешается передача значения четвертого разряда с шины входных заявок IZ4, на котором установлено нулевое значение, поэтому на выходах первой группы элементов И устанавливается код AND2[4-2]=000. При этом устанавливается нулевое значение флага нуля FZ=0, по которому разрешается передача кода IZ[4-1]=0110 через вторую группу элементов И с инверсным входом 61, 62, …, 6N (AND6[4-1]=0110) и далее на выходах четвертой группы элементов ИЛИ 72, 73, …, 7N будет установлен код OR7[4-2]=lll. Далее, аналогично как было приведено после момента времени t1, на внутренней шине данных BD будет установлен код BD[4-1]=0010, соответствующий приоритету второго разряда шины входных заявок IZ2.

В момент времени t2 на внешнюю шину входных заявок IZ поступают нулевые значения по всем разрядам IZ[4-1]=0000. Так как при этом установлено нулевое значение флага нуля FZ=0, то далее нулевые значения последовательно устанавливаются на выходах второй группы элементов И с инверсным входом 61, 62, …, 6N (AND6[4-1]=0000), четвертой группы элементов ИЛИ 72, 73, …, 7N (OR7[4-2]=000), третьей группы элементов ИЛИ 42, 43, …, 4N (OR4[4-2]=000), первой группы элементов И с инверсным входом 52, 53, …, 5N (AND5[4-2]=000) и внутренней шины данных BD[4-1]=0000. При этом также устанавливаются нулевые значения внутреннего флага запроса FU=0 и внутреннего флага разрешения FE=0.

В такте 4 по фронту тактового сигнала IC осуществляется запись с внутренней шины данных BD нулевого кода во второй регистр 12 и передача на внешнюю выходную шину указателей приоритета QU[4-1]=0000, а также установка в нулевое состояние триггера 11 и внешнего флага запроса QF=0. При этом при нулевом значении внутреннего флага разрешения FE=0 запрещена запись в первый регистр 10, в котором сохраняется значение BU=100 соответствующее последнему единичному запросу третьего разряда IZ3, а далее также сохраняется код OR1[4-3]=10 на выходах первой группы 13, 14, …, 1N элементов ИЛИ.

В момент времени t3 на фиг. 2 на внешнюю шину входных заявок поступает код IZ[4-1]=1010, для которого на выходах первой группы 22, 23, …, 2N элементов И устанавливается код AND2[4-2]=100, в котором установлено единичное значение от четвертого разряда IZ4, которое далее передается на внутреннюю шину данных BD[4-1]=1000 и формируются единичные значения внутреннего флага запроса FU=1 и внутреннего флага разрешения FE=1.

В такте 5 по фронту тактового сигнала IC осуществляется запись с внутренней шины данных BD соответствующих кодов в первый регистр 10 и второй регистр 12 и далее передача значений на соответствующие шины BU[3-1]=000 и QU[4-1]=1000, а также при единичном значении флага разрешения FE=1 осуществляется установка в единичное состояние триггера 11 и внешнего флага запроса QF=1. При нулевом значении на внутренней шине BU[3-1]=000 формируется нулевое значение на выходах первой группы 13, 14, …, 1N элементов ИЛИ (OR1[4-3]=00), далее на выходах первой группы элементов И 22, 23, …, 2N устанавливается код AND2[4-2]=000 и устанавливается нулевое значение флага нуля FZ=0, по которому разрешается передача кода IZ[4-1]=1010 через вторую группу элементов И с инверсным входом 61, 62, …, 6N (AND6[4-1]=1010). Далее на выходах четвертой группы элементов ИЛИ 72, 73, …, 7N будет установлен код OR7[4-2]=111 и поэтому далее на внутренней шине данных BD будет установлен код BD[4-1]=0010 соответствующий следующему единичному значению - второму разряду IZ2, а также сохраняются единичные значения внутреннего флага запроса FU=1 и внутреннего флага разрешения FE=1.

В момент времени t4 на фиг. 2 на внешнюю шину входных заявок поступает код IZ[4-1]=0011 и так как установлено нулевое значение флага нуля FZ=0, то на выходах второй группы элементов И с инверсным входом 61, 62, …, 6N устанавливается код AND6[4-1]=0011 и далее на выходах четвертой группы элементов ИЛИ 72, 73, …, 7N будет сохраняется код OR7[4-2]=lll, по которому далее на внутренней шине данных BD будет установлен код BD[4-1]=0001 соответствующий следующему единичному значению первого разряда IZ1.

Далее в такте 6 по фронту тактового сигнала 1С осуществляется запись с внутренней шины данных BD соответствующих кодов в первый регистр 10 и второй регистр 12 и передача значений на соответствующие шины BU[3-1]=001 и QU[4-1]=0001, а также сохраняется единичное состояние триггера 11 и внешнего флага запроса QF=1.

В момент времени t5 на фиг. 2 задается нулевое значение на внешнем входе разрешения работы IE=0, по которому формируется нулевое значение внутреннего флага разрешения FE=0. Поэтому далее в такте 7 по фронту тактового сигнала IC запрещена запись в первый регистр 10 (при FE=0), в котором сохраняется значение BU[3-1]=001 соответствующее последнему единичному запросу первого разряда IZ1, а также сохраняется код 0R1[4-3]=11 на выходах первой группы 13, 14, …, 1N элементов ИЛИ. Кроме того одновременно запрещается запись во второй регистр 12 (при IE=0), в котором сохраняется значение QU[4-1]=0001, и устанавливается в нулевое состояние триггер 11 и внешний флаг запроса QF=0.

В момент времени t6 на фиг. 2 задается единичное значение на внешнем входе разрешения работы IE=1 по которому в такте 8 по фронту тактового сигнала IC осуществляется запись с внутренней шины данных BD соответствующих кодов в первый регистр 10 и второй регистр 12 и передача значений на соответствующие шины BU[3-1]=001 и QU[4-1]=0010, а также устанавливается единичное состояние триггера И и внешнего флага запроса QF=1.

В момент времени t7 на фиг. 2 на внешнюю шину входных заявок поступает код IZ[4-1]=1001, для которого аналогично рассмотренному выше алгоритму формируются соответствующие значения указателей приоритета, которые передаются на внешнюю шину QU выходов указателей приоритета в такте 9 код QU[4-1]=1000 и в такте 10 код OU[4-1]=0001. Одновременно сохраняется единичное состояние триггера 11 и внешнего флага запроса QF=1.

Таким образом, в предлагаемом устройстве на группе внешних выходов указателей приоритета QU1, QU2, …, QUN будут установлены значения приоритетного разряда в виде унитарного кода «1 из N», а также формируется единичное значение внешнего флага запроса QF=1 при наличии единичных значений запросов на внешней шине входных заявок IZ или устанавливаются нулевые значения на внешней шине выходов указателей приоритета QU и формируется нулевое значение внешнего флага запроса QF=0 при отсутствии сигналов запроса (нулевых значениях) во всех разрядах входной шины IZ или нулевом значении на внешнем входе разрешения работы 1Е=0.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый круговой арбитр диспетчера задач обладает регулярностью узлов и связей и соответствует заявляемому техническому результату - реализация кругового арбитража для равноранговых входных запросов и указания номера приоритетного запроса в виде унитарного кода «1 из N».

Реферат

Изобретение относится к области вычислительной техники. Техническим результатом изобретения является повышение точности определения приоритетного указателя в равноранговых входных запросах на основе кругового арбитража. Устройство содержит N разрядные внешнюю шину входных заявок IZ и внешнюю шину выходов указателей приоритета QU, внешний вход разрешения работы IE, внешний тактовый вход IC, внешний вход установки в нулевое состояние IR и внешний флаг запроса QF, а также содержит первую группу из (N-2) элементов ИЛИ 13, 14, …, 1N, первую группу из (N-1) элементов И 22, 23, …, 2N, вторую группу из (N-2) элементов ИЛИ 33, 34, …, 3N, третью группу из (N-1) элементов ИЛИ 42, 43, …, 4N, первую группу из (N-1) элементов И с инверсным входом 52, 53, …, 5N, вторую группу из N элементов И с инверсным входом 61, 62, …, 6N, четвертую группу из (N-1) элементов ИЛИ 72, 73, …, 7N, элемент ИЛИ 8, элемент И 9, первый регистр 10, триггер 11, второй регистр 12, внутреннюю N разрядную шину данных BD, внутреннюю (N-1) разрядную шину приоритета BU, внутренний флаг разрешения FE, внутренний флаг запроса FU и внутренний флаг нуля FZ. 2 ил.

Формула

Документы, цитированные в отчёте о поиске

Арбитр диспетчера задач

Комментарии