Устройство селекции меньшего из двоичных чисел - RU2790010C1

Код документа: RU2790010C1

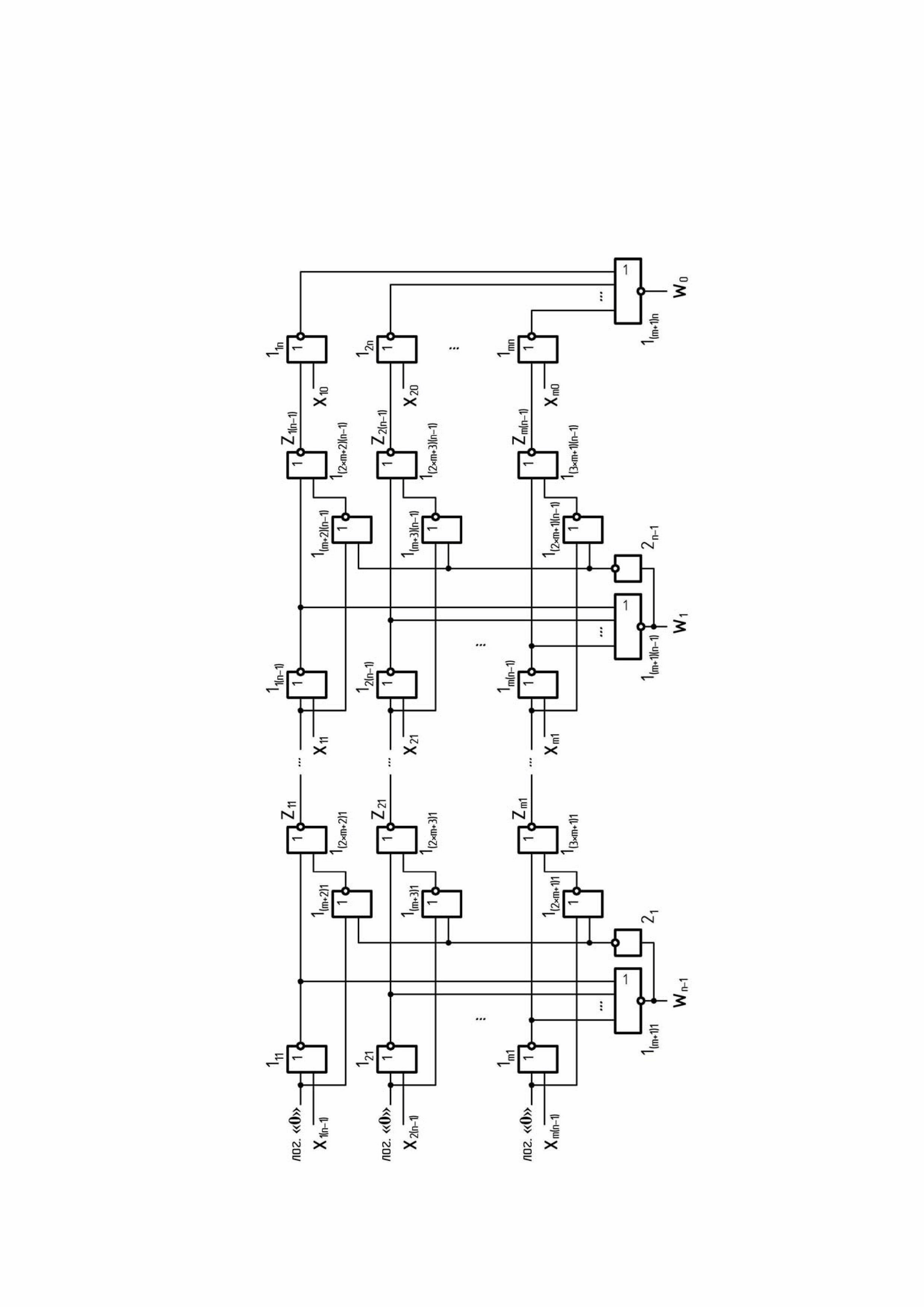

Чертежи

Описание

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны устройства селекции меньшего из двоичных чисел (см., например, патент РФ 2300133, кл. G06F7/02, 2007г.), выполняющие селекцию меньшего из двух двухразрядных двоичных чисел, задаваемых двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных устройств селекции меньшего из двоичных чисел, относятся ограниченные функциональные возможности, обусловленные тем, что не допускается обработка

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятое за прототип устройство селекции меньшего из двоичных чисел (патент РФ 2300130, кл. G06F7/02, 2007г.), которое содержит

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности, обусловленные тем, что не допускается обработка

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения селекции меньшего из

Указанный технический результат при осуществлении изобретения достигается тем, что в устройстве селекции меньшего из двоичных чисел, содержащем

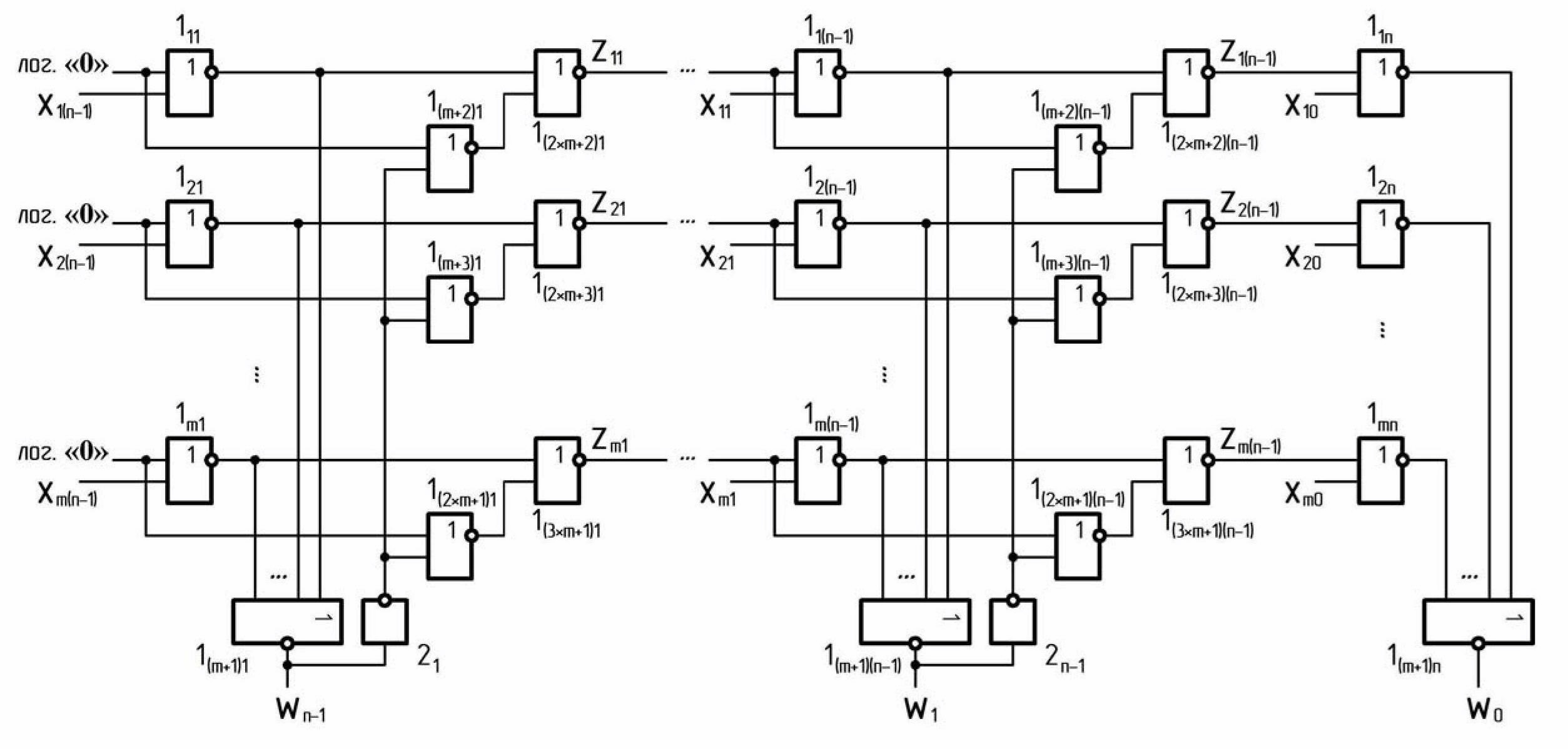

На чертеже представлена схема предлагаемого устройства селекции меньшего из двоичных чисел.

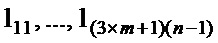

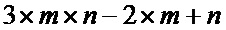

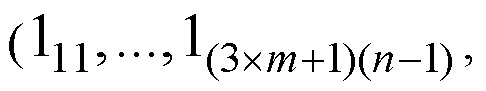

Устройство селекции меньшего из двоичных чисел содержит элементы ИЛИ-НЕ

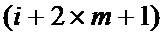

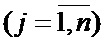

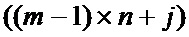

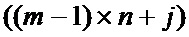

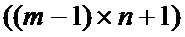

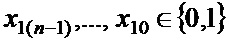

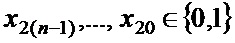

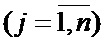

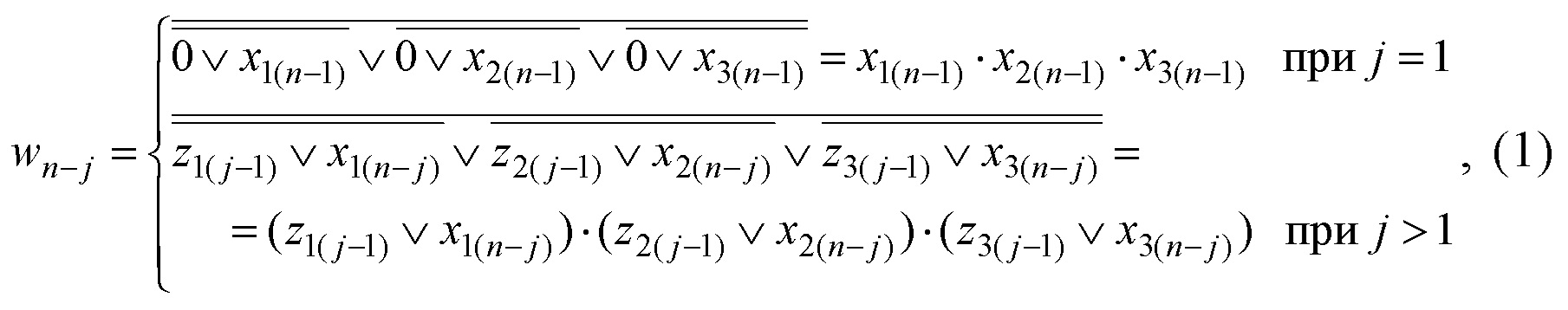

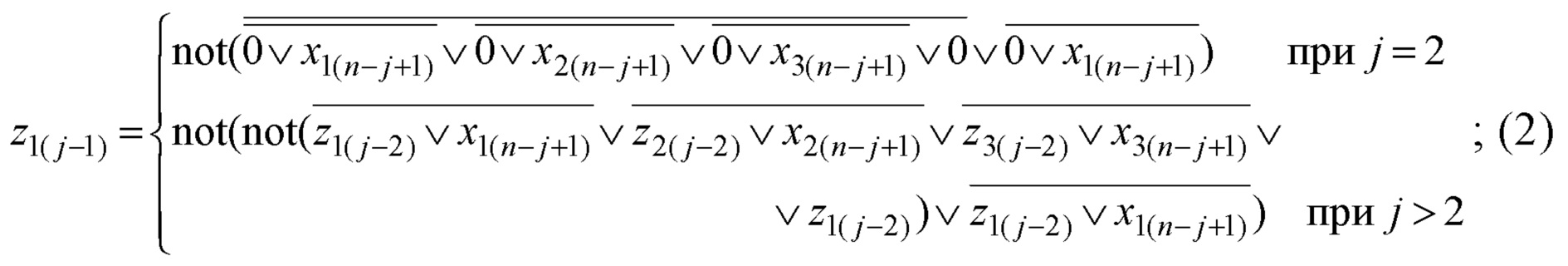

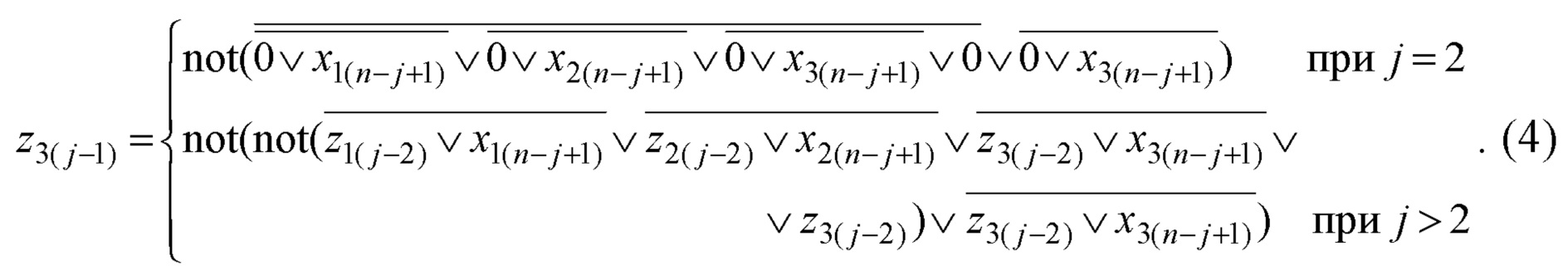

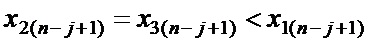

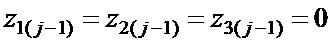

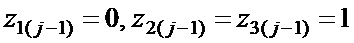

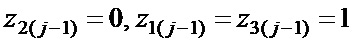

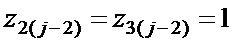

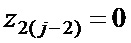

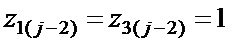

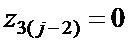

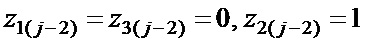

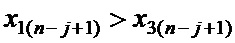

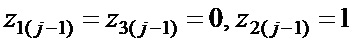

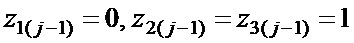

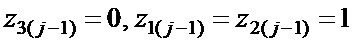

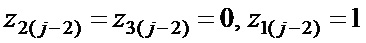

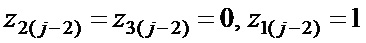

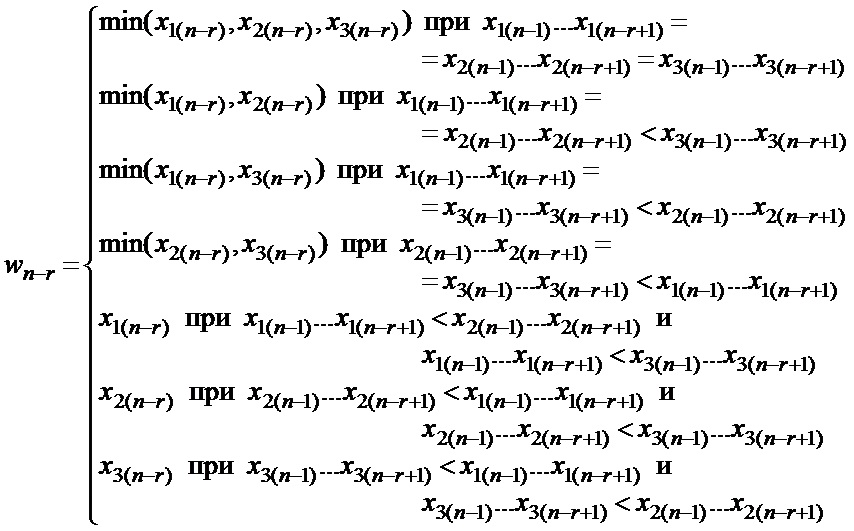

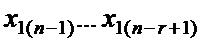

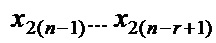

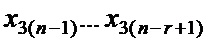

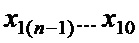

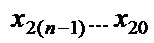

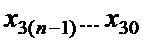

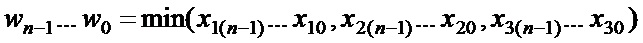

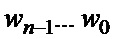

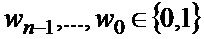

Работа предлагаемого устройства селекции меньшего из двоичных чисел осуществляется следующим образом. На его первый,…,n-й,

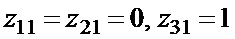

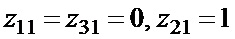

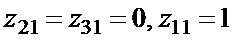

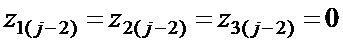

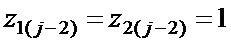

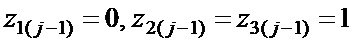

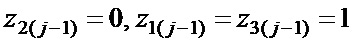

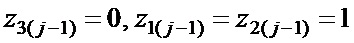

где

Здесь

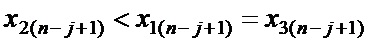

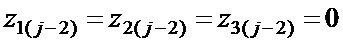

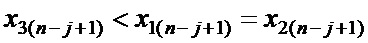

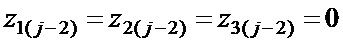

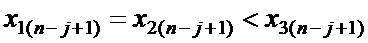

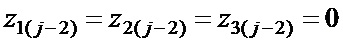

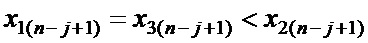

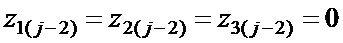

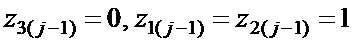

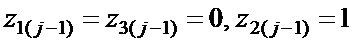

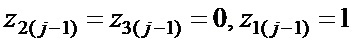

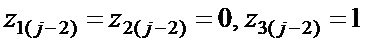

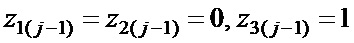

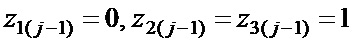

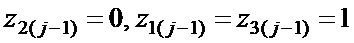

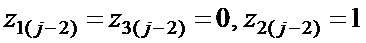

Анализ данных, приведенных в таблице, позволяет заключить, что:

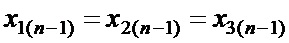

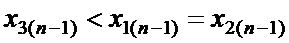

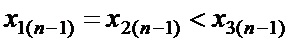

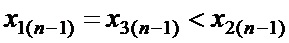

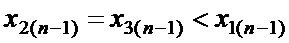

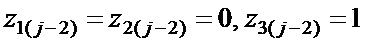

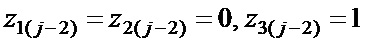

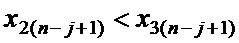

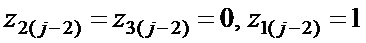

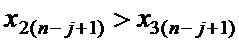

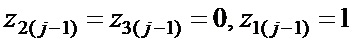

1) если

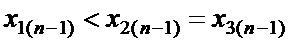

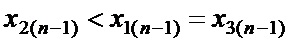

2) если

3) если

4) если

5) если

6) если

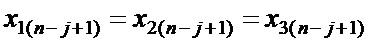

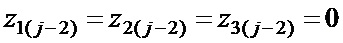

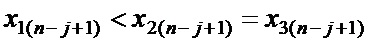

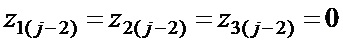

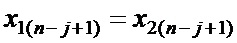

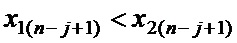

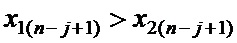

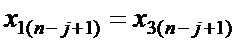

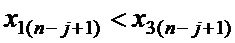

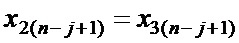

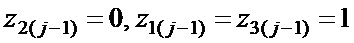

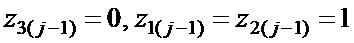

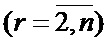

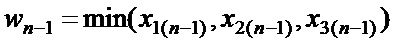

Таким образом, на первом и r-ом

и

где

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство обладает более широкими по сравнению с прототипом функциональными возможностями, так как обеспечивает селекцию меньшего из

Реферат

Изобретение относится к области вычислительной техники. Техническим результатом является расширение функциональных возможностей за счет обеспечения селекции меньшего из

Формула

Документы, цитированные в отчёте о поиске

Устройство селекции двоичных чисел

Комментарии