Способ и устройство для минимизирования коммутационных помех и их воздействия - RU2660959C2

Код документа: RU2660959C2

Чертежи

Описание

Область техники, к которой относится изобретение

Настоящее изобретение относится, в целом, к схемам управления электропитанием и, в частности, к способу и устройству для минимизации коммутационных помех при включении отключенного опорного напряжения, генерируемого для регулятора напряжения.

Уровень техники

Современные электронные устройства часто включают в себя различные электрические и электронные схемы. Например, вычислительное устройство, такое как смартфон или планшет, может включать в себя один или несколько процессоров или схемы цифрового сигнального процессора (DSP) с ассоциированной памятью; одну или более схем радиочастотного (RF) модема для осуществления радиосвязи; схему управления дисплеем; и различные схемы обработки сигнала, такие как приемник спутникового позиционирования, схемы обработки аудио или видео; и тому подобное. Эти различные схемы часто имеют разные требования к источнику питанию, такие как различные необходимые уровни напряжения постоянного тока.

Многие современные электронные устройства являются портативными и работают от аккумуляторов - либо сменных аккумуляторов, такие как щелочные батареи, или аккумуляторов, таких как NiCd, NiMH, LiOn или тому подобные. В любом случае, продолжительность работоспособности портативных электронных устройств ограничена величиной доступной мощности аккумулятора, которая уменьшается пропорционально увеличению продолжительности использования устройства и уровня потребления энергии во время его использования. С каждым новым этапом усовершенствования большинства электронных устройств сокращается диапазон конструктивных характеристик, из-за увеличения степени интеграции электронных средств и миниатюризации компонентов, таких как жесткие диски, в то же время добавляются новые признаки и функции, увеличивая число компонентов и/или вычислительную нагрузку. Обе эти тенденции требуют решения технической задачи, связанной с наличием ограниченной доступной мощности. Реализация аспекта минимизации размера устройства вынуждает также уменьшать размер аккумулятора, что, как правило, снижает доступную емкость заряда аккумулятора, в то время как аккумулятор должен обеспечить подачу электроэнергии на большее количество компонентов или обеспечивать работу процессоров на более высоких скоростях обработки информации. Эти факторы сформулировали фактор управления электропитанием, как важную техническую задачу, которую необходимо решить для оптимизации конструкций электронных устройств.

Один известный подход адаптивного управления электропитанием заключается в определении схем (или субсхем), которые не используются в течение длительного периода времени и в переводе их в состояние с низкой активностью, также называемый как «режим пониженного энергопотребления», даже если другие схемы в устройстве полностью активны. В качестве одного примера, дисплей с подсветкой многих устройств отключается после (по выбору) периода бездействия. Несложный способ отключения определенной электронной схемы заключается в прерывании поставки электропитания в данную схему. Так как остальная часть устройства по-прежнему активна, то требуется обеспечить поставку электропитания на множество отдельных схем.

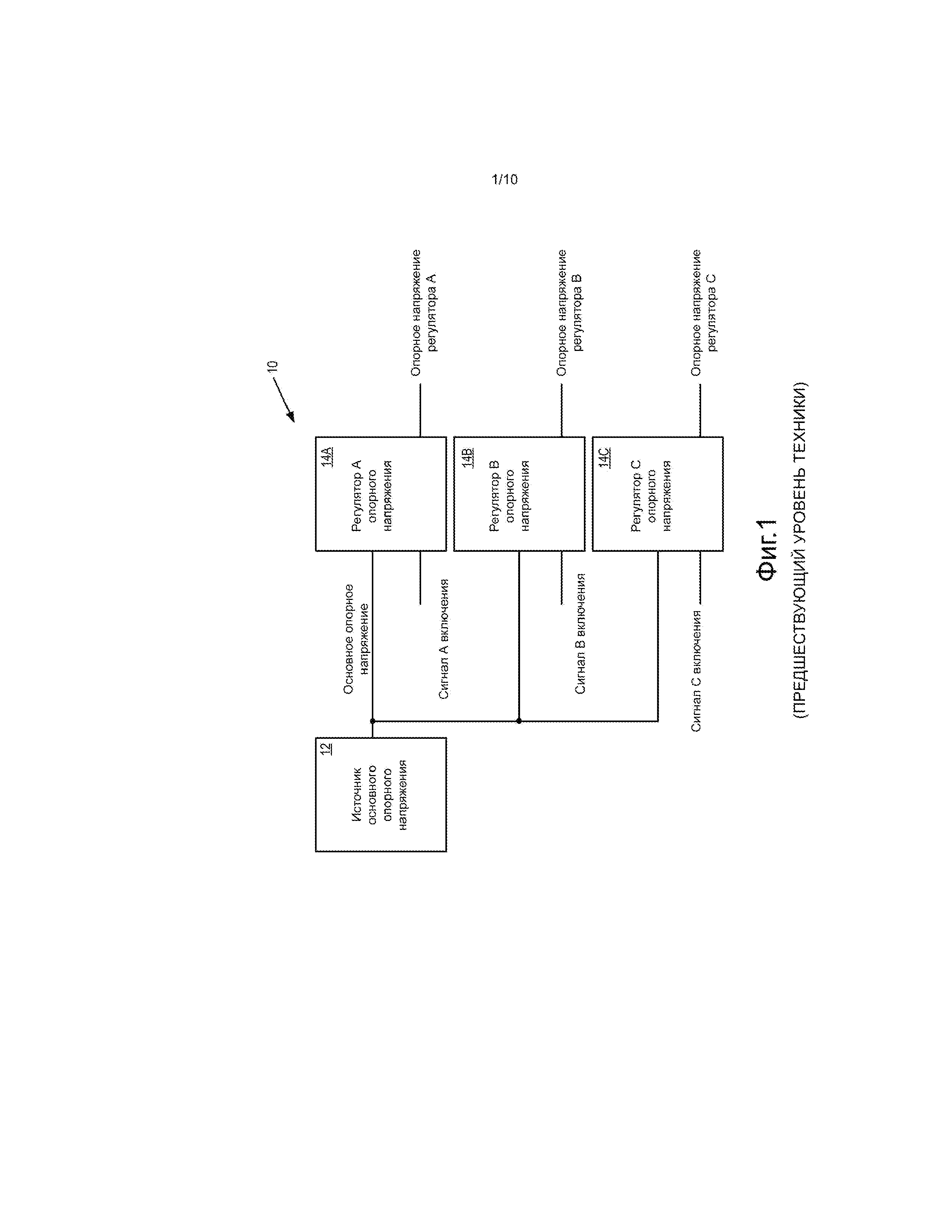

На фиг. 1 показана часть одной известной системы 10 управления электропитанием. Схема 12 основного опорного напряжения генерирует и поддерживает точное опорное напряжение. Основное опорное напряжение распределяется на множество схем 14А, 14В, 14С регулятора опорного напряжения. Каждая из схем 14А-С регулятора опорного напряжения генерирует опорное напряжение для регулятора напряжения ниже по потоку (не показано) путем деления значения основного опорного напряжения на коэффициент K, где K = [1, бесконечность]. Например, схема 14А регулятора опорного напряжения может вырабатывать 12В постоянного тока и ассоциированный с ней регулятор напряжения управляет работой аналоговых RF схем; схема 14В регулятора опорного напряжения может вырабатывать 5В постоянного тока и ассоциированный с ней регулятор напряжения управляет дискретной цифровой логикой; и схема 14С опорного регулятора напряжения может вырабатывать 3,3В постоянного тока и ассоциированный с ней регулятор напряжения управляет работой микропроцессора и памяти. Каждая из схем 14А-С регулятора опорного напряжения независимо друг от друга включается с помощью схемы управления (не показана) посредством отдельных сигналов включения. Ассоциированные регуляторы напряжения могут быть включены/выключены посредством одних и тех же сигналов включения, как и схемы 14А-С регулятора опорного напряжения.

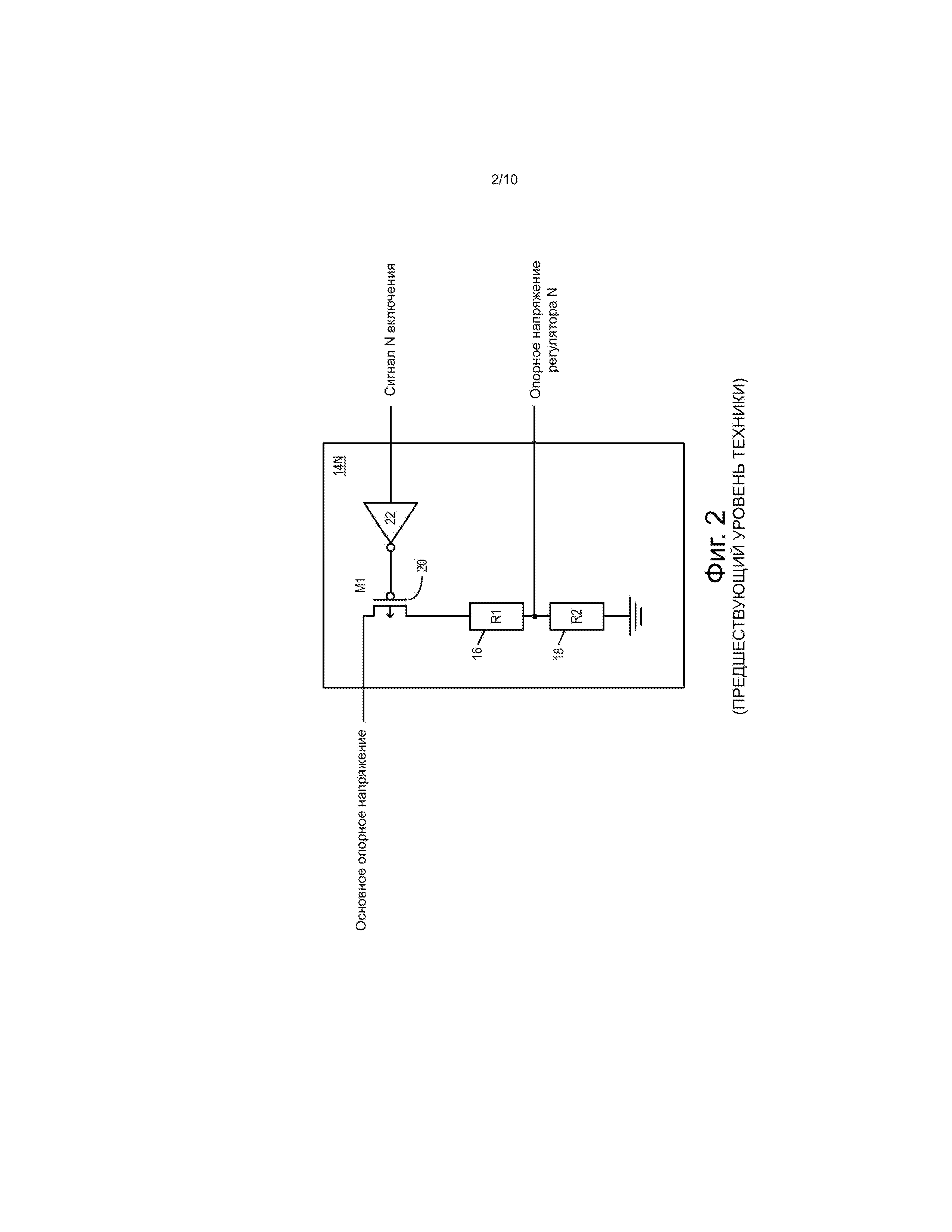

На фиг. 2 показана общая конфигурация репрезентативной схемы 14N регулятора опорного напряжения. Каждая схема 14N регулятора опорного напряжения включает в себя, например, схему установки напряжения, которая может быть цепью резистивного делителя напряжения, содержащий резисторы 16, 18, выполненные с возможностью понижать значение опорного напряжения на предварительно заданный коэффициент. Выборочное включение регулятора выходного опорного регулятора обеспечивается посредством размещения переключателя 20, например, полевого МОП-транзистора, соединенного последовательно со схемой 16, 18 установки напряжения. Переключатель 20 управляется enable_N сигналом включения, возможно, через буфер 22, для обеспечения достаточного уровня сигнала управления и установления уровнем сигнала, соответствующего конкретному типу используемого транзистора. Когда схема 14N регулятора опорного напряжения отключается, то переключатель 20 прерывает подачу электрического тока на резисторы 16, 18 установки напряжения, уменьшая выходное напряжение до нуля. Система может позже включить схему 14N регулятора опорного напряжения посредством перевода переключателя 20 в положение вкл. или переводом в проводящее состояние посредством enable_N сигнала включения. Таким образом, каждая схема 14А, 14В, 14С регулятора опорного напряжения (фиг. 1) может быть отдельно отключена и включена по желанию или при необходимости.

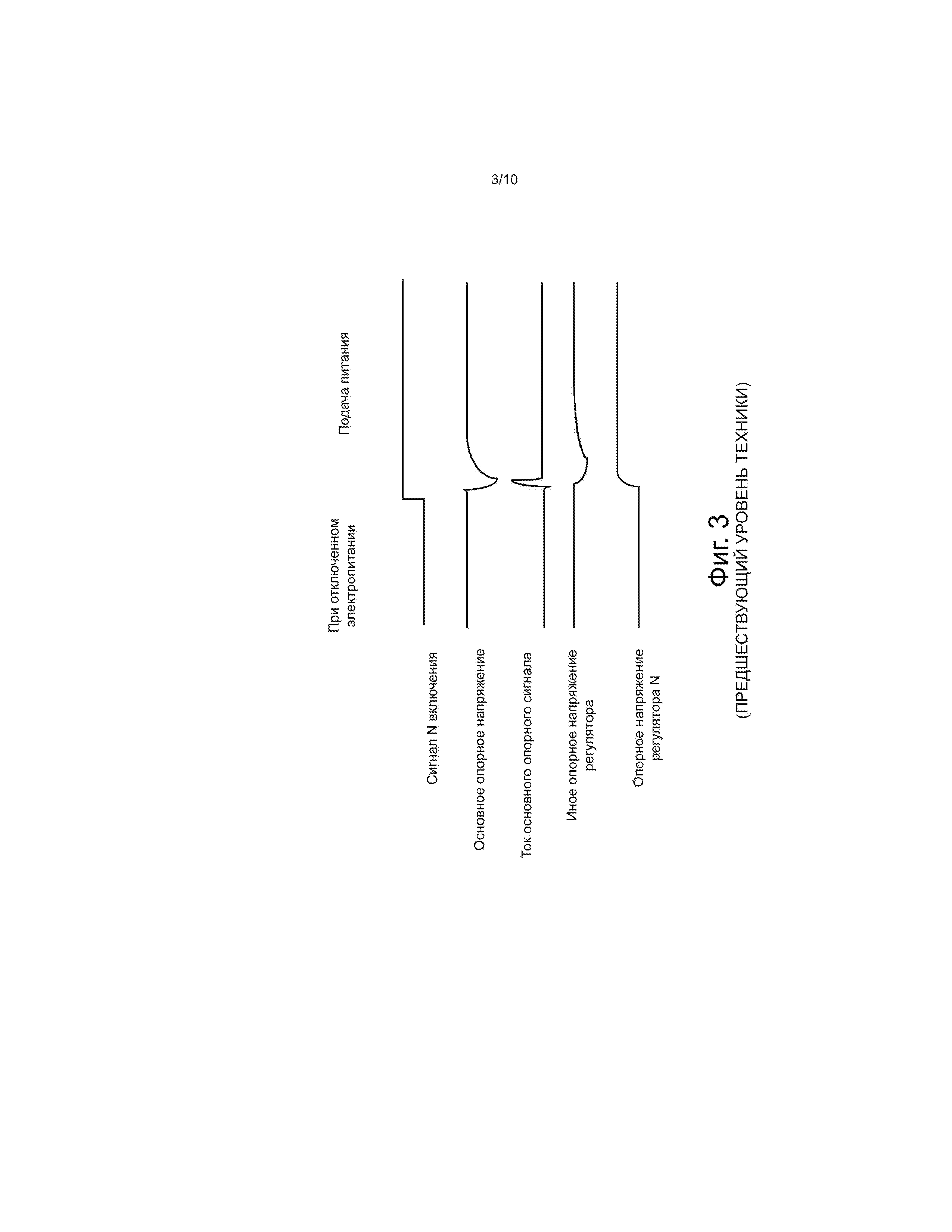

На фиг. 3 представлена иллюстрация отрицательного воздействия, вызванного функционированием системы управления электропитанием, показанной на фиг. 1 и фиг. 2. Являясь репрезентативной, схема 14N регулятора опорного напряжения включена, и соответствующий переключатель 20 находится в проводящем состоянии, внезапное приложение нагрузки вызывает кратковременное падение напряжения и выброс тока сигнала основного опорного напряжения. Это, в свою очередь, вызывает кратковременное падение напряжения сигналов регулятора опорного напряжения, выведенных всеми другими включенными в данный момент схемами регулятора опорного напряжения. Такой шум в линиях питания может оказывать вредное воздействие на работу соответствующих регуляторов напряжения, и впоследствии, на схемы, которые получают электропитание от регуляторов напряжения. Например, выбросы питания могут случайно вызвать изменение состояния некоторых, но не всех, цифровых запоминающих устройств, что может иметь отрицательные последствия, такие как, переключение режима работы процессоров, конечных автоматов, регистров состояния и т.п. в неизвестные и непреднамеренные состояния.

Подходы предшествующего уровня техники к устранению вредного влияния коммутационных помех в работающих схемах регулятора опорного напряжения включают в себя использование RC-фильтров. Тем не менее, резисторы и конденсаторы могут занимать значительный объем на интегральной схеме. Кроме того, во многих случаях коммутационные помехи переносятся на плоскость заземления RC конденсатора, которые могут нарушить чувствительность схем, совместно использующие ту же плоскость заземления.

Раздел «Уровень техники» этого документа предусмотрен для описания вариантов осуществления настоящего изобретения в технологическом и эксплуатационном контексте для оказания помощи специалистам в данной области техники в понимании сферы их применения и полезности. Если явно не определено как таковое, ни одно утверждение в настоящем документе не относится к предшествующему уровню техники посредством его включения в раздел «Уровень техники».

Сущность изобретения

Ниже представлено упрощенное изложение сущности изобретения в целях обеспечения базового понимания специалистами в данной области техники. Это краткое изложение не является исчерпывающим обзором изобретения и не предназначено для идентификации ключевых/критических элементов вариантов осуществления изобретения или определения объема изобретения. Единственной целью этого раздела «Сущность изобретения» является представление некоторых концепций, раскрытых здесь, в упрощенной форме в качестве вводной части более подробного описания, которое представлено ниже.

В соответствии с одним или более вариантами осуществления, описанными и заявленными здесь, схема управления электропитанием генерирует основное опорное напряжение и распределяет его на множество независимо работающих схем регулятора опорного напряжения, каждая из которых генерирует предварительно определенное выходное опорное напряжения для использования регулятором напряжения. Отдельные сигналы включения и сигналы разрешения предварительного заряда распределяются на каждую схему регулятора опорного напряжения. В качестве работающего регулятора опорного напряжения, включаемого с помощью своего соответствующего сигнала включения, сигнал разрешения предварительного заряда также обеспечивается в течение начального периода. Каждая схема регулятора опорного напряжения включает в себя схему установки напряжения, например, цепь резистивного делителя и первый токоограничивающий транзистор, соединенный последовательно, и выполненный с возможностью прерывать подачу тока в схему установки напряжения, когда схема регулятора опорного напряжения отключается. Второй токоограничивающий транзистор селективно сконфигурирован в качестве токового зеркала первого токоограничивающего транзистора, и ток смещения предварительного заряда от источника тока проходит через второй транзистор. Это ограничивает ток через первый транзистор и в схеме установки напряжения предотвращает возникновение значительных пиковых значений тока, которые возникают в схемах регулятора опорного напряжения в предшествующем уровне техники, для заряда паразитных емкостей до установки величины тока на расчетном эксплуатационном уровне. Ограничение тока эффективно снижает скорость нарастания выходного напряжения сигнала выходного напряжения, и сводит к минимуму мгновенное потребление тока от входного сигнала опорного напряжения. Благодаря предварительной зарядке, работающая схема регулятора опорного напряжения генерирует минимальный уровень помехи, которая оказывает воздействие на другие в данный момент работающие схемы регулятора опорного напряжения, принимающие тот же сигнал опорного напряжения. В конце начального периода (определяется сигналом разрешения предварительного заряда), источник тока и второй транзистор отключаются, и первый токоограничивающий транзистор поставляет полный рабочий ток в схему установки напряжения.

Один вариант осуществления относится к схеме управления электропитанием. Схема управления электропитанием включает в себя схему основного опорного напряжения, выполненную с возможностью генерации основного опорного напряжения, и множество схем регулятора опорного напряжения. Каждая схема регулятора опорного напряжения принимает сигнал основного опорного напряжения и сигнал включения, и выполнена с возможностью выводить сигнал, имеющий заранее определенное напряжение в ответ на сигнал включения. Каждая схема регулятора опорного напряжения включает в себя схему установка напряжения, выполненную с возможностью генерировать заранее определенное напряжение из опорного напряжения, и первый токоограничивающий транзистор, соединенный последовательно со схемой установки напряжения. Первый токоограничивающий транзистор выполнен с возможностью прерывания подачи тока в схему установки напряжения в ответ на сигнал включения. Каждая схема регулятора опорного напряжения также включает в себя второй токоограничивающий транзистор, пропорциональный по размеру с первым токоограничивающим транзистором, и выполненный с возможностью выполнять коммутацию, обеспечивающую соединение первого и второго токоограничивающих транзисторов. Схема управления выполнена с возможностью управления коммутационной цепью для соединения первого и второго токоограничивающих транзисторов в качестве конфигурации токового зеркала так, чтобы ограничивать ток, подаваемый на схему установки напряжения в начальном периоде, когда схема регулятора опорного напряжения включена. Схема управления дополнительно выполнена с возможностью включения первого токоограничивающего транзистора и отключения второго токоограничивающего транзистора после начального периода.

Другой вариант осуществления изобретения относится к способу селективного включения регулятора опорного напряжения, содержащий схему установки напряжения, выполненную с возможностью генерировать заранее определенное напряжение из поставленного основного опорного напряжения. Схема регулятора опорного напряжения отключается посредством прерывания поставки тока в схему установки напряжения. Для начального периода при включении схемы регулятора опорного напряжения, ток, поставляемый в схему установки напряжения, ограничивается до заранее определенного значения. После начального периода, заданный рабочий ток поступает на схему установки напряжения.

Краткое описание чертежей

Настоящее изобретение будет описано ниже более подробно со ссылкой на прилагаемые чертежи, на которых показаны варианты осуществления настоящего изобретения. Тем не менее, настоящее изобретение не должно быть истолковано как ограниченное вариантами осуществления, изложенными в данном документе. Скорее всего, эти варианты осуществления предоставлены для того, чтобы описание было полным и завершенным и полностью передавало объем изобретения специалистам в данной области техники. Одинаковые номера ссылаются на одинаковые элементы по всему описанию.

Фиг. 1 представляет собой функциональную блок-схему системы управления электропитанием предшествующего уровня техники.

Фиг. 2 представляет собой функциональную блок-схему регулятора опорного напряжения системы управления электропитанием предшествующего уровня техники, показанной на фиг. 1.

Фиг. 3 показывает схему токопрохождения, изображающую шум, вызванный работой схемы регулятора опорного напряжения предшествующего уровня техники, показанной на фиг. 2.

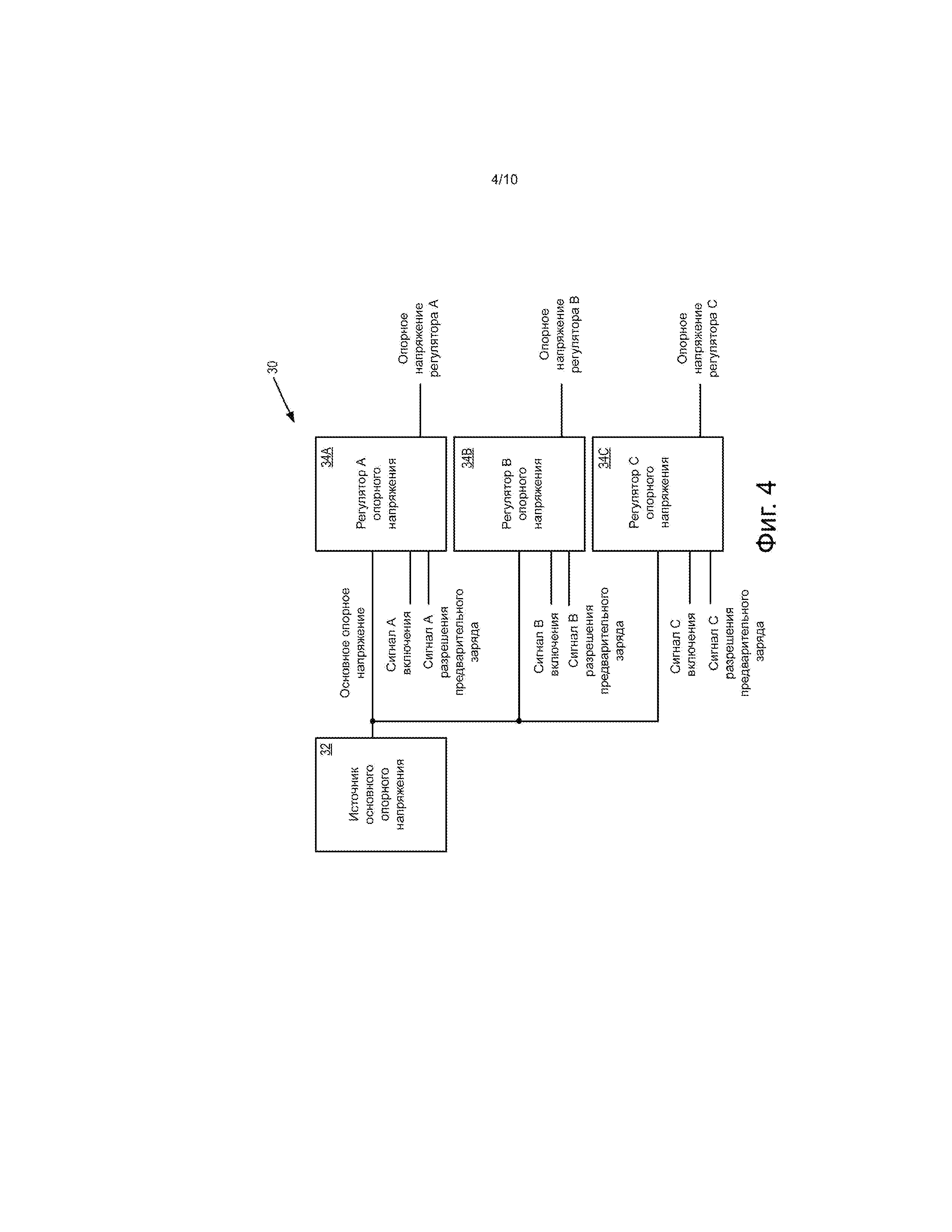

Фиг. 4 представляет собой функциональную блок-схему системы управления электропитанием в соответствии с одним из вариантов осуществления настоящего изобретения.

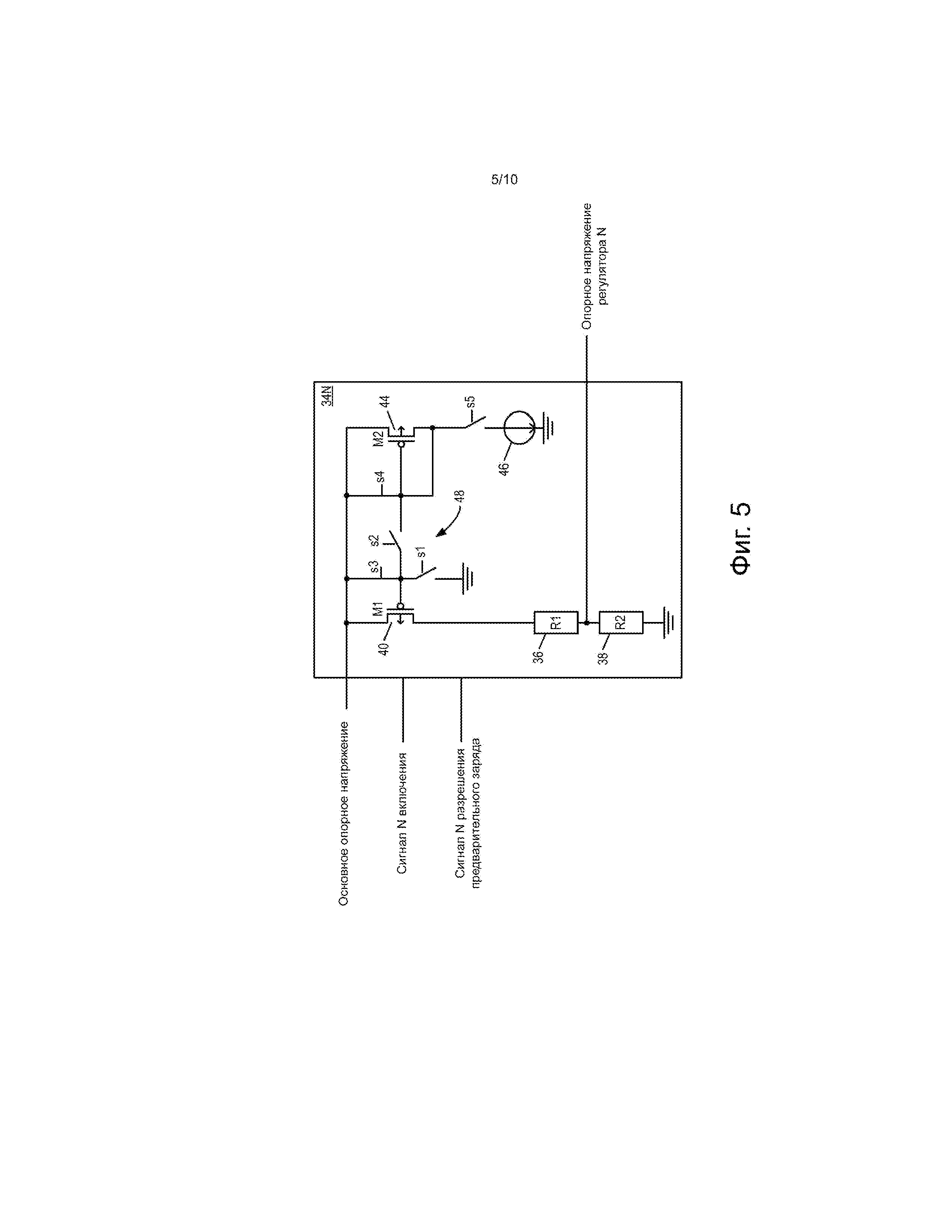

Фиг. 5 представляет собой функциональную блок-схему регулятора опорного напряжения в системе управления электропитанием, показанной на фиг. 4, в отключенном (нерабочем) состоянии.

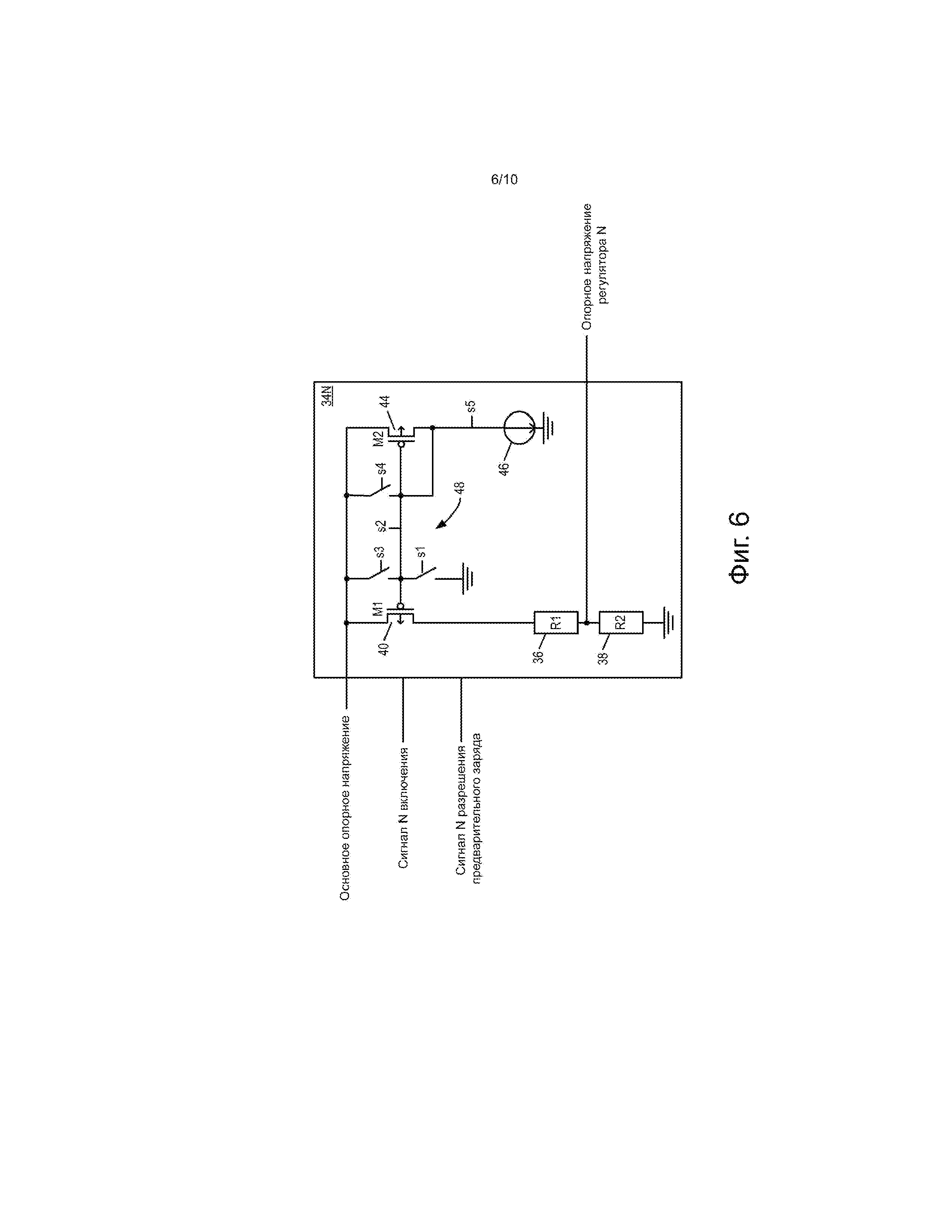

Фиг. 6 показывает функциональную блок-схему регулятора опорного напряжения, показанного на фиг. 5, в состоянии предварительного заряда (инициализации).

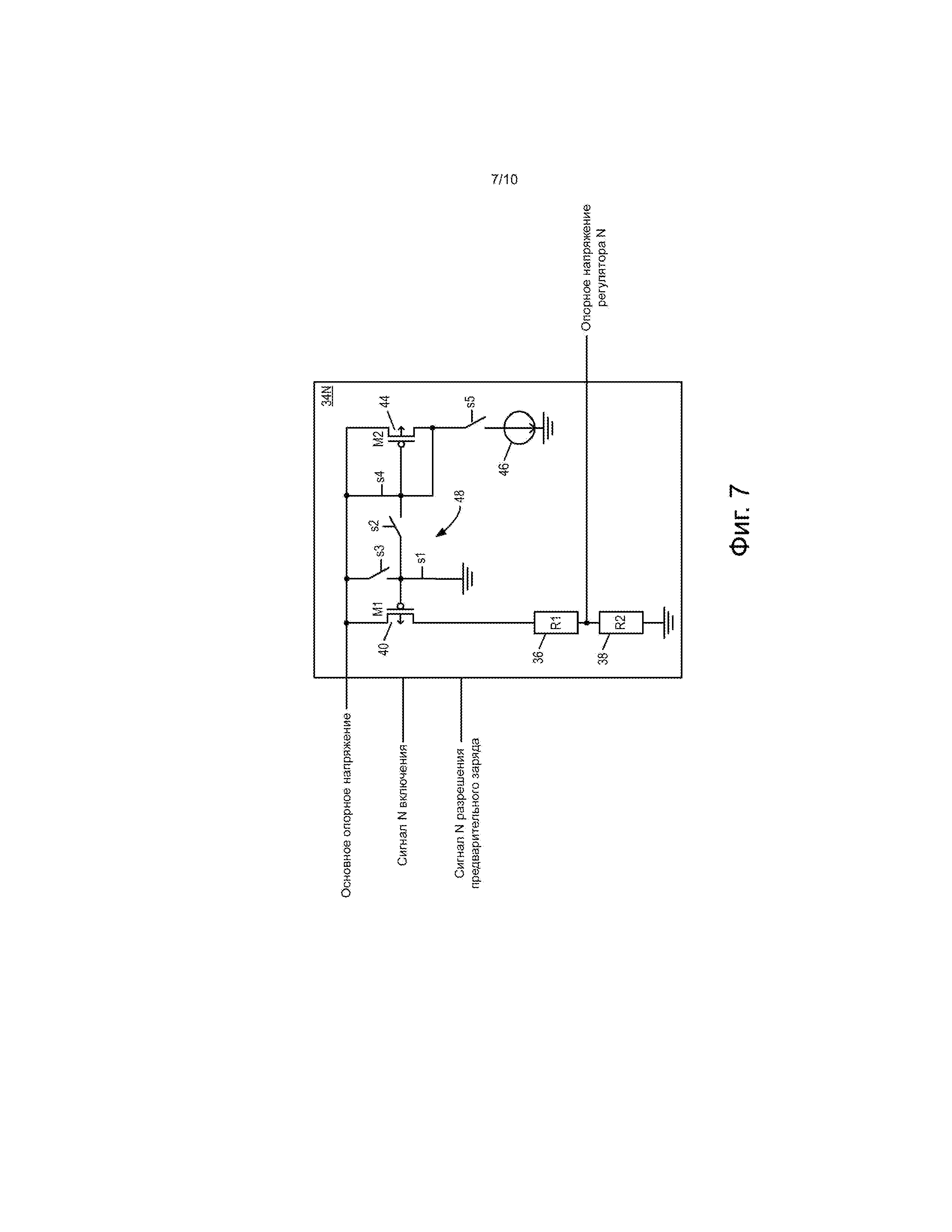

Фиг. 7 представляет собой функциональную блок-схему регулятора опорного напряжения, показанного на фиг. 5, во включенном (рабочем) состоянии.

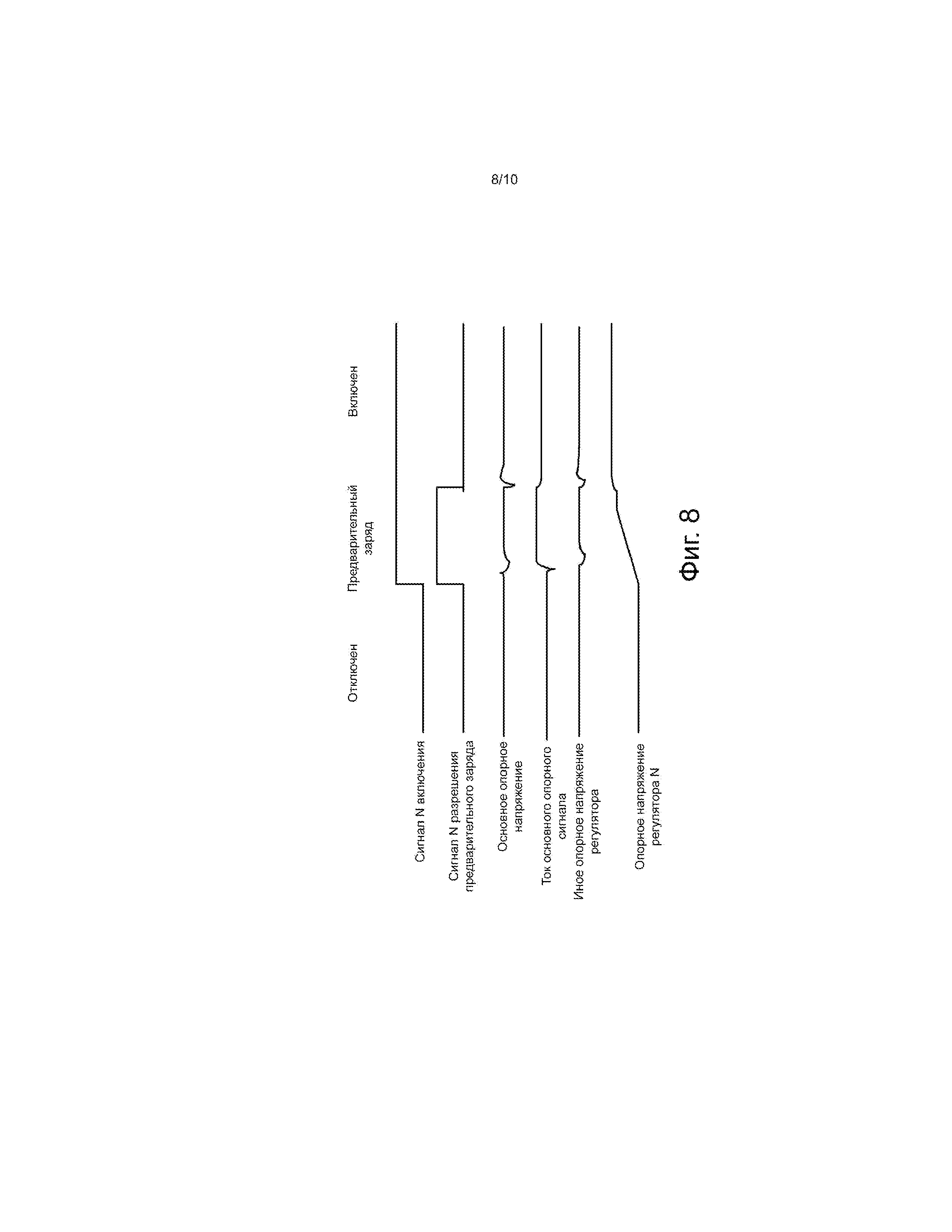

Фиг. 8 показывает схему токопрохождения, изображающую минимальный шум, вызванный работой схемы регулятора опорного напряжения, показанной на фиг. 5.

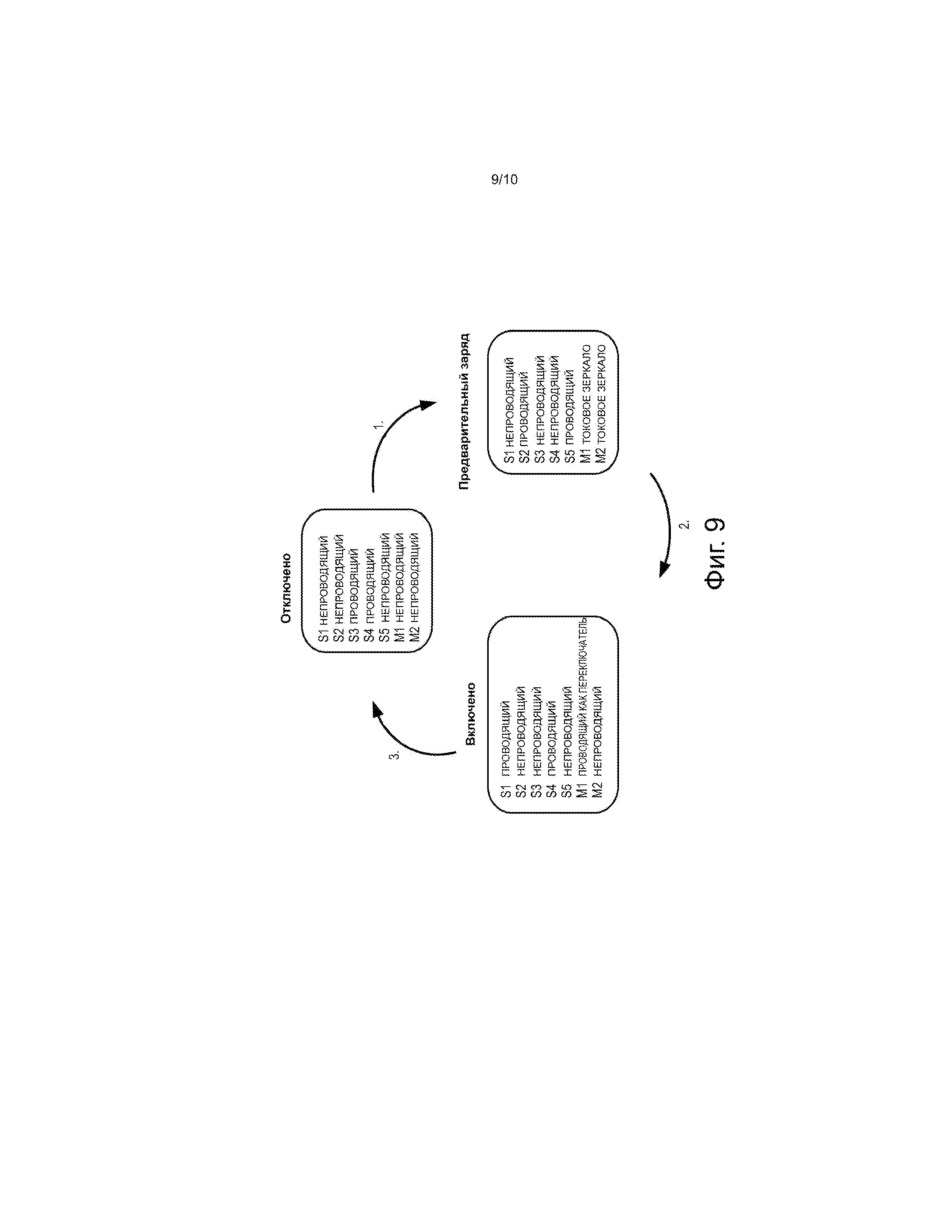

Фиг. 9 показывает диаграмму состояний, изображающую переход состояний между отключенным состоянием, предварительной зарядкой и включенным состоянием регулятора опорного напряжения, показанного на фиг. 5.

Фиг. 10 представляет собой блок-схему алгоритма способа избирательного включения регулятора опорного напряжения, такого как показано на фиг. 5.

Подробное описание

Следует понимать, что, несмотря на то, что далее представлено описание иллюстративных вариантов реализации одного или более вариантов осуществления настоящего изобретения, раскрытые системы и/или способы могут быть реализованы с использованием любого числа способов, будь то известные настоящее время или существующие. Раскрытие никоим образом не должно быть ограничено иллюстративными вариантами реализаций, чертежами и способами, которые проиллюстрированы ниже, включающие в себя примерные конструкции и структуры, показанные и описанные в настоящем документе, но могут быть модифицированы в пределах объема прилагаемой формулы изобретения совместно с их эквивалентами.

На фиг. 4 изображена схема 30 управления электропитанием в соответствии с одним из вариантов осуществления настоящего изобретения. Схема 30 управления электропитанием включает в себя схему 32 основного опорного напряжения, выполненную с возможностью генерировать и поддерживать точное значение основного опорного напряжения. Основное опорное напряжение распределяется на множество схем 34А, 34В, 34С регулятора опорного напряжения. Каждая из схем 34А-С регулятора опорного напряжения выводит заранее определенное значение опорного напряжения регулятора, например 12 В постоянного тока, 5 В постоянного тока, 3,3 В постоянного тока или некоторые другие значения. Каждая схема 34А-С регулятора опорного напряжения включается независимо с помощью схемы управления (не показана) посредством отдельных сигналов включения. Каждая схема 34А-С регулятора опорного напряжения также принимает отдельный сигнал разрешения предварительной зарядки, который определяет начальный период, когда схема 34А-С регулятора опорного напряжения включена из выключенного состояния, в течение которого сигнал регулятора опорного напряжения «возрастает» до своего заранее определенного значения, показывая увеличенную скорость нарастания выходного напряжения.

На фиг. 5 показана примерная схема 34N регулятора опорного напряжения. Схема 34N регулятора опорного напряжения включает в себя схему установки напряжения, которая может включать в себя сетевой резистивный делитель напряжения, образованный резисторами 36, 38, выполненный с возможностью уменьшения значения основного опорного напряжения до заранее определенного значения опорного напряжения регулятора напряжения. Первый токоограничивающий транзистор 40 (M1) соединен последовательно с резисторами 36, 38 установки напряжения, и выполнен с возможностью прерывания поставки тока на резисторы 36, 38 установки напряжения, когда схема 34N регулятора опорного напряжения отключается посредством enable_N сигнала включения. Первый токоограничивающий транзистор 40 управляется с помощью цепи 48 коммутации, которая изменяет состояние в ответ на подачу на вход enable_N сигнала включения и enable_N сигнала разрешения предварительного заряда. Как показано на фиг. 5, коммутатор S3 замкнут и коммутатор S1 разомкнут, соединяя затвор первого транзистора 40 к основному опорному напряжению на его источнике, таким образом, переводя транзистор 40 в непроводящее состояние. На фиг. 5 показана таким образом схема 34N регулятора опорного напряжения в отключенном (нерабочем) состоянии.

Варианты осуществления настоящего изобретения снижают влияние переходных эффектов, которые оказывают воздействие на основной сигнал опорного напряжения и, следовательно, на выходные сигналы регулятора опорного напряжения других схем регулятора опорного напряжения, когда схема 34N регулятора опорного напряжения включена из выключенного состояния. Для достижения этой цели, ток, подаваемый на резисторы 36, 38 установки напряжения, проходящий через первый токоограничивающий транзистор 40, ограничен в течение начального периода. Это позволяет стороне нагрузки транзистора 40 обеспечивать равномерную зарядку. Для достижения ограничения тока, схема 34N регулятора опорного напряжения также включает в себя второй токоограничивающий транзистор 44 (M2), который является токовым зеркалом по отношению к первому токоограничивающему транзистору 40, как изображено на фиг. 6. В этой конфигурации цепи 48 коммутации, коммутатор S2 замкнут и S1, S3 и S4 разомкнуты; Таким образом, исток и затвор двух транзисторов 40, 44 соединены друг с другом (и второй транзистор 44 выполнен с возможностью функционировать как диод, соединяя его затвор и сток).

Второй транзистор и первый транзистор 40 спарены на кремнии, и транзисторы 40, 44 являются пропорциональными по размеру. Например, транзисторы 40, 44 могут иметь одинаковую длину затвора; тем не менее, ширина WM1 затвора первого транзистора 40 может кратно превышать ширину WМ2 затвора второго транзистора 44. В конфигурации токового зеркала, ток IM1 стока первого транзистора 40 пропорционален току IM2 стока второго транзистора 44, в соответствии с:

(1)

Источник 46 тока, соединенный со вторым транзистором 44 с помощью переключателя S5, генерирует заранее определенный ток смещения предварительного заряда, когда включается посредством входного сигнала разрешения предварительного заряда enable_N. Это также ток IM2 стока второго транзистора 44. Сигнал разрешения предварительного заряда enable_N задается для начального периода, когда схема 34 регулятора опорного напряжения включается из выключенного состояния. Посредством конфигурации токового зеркала ограничивается ток IM1стока первого транзистора 40 к значению заданного уравнением (1), которое зависит от соотношения ширин затвора транзисторов 40, 44. Ограниченный ток IМ1 первого транзистора 40 позволяет не допустить возникновения большого переходного тока, который, в противном случае, обеспечит заряд паразитных емкостей, когда первый транзистор 40 работает. Уменьшенный ток IM1выбирается для плавного увеличения опорного напряжения регулятора схемы 34N регулятора опорного напряжения до заранее определенного уровня, с учетом наличия внутренней емкости между первым транзистором 40 и резисторами 36, 38 установки напряжения, при минимальной нагрузке основного входного сигнала опорного напряжения. В других вариантах осуществления внешний конденсатор может обеспечить лучшую фильтрацию шумов, но его использование вызывает дополнительные затраты и занимает дополнительную область. Специалисты в данной области техники могут принять решение относительно описанного выше предложения, принимая во внимание идеи настоящего изобретения.

После начального периода, когда величина выходного сигнала схемы 34N регулятора опорного напряжения увеличилась до его заданного значения, сигнал разрешения предварительного заряда enable_N сбрасывается (в то время как сигнал включения enable_N остается), переключая схему 34N регулятора опорного напряжения в полностью включенное состояние, как показано на фиг. 7. В этой конфигурации первый токоограничивающий транзистор 40 полностью включен или находится в проводящем состоянии путем заземления его затвора через переключатель S1, и отсоединяя затвор от основного опорного напряжения с помощью переключателя S3, будучи разомкнутым. Расчетный рабочий ток, таким образом, поступает на резисторы 36, 38 установки напряжения. Второй токоограничивающий транзистор 44 отсоединен от первого транзистора 40 с помощью переключателя S2, и переводится в состояние ВЫКЛ или непроводящее состояние, отсоединяя его затвор от основного опорного напряжения с помощью переключателя S4. Переключатель S5 разомкнут для отключения источника 46 тока. Такая конфигурация цепи 48 коммутации эффективно отключает второй токоограничивающий транзистор 44 и источник 46 тока, в результате чего, первый транзистор 40 действует как переключатель, и резисторы 36, 38 установки напряжения формируют заранее определенное значение опорного напряжения регулятора. Следует отметить, что, как и в схемах предшествующего уровня техники, схема 34N регулятора опорного напряжения может быть переведена из включенного состояния в отключенное состояние мгновенно с помощью сигнала включения enable_N, который переключает состояния переключателей S1 и S3, отключая затвор первого транзистора 40 от основного опорного напряжения и переводя транзистор 40 в непроводящее состояние (ср. фиг. 7 и фиг. 5). Следовательно, отсутствует задержка при отключении поставленного напряжения регулятора и схемы переводятся в режим «ожидания»; задержка предварительной зарядки может возникнуть только при их «активации».

На фиг. 8 показаны примерные графики напряжения и тока в качестве примера для пояснения процесса перехода схемы 34N регулятора опорного напряжения из выключенного состояния в активированное состояние через промежуточное состояние предварительного заряда, в соответствии с настоящим изобретением. Изначально, оба enable_N сигнал включения и enable_N сигнал разрешения предварительного заряда поступают вместе. Это оказывает определенное влияние на основной сигнал опорного напряжения, который распространяется через регулятор опорного напряжения других схем 34 регулятора опорного напряжения, подключенных к одному и тому же основному сигналу опорного напряжения. Тем не менее, эти переходные процессы незначительны по сравнению с предшествующим уровнем техники (см. фиг. 3). Выходное напряжение схемы 34N регулятора опорного напряжения, при его включении, проявляет уменьшенную скорость нарастания выходного напряжения, так как она медленно повышается от нуля до заранее определенного уровня опорного напряжения регулятора. После начального периода ограничения тока, сигнал разрешения предварительного заряда enable_N будет сброшен, в то время как сигнал включения enable_N остается, и схема 34N регулятора опорного напряжения находится во включенном состоянии.

В указанной ниже таблице 1, а также на фиг. 9, показаны состояния переключателей в коммутационной сети 48, при изменении состояний схемы 34N регулятора опорного напряжения, а именно, выключенного состояния, состояния предварительной зарядки и включенного состояния. Конечно, эта таблица отражает конкретную конфигурацию переключателей в цепи 48 коммутации, как показано на фиг. 5-7. Настоящее изобретение не ограничивается этой конкретной конфигурацией, и другие конфигурации переключателей будут функционировать по-разному для достижения преимуществ в соответствии с настоящим изобретением. Логика управления цепи 48 коммутации - или другой конфигурации переключателей – с использованием enable_N сигнала включения и enable_N сигнала разрешения предварительного заряда, понятна специалистам в этой области техники и, соответственно, не проиллюстрирована на чертежах.

Таблица 1: Состояния переключателей

На фиг. 10 показан способ 100 селективного включения схемы 34N регулятора опорного напряжения, изображенного на фиг. 5-7. Первоначально, схема 34N регулятора опорного напряжения находится в отключенном состоянии из-за прерывания подачи тока на резисторы 36, 38 установки напряжения (этап 102). Если оба входных сигнала enable_N включения и enable_N предварительного заряда не поступают (этап 104), то схема 34N регулятора опорного напряжения остается в отключенном состоянии (этап 102). Если оба сигнал включения enable_N и сигнал enable_N разрешения предварительного заряда поступают (этап 104), то схема 34N регулятора опорного напряжения входит в состояние предварительной зарядки, в котором ток подается на резисторы 36, 38 установки напряжения, в котором ограничивается для предотвращения возникновения большого переходного выброса тока (этап 106). В одном варианте осуществления это обеспечивается использованием первого токоограничивающего транзистора 40 в конфигурации токового зеркала со вторым токоограничивающим транзистором 44, что ограничивает величину тока, проходящего через второй транзистор 44. Таким образом, заранее определенное, ограниченное значение тока, подаваемого на резисторы 36, 38 установки напряжения, будет затем определяться в соответствии с уравнением (1).

Схема 34N регулятора опорного напряжения остается в состоянии предварительной зарядки до тех пор, пока подаются входные сигналы включения enable_N и enable_N разрешения предварительного заряда. Когда подается входной сигнал включения enable_N, и входной сигнал разрешения предварительного заряда enable_N будет сброшен (этап 108), то схема 34N регулятора опорного напряжения находится во включенном состоянии, обеспечивая подачу расчетного рабочего тока на резисторы 36, 38 установки напряжения (этап 110). В одном варианте осуществления это обеспечивается путем отключения токового зеркала, что делает первый токоограничивающий транзистор 40 полностью проводящим. Когда входной сигнал включения enable_N будет сброшен (этап 112), схема 34N регулятора опорного напряжения возвращается в неактивное состояние путем прерывания подачи тока на резисторы 36, 38 установки напряжения (этап 102).

Для специалистов в данной области техники будет понятно, что изменения способа 100 возможны в пределах объема настоящего изобретения. Например, в одном варианте осуществления, если схема 34N регулятора опорного напряжения отключается, и поступает только входной сигнал включения enable_N, то она может перейти непосредственно в активное состояние. Это может быть желательно, например, если все схемы 34A-C регулятора опорного напряжения отключены, и первая схема 34N регулятора опорного напряжения включена. В этом случае, помехи переходных процессов на основной линии опорного напряжения не будут иметь неблагоприятного последствия, и может быть устранена задержка и потребление мощности при переходе из состояния предварительной зарядки. Кроме того, блок-схема алгоритма, показанная на фиг. 10, изображает «стандартную» операцию для предоставления раскрытия вариантов осуществления настоящего изобретения, и не изображает процесс каждого возможного перехода. Например, с этапа 108, если были сброшены оба сигнал включения enable_N и сигнал enable_N разрешения предварительного заряда, то логика управления может переключить схему 34N регулятора напряжения в отключенное состояние (этап 102). Описание такого нестандартного процесса был опущено на фиг. 10 для ясности, но полная спецификация всех возможных операций переключений очевидна для специалистов в данной области техники, принимая во внимание идеи настоящего изобретения.

Варианты настоящего изобретения представляют преимущества над схемами управления электропитанием предшествующего уровня техники путем недопущения воздействия отрицательных переходных эффектов на все выходные сигналы регулятора опорного напряжения, независимо от того, одна или несколько схем 34А-С регулятора опорного напряжения активируются из выключенного состояния. В вариантах осуществления, показанных на фиг. 5-7, первый токоограничивающий транзистор 40 – используемый в схемах предшествующего уровня техники для отключения схемы 34N регулятора опорного напряжения - повторно используется для ограничения тока, в дополнение к его функциональности переключать непроводящее состояние или полностью проводящее состояние. Благодаря конфигурации токового зеркала, второй токоограничивающий транзистор 44 может быть относительно небольшим, занимая незначительный объем кремния и рассеивая мало энергии. Аналогичным образом, источник 46 тока должен генерировать только небольшой ток, чтобы ограничить ток, подаваемый на резисторы 36, 38 установки напряжения, дополнительно снижая потребление энергии.

Настоящее изобретение может, конечно, быть осуществлено иными способами, чем те, которые конкретно изложены в настоящем документе, не отступая от существенных характеристик изобретения. Настоящие варианты осуществления должны рассматриваться во всех отношениях как иллюстративные, а не ограничительные, и все изменения должны находиться в рамках и диапазоне эквивалентности прилагаемой формулы изобретения.

Реферат

Изобретение относится к области электротехники. Схема управления электропитанием генерирует опорное напряжение и распределяет его на множество независимо работающих схем регулятора опорного напряжения, каждая из которых генерирует заданное напряжение для регулятора напряжения. Отдельные сигналы включения и сигналы разрешения предварительного заряда распределяются на каждую схему регулятора опорного напряжения. Так как схема регулятора опорного напряжения включается с помощью своего соответствующего сигнала включения, то сигнал разрешения предварительного заряда также обеспечивается в течение начального периода. Каждая схема регулятора опорного напряжения включает в себя схему установки напряжения и первый токоограничивающий транзистор, соединенный последовательно, и выполненный с возможностью прервать подачу тока в схему установки напряжения, когда схема регулятора опорного напряжения отключена. Второй токоограничивающий транзистор выполнен с возможностью работать как токовое зеркало с первым токоограничивающим транзистором, и ток смещения предварительного заряда от источника тока проходит через второй транзистор. Эта операция ограничивает ток, протекающий через первый транзистор и в схему установки напряжения в течение начального периода. После окончания начального периода токовое зеркало отключается, и первый транзистор переводится в полностью проводящее состояние. 3 н. и 11 з.п. ф-лы, 10 ил., 1 табл.

Комментарии