Многофункциональный мажоритарный модуль - RU2626346C1

Код документа: RU2626346C1

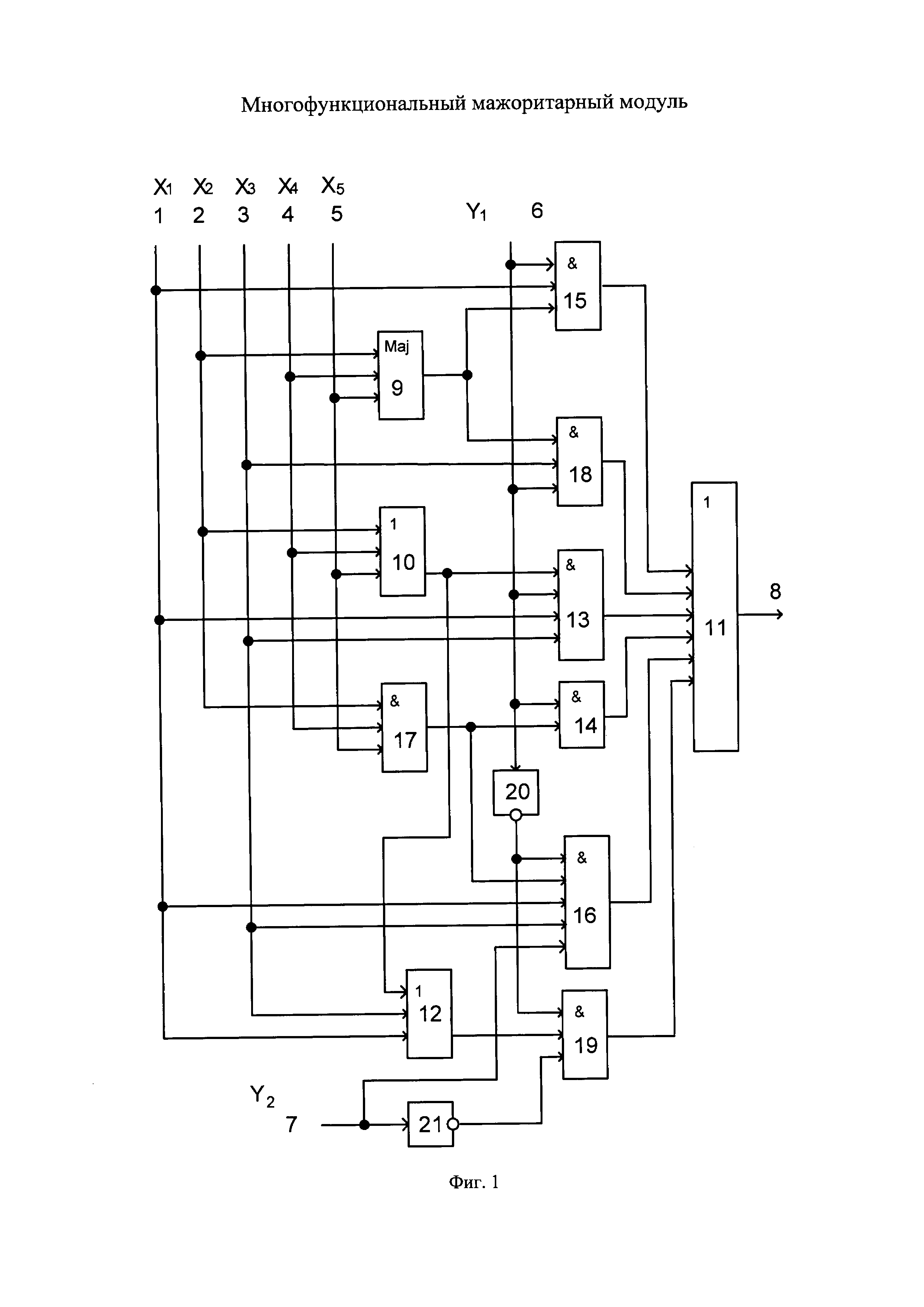

Чертежи

Описание

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известен мажоритарный модуль (см., например, патент РФ №2249844, кл. G06F 7/38, 2005 г.), который содержит элемент И, элемент ИЛИ, два мажоритарных элемента, который реализует мажоритарную функцию Maj(x1,x2,x3)=x1x2 v x1x3 v x2x3 трех аргументов - входных двоичных сигналов x1,x2,x3 ∈ {0, 1} либо дизъюнкцию (конъюнкцию) тех же трех аргументов.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных мажоритарных модулей, относятся ограниченные функциональные возможности, обусловленные тем, что не допускается обработка пяти входных сигналов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип мажоритарный модуль (патент РФ 2580801, кл. Н03K 19/23, G06F 7/38, G06F 7/57, 2016 г.), который содержит пять информационных входов, два настроечных входа, выход модуля, мажоритарный элемент, первый и второй элементы ИЛИ, первый и второй элементы И, причем второй информационный вход соединен с первым входом первого элемента ИЛИ, четвертый информационный вход соединен с первым входом мажоритарного элемента, пятый информационный вход соединен со вторым входом мажоритарного элемента, выход первого элемента ИЛИ соединен с первым входом первого элемента И, выход первого элемента И соединен с первым входом второго элемент ИЛИ, выход второго элемента И соединен со вторым входом второго элемента ИЛИ, который реализует мажоритарную функцию Maj(x1,x2,x3,x4,x5) пяти аргументов - входных двоичных сигналов x1,x2,x3,x4,x5 ∈ {0, 1} либо дизъюнкцию (конъюнкцию) тех же пяти аргументов.

К причине, препятствующей достижению указанного ниже технического результата при использовании известного мажоритарного модуля для реализации мажоритарной функции, дизъюнкции, конъюнкции пяти аргументов относятся низкое быстродействие, обусловленное тем, что в нем максимальное время задержки сигнала равно 4Тмаж, где Тмаж - время задержки в мажоритарном элементе и большая сложность, обусловленная большим количеством входов в элементы при его реализации в базисе И, ИЛИ, НЕ.

Техническим результатом изобретения является повышение быстродействия устройства и уменьшение его сложности при реализации мажоритарной функции, дизъюнкции, конъюнкции пяти аргументов.

Указанный технический результат при осуществлении изобретения достигается тем, что в многофункциональный мажоритарный модуль, предназначенный для реализации мажоритарной функции, конъюнкции и дизъюнкции пяти переменных, содержащий пять информационных входов, два настроечных входа, выход модуля, мажоритарный элемент, первый и второй элементы ИЛИ, первый и второй элементы И, причем второй информационный вход соединен с первым входом первого элемента ИЛИ, четвертый информационный вход соединен с первым входом мажоритарного элемента, пятый информационный вход соединен со вторым входом мажоритарного элемента, выход первого элемента ИЛИ соединен с первым входом первого элемента И, выход первого элемента И соединен с первым входом второго элемент ИЛИ, выход второго элемента И соединен со вторым входом второго элемента ИЛИ, введены дополнительно третий элемент ИЛИ, третий, четвертый, пятый, шестой и седьмой элементы И, первый и второй элементы НЕ, причем первый информационный вход соединен с вторым входом первого элемента И, первыми входами третьего элемента И, четвертого элемента И и третьего элемента ИЛИ, второй информационный вход соединен с третьим входом мажоритарного элемента и первым входом пятого элемента И, третий информационный вход соединен с третьим входом первого элемента И, вторым входом четвертого элемента И, первым входом шестого элемента И и вторым входом третьего элемента ИЛИ, четвертый информационный вход соединен с вторым входом первого элемента ИЛИ и вторым входом пятого элемента И, пятый информационный вход соединен с третьим входом первого элемента ИЛИ и третьим входом пятого элемента И, первый настроечный вход соединен со вторым входом третьего элемента И, вторым входом шестого элемента И, четвертым входом первого элемента И, первым входом второго элемента И и через первый элемент НЕ с третьим входом четвертого элемента И и первым входом седьмого элемента И, второй настроечный вход соединен с четвертым входом четвертого элемента И и через второй элемент НЕ со вторым входом седьмого элемента И, выход мажоритарного элемента соединен с третьим входом третьего элемента И и третьим входом шестого элемента И, выход первого элемента ИЛИ соединен с третьим входом третьего элемента ИЛИ, выход пятого элемента И соединен с вторым входом второго элемента И и пятым входом четвертого элемента И, выход третьего элемента ИЛИ соединен с третьим входом седьмого элемента И, выход третьего элемента И соединен с третьим входом второго элемента ИЛИ, выход шестого элемента И соединен с четвертым входом второго элемента ИЛИ, выход четвертого элемента И соединен с пятым входом второго элемента ИЛИ, выход седьмого элемента И соединен с шестым входом второго элемента ИЛИ, выход второго элемента ИЛИ соединен с выходом устройства.

На фиг.1 представлена схема многофункционального мажоритарного модуля. Многофункциональный мажоритарный модуль, содержащий пять информационных входов 1, 2, 3, 4, 5, два настроечных входа 6, 7, выход модуля 8, мажоритарный элемент 9, первый, второй и третий элементы ИЛИ 10, 11, 12, первый, второй, третий, четвертый, пятый, шестой и седьмой элементы И 13-19, первый и второй элементы НЕ 20, 21. Элементы схемы соединены следующим образом. Первый информационный вход 1 соединен с вторым входом первого элемента И 13, первыми входами третьего элемента И 15, четвертого элемента И 16 и третьего элемента ИЛИ 12. Второй информационный вход 2 соединен с третьим входом мажоритарного элемента 9, с первым входом первого элемента ИЛИ 10 и первым входом пятого элемента И 17. Третий информационный вход 3 соединен с третьим входом первого элемента И 13, вторым входом четвертого элемента И 16, первым входом шестого элемента И 18 и вторым входом третьего элемента ИЛИ 12. Четвертый информационный вход 4 соединен с вторым входом первого элемента ИЛИ 10 и вторым входом пятого элемента И 17, с первым входом мажоритарного элемента 9. Пятый информационный вход 5 соединен со вторым входом мажоритарного элемента 9, с третьим входом первого элемента ИЛИ 10 и третьим входом пятого элемента И 17. Первый настроечный вход 6 соединен со вторым входом третьего элемента И 15, вторым входом шестого элемента И 18, четвертым входом первого элемента И 13, первым входом второго элемента И 14 и через первый элемент НЕ 20 с третьим входом четвертого элемента И 16 и первым входом седьмого элемента И 19. Второй настроечный вход 7 соединен с четвертым входом четвертого элемента И 16 и через второй элемент НЕ 21 со вторым входом седьмого элемента И 19. Выход первого элемент ИЛИ 10 соединен с первым входом первого элемента И 13 и третьим входом третьего элемента ИЛИ 12, выход первого элемента И 13 соединен с первым входом второго элемент ИЛИ 11. Выход второго элемента И 14 соединен со вторым входом второго элемента ИЛИ 11. Выход мажоритарного элемента 9 соединен с третьим входом третьего элемента И 15 и третьим входом шестого элемента И 18. Выход пятого элемента И 17 соединен с вторым входом второго элемента И 14 и пятым входом четвертого элемента И 16. Выход третьего элемента ИЛИ 12 соединен с третьим входом седьмого элемента И 19. Выход третьего элемента И 15 соединен с третьим входом второго элемента ИЛИ 11. Выход шестого элемента И 18 соединен с четвертым входом второго элемента ИЛИ 11. Выход четвертого элемента И 16 соединен с пятым входом второго элемента ИЛИ 11. Выход седьмого элемента И 19 соединен с шестым входом второго элемента ИЛИ 11. Выход второго элемента ИЛИ 11 соединен с выходом устройства 8.

Работа многофункционального мажоритарного модуля осуществляется следующим образом.

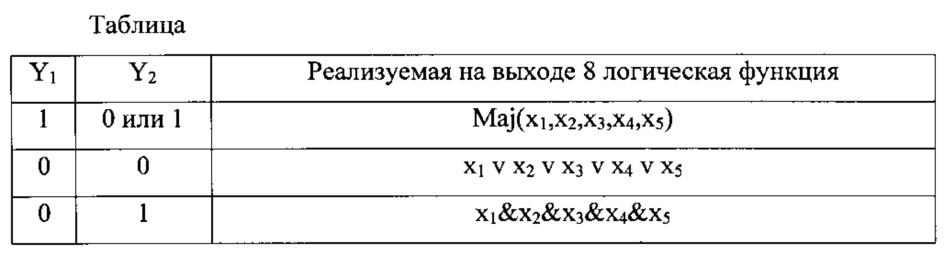

На входы 1, 2, 3, 4, 5 устройства подаются значения входных двоичных сигналов x1,x2,x3,x4,x5 ∈ {0, 1}. На вход 6 подается значение первого настроечного сигнала Y1, на вход 7 подается значение второго настроечного сигнала Y2, где Y1,Y2 ∈ {0, 1}. В таблице приведены значения настроечных сигналов для реализации соответствующих логических функций.

На выходе 8 реализуется выбранная для реализации логическая функция.

Заявленное устройство имеет те же функциональные возможности, как и прототип.

Сравним быстродействие прототипа и заявляемого устройства.

Мажоритарный элемент реализует логическую функцию Х1Х2 v Х1Х3 v Х2Х3, и при его реализации на элементах И и ИЛИ задержка сигнала в нем

Тмаж=Ти+Тили.

В заявленном устройстве максимальная задержка сигнала будет по цепи: входы устройства 2, 4, 5, мажоритарный элемент 9, элемент И 15 (или элемент И 18), элемент ИЛИ 11, выход 8 устройства

Тзаяв=Тмаж+Ти+Тили=2Тмаж.

Такая же задержка будет и по цепи: входы устройства 2, 4, 5, элемент ИЛИ 10, элемент ИЛИ 12, элемент И 19, элемент ИЛИ 11, выход 8 устройства.

В прототипе максимальная задержка Тпрот=4Тмаж.

Следовательно, заявленное устройство имеет большее быстродействие.

Сравним сложность реализации заявленного устройства и прототипа на элементах И, ИЛИ, НЕ, которая определяется суммарным количеством входов в используемые элементы.

Мажоритарный элемент реализует булеву функцию Х1Х2 v Х1Х3 v Х2Х3, и при его реализации на элементах И и ИЛИ его сложность Смаж составляет 9 входов.

Сложность прототипа:

Спрот=9Смаж+8=9×9+8=89.

Сложность заявленного устройства:

Сзаяв=Смаж+37=46.

Следовательно, заявленное устройство имеет меньшую сложность.

Реферат

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др. Техническим результатом изобретения является повышение быстродействия устройства и уменьшение его сложности при реализации мажоритарной функции, дизъюнкции, конъюнкции пяти аргументов. Многофункциональный мажоритарный модуль содержит пять информационных входов, два настроечных входа, выход модуля, мажоритарный элемент, три элемента ИЛИ, семь элементов И, два элемента НЕ. 1 ил., 1 табл.

Комментарии