Микросхемная сборка и способ изготовления микросхемной сборки - RU2635852C2

Код документа: RU2635852C2

Чертежи

Описание

Настоящее изобретение относится к микросхемной сборке с соединительной подложкой и несколькими расположенными на соединительной подложке полупроводниковыми подложками, причем расположенные на контактной поверхности полупроводниковой подложки контактные площадки соединены с контактными площадками на контактной поверхности соединительной подложки.

С увеличивающейся миниатюризацией электронных приборов возрастают также требования к плотности упаковки используемых в них электронных модулей. В особой степени это касается модулей памяти или расширений памяти, которые, как правило, собраны из большого числа микросхем памяти, которые находятся в электрическом контакте через общую контактную подложку.

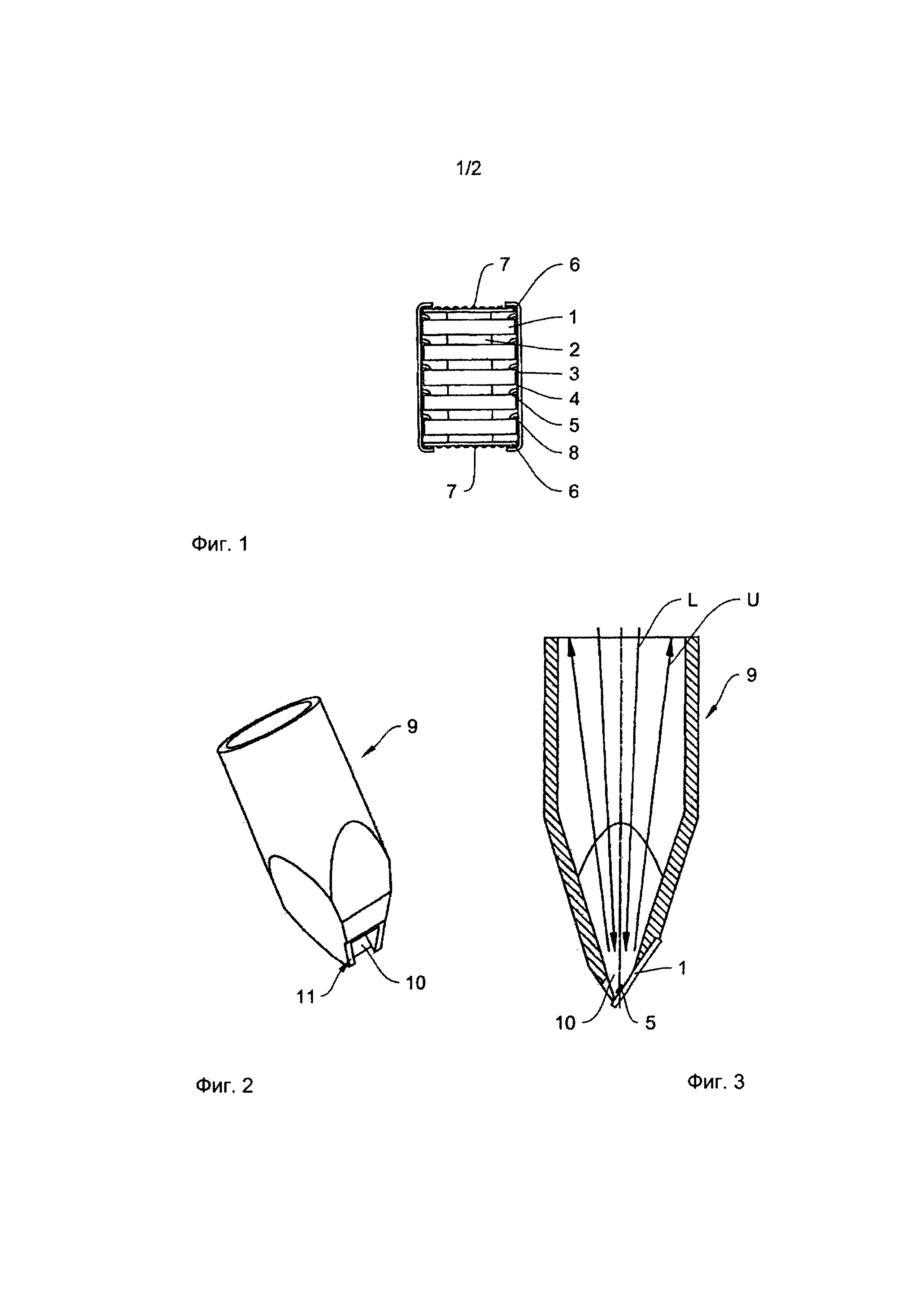

Из DE 19626126 А1 известна показанная схематически на фиг. 1 микросхемная сборка, которая собрана как штабельная укладка в виде многослойной конструкции с чередующимся расположением микросхем 1 и расположенных между ними клеевых слоев 2, которые, с одной стороны, обеспечивают монолитность штабельной сборки, а с другой стороны, делают возможным расположением отдельных микросхем 1 на расстоянии друг от друга. Сбоку от штабельной сборки предусмотрены подложки 3 с контактными проводниками, которые оснащены отдельными токопроводящими дорожками 4, которые делают возможным контактирование контактных площадок 5 микросхем 1 с ограничивающей штабельную сборку вверху и внизу соединительной подложкой 6, соединительные контакты 7 которой служат для внешнего электрического контактирования микросхемной сборки. Для создания электрического контакта между контактными площадками 5 микросхем 1 и токопроводящими дорожками 4 подложки 3 с контактными проводниками предусмотрены паяные соединения 8.

Учитывая сложную конструкцию показанной на фиг. 1 микросхемной сборки, является очевидным, что и изготовление микросхемной сборки является, соответственно, трудоемким с большим числом следующих друг за другом стадий способа, которые делают необходимым использование разных инструментов для изготовления штабельной сборки с расположенными друг над другом и отделенными друг от друга клеевыми слоями 2 микросхемами 1 и для создания паяных соединений 8 между контактными площадками 5 микросхемы 1 и токопроводящими дорожками 4 подложки 3 с контактными проводниками.

Исходя из уровня техники, в основу изобретения положена задача предложить микросхемную сборку, которая является легко изготавливаемой, а также способ, который делает возможным простое изготовление микросхемной сборки.

Эта задача решена микросхемной сборкой с признаками п. 1 формулы изобретения, а также способом изготовления микросхемной сборки с признаками п. 7 формулы изобретения.

У микросхемной сборки согласно изобретению микросхемы боковой кромкой простираются параллельно, а контактной поверхностью - перпендикулярно контактной поверхности соединительной подложки, причем в соединительной подложке расположены сквозные соединения, которые соединяют расположенные на внешней контактной стороне внешние контакты с выполненными на контактной поверхности соединительной подложки в виде внутренних контактов контактными площадками, причем расположенные смежно боковой кромке контактные площадки полупроводниковых подложек через переплавленный запас (депо) припоя соединены с внутренними контактами соединительной подложки. Микросхемная сборка согласно изобретению делает возможным, таким образом, рядовое расположение микросхем, причем микросхемы соединены с соединительной подложкой только на одной боковой кромке.

Предпочтительно, внутренние контакты соединительной подложки и контактные площадки микросхем расположены относительно друг друга так, что они образуют пространственный угол, так что переплавка расположенных только на внутренних контактах соединительной подложки запасов припоя делает возможным смачивание контактных площадок микросхем.

Является предпочтительным, если образованный между внутренними контактами и контактными площадками пространственный угол имеет угол раствора α между 30° и 150°, причем угол раствора α между 60° и 120°, и прежде всего 90°, делает возможным особо компактное выполнение микросхемной сборки.

Если боковые кромки микросхем и контактная поверхность соединительной подложки находятся на расстоянии друг от друга за счет заполняемой щели, то эта заполняемая щель для создания особо устойчивого к действию нагрузки механического соединения между микросхемами и соединительной подложкой может быть заполнена заливочным компаундом.

В предложенном в изобретении способе изготовления микросхемной сборки с соединительной подложкой и несколькими расположенными на соединительной подложке полупроводниковыми подложками, прежде всего микросхемами, причем расположенные на контактной поверхности полупроводниковой подложки контактные площадки соединены с контактными площадками на контактной поверхности соединительной подложки, микросхемы располагают с их боковой кромкой параллельно, а их контактной поверхностью перпендикулярно контактной поверхности соединительной подложки таким образом, что расположенные смежно боковой кромке контактные площадки микросхем соотнесены с образующими внутренние контакты контактными площадками соединительной подложки, которые через выполненные в соединительной подложке сквозные соединения соединены с расположенными на внешней контактной стороне соединительной подложки внешними контактами, и затем происходит соединение внутренних контактов с контактными площадками посредством переплавленного запаса припоя.

Когда для создания соединения между контактными площадками микросхемы и внутренними контактами соединительной подложки происходит размещение запасов припоя на внутренних контактах соединительной подложки, можно отказаться от нанесения припоя на несколько микросхем. Более того, необходимо нанесение запасов припоя только на внутренние контакты соединительной подложки, которая, кроме этого, уже может находиться в подходящем для оснащения микросхемами положении.

Если размещение запасов припоя на внутренних контактах соединительной подложки происходит перед позиционированием полупроводниковых подложек на контактной поверхности соединительной подложки, то нанесение припоя не затрудняется уже установленными микросхемами.

Является особо предпочтительным, когда позиционирование микросхем на контактной поверхности происходит посредством монтажного инструмента так, что микросхемы захватываются монтажным инструментом, ориентируются согласно желаемому положению относительно соединительной подложки и удерживаются в этом положении.

Предпочтительно, микросхемы позиционно удерживаются так, что между боковыми кромками микросхем и контактной поверхностью соединительной подложки образуется заполняемая щель.

Является особо предпочтительным, когда позиционирование микросхем происходит так, что внутренние контакты соединительной подложки и контактные площадки микросхем расположены относительно друг друга так, что между ними образован угол раствора α.

Предпочтительно, удержание микросхем происходит посредством пониженного давления.

Когда происходит переплавка запаса припоя для создания соединения между внутренними контактами соединительной подложки и контактными площадками микросхемы во время позиционирования микросхемы, позиционирование и переплавка могут происходить в общей стадии способа.

Предпочтительно, переплавка запаса припоя происходит посредством энергии лазера так, что воздействие лазерного излучения на запас припоя осуществляется сквозь монтажный инструмент.

Для особо простого выполнения рядового расположения микросхем позиционирование микросхем на контактной поверхности соединительной подложки и соединение контактных площадок микросхем с внутренними контактами соединительной подложки происходит последовательно так, что в направлении монтажа параллельно контактной поверхности соединительной подложки позиционируют одну микросхему за другой и соединяют с соединительной подложкой.

Ниже изобретение будет более подробно разъяснено со ссылкой на рисунки, причем, прежде всего, более подробно будет разъяснен способ изготовления микросхемной сборки согласно изобретению.

Показано на:

Фиг. 1: микросхемная сборка согласно уровню техники,

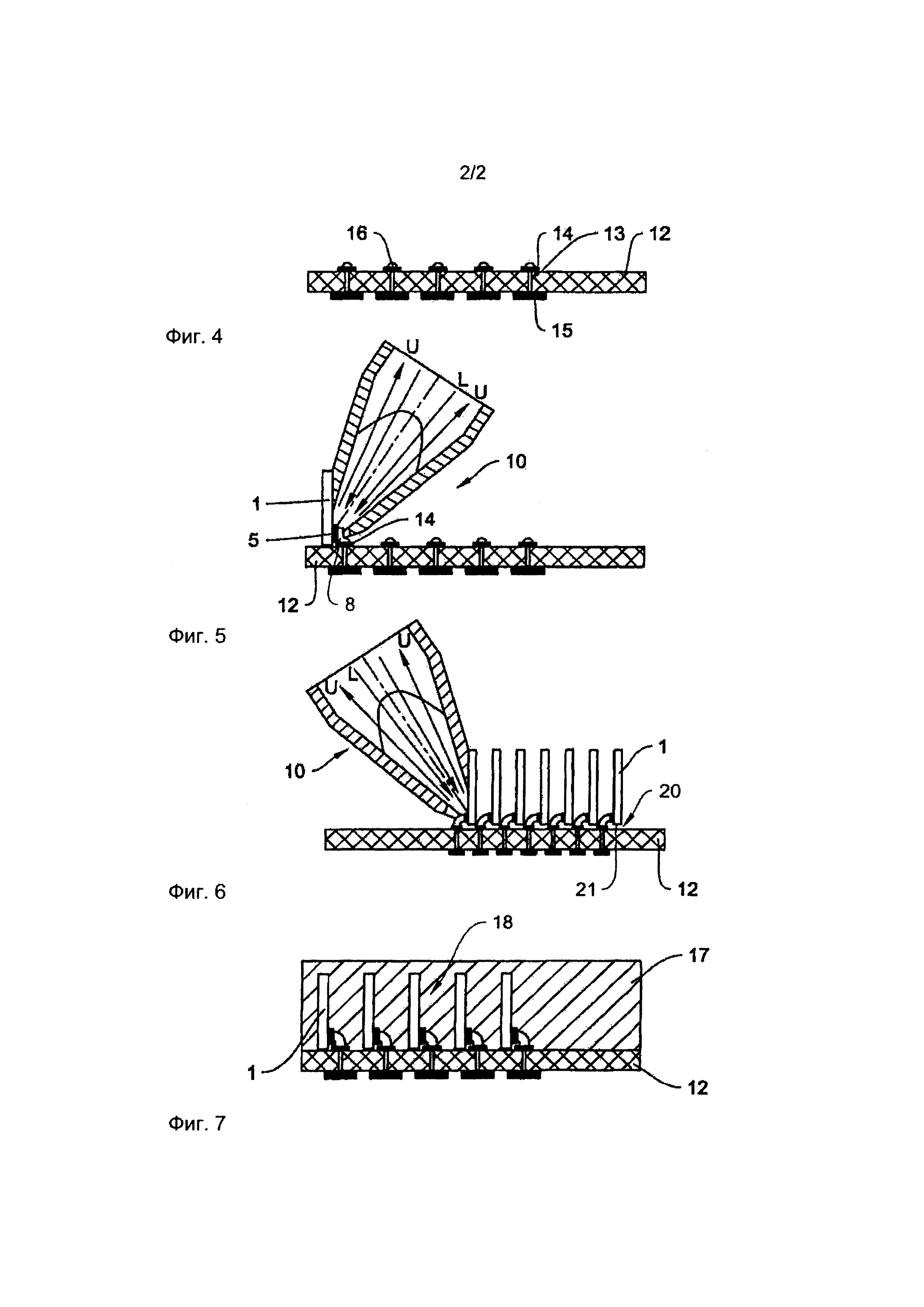

Фиг. 2: пример выполнения пригодного для изготовления микросхемной сборки монтажного инструмента,

Фиг. 3: изображение в продольном разрезе монтажного инструмента,

Фиг. 4: соединительная подложка микросхемной сборки,

Фиг. 5: позиционирование микросхемы на показанной на фиг. 4 соединительной подложке,

Фиг. 6: продолжающееся в направлении монтажа позиционирование микросхем на соединительной подложке,

Фиг. 7: микросхемная сборка с заливкой.

На фиг. 4-7 показаны следующие друг за другом стадии способа изготовления микросхемной сборки 18, которая для образования корпуса снабжена заливочным компаундом, причем сначала происходит подготовка показанной на фиг. 4 соединительной подложки 12, которая снабжена сквозными соединениями 13 для создания электропроводящего соединения между внутренними контактами 14, которые расположены на контактной поверхности соединительной подложки 12, и внешними контактами 15, которые расположены на стороне внешних контактов соединительной подложки 12.

На фиг. 2 и 3 показан используемый для изготовления представленной на фиг. 7 микросхемной сборки 18 монтажный инструмент 9 в изометрическом изображении. Монтажный инструмент 9 на конце канала имеет оконное отверстие 10 с позиционирующей рамкой 11, которая, как показано на фиг. 3, делает возможным точное позиционирование микросхемы 1 в оконном отверстии 10. Канал монтажного инструмента 9 делает возможным как приложение пониженного давления U к помещенной в позиционирующую рамку 11 микросхеме 1, так и воздействие лазерным излучением L на микросхему 1. Пониженное давление U делает возможным фиксированное удержание микросхемы 1 на позиционирующей рамке 11. Воздействие лазерным излучением L на микросхему 1 делает возможным определенное нагревание кремниевого корпуса микросхемы 1 и, таким образом, расположенных на контактной поверхности микросхемы 1 контактных площадок 5.

Как показано на фиг. 4, внутренние контакты 14 соединительной подложки 12 для подготовки к последующему контактированию с контактными площадками 5 микросхемы 1 снабжены запасом 16 припоя.

Затем проводится, как показано на фиг. 5 и 6, начиная с расположенной на краю соединительной подложки 12 микросхемы 1, последовательное контактирование отдельных микросхем 1, причем монтажным инструментом 9 посредством пониженного давления захватывается каждая отдельная микросхема 1 и ориентируется согласно ее желательного положения относительно соединительной подложки 12 так, что внутренние контакты 14 и контактные площадки 5 расположены относительно друг друга так, что они образуют пространственные углы, причем в данном случае образованный между внутренними контактами 14 и контактными площадками 5 угол раствора α образуется равным 90°. В этом относительном положении происходит, по меньшей мере, частичное расплавление запаса 16 припоя посредством излучающего лазерное излучение L источника энергии, так что после кратковременного расплавления происходит быстрое затвердевание выполненного из запаса 16 припоя паяного соединения 8.

Затем, как показано на фиг. 6, для выполнения рядового расположения микросхем 1 посредством монтажного инструмента 9 друг за другом последовательно позиционируются и контактируются дополнительные микросхемы 1. При этом микросхемы 1 позиционируются так, что между боковой кромкой 21 микросхем и контактной поверхностью соединительной подложки 12 образуется заполняемая щель 20, которая, как понятно из фиг. 7, после окончательного изготовления ряда из микросхем 1 заполняется заливочным компаундом 17.

Монтажный инструмент 9 делает возможным, таким образом, как определенное позиционирование микросхем 1 на соединительной подложке 12, так и расплавление запаса 16 припоя для создания паяного соединения 8 между внутренними контактами 14 соединительной подложки 12 и контактными площадками 5 микросхем 1. За счет этого происходит размещение микросхем 1 на соединительной подложке 12 и создание электропроводящего соединения путем расплавления запаса 16 припоя для образования паяного соединения 8 в одной общей стадии процесса, а не последовательно посредством двух разных инструментов, как это имеет место в случае описанного со ссылкой на фиг. 1 уровня техники.

Как показано на фиг. 6, все микросхемы 1 одна за другой располагаются на соединительной подложке 12 и электропроводяще соединяются с соединительной подложкой 12, причем микросхемы 1 после произошедшего расплавления запаса 16 припоя до повторного затвердевания паяного соединения в виде паяного соединения 8 удерживаются монтажным инструментом 9, так что для фиксации относительного расположения микросхем 1 не требуются расположенные между отдельными микросхемами 1 клеевые слои 2, как это имеет место в случае показанного на фиг. 1 уровня техники.

После окончательного оснащения соединительной подложки 12 желаемым количеством микросхем 1 теперь, как показано на фиг. 7, посредством заливочного компаунда 17, который наносится на соединительную подложку 12, может быть создано герметично закрытое, экранированное от внешних воздействий соединение микросхем 1 с соединительной подложкой 12.

Реферат

Использование: для микросхемной сборки. Сущность изобретения заключается в том, что микросхемная сборка содержит соединительную подложку с несколькими расположенными на соединительной подложке полупроводниковыми подложками, прежде всего микросхемами, причем расположенные на контактной поверхности микросхем контактные площадки соединены с контактными площадками на соединительной подложке, причем микросхемы боковой кромкой простираются параллельно, а контактной поверхностью - перпендикулярно контактной поверхности соединительной подложки, причем в соединительной подложке расположены сквозные соединения, которые соединяют расположенные на внешней контактной стороне внешние контакты с выполненными на контактной поверхности соединительной подложки в виде внутренних контактов контактными площадками, причем расположенные смежно боковой кромке контактные площадки микросхем соединены с внутренними контактами соединительной подложки посредством переплавленного запаса припоя. Технический результат: обеспечение возможности простого изготовления микросхемной сборки. 2 н. и 23 з.п. ф-лы, 7 ил.

Комментарии