Тестовая интегральная структура - RU2034306C1

Код документа: RU2034306C1

Чертежи

Описание

Изобретение относится к тестовой интегральной структуре, а более точно к чипу полупроводниковой интегральной схемы (ИС), имеющему внутри схему идентификации для сортировки чипов при проверке.

В последнее время в связи с развитием полупроводниковой техники во всех областях промышленности возрастает тенденция внедрения электронных систем. Но для каждой области требуется соответствующая характеристика электронной системы, чтобы удовлетворить различные требования пользователей. Например, поскольку емкость ЗУПВ (запоминающее устройство с произвольной выборкой) для управления дисплеем была увеличена до Мегабит, в дополнение к основному типу ЗУПВ разрабатываются иные типы. А именно, ЗУПВ для управления дисплеем на 1 или 4 Мбит подразделяются на 1-битовое, 4-битовое, 8-битовое и т.д. в соответствии с числом выходных данных, а также на быстродействующее постраничное, полубайтовое тип, статическое постолбцовое и т.д. в соответствии с входным сигналом управления. Поэтому, чтобы удовлетворить требования пользователей, поставщики ЗУПВ для управления дисплеем предусматривают ЗУПВ различных типов, работающие в различных режимах. При этом на одной линии производства ЗУПВ могут изготавливаться как основные ЗУПВы быстродействующего постраничного типа, и дополнительно ЗУПВы для управления дисплеем полубайтового или статического постолбцового типа, и проверки изделия отправляются как готовая продукция.

В случае производства ЗУПВ для управления дисплеем различных типов на одной линии кристаллы или чипы, относящиеся к различным типам ЗУПВ, часто смешиваются друг с другом. На этапе контроля ошибки выявляются, несоответствующие изделию чипы бракуются, что приводит к снижению производительности.

Кроме того, чтобы предотвратить смешивание кристаллов одного вида с кристаллами другого вида, требуется большое внимание, что снижает эффективность производства.

Соответственно, требуется техника, которая позволяет сортировать или идентифицировать чипы одного и того же типа на этапе проверки, когда перед запрессовкой чипы различных видов смешиваются друг с другом.

Такой способ идентифицирования полупроводниковых чипов описан в патентах США N 4150331 и 4510673. По патенту N 4150331 каждый чип идентифицируется путем использования на поверхности чипа программируемой схемы. Схема должна программироваться идентификационным кодом в соответствии с тем, образован или нет диод между дополнительной испытательной и диагностической клеммой и выбранной входной/выходной клеммой.

Однако этот способ контроля приводит к увеличению размеров корпуса из-за дополнительно предусмотренной испытательной клеммы, что имеет важное значение для стоимости полупроводникового чипа.

В патенте США N 4510673 раскрывается способ, при котором на заднюю поверхность полупроводникового чипа, используя лазерное устройство, наносят специфическую идентификационную отметку, и человек либо машина с помощью лазерного или оптического устройства может различить эту отметку. Недостаток способа заключается в использовании дорогостоящего лазерного устройства.

Целью настоящего изобретения является создание тестовой интегральной структуры, имеющей новый блок идентификации, который не нуждается в дополнительной испытательной и диагностической клемме, обладает повышенной надежностью, прост по конструкции и облегчает идентификацию полупроводникового чипа.

Указанные цели изобретения обеспечиваются тестовой интегральной структурой, содержащей первую и вторую клеммы для подключения напряжения питания, N входных клемм, блок идентификации, подключенный между первой или второй клеммами для подключения напряжения питания и одной из входных клемм, при этом в нее введены N блоков защиты входов, выходы которых соединены соответственно с одноименными клеммами блока идентификации и объекта контроля, где N число выводов объекта контроля, каждая из N входных клемм соединена соответственно с одноименными входами блока защиты входов, первая клемма для подключения напряжения питания соединена с соответствующим входом первого блока защиты входов, а первый и второй выходы каждого предыдущего блока защиты входов соединены соответственно с одноименными входами каждого последующего блока защиты входов, выход N-го блока защиты входов подключен к второй клемме для подключения напряжения питания, а блок идентификации содержит ограничитель напряжения и плавкую перемычку, первый вывод которой соединен с выходом ограничителя напряжения, а второй вывод подключен к второй клемме для подключения напряжения питания; ограничитель напряжения содержит N последовательно соединенных МОП-транзисторов, затворы которых соединены с их соответствующими стоками, которые соединены с одноименными клеммами блока идентификации, а исток N-го МОП-транзистора является выходом ограничителя напряжения.

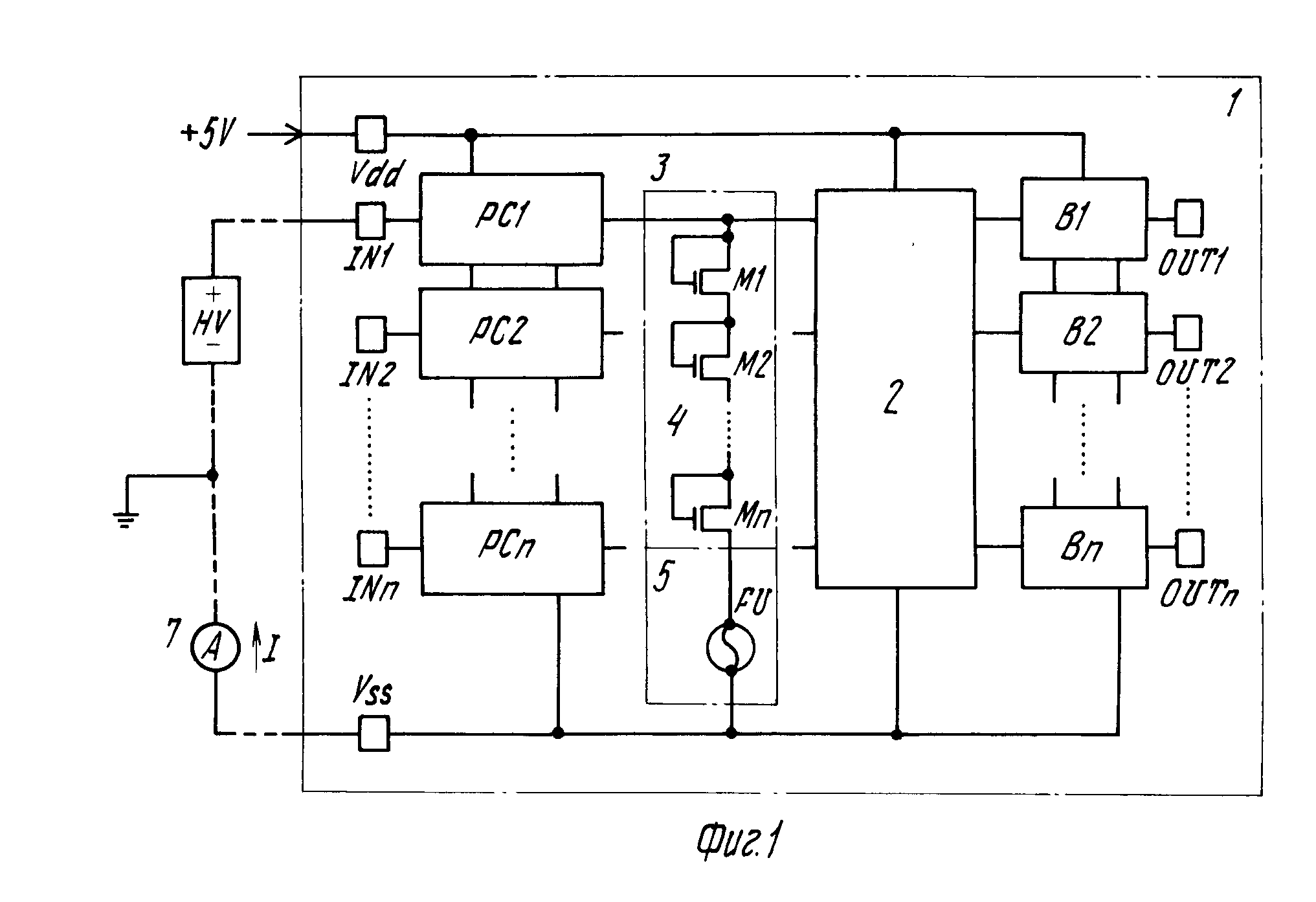

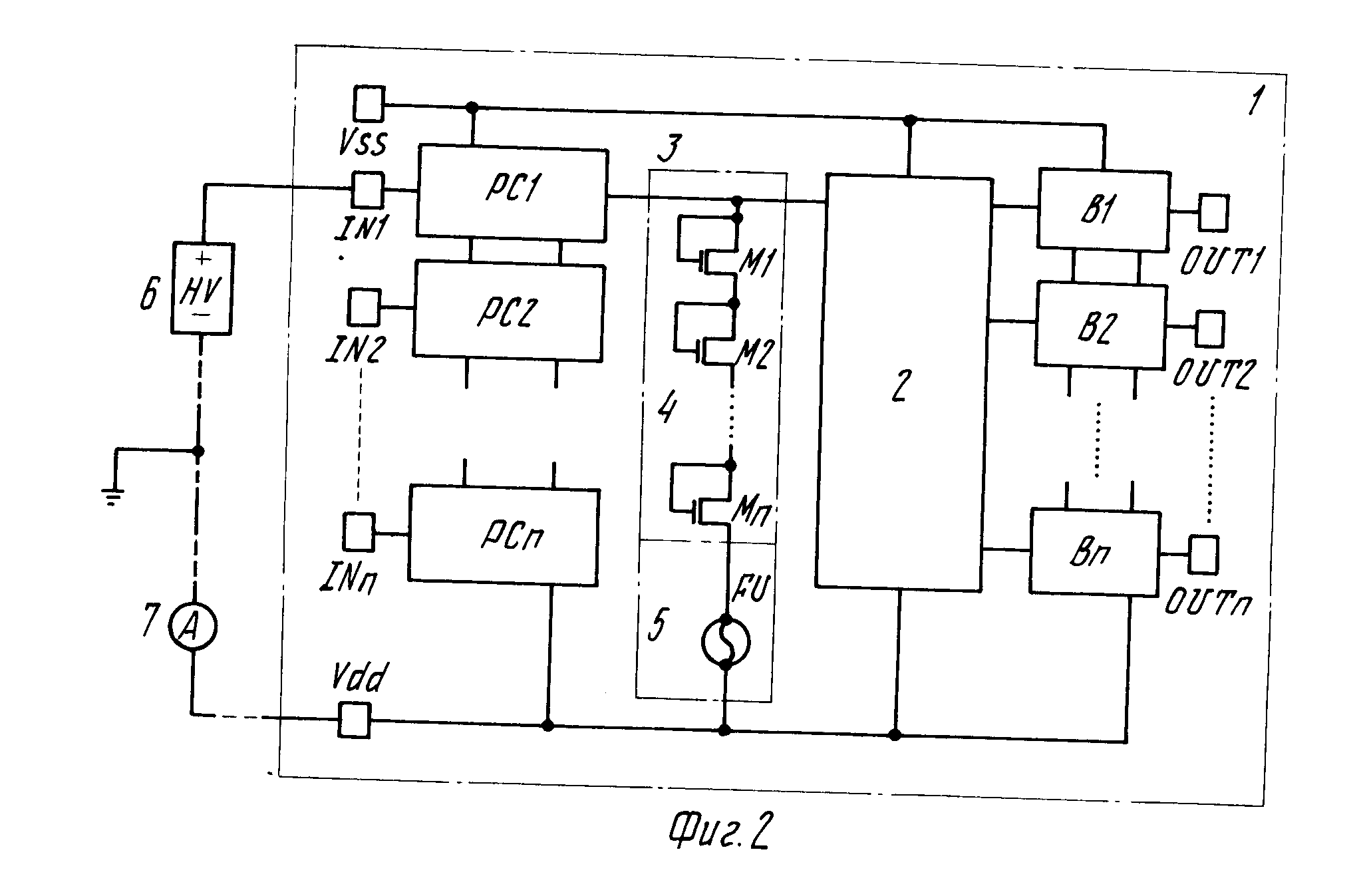

На фиг. 1 и 2 показаны варианты тестовой интегральной структуры, имеющей схему идентификации в соответствии с изобретением; на фиг. 3 схема идентификации чипов, вариант.

Тестовая интегральная структура 1 включает внутреннюю схему 2, блоки защиты входов PC1-PCn, выходные буферы B1-Bn, входные клеммы 1N1-1Nn, выходные клеммы OUT1-OUTn и пару клемм питания Vdd и Vss. Интегральная структура подключается к источнику питания (не показан), чтобы получать напряжение питания, например, 5 В через клемму напряжения питания Vdd и потенциал земли через клемму напряжения питания Vss. Внутренняя схема 2, получающая рабочее напряжение от указанных клемм напряжения питания Vdd и Vss, выполняет заданную функцию путем приема входных сигналов, подаваемых на входные клеммы 1N1-1N3, и генерирует предопределенные выходные сигналы на выходных клеммах OUT1-OUTn. Кроме того, указанные входные клеммы соединены с внутренней схемой 2 через соответствующие блоки защиты входов PC1-PCn, которые предотвращают пробой внутренней схемы 2 вследствие напряжения помехи, например всплеска, поступающего на входные клеммы.

Выходные клеммы OUT1-OUTn соединены с внутренней схемой 2 через выходные буферы B1-Bn, соответственно.

Блок идентификации 3 отличительная часть настоящего изобретения подключен между одной входной клеммой 1N1 и клеммой напряжения питания Vss тестовой интегральной структуры 1. Этот блок идентификации содержит ограничитель напряжения 4 и дополнительное устройство 5. Ограничитель напряжения 4 предусмотрен для ограничения по уровню входного сигнала, подаваемого между клеммой IN1 и схеммой питания Vss, до предопределенного логического уровня, который должен подаваться на внутреннюю схему 2. Этот ограничитель напряжения 4 состоит из множества последовательно соединенных МОП-транзисторов M1-Mn, затворы которых соединены с их соответствующими стоками. Кроме того, ограничитель напряжения 4 может устанавливать предопределенный логический уровень путем суммирования порогового напряжения каждого МОП-транзистора.

Например, когда на входную клемму подается уровень ТТЛ, будет установлен предопределенный логический уровень примерно более чем 2,5 В, и примерно более + 3 В, когда на входную клемму подается уровень КМОП.

Хотя в данном примере реализации используется диодная конфигурация МОП-транзисторов, отмечается, что в качестве ограничителя напряжения может использоваться любое устройство одностороннего пропускания тока, имеющее предопределенное пороговое напряжение, например диод с p-n-переходом или Зенеровский диод, либо т.п.

Предусмотрено дополнительное устройство 5, определяющее прохождение тока через ограничитель напряжения 4 во время процесса производства и соединенное с ограничителем напряжения 4. Вид чипа определяется соединением или разъединением плавкой перемычки или металлической проволочки во время процесса производства. После того как образуется плавкая перемычка, идентификационная информация записывается посредством выжигания плавкой перемычки лазером.

Например, во время процесса производства чипа плавкая перемычка FU в чипе для ЗУПВ быстродействующего постраничного типа сохраняется соединенной, а для ЗУПВ полубайтового типа выжигается, тем самым создается возможность идентифицировать чипы. Во время контроля процесса производства чипов с указанной идентификацией входная клемма IN1 соединяется с предопределенным источником высокого напряжения 6 (примерно 15 В), а клемма напряжения питания Vss соединяется с амперметром 7, и тогда можно различить вид ЗУПВ. Если ток протекает, образец идентифицируется как ЗУПВ быстродействующего постраничного типа, а если ток не протекает, он идентифицируется как ЗУПВ полубайтового типа. Протекание тока контролируется амперметром 7.

Здесь в случае ЗУПВ полубайтового типа плавкая перемычка выжигается, так что во время нормальной работы чипа входной сигнал передается на внутреннюю схему 2 независимо от наличия блока идентификации 3, а в случае ЗУПВ быстрого постраничного типа, если бы не было ограничителя напряжения 4, входная клемма IN1 через плавкую перемычку FU всегда была бы в состоянии логического "0". Ограничитель напряжения 4 предотвращает возникновение этого явления. Более подробно, когда на входную клемму IN1 подается логический "0", логический "0" вводится во внутреннюю схему 2 независимо от подключения схемы идентификации 3, а когда на входную клемму IN1 подается логическая "1", через схему идентификации течет ток, создавая на ограничителе напряжения 4 предопределенную разность напряжений, которая вводит на внутреннюю схему 2 логическую "1".

Схема идентификации 3 предпочтительно подключается к входной клемме IN1 через схему защиты входа PC1, которая защищает схему идентификации от порчи из-за внешнего выброса или т.п. На фиг. 2 показана тестовая интегральная структура в соответствии с настоящим изобретением, в которой конфигурация такая же, как и на фиг. 1, на блок идентификации 3 включен между клеммой напряжения питания Vdd и входной клеммой IN1. Поскольку напряжение +15 В, подаваемое на входную клемму, выше, чем напряжение +5 В, подаваемое на клемму напряжения питания Vdd, во время проверки идентификации принцип работы чипа тот же самый, что и в первом примере реализации.

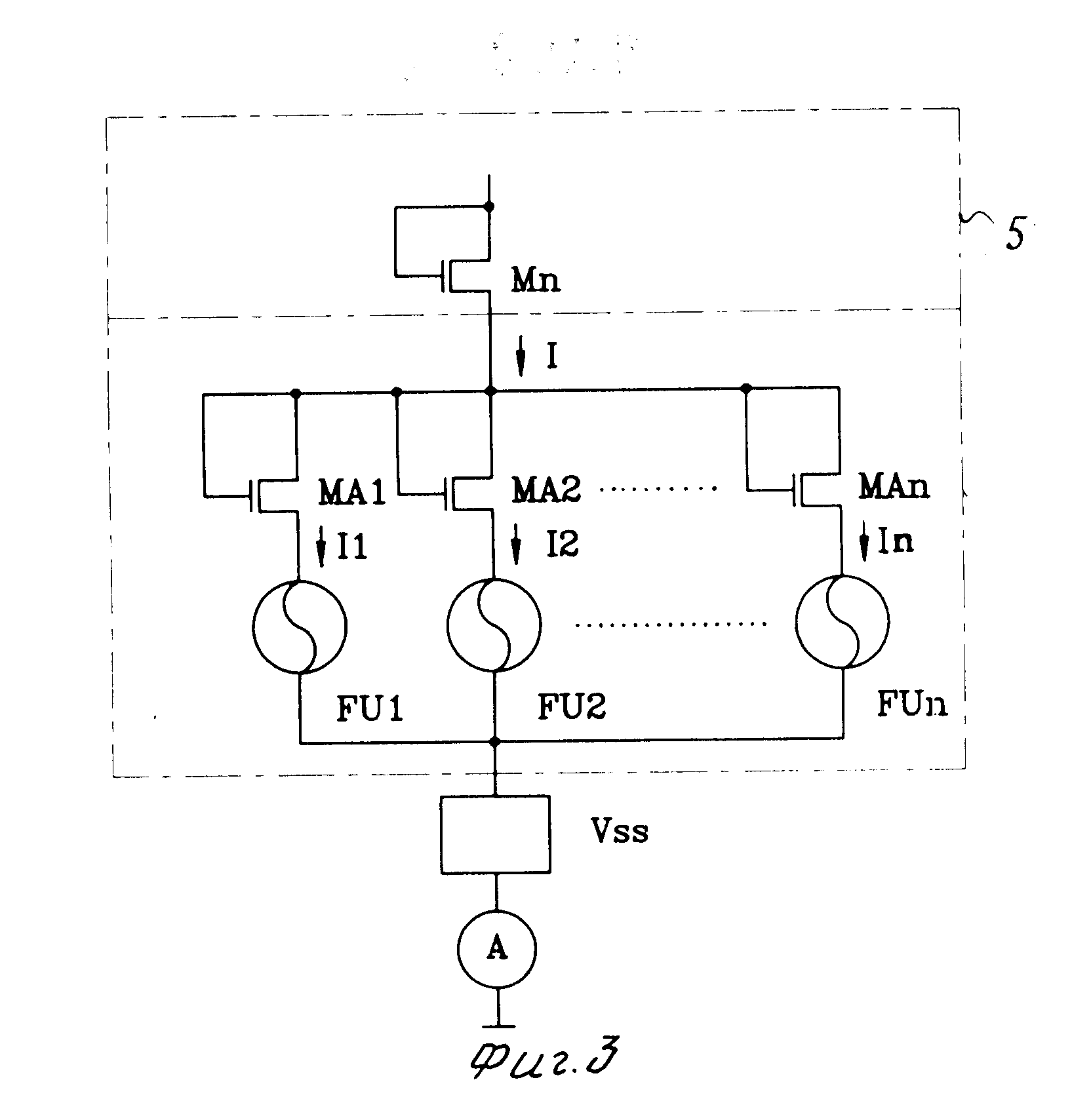

Показанное на фиг. 3 дополнительное устройство 5 содержит множество МОП-транзисторов MA1-MAn, затворы которых соединены с их стоками, и множество плавких перемычек FU1-FUn, подключенных к соответствующим МОП-транзисторам. Каждая комбинация МОП-транзистора и плавкой перемычки включена параллельно другой между ограничителем напряжения 4 и клеммой питания Vss (или Vdd).

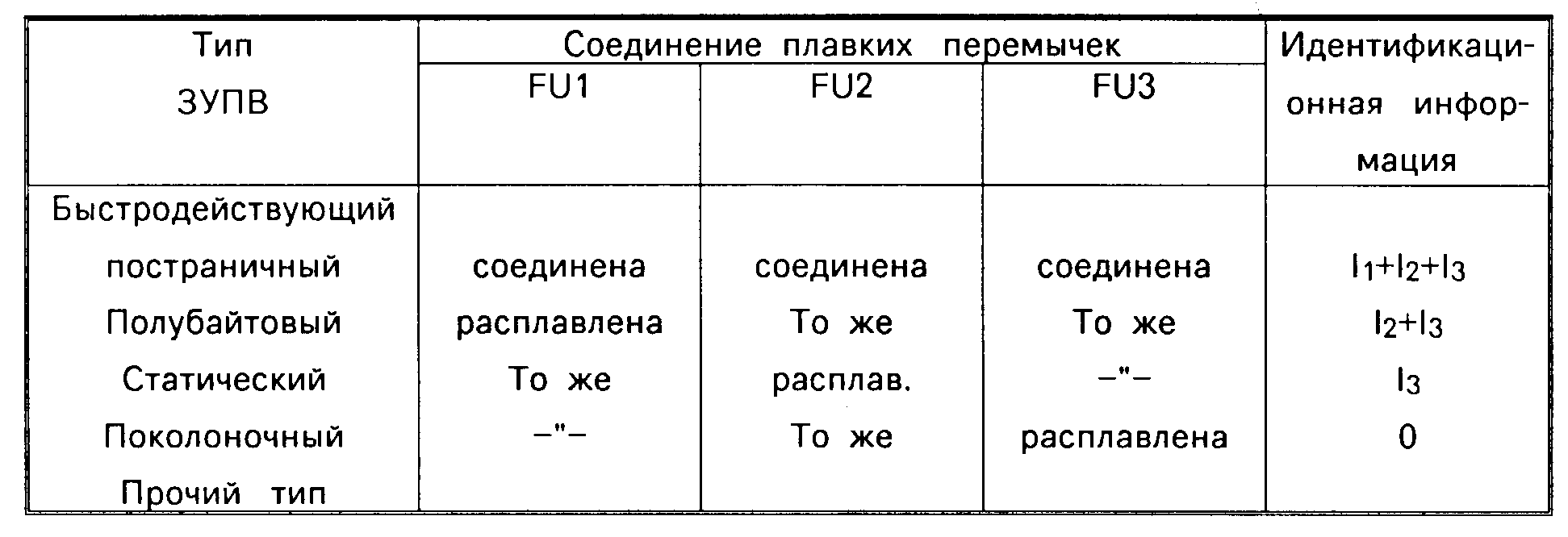

Для того чтобы идентифицировать этой схемой, идентификационная информация может задаваться значениями токов, протекающих через дополнительное устройство, как показано в таблице.

В соответствии с изобретением, идентификационная информация записывается посредством предусмотренного соединения или разъединения простой цепи во время процесса производства кристалла, а записанная информация идентификации детектируется на этапе контроля процесса сборки чипа, так что можно определять чипы одного и того же типа и раздельно обрабатывать их в последующем процессе.

Идентификация чипа по изобретению выполняется через входные и выходные клеммы и клеммы питания, так что обычная система производства используется до предела без каких-либо изменений, что очень экономично.

Кроме того, чип по настоящему изобретению не требует дополнительной испытательной и диагностической клеммы и лазерного оборудования или т.п. для его идентификации.

Следует заметить, что чип в соответствии с настоящим изобретением в примерах реализации приспособлен к МОП-транзисторам, но может при необходимости быть приспособлен к различным применениям. Таким образом, настоящий чип может модифицироваться в различные виды в объеме настоящего изобретения.

Реферат

Изобретение относится к полупроводниковым интегральным схемам. Тестовая интегральная структура содержит первую и вторую клемму для подключения напряжения питания, входные клеммы, блок идентификации, подключенный между первой и второй клеммами, первый и второй блоки защиты входов, выходы которых соединены с одноименными клеммами блока идентификации и объекта контроля, при этом блок идентификации содержит ограничитель напряжения и плавкую перемычку, а ограничитель напряжения выполнен на последовательно соединенных МОП-транзисторах, затворы которых соединены с их соответствующими стоками. 3 ил., 1 табл.

Комментарии