Изобретение относится к автомати ке, вычислительной и измерительной технике и может быть использовано

при разработке цифровых систем управления , в качестве специализирова ного вычислителя, входящего в соста

устройств., автоматики, управления и контроля. Известно яастотно-импульсное

устройство для возведения в степень содержащее двоичный делитель, схему

выделения периода, схему управления умножитель, два реверсивных счетчика схемы и и ИЛИ, счетчик степени,

ключи набора возводимой степени l. Недостатком устройства является

его сложность и невозможность воспроизведения функции вида U kx Наиболее близким rio технической

сущности к предлагаемому вычислител ному устройству является устройство

для воспроизведения степенной зависимости у цифровым регулируемы показателем, содержащее информацион

ный вход, первый, второй, третий, четвертый,и пятый счетчики, регистр управляющего кода, схему сравнения

кодов, первую и вторую группы элеме тов И, первый и второй элементы ИЛИ счетчик-делитель.

I Однако известное устройство воепроизводит только функции с целочислеиным показателем степени,и не

воспроизводит функции вида u.K.x«b,y, К недостаткам этого устройства

этносятся также большие аппаратурные эатраты. Целью изобретения является расши

рение функциональных возможностей за счет воспроизведения функций |Видаи«к.х и снижение аппаратурных

затрат., Поставленная цель достигается тем, что в вычислительное устройство

, содержащее первый и второй счет чики, первую и вторую группы элементов И, первый и второй элементы

ИЛИ, причем выход младшего разряда первого счётчика соединён с импульс ным входом i-ro элемента И первой группы, где i-количество разрядов

первого и второго счетчиков, потенциальный вход которого подключен к выходу старшего разряда второго

счетчика, выходы элементов И первой и второй групп соединены соответственно

со входами первого и второго элементов ИЛИ, введены дополнительно реверсивный счетчик, формирователь

импульса, вычитатель, коммутатор, генератор опорной частоты, первый

и второй триггеры, первый, второй, третий, четвертый, пятый и шестой

элементы И, третий и четвертый элементы ИЛИ, выход второго элемента

ИЛИ соединен с первыми входами первого и второго элементов И, выходы

которых подключены соответственно , к вычитаквдему и суммирукхчему входам

реверсивного счетчика, выход первого элемента ИЛИ соединен с первым входом

вычитателя, выход которого подключен к первому входу третьего элемента И, выход которого соединен с

первым входом третьего элемента ИЛИ, выход KOTOjJoro подключен к информационному

входу первого счетчика, вход управления устройства соединен с установочным входом первого триггера

, инверсный выход которого подключен к входу управления коммутатора, выход младшего разряда которого

соединен с потенциальным входом 1-го элемента И второй группы, импульсный

вход которого лодключен к выходу младшего разряда первого счетчика, первый вход устройства соединен с

установочным входом второго счетчика , выход переполнения которого подключен

к входу установки второго триггера, прямой выход которого соединен со вторым входом третьего

элемента И и с первым входом четвертого элемента И, выход которого

подключен ко второму входу третьего элемента ИЛИ, инверсный выход первого триггера соединен со вторым

входом второго элемента И, третьим входом третьего элемента И и первым

входом пятого элемента И, выход которого подключен к первому входу

четвертого элемента ИЛИ, выход которого соединен с инфс рмационным входом fffoporo счетчика, выход Первого элемента ИЛИ подключен к первому вхо ду шестого элемента И, выход которого

соединен со вторым входом четвертого элемента ИЛИ, прямой выход первого триггера соединен со вторым

входами первого, четвертого и шестого элементов И и через формировател импульса с управлягацими входами

первого и второго счетчиков, информационный вход устройства подключен ко вторым входам вычитателя и пятог

элемента И, выход реверсивного счетчика соединен со входом сброса второго триггера, выход генератора

опорной частоты подключен к третьему входу четвертого элемента И, второй и третий входы устройства

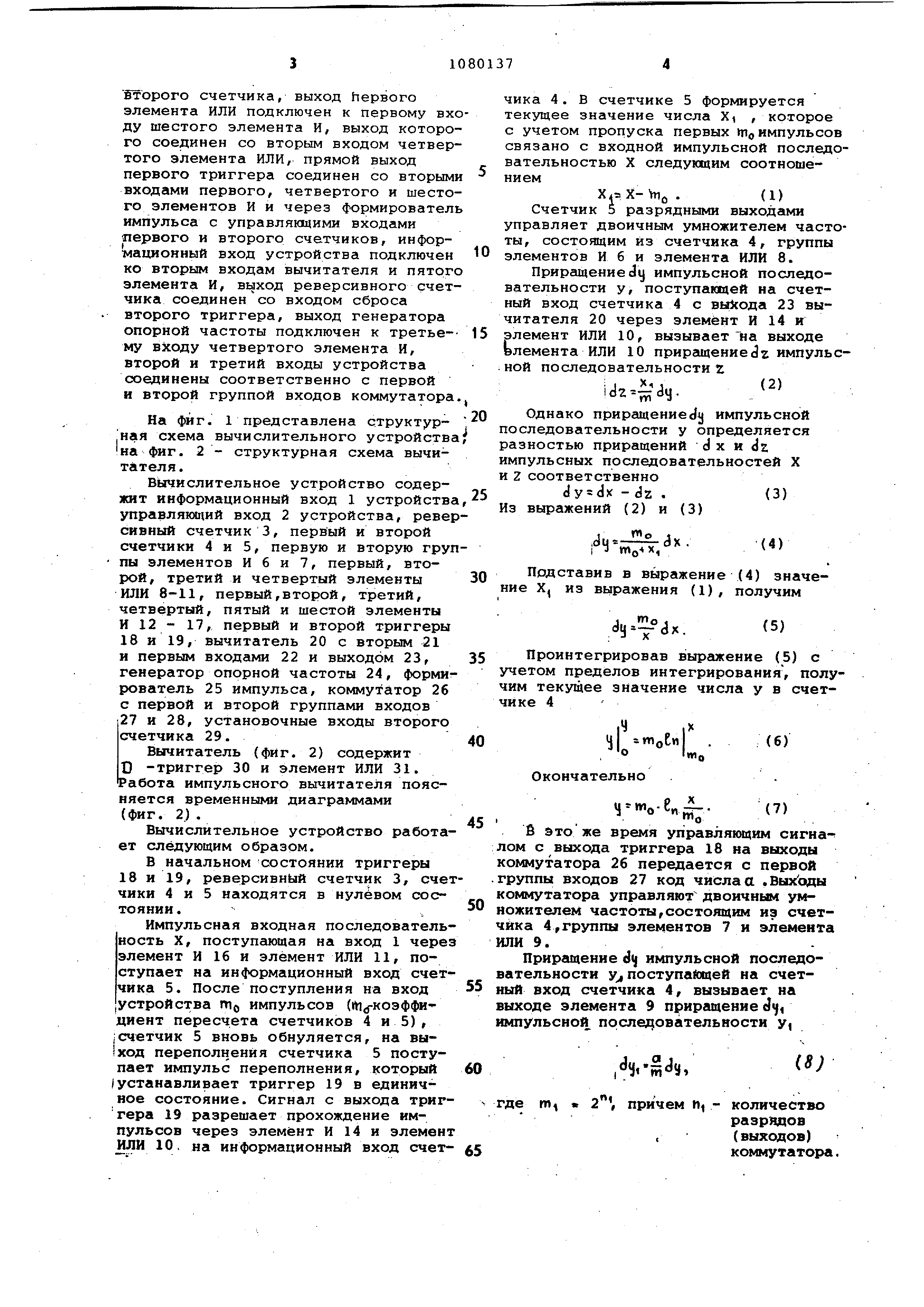

соединены соответственно с первой и второй группой входов коммутатора На фиг, 1 представлена структурная

схема вычислительного устройства на фиг. 2 - структурная схема вычитателя .

вычислительное устройство содержит информационный вход 1 устройства управляющий вход 2 устройства, ревер

сивный счетчик 3, первый и второй счетчики 4 и 5, первую и вторую груп

пы элементов И 6 и 7, первый, второй , третий и четвертый элементы ИЛИ 8-11, первый,в торой, третий,

четвертый, пятый и шестой элементы И 12 - 17, первый и второй триггеры

18 и 19, вычитатель 20 с вторым 21 и первым входами 22 и выходом 23,

генератор опорной частоты 24, формирователь 25 импульса, коммутатор 26 с первой и второй группами входов

27 и 28, установочные входы второго счетчика 29. Вычитатель (фИг. 2) содержит

О -триггер 30 и элемент ИЛИ 31. Работа импульсного вычитателя поясняется временными диаграммами

(фиг. 2). Вычислительное устройство работает следующим образом.

В начальном состоянии триггеры 18 и 19, реве:рсивнЬ1й счетчик 3, счет

чики 4 и 5 находятся в нулевом состоянии . Импульсная входная последовательность

X, поступающая на вход 1 через элемент И 16 и элемент ИЛИ 11, поступает на информационный вход счетчика

5. После поступления на вход устройства гпо импульсов (щ коэффи«иент пересчета счетчиков 4 и 5),

iсчетчик 5 вновь обнуляется, на переполнения счетчика 5 поступает импульс переполнения, который

Iустанавливает триггер 19 в единичное состояние. Сигнал с выхода триггера

19 разрешает прохождение импульсов через элемент И 14 и элемент ИЛИ 10, на информационный вход счетчика

4. В счетчике 5 формируется текущее значение числа X, , которое

с учетом пропуска первых т, импульсов связано с входной импульсной последовательностью

X следующим соотношением X. X-Vtio . (1)

Счетчик 5 разрядными выходами управляет двоичным умножителем частоты , состоящим из счетчика 4, группы

элементов И 6 и элемента ИЛИ 8. ПриращениесЗу импульсной последовательности у, поступающей на счетный

вход счетчика 4 с вы1сода 23 вычитателя 20 через элемент И 14 и элемент ИЛИ 10, вызывает на выходе

элемента ИЛИ 10 приращениеdz импульсной последовательности 2 . Однако

приргицение }у импульсной последовательности у определяется разностью приращений d х и dz

импульсных последовательностей X и Z соответственно dysdx -dz . (3)

Из выражений (2) и (3) Подставив в выражение (4) значение X, из выражения (1), получим

dy4° i Проинтегрировав выргикение (5) с учетом пределов интегрирования, получим

текущее значение числа у в счетчике 4 Ч с 1 -moln

Окончательно г« о-е„: 6 это же время управляющим сигналом

с выхода триггера 18 на выходы коммутатора 26 передается с первой

группы входов 27 код числа а .Выходы коммутатора управляют двоичным умножителем

частоты,состоящим из счетчика 4,группы элементов 7 и элемента ИЛИ 9.

Приращение A импульсной последовательности у поступайяцей на счетиый вход счетчика 4, вызывает на

выходе элемента 9 приращение Jifi импульсной последовательности У| , где т 2 , причем п - количество разридов . (выходов)

коммутатора. Импульсная последовательность

и, через элемент И 13 Поступает на суммирующий вход реверсивного счетчи ка 3.

Проинтегрировав выражение (8) и подставив значение У из выражения (7),можно записать значение числа

у, в реверсивном счетчике 3 .fj-. По окончании импульсной последовательности

X науправляющий вход 2 устройства поступает управляющий импульс , который устанавливает триггер

18 в единичное состояние. При переходе триггера 18 из нулевого в единичное состояние на выходе формирова

теля 25 импульса появляется короткий импульс, который обнуляет счетчик 4

и записывает в счетчик 5 с установоч ного входа 29 код числа Пд. После установки триггера 18 в

единичное состояние управляющий сигнал на входе коммутатора 26 меняется

и на выходах коммутатора 26 устанавливается код числа Ь, записанный на второй группе входов 28.

Далее работа устройства происходи следующим образом. От генератора 24 импульсная после

довательность Уг элемент И 15 и элемент ИЛИ 10 поступает на вход счетчика 4.

Приращение dg импульсной последовательности 2 вызывает на выходе .элемента ИЛИ 8 приращение du имлульс

Ьой последовательности и , поступающей через элемент И 17 и элемент

ИЛИ 11 на информационный в.ход счетчика 5.. На разрядных выходах счетчика 5

устанавливается управлякхций код двоичного умножителя, состоящего из счетчика 4, группы элементов И 6

и элемента ИЛИ 8. Приращение и равно

U

«-STo y

(10)

Проинтегрировав выражение (10) с

|Учетом пределов интегрирования получим текущее значение числа и

в счетчике 5

41.

.(J Спи

(11)

По Пpиpгш(eниedq, последовательности ij{ одновременно выэ1Ь1вает

приращейие ч импульсной последовательности V на выходе элемента ИЛИ 9 Jv.a..

Импульсная последовательность V -. поступает через элемент И 12 на вычи-.

.тающий вхо4 реверсивного счетчика 3. 6

,(хГъ

(19)

Ж№

Поскольку числа ot а и Ь константы/

то выражение (19) .можно записать в следующем виде:

а/Ь

(20)

U«K.X При поступлении на вход реверсивного

счетчика 3 количества импульсов, равного числу ij, , зафиксированному

ранее согласно выражению (9) в реверсивном счетчике 3, реверсивный счетчик

3 обнуляется и сигналом с выхода обнуления этого счетчика.триггер 19

устанавливается в нулевое состояние, которое запрещает дальнейшее поступление

импульсной последовательности генератора 24 через элемент И 15 и элемент ИЛИ 10 на вход счетчика

4. В этот момент процесс вычисления закончен. Окончательно проинтегрировав выражеЬйе

(12) с учетом пределов интегрирования , получим. Ь I

т,4г). 1,ЧаНайдем tjj из выражения (14) т,

2V4t Подставив выражение (15) и (11) получим

р„ U т. Ч С и - i - - По Ъ то

Подставив выражение (17) значение |J4 из выражения. (9) , получим знаение

числа U , зафиксированное в счетчике 5 по окончании вычисления f-««4

где КгПо/пв. В счетчике 4 после окончания вычислений

фиксируется число 1(,. С учетом вьфаженнй (15) и (9) можно записать .

.. о . (21) Таким образом, введение в состав

устройства указанных узлов и изменение связей позволяет вычислять функции

вида U К- и у.,Нп1оСм

. .. и снижает аппаратурные затраты.

Технико-экономические преимущества предлагаемого вычислительного

устройства по сравнению с базовым объектом, в качестве которого принят

прототип, следующие. Во-первых, предлагаемое вычислительное устройствр реализует степенную функцию с любым

показателем степени, в то время

как базовый объект способен возводить

только в целую степень. Во-вторых , помимо воспроизведения степенной функции, предлагаемое устройство

дополнительно воспроизводит логарифмическую зависимость, В-третьих, уменьшаются аппаратурные затраты.

Согласно расчету предлагаемое изобретение позволяет уменьшить относительно

базового объекта себестоимость на 12,8% за счет комплектующих ;изделий.

Комментарии