Устройство для инициирования электрических нагрузок, способ инициирования электрических нагрузок по истечении предварительно установленных временных задержек и дистанционное электрическое устройство задержки для инициирования электрической нагрузки - RU2077699C1

Код документа: RU2077699C1

Чертежи

Описание

Изобретение относится к устройству и способу для инициирования электрических нагрузок по истечении предварительно установленных временных задержек и дистанционному электрическому устройству задержки при взрывных работах.

Известны устройства и способ для инициирования некоторого множества электрических нагрузок после заданных временных задержек и задерживающее устройство. Устройство для инициирования содержит центральный управляющий блок для генерирования временных сигналов (timing signal), дистанционные электрические задерживающие устройства, каждое из которых соединено с соответствующей электрической нагрузкой и последовательно для последовательного программирования временным сигналом, исходящим от центрального управляющего блока, причем длительность задержки задается временным сигналом.

Управляющий блок содержит средство генерирования временных, пусковых и сплошных сигналов, управляющее безопасностью средство в виде управляемого переключателя. При этом задерживающее устройство содержит управляющее запоминанием синхронизирующих сигналов средство и накапливающее заряд средство. Устройство реализует способ передачи временных сигналов последовательно от центрального управляющего блока на каждое дистанционное электрическое задерживающее устройство для его программирования, контроль за программированием задерживающих устройств, генерирование пусковых сигналов на все задерживающие устройства одновременно вслед за программированием запускающих устройств, передачу силовых сигналов для питания каждого задерживающего устройства, осуществление заряжения средств накопления энергии в задерживающих устройствах.

Обвалы породы и взрывы в некоторых других частях шахты могут повредить как дистанционные задерживающие устройства, так и электрическую соединительную линию, связывающую эти устройства с управляющим устройством. Если это произойдет перед или во время программирования, то становится необходимостью отменить взрывную операцию, поскольку некоторые из задерживающих устройств окажутся не обеспеченными опорными синхронизирующими сигналами и их нельзя будет заставить сработать.

Электрические неисправности или сбои в работе центрального управляющего устройства или дистанционных задерживающих устройств также могут повлечь несчастные случаи.

Поскольку на время взрывных работ персонал эвакуируют, то простой, возникающий в результате возникновения таких сбоев, может обходиться очень дорого.

Изобретение направлено на устранение вышеизложенных недостатков, присущих известным устройствам.

Цель изобретения достигается тем, что в известном устройстве для инициирования электрических нагрузок, содержащем центральный блок

управления, включающий средства выработки пусковых и синхросигналов силовых и дистанционные электрические устройства задержки, каждое из которых связано с соответствующей электрической нагрузкой и

соединено проводным соединением последовательно для последующего программирования с помощью синхросигнала, поступающего от центрального блока управления, проводное соединение дистанционных

электрических устройств задержки выполнено в виде двунаправленной линии, противоположные концы которой соединены с выводами входа-выхода, центрального блока управления, в который введен микрокомпьютер,

а дистанционные электрические устройства задержки выполнены одинаковыми, причем каждое из них снабжено средствами управления синхросигналом, поступающим на дистанционное электрическое устройство

задержки в одном из двух заданных направлений, и запоминающим устройством для приема синхросигнала, поступающего от центрального блока управления, при этом в устройство для инициирования электрических

нагрузок введены средства детектирования, включенные между центральным блоком управления и запоминающим устройством в каждом дистанционном электрическом устройстве задержки для определения

неисправности в каждой линии синхросигнала;

введены средства коммутации, подключенные последовательно с двунаправленной линией синхросигнала между выводами входа-выхода центрального блока

управления для отмены команд, поступивших на дистанционные электрические устройства задержки, и отмены взрыва в том случае, когда заранее определенное число дистанционных электрических устройств

задержки запрограммировано неправильно или незапрограммировано; средства коммутации включают блок коммутации, имеющий переключатели, которые служит для изоляции двунаправленной линии синхросигнала и

закорочены друг с другом.

В центральном блоке управления средства выработки пускового сигнала включены между микрокомпьютером и линией пускового сигнала. В центральном блоке управления средство выработки силового сигнала выполнено в виде источника питания логики, включенного между микрокомпьютером и линией силового сигнала через средства коммутации, предназначенные для выработки силовых сигналов и для подачи питания к каждому дистанционному электрическому устройству задержки.

Средства детектирования включают буферы, управляемые микрокомпьютером, включенные между двунаправленной линией синхросигнала и выходными выводами микрокомпьютера при подключении другого конца двунаправленной линии синхросигнала непосредственно к входным выводам микрокомпьютера. Кроме того, устройство для инициирования электрических нагрузок дополнительно включает средства безопасного управления, включенные между микрокомпьютером и средствами коммутации с закорачиванием последних на землю для предохранения дистанционного электрического устройства задержки от программирования или запуска от ложных сигналов; средства безопасного управления включают сердечник для перемещения средств коммутации от позиции покоя, в которой сигнальные линии изолированы от центрального блока управления, к позиции разрешения, в которой сигнальные линии подключаются к выводам входа-выхода центрального блока управления, и средства привода в виде двигателя для перемещения сердечника.

Центральный блок управления дополнительно включает средства управления микрокомпьютером в виде одновибратора с перезапуском, включенного между выходными выводами центрального блока управления и соответствующим источником питания логики, и блок питания для контроля микрокомпьютера. Средство выработки синхроимпульсов выполнено в виде прецизионного генератора синхроимпульсов, а каждое дистанционное электрическое устройство задержки включает непрецизионный генератор синхроимпульсов, при этом каждое дистанционное электрическое устройство задержки включено как на прием сигнала через линию синхронизации от центрального блока управления, так и на передачу по крайней мере одного непрецизионного синхроимпульса на центральный блок управления для измерения его длительности относительно прецизионного генератора синхроимпульсов.

Прецизионный генератор синхроимпульсов включает прецизионный задающий генератор, подключенный к микрокомпьютеру, а непрецизионный генератор синхроимпульсов включает локальный задающий генератор, расположенный в каждом дистанционном электрическом устройстве задержки, причем синхросигнал представлен в цифровом виде.

В способе инициирования электрических нагрузок по истечении предварительно установленных временных задержек, предусматривающем передачу силовых сигналов для задействования каждого дистанционного электрического устройства задержки, передачу синхроимпульсов последовательно от центрального блока управления к каждому дистанционному электрическому устройству задержки, последовательный прием их устройствами задержки и передачу сигнала управления, передают синхросигналы, определяющие длительность задержки, по двунаправленной линии, при наличии или отсутствии неисправности формируют двунаправленный синхросигнал, а направление передачи синхросигнала в двунаправленной линии выбирают в соответствии с месторасположением неисправности.

Осуществляют контроль числа дистанционных электрических устройств задержки, которые программируют с помощью синхросигналов, и отключение центрального блока управления и дистанционных электрических устройств задержки, а также отменяют взрыв в случае, если, по меньшей мере, одно из дистанционных электрических устройств задержки неправильно запрограммировано или незапрограммировано.

После обнаружения неисправности определяют местоположение неисправности и подсчитывают число дистанционных электрических устройств задержки на противоположных сторонах от мест возникновения неисправности для последующего программирования каждого дистанционного электрического устройства задержки с помощью правильного синхросигнала.

Затем осуществляют генерирование управляющего сигнала после программирования дистанционных электрических устройств задержки одновременно на все дистанционные электрические устройства задержки для инициирования электрических нагрузок по истечении предварительно установленных временных задержек в каждом дистанционном электрическом устройстве задержки; осуществляют передачу синхронизирующих, силовых и управляющих сигналов по отдельным двунаправленным линиям.

Перед программированием дистанционных электрических устройств задержки двунаправленные линии изолируют и шунтируют на заземляющую линию, выбирают синхронизирующий образец для выполнения взрыва, соединяют двунаправленные линии для управления по истечении времени выдержки, причем длительность синхросигналов определяют образцом синхронизации. Перед изолированием и шунтированием двунаправленной линии на заземляющую линию осуществляют накопление энергии в дистанционных электрических устройствах задержки с помощью заряда и запуск дистанционных электрических устройств задержки, контролируют функционирование центрального блока управления перед подачей сигналов на дистанционные электрические устройства задержки; осуществляют передачу по крайней мере одного непрецизионного синхроимпульса от дистанционного электрического устройства задержки на центральный блок управления, который формирует по крайней мере один прецизионный синхроимпульс, измеряют длительность непрецизионного синхроимпульса, вычисляют коэффициент коррекции на основе отношения между длительностями прецизионного и непрецизионного синхроимпульсов и подачу его в качестве синхросигнала, который принимают дистанционным электрическим устройством задержки.

В дистанционное электрическое устройство задержки для инициирования электрической нагрузки, содержащее средство для запоминания синхросигнала, поступающего по двунаправленной линии, введены два средства управления синхронизирующими сигналами, соединенные с двунаправленной линией для управления синхросигналами, поступающими на устройство в двух встречных направлениях по двунаправленной линии, включающие средства обхода для возможности синхросигналом обходить устройство, при этом выходы средств управления синхронизирующими сигналами соединены со средствами для запоминания синхросигнала, при этом средства обхода сигналов выполнены с возможностью установки в режим блокировки сигналов для предотвращения прохождения синхросигналов через устройство или поступление на него. Кроме того, в дистанционное электрическое устройство задержки введены логическая схема, соединенная со средствами управления синхросигналами и средством запоминания синхросигнала для селективного задействования средств управления синхросигналами и для селективного разрешения или предотвращения запоминания синхросигналов, введены средства определения неисправности, включенные между линией синхросигнала и средствами запоминания синхросигнала для определения неисправности в двунаправленной линии синхросигнала, два управляемых ключа, выполненных в виде пары однонаправленных буферов, соединенных последовательно для приема сигналов, проходящих в одном или в другом направлении, причем средства управления первым и вторым сигналом выполнены в виде двунаправленного буфера, состоящего по крайней мере из двух непараллельных, противоположно направленных буферов, связанных вместе.

Кроме того, дистанционное электрическое устройство задержки снабжено первым управляемым ключом, включенным между первым источником напряжения и линией синхросигнала для поддержания первого уровня напряжения на одном из выводов дистанционного электрического устройства задержки и для обеспечения приема синхросигнала на этот вывод, и вторым управляемым ключом, включенным между линией синхросигнала и землей для обеспечения второго уровня напряжения для передачи синхросигнала от одного вывода на другой, причем выход второго управляемого ключа включен с обеспечением управления частично первым уровнем напряжения.

Первый управляемый ключ выполнен в виде транзистора с последовательно подключенным нагрузочным резистором для подъема уровня напряжения одного из выводов, а второй управляемый ключ выполнен в виде транзистора, соединяющего второй вывод с землей.

В дистанционное электрическое устройство задержки введены средства хранения заряда для подзарядки устройства при приеме запускающего сигнала и для инициирования электрической нагрузки и в течение определенного времени задержки после приема запускающего сигнала, причем средства хранения заряда подключены между сигнальной линией питания и ключами, подсоединенными к электрической нагрузке.

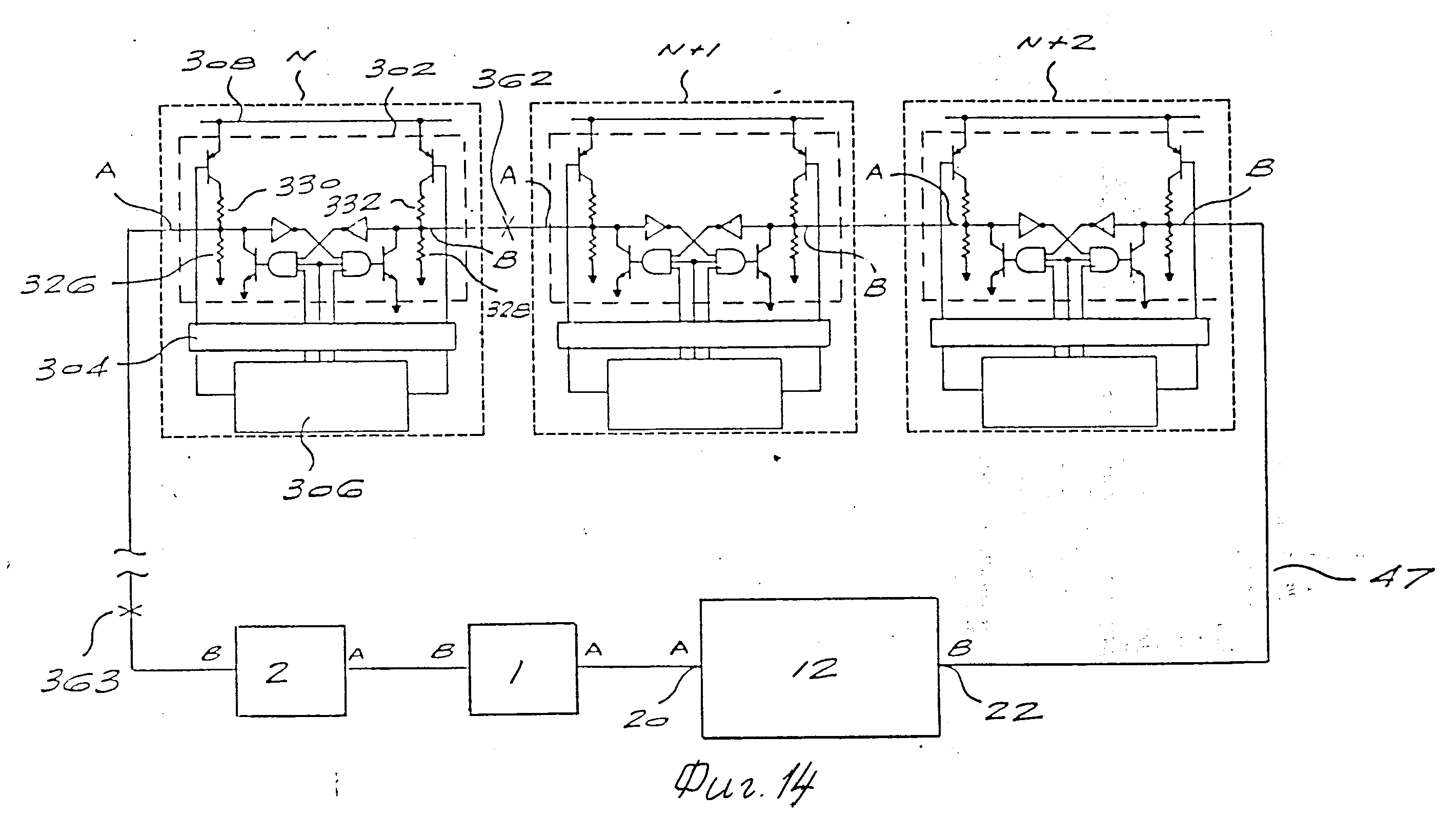

На фиг.1 изображено предлагаемое устройство; на фиг.2 структурная схема центрального управляющего устройства или контроллера, первого варианта осуществления настоящего изобретения; на фиг.3 алгоритмическая последовательность шагов, посредством которой осуществляется активизация контроллера и программирование задерживающих устройств первого варианта осуществления изобретения; на фиг. 4 временная диаграмма, эквивалентная последовательности шагов, представленной на фиг.3; на фиг.5 диаграмма безопасных уровней, иллюстрирующая разнообразные безопасные уровни синхронизирующего устройства, представленного на фиг.2; на фиг.6 - функциональная блок-схема первого варианта осуществления задерживающего устройства в соответствии с изобретением; на фиг.7 временная диаграмма выхода контроллера при программировании в направлении, совпадающим с направлением движения часовой стрелки; на фиг.8 временная диаграмма выхода контроллера при программировании в направлении, противоположном движению часовой стрелки; на фиг.9 временная диаграмма, иллюстрирующая способ программирования опорного синхронизирующего сигнала в задерживающем устройстве, представленном на фиг.6; на фиг.10 функциональная блок-схема второго варианта осуществления задерживающего устройства в соответствии с изобретением; на фиг.11 временная диаграмма способа программирования опорного синхронизирующего сигнала в задерживающем устройстве, представленном на фиг.7; на фиг.12 схематическая блок-схема двунаправленного буфера, образующего часть задерживающих устройств, представленных на фиг.4 и 10; на фиг. 12 временная диаграмма, иллюстрирующая работу двунаправленного буфера, представленного на фиг. 12; на фиг.14 третий вариант осуществления синхронизирующего устройства, соответствующего изобретению, иллюстрирующий последовательность задерживающих устройств по изобретению, содержащих двунаправленные буфера; на фиг.15 принципиальная схема двунаправленного буфера и логическая схема буферной части задерживающих устройств, представленных на фиг. 14; на фиг.16 и 17 временные диаграммы, иллюстрирующие способ задания программируемого направления относительно синхронизирующего устройства, представленного на фиг.14, соответственно для испорченной и неиспорченной проводки; на фиг.18 временная диаграмма, иллюстрирующая способ программирования задеpживающих устройств, представленных на фиг.14 в отсутствие разрыва в проводке; на фиг. 19 временная диаграмма, иллюстрирующая способ программирования задерживающих устройств, представленных на фиг. 14, когда в проводке есть разрыв; на фиг.20 алгоритмическая последовательность, указывающая шаги, исполняемые при программировании и пуске синхронизирующего устройства, представленного на фиг.14, соответственно при исправной и неисправной проводке.

На фиг.1-20, изображено устройство для инициирования электрических нагрузок, содержащее центральный блок управления, включающий средства выработки пусковых, силовых и синхросигналов дистанционные электрические устройства задержки, каждое из которых связано с соответствующей электрической нагрузкой и соединено проводным соединением последовательно для последующего программирования с помощью синхросигнала, поступающего от центрального блока управления, при этом проводное соединение дистанционных электрических устройств задержки выполнено в виде двунаправленной линии, противоположные концы которой связаны с выводами входа-выхода центрального блока управления, в который введен микрокомпьютер, а дистанционные электрические устройства задержки выполнены одинаковыми, причем каждое из них снабжено средствами управления синхросигналом, поступающим на дистанционное электрическое устройство задержки в одном из двух заданных направлений, и запоминающим устройством для приема синхросигнала, поступающего от центрального блока управления, кроме того, введены средства детектирования, включенные между центральным блоком управления и запоминающим устройством в каждом дистанционном электрическом устройстве задержки для определения неисправности в каждой линии синхросигнала; средства коммутации, подключенные последовательно с двунаправленной линией синхросигнала между выводами входа-выхода центрального блока управления для отмены команд, поступивших на дистанционные электрические устройства задержки, и отмены взрыва в том случае, когда заранее определенное число дистанционных электрических устройств задержки запрограммировано неправильно или незапрограммировано.

Причем средства коммутации включают блок коммутации, имеющий переключатели, которые служат для изоляции двунаправленной линии синхросигнала и закорочены друг с другом, кроме того, в центральном блоке управления средства выработки пускового сигнала включены между микрокомпьютером и линией пускового сигнала; в центральном блоке управления средство выработки силового сигнала выполнено в виде источника питания логики, включенного между микрокомпьютером и линией силового сигнала через средства коммутации, предназначенные для выработки силовых сигналов и для подачи питания к каждому дистанционному электрическому устройству задержки, средства детектирования включают буферы, управляемые микрокомпьютером, включенные между двунаправленной линией синхросигнала и выходными выводами микрокомпьютера при подключении другого конца двунаправленной линии синхросигнала непосредственно к входным выводам микрокомпьютера.

Кроме того имеются средства безопасного управления, включенные между микрокомпьютером и средствами коммутации с закорачиванием последних на землю для предохранения дистанционного электрического устройства задержки от программирования или запуска от ложных сигналов, причем средства безопасности управления включают сердечник для перемещения средств коммутации от позиции покоя, в которой сигнальные линии изолированы от центрального блока управления, к позиции разрешения, в которой сигнальные линии подключаются к выводам входа-выхода центрального блока управления, и средства привода в виде двигателя для перемещения сердечника, центральный блок управления дополнительно включает средства управления микрокомпьютером в виде одновибратора с перезапуском, включенного между выходными выводами центрального блока управления и соответствующим источником питания логики, и блок питания для контроля микрокомпьютера.

Средство выработки синхроимпульсов выполнено в виде прецизионного генератора синхроимпульсов, а каждое дистанционное электрическое устройство задержки включает непрецизионный генератор синхроимпульсов, при этом каждое дистанционное электрическое устройство задержки включено как на прием сигнала через линию синхронизации от центрального блока управления, так и на передачу, по крайней мере, одного непрецизионного синхроимпульса на центральный блок управления для измерения его длительности относительно прецизионного генератора синхроимпульсов; прецизионный генератор синхроимпульсов включает прецизионный задающий генератор, подключенный к микрокомпьютеру, а непрецизионный генератор синхроимпульсов включает локальный задающий генератор, расположенный в каждом дистанционном электрическом устройстве задержки, причем синхросигнал представлен в цифровом виде.

Согласно указанным чертежам способ инициирования электрических нагрузок по истечении предварительно установленных временных задержек предусматривает передачу силовых сигналов для задействования каждого дистанционного электрического устройства задержки, передачу синхроимпульсов последовательно от центрального блока управления к каждому дистанционному электрическому устройству задержки, последовательный прием их устройствами задержки и передачу сигнала управления, при этом синхросигналы, определяющие длительность задержки, передают по двунаправленной линии, при наличии или отсутствии неисправности формируют двунаправленный синхросигнал, а направление передачи синхросигнала в двунаправленной линии выбирают в соответствии с месторасположением неисправности.

Кроме того, в указанном способе осуществляют контроль числа дистанционных электрических устройств задержки, которые программируют с помощью синхросигналов, и отключение центрального блока управления и дистанционных электрических устройств задержки, а также отменяют взрыв в случае, если, по меньшей мере, одно из дистанционных электрических устройств задержки неправильно запрограммировано или незапрограммировано; после обнаружения неисправности определяют местоположение неисправности и подсчитывают число дистанционных электрических устройств задержки на противоположных сторонах от мест возникновения неисправности для последующего программирования каждого дистанционного электрического устройства задержки с помощью правильного синхросигнала, генерирование управляющего сигнала осуществляют после программирования дистанционных электрических устройств задержки одновременно на все дистанционные электрические устройства задержки для инициирования электрических нагрузок по истечении предварительно установленных временных задержек в каждом дистанционном электрическом устройстве задержки; передачу синхронизирующих, силовых и управляющих сигналов осуществляют по отдельным двунаправленным линиям.

Перед программированием дистанционных электрических устройств задержки двунаправленные линии изолируют и шунтируют и на заземляющую линию, выбирают синхронизирующий образец для выполнения взрыва, соединяют двунаправленные линии для управления по истечении времени выдержки, причем длительность синхросигналов определяют образцом синхронизации; перед изолированиеми шунтированием двунаправленной линии на заземляющую линию осуществляют накопление энергии в дистанционных электрических устройствах задержки с помощью сигнала заряда и запуск дистанционных электрических устройств задержки, функционирование центрального блока управления контролируют перед подачей сигналов на дистанционные электрические устройства задержки, осуществляют передачу, по крайней мере, однако непрецизионного синхроимпульса от дистанционного электрического устройства задержки на центральный блок управления, который формирует, по крайней мере, один прецизионный синхроимпульс, измеряют длительность непрецизионного синхроимпульса, вычисляют коэффициент коррекции на основе отношения между длительностями прецизионного и непрецизионного синхроимпульсов и подачу его в качестве синхросигнала, который принимают дистанционным электрическим устройством задержки.

Дистанционное электрическое устройство задержки для инициирования электрической нагрузки, содержит два средства для запоминания синхросигнала, поступающего по двунаправленной линии, два средства управления синхронизирующими сигналами, соединенных с двунаправленной линией для управления синхросигналами, поступающими на устройство в двух встречных направлениях по двунаправленной линии, включающие средства обхода для возможности синхросигналом обходить устройство. При этом выходы средств управления синхронизирующими сигналами соединены с средствами для запоминания синхросигнала. Средства обхода сигналов выполнены с возможностью установки в режим блокировки сигналов для предотвращения прохождения синхросигналов через устройство или поступление на него. Кроме того, введена логическая схема, соединенная с средствами управления синхросигналами и средством запоминания синхросигнала для селективного задействования средств управления синхросигналами и для селективного разрешения или предотвращения запоминания синхросигналов, имеются средства определения неисправности, включенные между линией синхросигнала и средствами запоминания синхросигнала для определения неисправности в двунаправленной линии синхросигнала, два управляемых ключа, выполненных в виде пары однонаправленных буферов, соединенных последовательно для приема сигналов, проходящих в одном или в другом направлении, причем средства управления первым и вторым сигналом выполнены в виде двунаправленного буфера, состоящего по крайней мере из двух непараллельных, противоположно направленных буферов, связанных вместе.

Кроме того, имеется первый управляемый ключ, включенный между первым источником напряжения и линией синхросигнала для поддержания первого уровня напряжения на одном из выводов дистанционного электрического устройства задержки и для обеспечения приема синхросигнала на этот вывод, и второй управляемый ключ, включенный между линией синхросигнала и землей для обеспечения второго уровня напряжения для передачи синхросигнала от одного вывода на другой.

Выход второго управляемого ключа включен с обеспечением управления частично первым уровнем напряжения. Первый управляемый ключ выполнен в виде транзистора с последовательно подключенным нагрузочным резистором для подъема уровня напряжения одного из выводов, а второй управляемый ключ в виде транзистора, соединяющего второй вывод с землей.

Кроме того, введены средства хранения заряда для подзарядки устройства при приема запускающего сигнала и для инициирования электрической нагрузки в течение определенного времени задержки после приема запускающего сигнала, причем средства хранения заряда подключены между сигнальной линией питания и ключами, подсоединенными к электрической нагрузке.

Синхронизирующее устройство 10 первого варианта осуществления изобретения (фиг.1) предназначено для использования в шахтах и карьерах для детонирования взрывчатых устройств спустя определенные задержки после поступления пускового сигнала. Синхронизирующее устройство 10 содержит управляющее устройство или контроллер 12, электрически соединенный в параллель посредством проводника 14 с дистанционными электронными задерживающими устройствами 16.1, 16.2, 16.3, 16.4, 16.5 и 16.6, каждое из которых в свою очередь соединено соответствующей электрической нагрузкой или детонатором 18 для подрыва заряда взрывчатки. Проводка имеет форму петли, концы которой соединены с первым А и вторым В портами 20 и 22 контроллера 12.

Проводка 14 содержит тракт синхронизирующих сигналов в виде программирующей линии, которая последовательно соединяет все задерживающие устройства для их последовательного программирования синхронизирующими сигналами от контроллера. Проводка также содержит силовые линии и заземленную линию, которые соединяют все задерживающие устройства в параллель, создавая возможность одновременного приведения в действие всех задерживающих устройств и обеспечения передачи пускового сигнала для активизации задерживающих устройств по истечении временных задержек, которые задаются посредством синхронизирующих сигналов, которые предварительно программируются в каждое из задерживающих устройств.

Эта схема позволяет последовательно программировать синхронизирующие сигналы, идущие от контроллера 12 в каждое из задерживающих устройств 16, при этом каждый синхронизирующий сигнал имеет специфическую длительность или временной интервал. Последующий взрывной сигнал одновременно запускает обратный отсчет временных интервалов, заполненных в каждом из задерживающих устройств, тем самым активизируя детонатор, ассоциированный с каждым задерживающим устройством после истечения синхронизирующего интервала. Поскольку проводка 14 имеет петлеобразную форму и благодаря конфигурации входа-выхода задерживающих устройств, синхронизирующие сигналы от контроллера 12 можно программировать в задерживающие устройства с 16.1 по 16.6 как в направлении хода часовой стрелки, так и против ее хода, причем эти направления обозначены соответственно стрелками 24 и 26.

Если возникнет разрыв в проводке 14 по причине обвала, например, необходимо пользоваться двунаправленным программированием, подавая синхронизирующие сигналы из обоих первого и второго портов 20 и 22 контроллера 12, чтобы запрограммировать все задерживающие устройства. Задерживающие устройства 16.1, 16.2 и 16.3 запрограммированы синхронизирующими сигналами, поданными через первый порт 20. Контроллер изменяет маршрут остальных синхронизирующих сигналов таким образом, что они исходят из второго порта 22, обеспечивая возможность программирования задерживающих устройств 16.4, 16.5 и 16.6 в направлении, противоположном ходу часовой стрелки.

Контроллер 12, представленный на фиг. 2, имеет центральный микрокомпьютер 28, который получает питание от батареи 30, включаемой выключателем 31. Микрокомпьютером 28 управляют вручную с помощью набора переключателей 32, смонтированных на пульте управления 34.

Микрокомпьютер 28 соединен через шинный интерфейс 35 с справочной таблицей 40 только считываемой памяти, в которой хранятся разнообразные опорные последовательности синхронизирующих сигналов, один из которых можно выбрать с помощью селекторных переключателей 42. Программирование по усмотрению пользователя можно осуществлять с помощью клавиатуры при более специфичных или необычных прикладных задачах, требующих подачу нестандартной взрывной последовательности. Часы 44 соединены с микрокомпьютером 28 и ведут счет времени, позволяя операторам покинуть зону перед началом взрыва.

Выходные линии идут от микрокомпьютера 28. Среди них есть РROG A (программирующая) линия 46 и PROG B линия 48, которые соединены с микрокомпьютером через первый и второй трехстабильные буфера 50 и 52 соответственно. Буфера активизируются посредством сигналов, поступающих от соответствующих первой 54 и второй 56 разрешающих линий. PROG A и PROG B линии подсоединены к отдельным соответствующим входным-выходным портам 58 и 60 микрокомпьютера 28.

Четыре отдельные линии идут от контроллера 12 на разъем проводки (кабеля) 36) в первом порту 20, а именно, DETONATOR (детонаторная) и LOGIC POWER (питающая логику) линии 62 и 64, PROG линии 46 и GROUND (заземляющая) линия 66. Аналогично, четыре отдельные линии идут на разъем проводки 38 во втором порту 22, причем две из них (DETONATOR линия 62.1 и LOGIC линия 64.1) являются ветвями тех линий, которые идут к разъему проводки 36, а другими двумя являются общая GROUND линия 66 и PROG В линии 48. Из этого следует, что проводка 14 имеет четыре соответствующих линии: DETONATOR линии 62.2, LOGIC линия 64.2, PROG линия 47 и GROUND линия 66.2.

Противоположные концы отдельных линий проводки заведены в штырьковые разъемы 36.1 и 38.1, которые вставляются в соответствующие разъемы проводки 36 и 38. Это приводит к тому, что LOGIC линия, образованная индивидуальными линиями 64, 64.1 и 64.2, а также DETONATOR линия, содержащая линии 62, 63.1 и 62.2, образуют замкнуты петли. PROG А линия 46 и PROG В линия 48 образуют открытую петлю с PROG линией 47. DETONATOR, LOGIC, PROG A и PROG B линии 62, 64, 46, 48 соединены с контроллером через закорачивающий переключательный блок 78, который содержит набор закорачивающих переключателей 79. DETONATOR линия 62 в свою очередь соединена с микрокомпьютером 28 через входной-выходной порт 79.1.

Двигатель 80, имеющий управляющий двигателем блок 82, управляемый микрокомпьютером 28, оснащен нарезным валом 84, который несет сердечник 86, механически соединенный с закорачивающими переключателями 79. Вращение вала 84 приводит к тому, что сердечник 86 перемещается от позиции "запрещено", которая обозначена пунктирным контуром 87, в которой линии проводки заземлены, в направлении стрелки 88 к позиции "разрешено", в которой сердечник 15, обозначенный контуром сплошной линии, и линии проводки соединены с контроллером 12. Вращение вала 84 в противоположном направлении принуждает сердечник 86 перемещаться к переключателям 79, т.е. обратно в позицию "запрещено".

Переключатель 89 приводится в действие сердечником 86, когда он находится в позиции "запрещено", передачей сигнала на микрокомпьютер 28, таким образом активизированный. Если микрокомпьютер 28 не принимает такой сигнал после предварительного включения питания, он активизирует двигатель 80 через управляющий двигателем блок 82 так, чтобы сердечник 86 переместился к позиции "запрещено", если сердечник уже не находился в этой позиции. Если по причине неисправности двигателя 80 или управляющего двигателем блока 82 сердечник 86 не переместится в позицию "запрещено", то контроллер 12 "отсчитывает в обратном направлении время" и предотвращает взрыв. Передается сигнал по сигнальной линии 89.1 от переключательного блока 78, указывающему микрокомпьютеру 28 момент, когда сердечник достигает позиции "разрешено".

После того, как оператор соединил проводку 14 с контроллером 12, он включает переключатель 31, чем переводит безопасный уровень с уровня 5 (наиболее безопасный уровень) на уровень 4 (фиг. 5). Контроллер 12 продолжает оставаться в бездействии до тех пор, когда оператор выберет подходящий рисунок синхронизации (другими словами, длительности задержек, подлежащих программированию) с помощью подходящих селекторного переключателя 42 и ARM переключателя 90, заставляющего часы 44 начать отсчет времени периода воздержания, который обычно приравнивают двум часам (обратитесь к блоку 92 алгоритмической последовательности и шагу 4). После истечения этого времени будет приведен в действие двигатель 80, чтобы переместить сердечник из позиции "запрещено" в направлении стрелки 87, тем самым соединяя линии проводки 14 с контроллером 12, как можно усмотреть при изучении блока 94 алгоритмической последовательности и шага 5 на фиг.5.

Затем активизируют LOGIC линию посылкой импульсного сигнала от микрокомпьютера на запускаемый моностабильный элемент 96, который в свою очередь активизирует источник питания логики 98, обеспечивающий питанием LOGIC линию 64 (смотрите блок 100 алгоритмической схемы, а также нарастающий фронт LOGIC импульса на фиг. 4). Запускаемый моностабильный элемент 96 должен получать регулярную импульсную последовательность от микрокомпьютера 28, чтобы источник питания логики 98 оставался включенным. Таким образом, если выйдет из строя микрокомпьютер 28, он перестанет посылать регулярную импульсную последовательность на моностабильный элемент 96, что повлечет отключение источника питания логики 98 и понижение потенциала LOGIC линии 64.

Затем сигнал от микрокомпьютера 28 по разрешающей линии 54 разрешает работу буфера 50, тем самым разрешает программирование задерживающих устройств 16.1 по 16,6 путем подъема потенциала в позиции 104 PROG A линии 46 (см. блок 106). Мониторинг программирования каждого из задерживающих устройств осуществляется наблюдением за обратными сигналами по DETONATOR линии 62, которая на этом этапе имеет высокий импеданс, обеспечивающий обратную связь. Обратный сигнал 108, появляющийся на линии DETONATOR 62, отмечает момент начала синхронизации задерживающего устройства 16.1 и PROG A линия переходит на низкий потенциал, отмечая конец периода синхронизации, на котором первый синхронизирующий сигнал 104.1 программируется в первое задерживающее устройство 16,1, заставляя DETONATOR линию перейти на высокий потенциальный уровень. Следующий синхронизирующий сигнал 104,2 поступает на следующее задерживающее устройство 16.2. Фактические длительности задержек, которые подлежат программированию, извлекаются из взрывной последовательности, хранящейся в справочных таблицах 40 только считываемой памяти, и процедура программирования воспроизводится до тех пор, когда окажутся запрограммированными все задерживающие устройства 16.1 по 16.6.

Когда будут запрограммированы все задерживающие устройства, по PROG A линии посылается дополнительный импульс 109. Поскольку уже все задерживающие устройства запрограммированы, этот дополнительный импульс проходит через все задерживающие устройства и принимается PROG B входным-выходным портом 60. После приема дополнительного импульса 109 контроллер делает заключение, что все задерживающие устройства правильно запрограммированы и поднимает потенциал DETONATOR линии 62 (в позиции 115), включая источник питания детонаторов 116. В результате этого происходит заряжение накопителей энергии или конденсаторов в задерживающих устройствах, что будет ниже описано подробнее. Затем питание детонаторов отключается, причем спадающий фронт 120работает как пусковой сигнал, по которому все задерживающие устройства начинают отсчет собственных длительностей задержек.

Если во время программирования по PROG A линии обнаруживается разрыв по отсутствию обратного сигнала по DETONATOR линии, контроллер продолжает посылать программирующие импульсы до тех пор, пока не будут запрограммированы все задерживающие устройства, еще соединенные с контроллером по PROG A линии. По-прежнему будет послан дополнительный импульс по PROG A линии и PROG B входной-выходной порт 60 будет ждать обратный импульс. Отсутствие обратного импульса подтверждает разрыв.

В ответ на это контроллер запрещает работать PROG A буферу 50 и разрешает работать PROG В буферу 52. Процедура программирования завершается по PROG B линии 48 против хода часовой стрелки контроллером, который считывает синхронизирующую последовательность из справочной таблицы в только считываемой памяти в обратном порядке. Эта процедура проиллюстрирована более подробно на фиг. 8, на котором PROG A линия имеет низкий потенциал и синхронизирующие сигналы 104.6, 104.5 и 104.4 поступают по PROG B линии в обратном порядке для программирования задерживающих устройств 16.6, 16.5 и 16.4.

Процесс программирования остающихся задерживающих устройств и в этом случае наблюдается по DETONATOR линии. Число задерживающих устройств, подлежащих программированию, предварительно заносится в справочные таблицы только считываемой памяти, и это число должно соответствовать числу задерживающих устройств, фактически соединенных с проводкой. Таким образом, оказывается возможным определить длину разрыва, с помощью линии DETONATOR подсчитывая число успешно запрограммированных задерживающих устройств. Учитывая число задерживающих устройств, которые были успешно запрограммированы (причем это число совпадает с числом сигналов по обратной связи по линии DETONATOR 62), микрокомпьютер 28 решает отменить полностью операцию или продолжать. Например, если только одно из задерживающих устройств оказалось незапрограммированным, то операцию можно продолжить. Если более одного задерживающего устройства оказались и незапрограммированными, то взрывная процедура может быть отменена путем отключения источника питания LOGIC (логики) и переключения двигателя 80 на перемещение сердечника 86 в позицию "запрещено", тем самым заземляя линии (см. блоки 112, 114 и 114.1).

Как описано выше, после успешного программирования всех задерживающих устройств DETONATOR линия 62 переводится на высокий потенциальный уровень (в позиции 115) путем включения источника питания детонаторов 116, который в свою очередь включается запускаемым моностабильным элементом 118, импульсы на который проходят от микрокомпьютера 28 (см. блок 119). Как и с источником питания логики 98, неисправность микрокомпьютера повлечет прекращение импульсной последовательности и отключение источника питания детонаторов 116. После окончания заряжения конденсаторов всех задерживающих устройств 16.1 по 16.1 источник питания детонаторов 116 отключится, снижая потенциальный уровень DETONATOR линии в позиции 120, при этом спадающий фронт 120 работает как пусковой сигнал для задерживающих устройств, задающий начало отсчета их соответствующих временных задержек. В это время подается питание на двигатель 80, чтобы он переместил сердечник 86 в позицию "запрещено" 88 (см. блок 114.1), что влечет заземление линий проводки и возврат системы в исходное состояние. Пищик 12.1 соединен с микрокомпьютером 28 и звучит при каждом подсоединении переключателей к проводке и заземлении линий проводки.

Работа системы будет ниже описана со ссылками на задерживающие устройства. Задерживающее устройство 16.1 на фиг. 4 включено в параллель через защитную схему 122 между GROUND линией 66.2 LOGIC или LOGIC POWER линией 64.2 и DETONATOR или DET POWER (питание детонаторов) линией 62.2 и соединено последовательно с PROG A и PROG B линиями. Последние две линии соединены друг с другом через двунаправленный буфер 124, который более подробно будет описан в спецификации.

Вообще говоря, задерживающее устройство 16 имеет логический блок 126, который принимает опорный синхронизирующий сигнал либо по PROG A, либо PROG B линии через двунаправленный буфер 124 и управляющую двунаправленным буфером схему 127. Локальное тактирование обеспечивается локальным осциллятором 128, которое используется для увеличения показания счетчика 130.

Как только LOGIC линия переходит на высокий потенциальный уровень в позиции 125, она подает питание на логический блок 126 и все другие активные компоненты задерживающего устройства 16.1 через стабилизатор напряжения 131, обозначенный пунктирными линиями 132 на фиг.6. После получения питания через стабилизатор напряжения 131 сбрасывающая схема 137 генерирует импульс сброса для возврата логического блока 126 в исходное состояние и включения двунаправленного буфера 124 и управляющей им схемы 127. Когда LOGIC линия 64.2 переходит на высокий уровень, DETONATOR линия 62.2 также переводится в позиции 130 на уровень LOGIC линии посредством повышающего резистора 133, расположенного в контроллере 12 на фиг.2. Уровень напряжения DETONATOR линии ограничивается уровнем, который не позволяет стать проводящим зенеровскому диоду 134, который соединен с накапливающим энергию устройством 136.

Логический блок 126 принимает синхронизирующий сигнал 138 от PROC A линии через двунаправленный буфер 124 и управляющую им схему 127. Поскольку PROG A линия переходит на высокий потенциальный уровень, логический блок 126 передает импульс сброса 142, очищающий настроечный счетчик 130 и текущий счетчик 146. В то же самое время прямого направления сигнала 148 переходит на высокий уровень, запрещая работать обратным буферам и разрешая единственно прохождение опорных синхронизирующих сигналов, идущих в прямом направлении по PROG A линии. Ниже, в спецификации работа двунаправленного буфера 124 и управляющей им схемы 127 будет описана более подробно.

По нарастающему фронту 150 первого импульса 151, с генерированного локальным осциллятором 128 после перехода PROG A линии на высокий уровень, логический блок 126 переходит DETONATOR линию в позиции 152 на низкий уровень через транзистор с разомкнутым коллектором 154, тем самым давая знать контроллеру 12, что он начал формировать временной период. Одновременно локальный осциллятор 128 начинает увеличивать содержимое установочного счетчика 130. Понижение уровня DETONATOR линии в позиции 152, которое отмечает стартовый период настроечного счетчика 130, опознается контроллером 12, который переводит на низкий уровень PROG A линию в позиции 154 в тот момент, когда локальный осциллятор 128 закончит настройку настроечного счетчика 130 на заданный период. DETONATOR линия переходит в позиции 156 на высокий уровень в ответ на переход на низкий уровень PROG A линии, заставляя настроечный счетчик 130 "заморозить" показание числа периодов, которые совершил локальный осциллятор за время счета.

В ответ на переход на высокий уровень DETONATOR линии в позиции 156, разрешающая линия двунаправленного буфера переходит на высокий уровень в позиции 158, в результате чего последующий опорный синхронизирующий сигнал, идущий по PROG A линии, обходит задерживающее устройство, о котором идет речь, и проходит к следующему задерживающему устройству в последовательности ждущих программирование и которому синхронизирующий сигнал предназначен. Эта процедура повторяется для каждого задерживающего устройства. Когда все задерживающие устройства 16.1 и 16.6 окажутся запрограммированы, напряжение DETONATOR линии поднимается до уровня, при котором происходит пробой зенеровского диода (см. позицию 115 на фиг. 3В), чтобы зарядились все конденсаторы 136, в результате чего они станут независимыми источниками питания своих соответствующих задерживающих устройств 16.1 по 16.6. После окончания полного заряжения всех конденсаторов задерживающих устройств DETONATOR линия и LOGIC линия (см. позицию 120 на фиг. 3В) одновременно переходит на низкий уровень, создавая пусковой сигнал. Затем конденсатор 136 берет на себя питание стабилизатора напряжения 131, когда LOGIC линия перестает обеспечивать мощностью локальный осциллятор 128, установочный счетчик 130, текущий счетчик 146 и другие активные компоненты схемы задерживающего устройства.

Пусковой сигнал логический блок 126 принимает через ограничитель напряжения 140, который ограничивает напряжение пускового сигнала до уровней, приемлемых логическим блоком 126.

После приема пускового сигнала задерживающие устройства начинают отсчитывать каждый конкретную задержку, которая была ранее внесена в каждый из их настроечных счетчиков 130, с помощью локального осциллятора 128, увеличивая показание текущего счетчика 146, через логический блок 126. Компаратор 160 воздействует на переключатель 162, когда хранящееся в установочном счетчике 130 число становится равным содержимому текущего счетчика 146. Срабатывание переключателя 160 влечет разряд оставшегося в конденсаторе 136 заряда на электрическую нагрузку или детонатор 18, что влечет детонирование взрывчатого заряда.

Если GROUND (земельная) линия 66,2, идущая к задерживающему устройству, окажется разорванной или отсоединенной, то существует вероятность, что схема будет флуктуировать и, возможно, колебаться. Это может влиять на PROG A и PROG B линии, которые в свою очередь способны вредно воздействовать на соседние задерживающие устройства, в частности, если задерживающее устройство осциллирует, поскольку это может повлечь программирование соседних сдерживающих устройств паразитными сигналами. Поэтому диод 164 включен между DETONATOR и GROUND линиями каждого задерживающего устройства для гарантии, что во время фазы программирования, если GROUND линия этого задерживающего устройства окажется отсоединенной, он останется на уровне, задаваемом DETONATOR линией.

Перейдем теперь к фиг.10, на которой представлен второй вариант осуществления задерживающего устройства 165, на котором компоненты, соответствующие компонентам на фиг.4, обозначены одинаковыми числовыми позициями. Компаратор 160, настроечный счетчик 130 и текущий счетчик 146, имеющиеся на фиг. 6, заменены на сдвиговый регистр 166 и предварительно устанавливаемый счетчик 168. Работа задерживающего устройства 166 ниже описана со ссылками на временную диаграмму на фиг.11.

Процедура программирования инициируется посылкой положительного адресного импульса 170 по PROG A линии. Задерживающее устройство 165 познает этот импульс и отвечает на него обратным сигналом 172 на контроллер по DET POWER линии, который пропорционален сигналу от его локального осциллятора 128. Затем период 174 этого сигнала точно измеряется на контроллере 12 с помощью управляемого кристаллом осциллятора, который работает в МГц диапазоне. После этого контроллер вычисляет точное значение, которое должно быть загружено в сдвиговый регистр 166 задерживающего устройства, чтобы получить правильную длительность задержки. Если, например, 12 мс задержка подлежит программированию в задерживающее устройство и период локального осциллятора после измерения управляемым кристаллом осциллятором оказывается равным 1,5 мс, то микропроцессор высчитает, что необходимо загрузить цифровое слово, соответствующее восьми периодам локального осциллятора (т.е. 1000). Цифровое слово 176, представляющее такую задержку, затем передается последовательно на задерживающее устройство по PROG A линии, используя сигнал 178 локального осциллятора в качестве тактового сигнала для последовательной передачи.

Когда цифровое слово 176 получено задерживающим устройством, оно загружается в сдвиговый регистр 116. Двунаправленный буфер 124 настраивается так, что вся информация, идущая по PROG A линии, обходит первое задерживающее устройство и передается на следующее из последовательно соединенных задерживающих устройств, обращение к которому осуществляется вторым импульсом 180 по линии PROG A и которому затем посылается второе цифровое слово 182. Этот процесс повторяется, пока не окажутся запрограммированными все задерживающие устройства. После понижения потенциального уровня линии в позиции 120 цифровые данные, хранящиеся в сдвиговом регистре 166 задерживающего устройства, пересылаются параллельно на предварительно устанавливаемый счетчик 168. Затем предварительно устанавливаемый счетчик 168 начинает уменьшать свое показание, и, как только его показание достигнет нуля, срабатывает переключатель 162 и запускается детонатор описанным выше образом.

Преимущество этого варианта осуществления состоит в том, что для программирования задерживающего устройства применяется фактическая частота локального RC осциллятора 128. Поскольку частота локального осциллятора зависит от температуры и допусков на компоненты, она варьируется от одного задерживающего устройства к другому. Цифровое слово, посылаемое контроллером на каждое из задерживающих устройств, компенсирует вариации, вызванные подобными различиями, и позволяет очень точно задавать длительность задержки, используя сравнительно недорогие RC осцилляторы, однако при условии стабильности такого осциллятора. Далее использование цифрового слова вместо сигнала реального времени делает длительность программирования всех задерживающих устройств совершенно независимой от фактических длительностей задержки, программируемых в задерживающие устройства. Фактически длительность программирования сокращается, в результате чего уменьшается период, на котором линии проводки не заземлены и потенциально небезопасны.

Ниже дано подробное описание работы двунаправленного буфера 124 и управляющей им схемы 127 со ссылками на фиг. 12 и 13. При нормальных условиях работы терминалы 46.1 и 48.1, к которым присоединены PROG A и PROG B линии 46 и 48, заземлены понижающими резисторами 184 и 186 соответственно. PROG A терминал 46.1 соединен с INTERNAL 1 шиной 188 через прямого направления входной буфер 190, который управляется сигналом INI*, приходящим с Q выхода триггера 191. INTERNAL I шина 183 в свою очередь соединена с PROG B терминалом 48.1 через прямого направления выходной буфер 192, управляемый сигналом OUTI*, приходящим с Q выхода триггера 193. PROG В терминал 48.1 соединен с INTERNAL 2 шиной 193 для приема синхронизирующих сигналов в обратном направлении через обратного направления входной буфер 196, управляемый управляющим сигналом IN2*, приходящим от Q выхода триггера 197. INTERNAL 2 шина соединена с PROG A линией 46 через обратного направления выходной буфер 198, управляемый управляющим сигналом OUT2, приходящим от Q выхода триггера 199.

После приложения питания к задерживающему устройству путем подъема потенциального уровня LOGIC линии (см. позицию 125 на фиг.7) логический блок 126 генерирует RESET импульс 200, распространяющийся по входной линии 204, соединенной с входом установки триггера 191, заставляя Q выход триггера 191 перейти на высокий уровень, тем самым переводя на высокий уровень INI* сигнал в позиции 208 и запрещая работу прямого направления входного буфера 190, предотвращая проход опорных синхронизирующих сигналов по PROG A линии на INTERNAL 1 шину 188. Затем логический блок 126 генерирует S RESET импульс 210 на тактовом входе триггера 191, вызывая передачу сигнального уровня на Р входе, с которым соединена PROG A линия, на Q выход. Поскольку при нормальных рабочих условиях PROG A линия на этом этапе находится на низком уровне, INI* сигнал переходит на низкий уровень в позиции 212, разрешая работу входного буфера 190 и позволяя синхронизирующим сигналам проходить через PROG A линию 46 на INTERNAL 1 шину 188. Триггером 197 также управляют RESET и S RESET сигналы от логического блока 126, точно так, как триггер 191, причем импульс 216 IN2*, приходящий с Q выхода триггера 197, идентичен с импульсом 208. Обратного направления входной буфер 196, таким образом, получает запрет и последующее разрешение на работы точно так, как буфер 190, сначала предотвращая и затем разрешая проход опорных синхронизирующих сигналов по PROG B линии 48 на INTERNAL 2 шину 194.

Во время периода, когда INI* и IN2* сигналы находятся на высоком уровне и запрещено работать входным буферам 190 и 196, за логическим уровнем PROG A и PROG B линий 46 и 48 осуществляется наблюдение, поскольку с этой целью они мониторинговыми линиями 218 и 220 соединены с D входами триггеров 191 и 197. Таким образом, если логический уровень PROG A или PROG B линии перейдет на высокий уровень на этом периоде в результате закорочения любой из них на высокий потенциал, Q выходы после тактирования будут удерживаться на высоком уровне S RESET импульсом 210 и постоянно будет запрещена работа входных буферов 190 и 196, чтобы предотвращался вход любых паразитных сигналов на INTERNAL 1 и INTERNAL 2 шины и их программирование в задерживающее устройство. На этом этапе INTERNAL 1 и INTERNAL 2 шины заземлены понижающими резисторами 221.

Нарастающий фронт RESET импульса 200 также заставляет перейти на высокий уровень выхода ИЛИ вентилей 222 и 224, соединенных с SET входами триггеров 193 и 199, тем самым переводя на высокий уровень OUTI* и OUIT2* сигналы на 230 и 232. Результатом этого является запрет на работу выходных буферов 192 и 198, что предотвращает прохождение программирующих сигналов через задерживающее устройство и предотвращает передачу паразитных сигналов, генерируемых на задерживающем устройстве, на соседнее задерживающее устройство через чувствительные линии 218 и 220.

При условии, что PROG A и PROG B линии находятся на низком уровне во время нарастающего фронта S RESET импульса 210, обоим входным буферам разрешено работать, поскольку INI* и IN2* сигналы находятся на низком уровне, что обеспечивает свободный доступ синхронизирующих сигналов, идущих по PROG A и PROG B линиям, к INTERNAL 1 и INTERNAL 2 шинам соответственно. Поэтому двунаправленный буфер готов к приему синхронизирующего сигнала, придет ли он по PROG A или PROG B линии. Если опорный синхронизирующий сигнал 234 приходит на PROG A терминал 46.1, т.е. при программировании в направлении хода часовой стрелки, INTERNAL 1 линия 188 также перейдет в позиции 236 на высокий уровень, когда входной буфер 190 имеет разрешение на работу. Это повлечет переход выхода ИЛИ вентиля 238 на высокий уровень. Поскольку RESET импульс 200 ранее зафиксировал Q выход триггера 240 на высоком уровне, выход И вентиля 242, а именно PROG линия 243, перейдет на высокий уровень в позиции 246 в ответ на появление высокого уровня на своем входе, соединенном с ИЛИ вентилем 238. В момент окончания синхронизирующего сигнала 234 от контроллера, который знаменуется переходом PROG A линии на низкий уровень в позиции 248, INTERNAL 1 линия перейдет на низкий уровень в позиции 250. Это повлечет прохождение положительного сигнала через НЕ вентиль 252 к тактовому входу триггера 193, тактируя внутрь земельный уровень D входа, в результате чего переходит на низкий уровень OUTI* сигнал в позиции 254, что дает разрешение на работу прямого направления выходного буфера 192 и соединяет INTERNAL 1 шину 188 с PROG B линией 48.

В то же самое время триггер 240 перекинется в результате перехода на низкий уровень выхода И вентиля 242 после перехода на низкий уровень выхода ИЛИ вентиля 238. Выходной сигнал от И вентиля 242 направляется обратно через инвертор 256, чем Q выход триггера 240 удерживается на нуле и предотвращается поступление дальнейшей информации на задерживающее устройство через PROG линию 243.

ИЛИ вентили 222 и 224, у каждого из которых один вход соединен с Q* выходом противоположных триггеров 193 и 199 соответственно, предотвращают триггер 199 от выдачи разрешения работать выходному буферу, когда происходит программирование по PROG линии, а также предотвращает триггер 193 от выдачи разрешения работать выходному буферу 192, если синхронизирующие сигналы идут в противоположном направлении по линии PROG B.

PROG линия 243 используется для передачи программирующего сигнала 246, который программирует задерживающее устройство через логический блок 126, как выше было описано со ссылками на фиг.6 и 10.

Когда по PROG A линии приходит следующий импульс 256, получают разрешение работать входной буфер 190 и выходной буфер 192, что разрешает импульсу 256 пройти через буфера 190 и 192, тем самым минуя рассматриваемое задерживающее устройство, и попасть на следующее задерживающее устройство, подлежащее программированию. При нормальных рабочих условиях импульс 256 оказывается первым импульсом, проходящим по PROG 48, и поэтому он будет запрограммирован в следующее задерживающее устройство описанным выше образом.

Если произойдет разрыв в проводке 14, о чем сказано выше, перед программированием рассматриваемого задерживающего устройства синхронизирующие сигналы при участии контроллера изменяют маршрут следования на обратное направление: от входного-выходного порта 60 по PROG В линии, как это описано выше. Программирование в обратном или против хода часовой стрелки по PROG В линии осуществляется точно так, как это описано применительно к PROG А линии, поскольку схема двунаправленного буфера 124 абсолютно симметрична.

Обратимся теперь к фиг.11, на которой изображен альтернативный вариант осуществления двунаправленного буфера и его логической схемы, в которой последовательность задерживающих устройств 1, 2.N, N+1, встроенных в этот вариант, соединены последовательно с портами А и В контроллера 12. Для простоты иллюстрации изображена лишь PROG линия 47 проводки. Каждое из задерживающих устройств 1,N+2 содержит двунаправленный буфер 302, работой которого управляет логическая схема буфера 304, которая более подробно проиллюстрирована на фиг.12. Логическая схема буфера 304 в свою очередь соединена с остальной частью схемы задерживающего устройства 306, которое может быть выполнено в соответствии с любым из вариантов, представленных на фиг.6 и 10.

Основными шагами настройки и программирования синхронизирующего устройства являются следующие.

Первоначально, как проиллюстрировано на фиг. 16, LOGIC линия 64 переходит на высокий уровень в позиции 314, обеспечивая питанием стабилизированную внутреннюю 5-ти вольтовую силовую линию 308 для подачи питания на двунаправленные буфера 302 и буферную логическую схему 304. Задерживающие устройства 1 по N+2 каждый имеет PROR А и PROG B терминалы. PROG А терминалы принимают синхронизирующие сигналы, идущие в направлении движения часовой стрелки по PROG линии 47 от А порта 20 контроллера 12, и терминалы PROG В принимают синхронизирующие сигналы, идущие в направлении, противоположном ходу часовой стрелки, от порта В 22 контроллера 12. Для простоты иллюстрации, на фиг. 11 подробно представлены только три задерживающих устройства, три сотни и более задерживающих устройств можно соединить вместе для реализации синхронизирующего устройства.

После перевода внутренней силовой линии 308 на высокий уровень логической линией контроллер 12 передает тест-сигнал 316 через В порт 22. Если в проводке 14 нет разрыва, тест-сигнал проходит через задерживающие устройства в направлении, противоположном ходу часовой стрелки, и оказывается принятым в порту А контроллера спустя короткую задержку, как проиллюстрировано импульсом 318. В ответ на прием этого пульса контроллер переводит В порт на низкий уровень, как изображено в позиции 320. Это в свою очередь приводит к тому, что "0" проходит через задерживающее устройство в направлении, противоположном ходу часовой стрелки, при этом наличие "0" на соответствующих В терминалах задерживающих устройств 1. N+2 означает, что программирование будет происходить в направлении хода часовой стрелки.

Наблюдая за состоянием своего порта А, контроллер 12 может определить: есть или нет разрыв в проводке 14. Если порт А принимает входной сигнал высокого уровня по тест-сигналу 318, в проводке 14 нет разрыва и система, вероятно, не имеет повреждений. Однако, если вход порта А остается на низком уровне, как проиллюстрировано позицией 322 на фиг.17, это означает, что проводка 14 имеет разрыв, поэтому некоторые задерживающие устройства надо программировать в направлении хода часовой стрелки, а некоторые против хода часовой стрелки. Поскольку контроллер 12 не получает тест-сигнал 318 на своем порту А, он удерживает тест-сигнал, исходящий из порта В, на высоком уровне, как проиллюстрировано позицией 324, указывая, что по крайней мере, некоторые из задерживающих устройств должны программироваться синхронизирующими сигналами, исходящими из порта В.

Ниже подробно описана работа двунаправленного буфера 302 и управляющей буфером логической схемы 304 со ссылками на фиг.15, 18 и 20.

А и В терминалы каждого задерживающего устройства имеют соответственные понижающие резисторы 326 и 328, соединенные с землей, и соответственные повышающие резисторы 330 и 332, соединенные с внутренней силовой линией 308 через соответственно первый и второй управляемые переключатели 334 и 336, которые представляют собой pnp транзисторы. Когда включены управляемые переключатели 338 и 340, представляющие собой p-транзисторы, непосредственно соединяют А и B терминалы с землей. После подачи питания на задерживающее устройство сбрасывающий сигнал, исходящий от сбрасывающей схемы 137 на фиг.6 и 10, сбрасывает D триггеры 341, 342 и 314, тем самым устанавливая в единицу триггеры 344 и 346 с Q выходами на высоком уровне и сбрасывая триггеры 341, 342 и счетчик 348 с Q выходами на низком уровне. В результате этого И вентиль 350 будет иметь на выходе низкий уровень и ИЛИ вентиль 351 высокий уровень на выходе, что влечет запирание соответственно транзисторов 340 и 336. Транзисторы 334 и 338 заставляют выходной сигнал на терминале А повторят входной сигнал на терминале В следующим образом. Если терминал В на низком потенциальном уровне, то этот уровень будет преобразован инвертором 352, так, чтобы на вентиль 353 поступил входной сигнал высокого уровня. Поскольку два других входа И вентиля фиксируются на высоком уровне, высокий выходной сигнал И вентиля 353 отопрет транзистор 338. Низкого уровня входной сигнал от терминала В так же будет инвертирован инвертором 354, обеспечивая высокий выходной сигнал от ИЛИ вентиля 356, что в свою очередь обеспечивает высокий выходной сигнал ИЛИ вентиля 358 через И вентиль 360, запирающий pnp-транзистор 334.

Если, с другой стороны, на терминале В высокий уровень, транзистор 334 отопрется и транзистор 338 запрется противоположным действием тех же самых вентилей, обеспечивая сигналу высокого уровня на терминале В прохождение на терминал А. Совокупность транзисторов, резисторов И вентилей 350 и 353 и инверторов 352 и 361 составляет схему двунаправленного буфера в этом варианте осуществления изобретения.

Высокого уровня сигнал на порту В контроллера 22 будет распространяться в направлении, противоположном ходу часовой стрелки, от терминала В к терминалу А задерживающих устройств описанным выше образом, только не будет достигать А порта 20, если в проводке 14 имеется разрыв. Если в проводке будет разрыв, как проиллюстрировано позицией 362, резистор 328 задерживающего устройства N, терминал которого соседствует с разрывом и который, следовательно, отсоединен от соседнего задерживающего устройства N+1, переведет В терминал на низкий потенциальный уровень, приводя к распространению низкого уровня сигнала в обратном направлении через задерживающие устройства N, 2 и 1 к порту А контроллера 12, как проиллюстрировано позицией 322 на фиг.17, приводя к сохранению сигнала высокого уровня на порте В, что проиллюстрировано позицией 324.

Как сказано выше, если не обнаружена неисправность, контроллер 12 переводит на низкий потенциальный уровень порт В, причем низкого уровня сигнал распространяется через все задерживающие устройства в направлении, противоположном ходу часовой стрелки, принимая низкий уровень на порту А, тем самым настраивая проводку 14 на программирование в направлении хода часовой стрелки, как это будет более подробно разъяснено в спецификации.

После подачи питания на задерживающее устройство N на фиг.15 локальный осциллятор 128 создает тактовый сигнал и посылает его через И вентиль 363 на тактовый вход счетчика 348, заставляя Q выход счетчика создать высокого уровня DIRN STORE сигнал спустя приблизительно 10 мс после того, как посредством тестового сигнала был определен интервал времени, за который определялось наличие повреждения в проводке и все терминалы задерживающих устройств приведены в надлежащее состояние. DIRN STORE cигнал в свою очередь передается на тактовый вход триггера 341, передающего этот уровень терминала В на Q выход триггера 341. После дальнейшей задержки около 10 мс DIRN SET сигнал, исходящий от Q выхода счетчика 348, переносит уровень терминала В, заполненный триггером 341, на триггеры 342 и 344. Если терминал В имеет низкий уровень, то запрется транзистор 338, поскольку И вентиль 353 принимает на входе сигнал низкого уровня с Q выхода триггера 344.

Низкого уровня выходной сигнал И вентиля 360, один из входов которого принимает сигнал низкого уровня выхода Q триггера 344, влечет появление низкого выходного сигнала на ИЛИ вентиле 358. Этот низкого уровня выходной сигнал в свою очередь заставляет открыться транзистор 334, что влечет повышение уровня терминала А и, следовательно, его способность принимать отрицательные программирующие сигналы, исходящие из порта А контроллера 12. Транзистор 336 запирается высоким выходным сигналом вентиля ИЛИ 351, поскольку Q* выход триггера 342 находится на высоком уровне по причине наличия низкого уровня сигнала на его D входе, который был установлен DIRN SET сигналом. Транзистор 340 по-прежнему способен переключаться в зависимости от уровня входного сигнала на терминале А. Если на терминале А низкий уровень, терминал В будет приведен на низкий уровень, так как транзистор 340 будет включен через И вентиль 350, по причине чего, если терминал А имеет высокий уровень, транзистор 340 закроется, освобождая терминал В и позволяя ему принять высокий потенциальный уровень от терминала А соседнего задерживающего устройства. Поэтому те задерживающие устройства, чьи В терминалы находятся на низком уровне перед прибытием DIRN SEТ и DIRN STORE сигналов, устанавливаются в единицу с отпиранием их транзисторов 334, причем их А терминалы обретают высокий потенциальный уровень и разрешают отрицательным программирующим импульсам проходить на их В терминалы.

Если, с другой стороны, терминал В имел высокий уровень, когда настраивалась РРОС линия 47 проводки 14, это означало, что имелся разрыв 362 в проводке 14 между задерживающим устройством N+2 и портом А контроллера 12. После перехода DIRN SЕТ сигнала на высокий уровень транзистор 336 отпирается через вентиль ИЛИ 351, транзистор 334 запирается через посредство высокого уровня сигнала от И вентиля 360 и ИЛИ вентиля 358, и транзистор 340 запирается низкого уровня сигналом от И вентиля 350. Двунаправленный буфер 302 окажется настроенным на конфигурацию, которая является обратной относительно ранее описанной. В терминале задерживающих устройств N+1 и N+2 будут переведены на высокий потенциальный уровень, после чего станут готовы принять отрицательные программирующие импульсы, идущие в направлении, противоположном ходу часовой стрелки. После приема отрицательного программирующего сигнала на терминале В задерживающего устройства N+2, идущего от порта В, транзистор 338 задерживающего устройства N+2 получает разрешение переключаться, создавая возможность низкому сигнальному уровню на его терминале В перейти на его же терминал А и, следовательно, на терминал В задерживающего устройства N+1, переводя на низкий уровень терминала А задерживающего устройства N+2 вопреки токового возбуждения от транзистора 336 задерживающего устройства N+1. Эта процедуpа будет более подробно описана в спецификации.

После перехода DIRN SЕТ на низкий уровень ОЗ выход счетчика 348 переходит на высокий уровень и инвертируется инвертором 347. Низкого уровня PROG ENABLE (разрешение программирования) сигнал с выхода инвертора 347 снимает управление "установка" с триггера 346 и управление "сброс" с триггера 368 или 370, что зависит от состояния триггера 344, выходное сигналы которого определяют направление программирования. Если на Q выходе триггера 344 высокий уровень, означающий, что принято противоположное ходу часовой стрелки направление программирования от терминала В к терминалу А, то триггер 368 остается в сброшенном состоянии через посредство ИЛИ вентиля 371 и не будет принимать участие в процедуре программирования. С другой стороны, если Q* выход триггера 344 имеет высокий уровень, означающий программирующее направление по ходу часовой стрелки, триггер 370 остается в сброшенном состоянии через посредство ИЛИ вентиля 372 и не будет принимать участие в процессе программирования.

На этом этапе задерживающие устройства по-отдельности настраиваются на прием синхронизирующих сигналов в направлении хода часовой стрелки от терминала А к терминалу В, если ранее не был обнаружен разрыв непрерывности в проводке 14. Транзистор 334 откроется, разрешая буферу 302 принять отрицательный программирующий импульс, поступающий на терминал А. Когда терминал В соединен с функционирующим задерживающим устройством, он будет удерживаться на высоком уровне pnp-транзистором А терминала этого задерживающего устройства. С другой стороны, другой pnp-транзистор 336 закроется и его соответственный терминал В будет удерживаться на низком уровне понижающим резистором 328, если соединен либо с непрограммирующим портом В контроллера, либо с неисправным задерживающим устройством или оборванной частью проводки. При наличии разрыва задерживающее устройство со своим терминалом А, соседствующим с терминалом В вышеназванного задерживающего устройства, буфер 302 может быть настроен на прием отрицательных программирующих импульсов, поступающих на его терминал В в противоположном ходу часовой стрелки направлении, причем его pnp-транзистор 336 будет открыт и его pnp-транзистор 334 закрыт, обеспечивая возможность сигнальному уровню на терминале А повторять таковой, имеющийся на терминале В.

Затем контроллер 12 переводит свои А и В порты 20 и 22 в состояние высокого импеданса, позволяя им принять высокий уровень под влиянием соседних задерживающих устройств, исключая случаи, когда нет повреждений в проводке, а в таких случаях порт В контроллера переводится на низкий уровень резистором 328 соседнего задерживающего устройства N+2.

В случае появления разрыва непрерывности в позиции 362, например, для контроллеpа 12 становится необходимостью определения его точного местоположения, чтобы были запрограммированы правильные синхронизирующие сигналы в задерживающие устройства, находящиеся по другую сторону от этой неисправности.

Для этого после настройки на программирование либо по ходу, либо против хода часовой стрелки каждое задерживающее устройство подвергается квази-программирующей процедуре, в ходе которой оно программируется коротким отрицательным импульсом от контроллера 12, во время которого оно реагирует через DETONATOR линию описанным выше образом.

В случае обнаружения разрыва, подобного проиллюстрированному позицией 362, последовательность коротких отрицательных импульсов подается из порта А контроллером для квази-программирования задерживающих устройств 1,2. до N. Задерживающие устройства от 1 до N предварительно настроены на программирование в направлении хода часовой стрелки, и первый квази-программирующий или счетный импульс, переданный из порта А контроллера, обходит задерживающие устройства с 1 по N-1, которые настроены на режим пропуска сигнала, причем их В терминалы переведены на высокий уровень pnp-транзисторам 334 соседнего задерживающего устройства. По причине неисправности 362 задерживающее устройство N имеет на своем В терминале низкий уровень, задаваемый понижающим резистором 328, который заставляет его работать в режиме запоминания сигнала, разрешая ему принять первый отрицательный счетный импульс. После выполнения программирования терминал А задерживающего устройства переводится на низкий уровень понижающим резистором 326, что влечет переход на низкий уровень терминала В соседнего N-1 задерживающего устройства, тем самым разрешая ему работать в режиме запоминания сигнала для приема следующего отрицательного квази-программирующего сигнала. Таким образом, квази-программирование задерживающих устройств осуществляется в обратном порядке от N до 1. После того как задерживающее устройство 1 оказалось "запрограммированным", его терминал А переходит на низкий уровень, что в свою очередь делает низким сигнальный уровень порта А, в то время как его буфер "плавает" в режиме высокого импеданса.

Во время процедуры тестирования и подсчета задерживающих устройств, описанной выше, каждый квази-программирующий сигнал возвращается через DET POWER линию, которая включена в параллель с каждым задерживающим устройством, как это проиллюстрировано на фиг.6 и 10, когда имеет место программирование или подсчет задерживающего устройства. Если разрыв 363 в проводке 47 отделяет все линии, счетные сигналы будут возвращаться в порт А контроллера 12 по линии DET POWER. Если, с другой стороны, разрыв 362 отделяет только PROG линию, квази-программирующие сигналы будут возвращаться на оба порта А и В. Затем контроллер подсчитывает число сигналов, возвращающихся по DET POWER линии, и это число запоминается контроллером.

Затер порт В контроллера 12 посылает последовательность отрицательных импульсов, чтобы "запрограммировать" задерживающие устройства N+1 и N+2. Путем наблюдения за линией можно установить число задерживающих устройств, нуждающихся в программировании в противоположном ходу часовой стрелки направлении.

Запомнив число запоминающих устройств с каждой стороны разрыва 362, контроллер оказывается в состоянии выбрать из своей таблицы в только считываемой памяти правильный синхронизирующий сигнал для каждого сдерживающего устройства. Далее, задавая программирующую последовательность, можно установить приблизительно местоположение разрыва 362, а также число задерживающих устройств, которые доступны для программирования. Может возникнуть ситуация, когда проводка 47 разорвалась в двух местах, например в позиции 362 и позиции 363. В этом случае счетными импульсами можно считать только четыре задерживающих устройств, а именно: 1,2 N+1 и N+2, при общении с контроллером 12. Предполагая, что общее число задерживающих устройств, соединенных последовательно в систему, равно пятидесяти, можно легко обнаружить, что не все устройства подсоединены к контроллеру 12 и принять решение об отмене всей процедуры.

Если в проводке нет разрыва и задерживающие устройства настроены на программирование в направлении хода часовой стрелки, ту же самую счетную процедуру можно применить для подтверждения того, что к контроллеру 12 подсоединено заданное число задерживающих устройств.

При настройки и подсчете задерживающих устройств отключение питания от всех задерживающих устройств осуществляется переводом питающей логику линии на низкий уровень, чтобы выполнить сброс всех запоминающих устройств и стереть счетные сигналы, которые были запрограммированы в каждый установочный счетчик задерживающего устройства. Затем на задерживающие устройства подается питание и выполняется процедура задания направления путем повышения уровня порта В в случае разрыва проводки или понижением уровня порта В в случае, если разрыв не обнаружен. Затем буфера 50 и 52 соответственно А и В портов переводятся в режим высокого импеданса перед началом фактического программирования синхронизирующих сигналов в задерживающие устройства. В ходе фактического программирования задерживающие устройства работают точно так, как это описано выше применительно квази-программированию или счетной процедуре.

После программирования синхронизирующих сигналов в задерживающие устройства уровень DET POWER поднимается для заряжения конденсаторов в каждом задерживающем устройстве, как это было выше описано со ссылкой на позицию 115 фиг. 6, и затем уровень DET POWER линии понижается в позиции 120 для пуска задерживающих устройств, заставляя их активизировать ассоциированные с ними детонаторы после истечения временной задержки, которая запрограммирована в каждое из задерживающих устройств. Представленный на фиг.20 алгоритм ясно представляет процедуру, описанную выше, что избавляет от необходимости давать дальнейшие разъяснения.

Ниже будут даваться ссылки на фиг.18, которая иллюстрирует временную диаграмму программирования в направлении хода часовой стрелки, когда в проводке 14 не обнаружен разрыв. Контроллер 12 поднимает уровень своей DETONATOR линии до мониторингового уровня 400. Порт А контроллера удерживается на уровне 402 повышающим резистором 330 и pnp-транзистором 334 соседнего задерживающего устройства 1. Затем контроллер 12 понижает уровень порта А в позиции 404, задавая начало первого программирующего импульса. Q выход триггера 344 имеет низкий уровень, означающий, что принято для программирования направление движения часовой стрелки от терминала А к терминалу В. Состояние сброса снимается с триггера 368 через ИЛИ вентиль 371, тем самым разрешая ему работать, и Q выход триггера 344 заставляет триггер 370 выполнить сброс через ИЛИ вентиль 372, запрещая тем самым ему работать.

После этого задерживающие устройства 1 до N+2 оказываются настроенными на распространение отрицательных программирующих импульсов в направлении хода часовой стрелки, причем их В терминалы удерживаются на высоком уровне pnp- транзисторами 334 соседних задерживающих устройств. Таким образом, сигнальный уровень на терминале В будет повторять сигнальный уровень на терминале А через посредство И вентиля 350 и npn- транзистора 340 после короткой задержки, равной длительности прохождения. Если терминал В задерживающего устройства 1 имеет высокий уровень, означающий незапрограммированность соседнего задерживающего устройства 2, то высокий входной сигнал на терминале В инвертируется инвертором 376 для создания низкого уровня сигнала на D-входе триггера 358.