Масштабируемое интегрированное устройство обработки данных - RU2201015C2

Код документа: RU2201015C2

Чертежи

Описание

Изобретение относится к масштабируемому интегрированному устройству обработки данных, в частности микрокомпьютеру, включающему в себя процессорный модуль, содержащий по меньшей мере один процессор, и запоминающий модуль, имеющий по меньшей мере один блок памяти, и выполненному на несущей подложке, с использованием взаимно смежных по существу параллельно упакованных основных слоев, при этом процессорный и запоминающий модули сформированы в по меньшей мере одном основном слое, и каждый отдельный основной слой содержит по меньшей мере один процессор и/или по меньшей мере один блок памяти, а каждый основной слой внутри слоя или на слое содержит электропроводящие структуры, образующие в нем внутренние электрические соединения.

Очевидный парадокс современных устройств обработки данных на основе полупроводников состоит в том, что хотя производительность микропроцессоров в последние годы повышалась в среднем на 60% в год, и, следовательно, с конца восьмидесятых годов и до 1998 г. возросла приблизительно в 100 раз, время доступа к запоминающему устройству (или время выборки) с произвольной выборкой так называемых ЗУПВ, уменьшалось приблизительно на 7% в год и, следовательно, уменьшилось только вдвое за тот же самый период времени. Следовательно, за последние десять лет разрыв между производительностью процессора и временем доступа к запоминающим устройствам ЗУПВ увеличился приблизительно в 50 раз. Поэтому разработки, направленные на повышение производительности процессора и сокращение времени выборки, наряду с усовершенствованием пропускной способности памяти призваны сократить время ожидания, в течение которого должны быть найдены и считаны инструкции и данные. Однако при разработке динамических ЗУПВ (DRAM) акцент делался на снижении размера ячеек памяти, чтобы реализовать динамические ЗУПВ (DRAM) с высокой плотностью хранения.

В более широком смысле причина вышеупомянутой диспропорции совершенно очевидна. На различных стадиях вычислений процессор должен взаимодействовать с по меньшей мере одним типом памяти, и в некоторых случаях связь может быть очень интенсивной, например, когда обработка предполагает использование справочных таблиц. На практике для того чтобы достичь высоких скоростей обработки, самые быстродействующие и наиболее часто используемые блоки памяти выполняются интегрированными с центральным процессором. Однако при значительных емкостях хранения блоков памяти последние занимают относительно большую площадь чипа, и в этом случае трудно достичь компромисса при распределении площади чипа между процессором и быстродействующими блоками памяти. Это в свою очередь подразумевает, что дополнительная емкость памяти может быть получена только с помощью проводников шины, подключенных к более отдаленным модулям памяти. В общем случае в зависимости от оптимизации в каждом отдельном случае в результате может быть получена общая архитектура устройства, в которой большая часть площади чипа и производительность обработки центрального процессорного модуля используется для манипуляции потоком данных между центральным процессором и более отдаленными модулями памяти, которые соединены с центральным процессорным модулем с помощью проводников шины на полупроводниковой подложке.

В конкретных условиях это означает, что микропроцессор затрачивает 75% времени в запоминающем устройстве, когда он должен выполнять обработку базы данных и матричные вычисления. Тенденции развития таковы, что 60% площади и 90% транзисторов наиболее современных микропроцессоров используются для преодоления разрыва между производительностью процессора и частотой выборки посредством использования в специальных аппаратных средствах на чипе, например в специальных быстродействующих блоках памяти или блоках кэш-памяти для того, чтобы отрегулировать увеличивающееся время ожидания. Разработчики столкнулись также с трудностями при совершенствовании динамического ЗУПВ (DRAM). В 1986 г. использовалась типовая минимальная емкость памяти для ПК из 32 динамических запоминающих устройств ЗУПВ (DRAM) емкостью 1 Мбит, тогда как в 1997 г. использовалось два динамических запоминающих устройства ЗУПВ (DRAM) емкостью 64 Мбит, поскольку скорость роста минимального объема памяти составила только половину скорости роста емкости динамического ЗУПВ (DRAM). Поскольку большинство современных микропроцессоров ориентируется на использование блоков кэш-памяти, необходима память с более низким временем ожидания, однако разработки развивались в направлении более высокой пропускной способности и меньшего времени ожидания. Очевидно, что увеличение емкости динамических ЗУПВ (DRAM) не решает проблему, поскольку разработка динамических ЗУПВ (DRAM) с емкостью 256 Мбит или 1 Гбит в действительности приведет к более высокой стоимости в расчете на бит и вызовет более высокие требования к пропускной способности для осуществления контроля над ошибками, что повлечет за собой увеличение времени ожидания.

Попытка решить проблему диспропорции между производительностью процессора и временем доступа к ЗУПВ (RAM) была предпринята в публикации (Patterson и соавт., "Intelligent RAM (IRAM): Chips that Remember and Compute", 1997, IEEE International Solid-State Circuits Conference, стр.224-225), в которой предложено воспроизводить процессорную логику и память на одном и том же чипе, в котором большинство транзисторов будет использоваться в запоминающем устройстве. Интегрированное устройство обработки данных этого вида было названо интеллектуальным ЗУПВ или ИЗУПВ (IRAM). Использование памяти динамического ЗУПВ (DRAM) с емкостью 1 Гбит обеспечивает достаточное число транзисторов для создания мощного процессора и памяти, которая является достаточно емкой, чтобы содержать целые программы и наборы данных. В интеллектуальном ЗУПВ (IRAM, ИЗУПВ) этого вида запоминающее устройство (ЗУ) разделяется на блоки с вентильными схемами памяти размером, например, 1 Кбит. В случае, если типовые размеры чипа будут составлять 600 мм2, для интеллектуального ЗУПВ (IRAM, ИЗУПВ) будет требоваться большее количество металлических слоев для увеличения скорости передачи линии связи, а также, возможно, потребуются более высокочастотные транзисторы для быстродействующего интерфейса синхронных динамических ЗУПВ (DRAM). Возможные преимущества, получаемые в случае использования интеллектуального ЗУПВ (IRAM, ИЗУПВ), включают в себя на порядок более низкое время ожидания памяти, на два порядка более высокую пропускную способность памяти и более низкую потребляемую мощность. Размеры ЗУ (размеры по ширине) могут регулироваться, и интеллектуальное ЗУПВ (IRAM, ИЗУПВ) не должно занимать на плате площадь, аналогичную по размеру площади, занимаемой известными устройствами обработки данных с соответствующей емкостью хранения и процессорной обработкой.

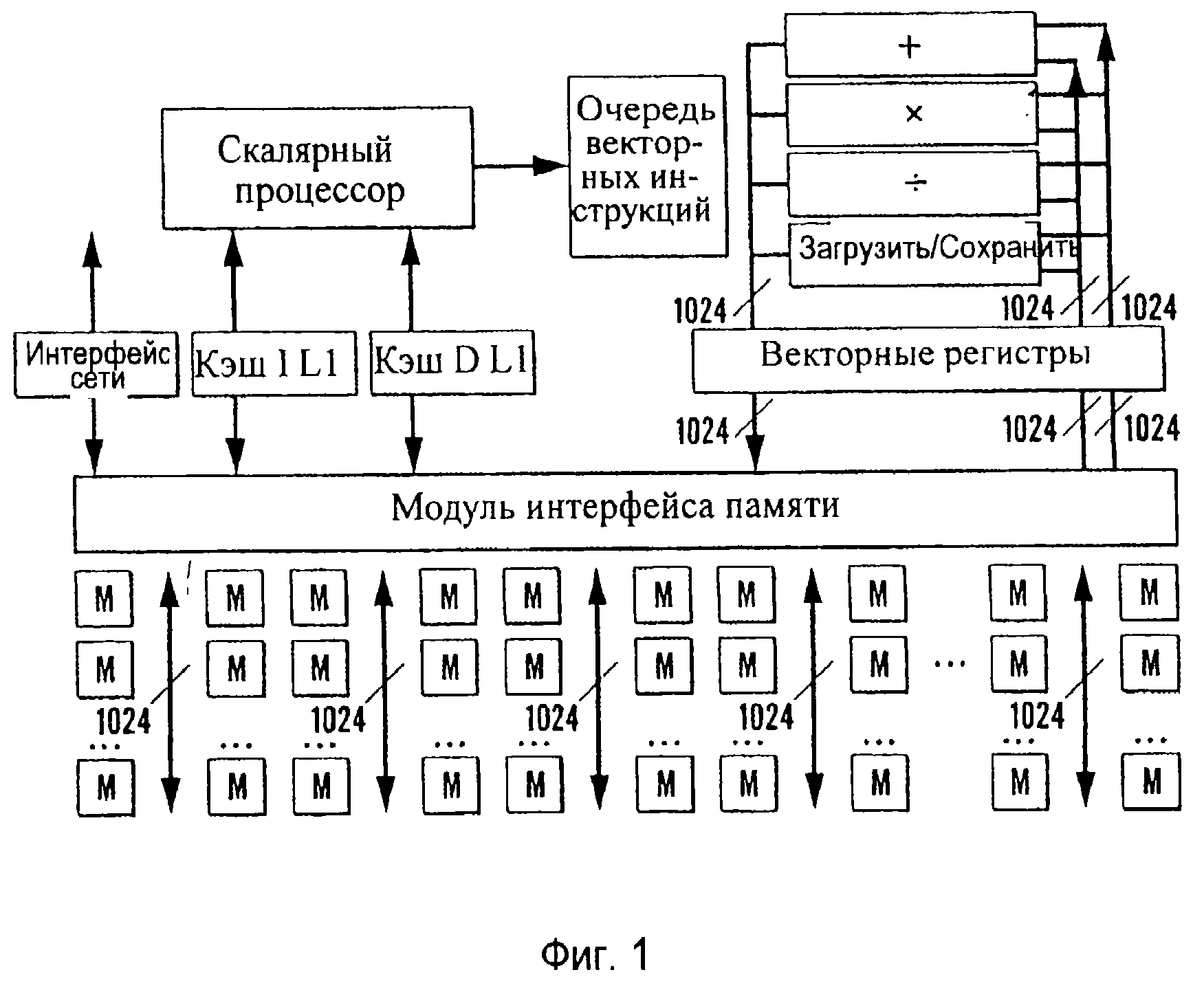

В качестве альтернативы было предложено (Yoo и соавт., "A 32-bank I Gb DRAM with GB/s Bandwidth, ISSCC Digest of Technical Papers, стр 378-379, Feb. 1996) использовать интеллектуальное ЗУПВ (IRAM, ИЗУПВ) с векторными процессорами. Векторные процессоры такого типа работают с линейными матрицами чисел. Векторные процессоры не нуждаются в блоках кэш-памяти, но требуют ЗУ с низким временем ожидания, часто реализуемое в виде статистического ЗУПВ (SRAM) с большой пропускной способностью, поскольку могут использоваться сотни отдельных групп памяти. Следовательно, предложенная система интеллектуального ЗУПВ (IRAM, ИЗУПВ) с емкостью памяти 1 Гбит будет адаптирована к потребностям векторного процессора. Вышеприведенный уровень техники проиллюстрирован на фиг. 1, на которой изображена схема осуществления векторного микропроцессора с интеллектуальным ЗУПВ (IRAM, ИЗУПВ). На основе процессора размером 0,18 мкм с динамическим ЗУПВ (DRAM) с площадью чипа 6 см2 интеллектуальное ЗУПВ (IRAM, ИЗУПВ) могло бы иметь 16 модулей сложения и умножения с рабочей частотой 500 МГц и 16 портов памяти шириной 1024 бита, которые при частоте 50 МГц совместно будут обеспечивать пропускную способность памяти 100 Гбайт/с. Интеллектуальное ЗУПВ (IRAM, ИЗУПВ) такого типа могло бы выполнять типовую тестовую программу (Linpack) с быстродействием 8•109 операций с плавающей запятой в секунду (Гига FLOPS), что в пять раз превышает быстродействие векторного процессора суперкомпьютера фирмы Крей (Cray Т-90). Может ли интеллектуальное ЗУПВ (IRAM, ИЗУПВ) иметь хорошие перспективы, будет зависеть от емкости памяти на чипе, поскольку ожидается, что емкость увеличится с 10-32 Мбайт для графических приложений, таких, как игры, и до 128-256 Мбайт для сетевых компьютеров и портативных ПК.

Кроме того, из уровня техники также известно использование параллельной обработки для увеличения скорости обработки. Это было достигнуто за счет использования архитектуры построения процессоров, позволяющей обрабатывать данные и наборы данных параллельно. В качестве примера можно привести процессоры с параллельной обработкой на уровне инструкций, типа конвейерных процессоров или суперскалярных процессоров, имеющих архитектуру, которая может манипулировать с очень длинными словами инструкций (VLIW). Также были разработаны процессоры, работающие на уровне инструкций, но параллельно с данными, что может быть реализовано с использованием любой архитектуры - конвейерной архитектуры, систолической архитектуры и, как уже упоминалось выше, векторной архитектуры. Труднореализуемой целью разработчиков являлось создание устройств обработки данных, способных работать с архитектурами, обеспечивающими возможность параллельной обработки данных на уровне процессора, т.е. с так называемой архитектурой MIMD ("много инструкций - много потоков данных"). Были предложены архитектуры "много инструкций - много потоков данных" либо с распределенной памятью, либо с общей памятью, но большинство этих архитектур априорно основано на различных формах параллельной многопроцессорной обработки, которая осуществляется с использованием сетей процессоров. В настоящее время указанные разработки трудно реализовать с оптимальной взаимосвязанностью и в любом случае невозможно осуществить с конфигурацией чипа при современном уровне полупроводниковой технологии, в частности, до тех пор, пока размер чипа ограничен несколькими см2.

Увеличивающийся разрыв между теоретическим быстродействием обработки современных центральных процессоров и общим быстродействием устройств представляет собой важную проблему, которая оказалась трудно устранимой и которую почти невозможно решить посредством дальнейшей разработки устройств обработки данных на базе, например только полупроводниковой технологии на основе кремния. Ни увеличение размера чипа, ни структурные решения, использующие вертикальные структуры и, следовательно, не позволяющие получить большее число компонентов на одном и том же материале подложки, не позволили решить вышеуказанную проблему. Это связано с тем, что ячейки памяти запоминающих устройств явно зависят от переключателей, выполненных в полупроводниковом материале подложки. Другими словами, каждый участок бита в ЗУ должен иметь эксклюзивный доступ к части подложки, и, следовательно, требуются структурные решения, при которых запоминающие устройства и процессор должны быть расположены рядом друг с другом. Попытки формирования вертикальных структур, например, посредством укладки нескольких слоев друг на друга, также потерпели неудачу, поскольку все это необходимо осуществлять с возможностью электрического доступа и с компонентами, например переключателями, находящимися на одной и той же нижележащей полупроводниковой подложке. Следовательно, не удается получить никакого общего увеличения емкости с использованием многослойных решений и с площадью подложки, уже эксплуатируемой с максимальной плотностью. При использовании вертикально уложенных слоев схем дополнительно возникает проблема с рассеянием тепла в отдельных слоях, поскольку современные блоки памяти на основе полупроводников не сохраняют информацию при выключении электропитания, и, следовательно, нуждаются в токе регенерации.

Вообще говоря упаковка нескольких слоев с компонентами, в которых используются активные переключатели, основанные на современных полупроводниковых технологиях, подразумевает использование поперечных токовых дорожек к нижележащим слоям. Это в большой степени ограничивает число слоев, которые могут быть упакованы, в частности, в которых различные слои и их части необходимо подключать токовыми дорожками. В дополнение к этому объем, заполненный плотной сетью поперечных токовых дорожек, сложность изготовления и, следовательно, увеличение издержек производства быстро возрастает с ростом числа слоев в упаковке.

В дальнейшем будет приведен ряд патентных публикаций, которые могут быть рассмотрены в качестве релевантных в том смысле, что они позволяют понять уровень техники, на котором основывается настоящее изобретение, но ни в коей мере не предвосхищающих изобретательскую идею в целом. Наиболее важные из этих публикаций принадлежат одному и тому же заявителю и, очевидно, имеют в своей основе одну и ту же изобретательскую идею.

В частности, в опубликованной международной заявке WO 95/09438 (Zavracky и соавт. , правопреемник патентовладельца - корпорация Kopin Corp.) раскрыт трехмерный процессор, в котором используются переведенные тонкопленочные схемы. Он реализуется в виде многослойной структуры, в которой микропроцессор скомпонован в различных слоях и имеет вертикальные межсоединения через изолирующие слои, отделяющие каждый слой схемы в структуре. Каждый слой схемы может быть изготовлен на отдельной тонкой кристаллической пластине или в тонкопленочном материале, а затем перенесен на слоистую структуру и взаимосвязан с ней. Более конкретно патент WO 95/09438 раскрывает комбинацию первого слоя схемы с управляющим модулем, и второго слоя схемы с логическим модулем, причем первый и второй слои схемы соединяются с помощью адгезионного слоя, а межсоединения между первым и вторыми слоями схемы формируются с помощью сквозных перемычек, которые проходят через отверстия в адгезионном слое. Как следует из патентного описания WO 95/09438, первый слой схемы может содержать управляющий модуль, второй слой схемы - арифметический логический модуль, а третий слой схемы - ЗУПВ, хотя блоки памяти также могут быть выполнены на первом и втором слоях схемы с образованием всеми слоями схемы комбинации микропроцессор - ЗУПВ, в которой, как уже упоминалось выше, вертикальные соединения обеспечиваются раздельными сквозными перемычками, которые непосредственно не образуют интегральную составную часть материала, поскольку слои схемы выполняются с дискретными компонентами, сформированными в или на слое полупроводника и, возможно, со вторым слоем схемы, выполненным со схемами в полупроводниковой тонкой пленке, нанесенной на изолирующую подложку. Решение по патенту WO 95/09438 существенно отличается от настоящего изобретения тем, что в нем не показано, каким образом основной слой схемы выполняется из множества подслоев, каждый из которых может содержать диэлектрические, полупроводящие и электропроводящие элементы. В противоположность этому в изобретении по патенту WO 95/09348 предполагается, что требуются отличающиеся и отделенные друг от друга слои для осуществления каждой электрической функции, и что взаимное электрическое соединение между компонентами обеспечивается посредством отдельных дорожек, нанесенных на слоях, или посредством отдельных сквозных перемычек, которые проходят через отверстия, сформированные в слоях, и, следовательно, не образуют интегрального участка из материала слоя. Применение указанной структуры в решении по патенту WO 95/09348 продиктовано использованием неорганической полупроводниковой технологии и тем, как она может использоваться для реализации чередующихся слоев памяти и процессора.

Патент США 5 656 548 (Zavracky и соавт., правопреемник патентовладельца - корпорация Kopin Corp.) аналогично патенту WO 95/09438 базируется на патентном описании США 08/130033 от 30 сентября 1993 и основан на заявке в продолжение, которая, в свою очередь, является приоритетной для патента WO 95/09438. Патент США 5 656 548 раскрывает прежде всего способ для изготовления многослойной структуры микропроцессора, состоящей из отдельных слоев, разделенных специальными изолирующими слоями таким образом, что вертикальное соединение образуется отдельным сквозными перемычками через слои. Каждый слой схемы может быть сформирован на отдельной тонкой кристаллической пластине из полупроводникового материала или в тонкопленочном материале, который переносится на слоистую структуру и взаимно соединяется с ней. Способ согласно патенту WO 95/09348 практически не отличается от способа согласно патенту США 5 656 548.

В патенте США 5 793 115 (Zavracky и соавт., правопреемник патентовладельца - корпорация Kopin Corp.), являющемся заявкой в частичное продолжение вышеупомянутого патента США 08/130033 от 30 сентября 1993 г., аналогично вышеупомянутым публикациям, первый слой схемы формируется в полупроводниковом материале и содержит управляющий модуль, в то время как второй слой схемы специальным образом формируется в тонкопленочном кремниевом материале с так называемой структурой кремния на изоляторе (структура SOI) и содержит логический модуль, подразумевающий формирование двумя слоями схемы процессорного модуля. Третий слой схемы формируется в виде запоминающего устройства ЗУПВ и, кроме того, в специальных версиях все устройство может быть реализовано в виде оптоэлектронного устройства обработки данных, в котором второй слой схемы в этом случае содержит светоизлучающее устройство. В этом случае многопроцессорный вариант осуществления устройства состоит из упаковки комбинаций смежных процессоров и запоминающих устройств ЗУПВ, с получением интегрированного многопроцессорного устройства, с вертикально уложенными слоями. Межсоединение между слоями и упаковкой, как и в предыдущих решениях, должно быть сформировано отдельными сквозными перемычками, которые не являются интегральными частями слоев и которые проходят через отверстия в слоях для подключения к электрическим межсоединениям в отдельных слоях схемы.

В патенте США 5 702 963 (Vu и соавт., правопреемник патентовладельца - корпорация Kopin Corp.) раскрываются лишь инструкции для изготовления устройства под названием "Устройство четырехполюсного полевого МОП-транзистора (MOSFET)", а также способы для изготовления нескольких таких устройств, например, в виде схем комплементарных КМОП структур, либо по планарной технологии на общей подложке, либо уложенных с использованием между ними изолирующих слоев с формированием трехмерной архитектурной схемы. Для того чтобы обеспечить электрическое соединение через слои, должны использоваться раздельные металлические сквозные перемычки, и по существу каждый отдельный слой выполняет исключительно одну и ту же электрическую функцию.

Далее в качестве примера предшествующего уровня техники может быть упомянут ряд патентных публикаций, которые имеют некоторое обобщенное отношение к последнему упомянутому патенту США 5 702 963, поскольку они затрагивают двух- или трехмерные схемотехнические структуры и по существу выполнены по известной полупроводниковой технологии.

Например, патент США 5 306 935 (Esquivel и соавт.) раскрывает матрицу памяти с двумя или более уложенными слоями ячеек памяти, где нижний слой является матрицей транзисторов, например с планарными структурами, структурами х-ячейки, или скрытыми N++ структурами лавинно-инжекционных МОП-транзисторов с плавающим затвором (FAMOS), и где верхний слой предпочтительно содержит матрицу планарных транзисторов. Эпитаксиальный кремниевый слой используется в качестве подложки для второго слоя. Даже несмотря на то, что в реферате публикации говорится о двух или более уложенных слоях или ячейках памяти, описание раскрывает вариант осуществления с двумя слоями, в котором для того чтобы получить необходимые электрические соединения через слои, в частности, обеспечиваются вертикальные металлические контакты в виде отверстий, пронизывающих слои.

Патент США 5 383 269 (Rathmell и соавт.) описывает не схемы, а трехмерное устройство, предназначенное для соединения интегральных схем между собой, которое позволяет осуществить соединение множества чипов схем в модуль со стандартной опорной поверхностью, для установки посредством различных технологий. Каждая интегральная схема монтируется на взаимно связывающейся пластинке, и пластинки укладывают вместе с электрическими соединениями от одного слоя пластинки к другому. В качестве пластинок могут быть использованы многослойные керамические пластинки или материалы, которые используются в печатных платах. В результате изготавливается модуль, состоящий из отдельных схем, сформированных друг над другом, взаимосвязанных между собой посредством отдельных взаимных соединений, которые не образуют часть соответствующих схем.

Патент США 5 817 986 (Davidson и соавт.) раскрывает архитектуру упаковки или укладки, которая позволяет осуществить очень плотную упаковку или укладку чипов интегральных схем с минимальными расстояниями взаимных соединений. Сама структура упаковки формируется посредством множества субблоков в виде подложки с по меньшей мере одной интегральной схемой, установленной на ней, после чего следует дополнительная подложка со специальной функцией и новый субблок, в котором чип схемы расположен на последнем упомянутом субблоке и формируется на подложке, соответствующей первому субблоку. Электрические соединения и соединения дорожек в субблоках, на которых монтируются чипы схем, расположены с возможностью контактирования с участками в подложке, находящейся между ними, то есть во втором субблоке, причем электрические соединения формируются посредством пайки, проводных соединений и т.п. Первая подложка в любом случае должна обеспечивать электрическое соединение между схемами и каждым субблоком, тогда как другая подложка может обеспечивать заземление и подачу питания к ряду субблоков. Субблоки, подложки и схемы, очевидно, могут быть заключены в устройство кубической формы, в котором чипы схем являются чипами схем памяти, что позволяет обеспечить объемное запоминающее устройство. Соединения между интегральными схемами и блоками памяти, очевидно, не образуют из них или из субблоков интегральный элемент, а являются, как упомянуто выше, разделенными взаимными соединениями дорожек или паянными соединениями.

Ниже приведены примеры элементов схем из предшествующего уровня техники. Например, патент США 5 612 228 (Shieh и соавт.) раскрывает схему КМОП структуры, сформированную посредством транзисторов из органических и неорганических материалов соответственно по тонкопленочной технологии, но по существу реализованную в виде плоской структуры с различными слоями с раздельными и отличающимися электрическими функциями, а патент США 5 714 768 (Ovshinsky и соавт.) раскрывает вычислительный модуль с процессором и специфической матрицей памяти, изготовленной по тонкопленочной технологии, смонтированной над процессором в верхней части устройства и выполненной, очевидно, на основе неорганического материала, который может принимать различные значения электрического сопротивления в ответ на электрические входные сигналы, подаваемые в отдельную ячейку памяти. Однако данная публикация имеет более близкое отношение к специальным элементам памяти в виде так называемой аморфно-полупроводниковой памяти (переключателям Овшинского), которые основаны на электрическом изменении фазы и выполняются с использованием неорганических халькогенидных соединений в качестве переключателей. В указанной публикации не содержится признаков устройства, близкого масштабируемому устройству обработки данных, которое является предметом настоящего описания, и высказана лишь идея относительно размещения запоминающего устройства в верхней части логического устройства, которая сама по себе при строгом рассмотрении не является принципиально новой, поскольку уже была предложена ранее для разработки запоминающих устройств, выполненных, например, на подложках с использованием известной полупроводниковой тонкопленочной технологии, на основе неорганических материалов, и содержащих схемы, например, выполненные по КМОП технологии, а также для разработки блоков памяти с такой конфигурацией укладки, которая позволила бы получить объемный вариант осуществления устройства.

Возможности увеличения процессорной обработки и емкости памяти в интегрированном устройстве обработки данных и достижения достаточной пропускной способности памяти при уменьшении времени ожидания в соответствии с увеличенным быстродействием процессора кажутся незначительными при использовании современной полупроводниковой технологии. Увеличение емкости памяти является основной задачей для всех типов памяти, применяемых в современных устройствах обработки данных, но оказывается особенно труднореализуемым для блоков памяти с быстрым произвольным доступом, с сохранением производительности процессорной обработки, а также размеров и стоимости устройств. Необходимые электрические соединения являются проблематичными сами по себе и кажутся неосуществимыми ни с использованием вертикальных или укладочных конфигураций, ни с увеличением площади чипа в обычных однослойных технологиях.

Задача, стоящая в основе настоящего изобретения, заключается в том, чтобы создать интегрированное устройство обработки данных, в котором процессорный модуль и модуль памяти имели бы практически неограниченные возможности варьирования конфигураций и архитектур, с оптимизацией требования по пропускной способности и времени ожидания, а также без необходимости электрического соединения между отдельными компонентами, накладывающего ограничение на величину емкости и время пересылки данных.

Другая задача настоящего изобретения заключается в том, чтобы избежать использования известных динамических запоминающих устройств (DRAM), реализуя вместо этого модуль памяти по технологии, которая обеспечивает одновременно как возможность быстрого доступа и большую емкость, так и возможности функциональной конфигурации модуля памяти в подмодулях, которые по отдельности выполняют, например, функции запоминающего устройства с произвольной выборкой ЗУПВ (RAM), функции постоянного запоминающего устройства ПЗУ (ROM) или широкие функции хранения.

Третья задача настоящего изобретения заключается в сокращении времени ожидания любого вида, для максимальной адаптации производительности процессора и доступа к памяти предпочтительно для исключения использования блоков кэш-памяти в процессоре.

Четвертая задача заключается в том, чтобы обеспечить возможность создания оптимально масштабируемых архитектур для параллельной обработки, интегрированных на одной и той же подложке, будь то использование параллельной архитектуры процессора, либо архитектуры многопроцессорной системы с динамическим соединением между процессорами, работающими параллельно.

Пятая задача изобретения заключается в том, чтобы реализовать интегрированное устройство обработки данных в объемной конфигурации и с токовыми дорожками, формируемыми и в горизонтальном и в вертикальном направлениях в объемной конфигурации, для обеспечения оптимальной взаимосвязанности между отдельными компонентами устройства обработки данных, и одновременного снижения скорости передачи данных между компонентами.

Вышеупомянутые и другие задачи решаются тем, что в предложенном устройстве обработки данных согласно изобретению каждый основной слой сформирован из множества подслоев; каждый подслой содержит разграниченные части с заданной геометрической формой, образующие соответственно диэлектрические, полупроводниковые или электропроводящие участки в подслое, причем подслой в дополнение по меньшей мере к одной диэлектрической части содержит по меньшей мере одну полупроводящую и/или электропроводящую часть, при этом в каждом подслое сформированы специфические разграниченные части с заданным электрическим параметром в регистрируемом соотношении с по меньшей мере одной соответствующей частью по меньшей мере в одном из смежных соседних подслоев, с возможностью образования указанными специфическими частями элементов интегральной схемы, разграниченных в плоскости подслоев, проходящих вертикально через один или более подслоев, причем каждый элемент схемы, зависящий от состава и электрических свойств, образует активные и/или пассивные элементы схемы в каждом основном слое, содержащие по меньшей мере резисторы, конденсаторы, диоды, транзисторы и элементы памяти, в каждом случае формируемые и электрически соединяемые между собой с возможностью реализации по меньшей мере одного процессора и/или блока памяти в основном рассматриваемом слое, а электропроводящие структуры формируются электропроводящими частями в подслое в горизонтальном направлении для создания горизонтальных электропроводящих структур, либо в регистрируемом соотношении с соответствующими электропроводящими частями в по меньшей мере одном соседнем смежном подслое, с возможностью образования электропроводящими структурами, интегрированными в подслоях, трехмерных электрических взаимосвязанных сетей в основных слоях и обеспечения межсоединения указанными структурами элементов схемы в трех измерениях, а также обеспечения факультативного межсоединения основных слоев, причем в устройстве обработки данных формируются дополнительные электропроводящие структуры с возможностью обеспечения межсоединения основных слоев и/или основных слоев с подложкой и обеспечения соединения с внешними по отношению к устройству обработки данных устройствами.

Согласно предпочтительному варианту осуществления устройства обработки данных согласно настоящему изобретению, подслои в по меньшей мере одном основном слое выполнены по технологии, предусматривающей на первом уровне функциональной иерархии функциональную компоновку по меньшей мере одного основного слоя в качестве объединенного слоя процессора и ЗУ, либо по меньшей мере одного основного слоя по существу в качестве слоя процессора, либо по меньшей мере одного основного слоя по существу в качестве слоя памяти.

Полезно, чтобы процессорный модуль в основном слое функционально был скомпонован на втором уровне функциональной иерархии в виде по меньшей мере одного процессора, либо частей по меньшей мере одного процессора, причем по меньшей мере один процессор является центральным процессором или микропроцессором в устройстве обработки данных, и возможно введение дополнительных процессоров, факультативно компонуемых в виде управляющих и/или связных процессоров соответственно.

Предпочтительно, чтобы центральный процессор был также функционально скомпонован на третьем уровне функциональной иерархии в виде параллельного процессора с несколькими исполнительными модулями, работающими параллельно, сформированными в одном и том же основном слое или по меньшей мере в двух основных слоях или в их подслоях, с возможностью обеспечения оптимальной топологии межсоединения. Если в данном варианте осуществления альтернативно имеется более одного центрального процессора, то каждый центральный процессор может иметь межсоединения и быть адаптированным для работы в параллельном режиме и быть сформированным в одном и том же основном слое или в по меньшей мере двух основных слоях для обеспечения оптимальной топологии межсоединения.

В этом же предпочтительном варианте осуществления согласно настоящему изобретению запоминающий модуль в основном слое функционально компонуется на втором уровне функциональной иерархии в виде по меньшей мере одного блока памяти или частей по меньшей мере одного блока памяти, причем по меньшей мере один блок памяти составляет ЗУПВ и соединяется по меньшей мере с одним управляющим процессорным модулем или микропроцессором, при этом возможно введение дополнительных блоков памяти, факультативно компонуемых как быстродействующие блоки памяти, постоянные запоминающие устройства ПЗУ (ROM), запоминающие устройства с однократной записью и многократным считыванием (WORM), СТИРАЕМЫЕ и ПЕРЕПРОГРАММИРУЕМЫЕ соответственно.

В связи с этим представляется выгодным, чтобы по меньшей мере два ЗУПВ были подключены к центральному процессору и соответственно присвоены по меньшей мере двум подмодулям в центральном процессоре, причем ЗУПВ и подмодули распределены в выбранных комбинациях по меньшей мере в одном основном слое для обеспечения оптимальной топологии межсоединения.

Кроме того, в процессе формирования по меньшей мере двух центральных процессоров, соединяемых с по меньшей мере одним общим запоминающим устройством или устройствами с произвольной выборкой ЗУПВ, предпочтительно, чтобы каждый центральный процессор был сформирован во взаимно смежных основных слоях или распределен в выбранных комбинациях между по меньшей мере двумя основными слоями, а запоминающее устройство или устройства с произвольной выборкой ЗУПВ были сформированы в выбранных комбинациях в по меньшей мере одном основном слое и/или в по меньшей мере одном слое ЗУ, смежном с последним, либо расположены чередующимися слоями между ними для обеспечения оптимальной топологии межсоединения.

Наконец, в данном варианте осуществления изобретения предпочтительно, чтобы по меньшей мере часть запоминующего модуля была выполнена в виде: ЗУ большой емкости, факультативно компонуемого как запоминающее устройство с произвольной выборкой ЗУПВ, постоянного запоминающего устройства ПЗУ (ROM), запоминающего устройства с однократной записью и многократным считыванием (WORM), СТИРАЕМОГО и ПЕРЕПРОГРАММИРУЕМОГО или их комбинации.

Согласно еще одному варианту осуществления, устройство обработки данных содержит несколько слоев процессора и несколько слоев ЗУ, причем слои памяти с целью уменьшения пути сигнала между ними и слоями процессора могут предпочтительно чередоваться между слоями процессора.

Согласно настоящему изобретению, представляется также предпочтительным формирование дополнительных электропроводящих структур в качестве торцевых электрических соединений на по меньшей мере одном боковом торце или через боковой торец по меньшей мере одного основного слоя для обеспечения контакта с электропроводящими структурами в других основных слоях и/или обеспечения электрического соединения между основными слоями и подложкой, и/или в качестве вертикальных проводящих структур в по меньшей мере одном основном слое с формированием электрических соединений в перекрестном направлении основных слоев, а также перпендикулярно к их плоскостям для контакта с электропроводящими структурами в других основных слоях и/или обеспечения электрического соединения между основными слоями и подложкой.

Согласно еще одному варианту осуществления изобретения, по меньшей мере один основной слой может быть сформирован из органического тонкопленочного материала, органического тонкопленочного материала или материалов, выбираемых из числа мономерных, олигомерных и полимерных органических материалов и металлоорганических комплексов, или комбинаций материалов данного типа. В связи с этим все основные слои предпочтительно формировать из органического тонкопленочного материала.

Согласно настоящему изобретению, также представляется предпочтительным, чтобы по меньшей мере один основной слой был сформирован из неорганического тонкопленочного материала, неорганического тонкопленочного материала или материалов, выбираемых из числа кристаллических, поликристаллических и аморфных тонкопленочных материалов, или комбинаций материалов данного типа.

Наконец, согласно настоящему изобретению, представляется предпочтительным, чтобы по меньшей мере один основной слой был сформирован как из органических, так и из неорганических тонкопленочных материалов или комбинаций материалов этого типа, органического тонкопленочного материала или материалов, выбираемых из числа мономерных, олигомерных и полимерных органических материалов и металлоорганических комплексов, или комбинаций материалов данного типа, а также неорганического тонкопленочного материала или материалов, выбираемых из числа кристаллических, поликристаллических и аморфных тонкопленочных материалов, или комбинаций материалов данного типа.

В дальнейшем изобретение поясняется описанием

конкретных вариантов его осуществления со ссылками на фиг.1-26, на которых одинаковые номера позиций обычно обозначают подобные части (но подобные части не везде снабжены номерами позиций) и на

которых:

фиг.1 изображает интеллектуальное ЗУПВ (интеллектуальное ЗУПВ (IRAM, ИЗУПВ)) с векторным микропроцессором согласно уровню техники;

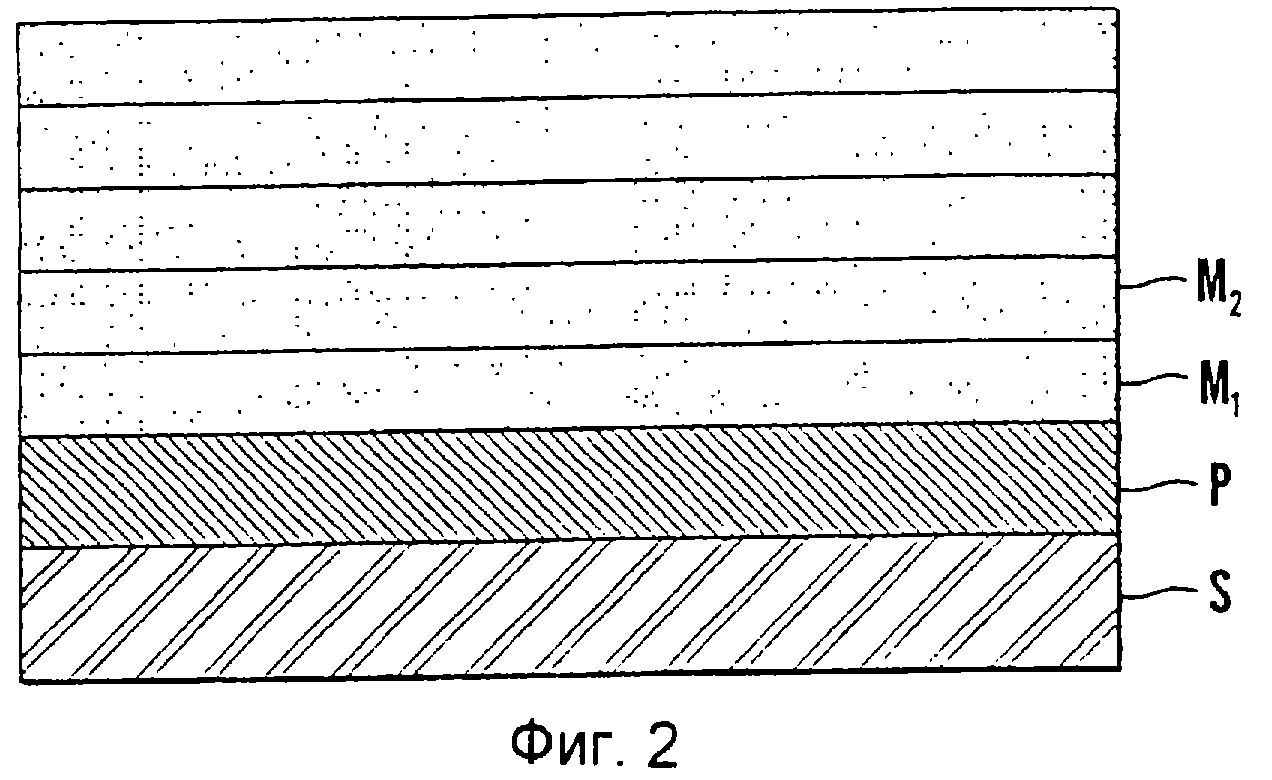

фиг.2 изображает устройство обработки

данных, интегрированное в виде упакованных слоев, согласно настоящему изобретению;

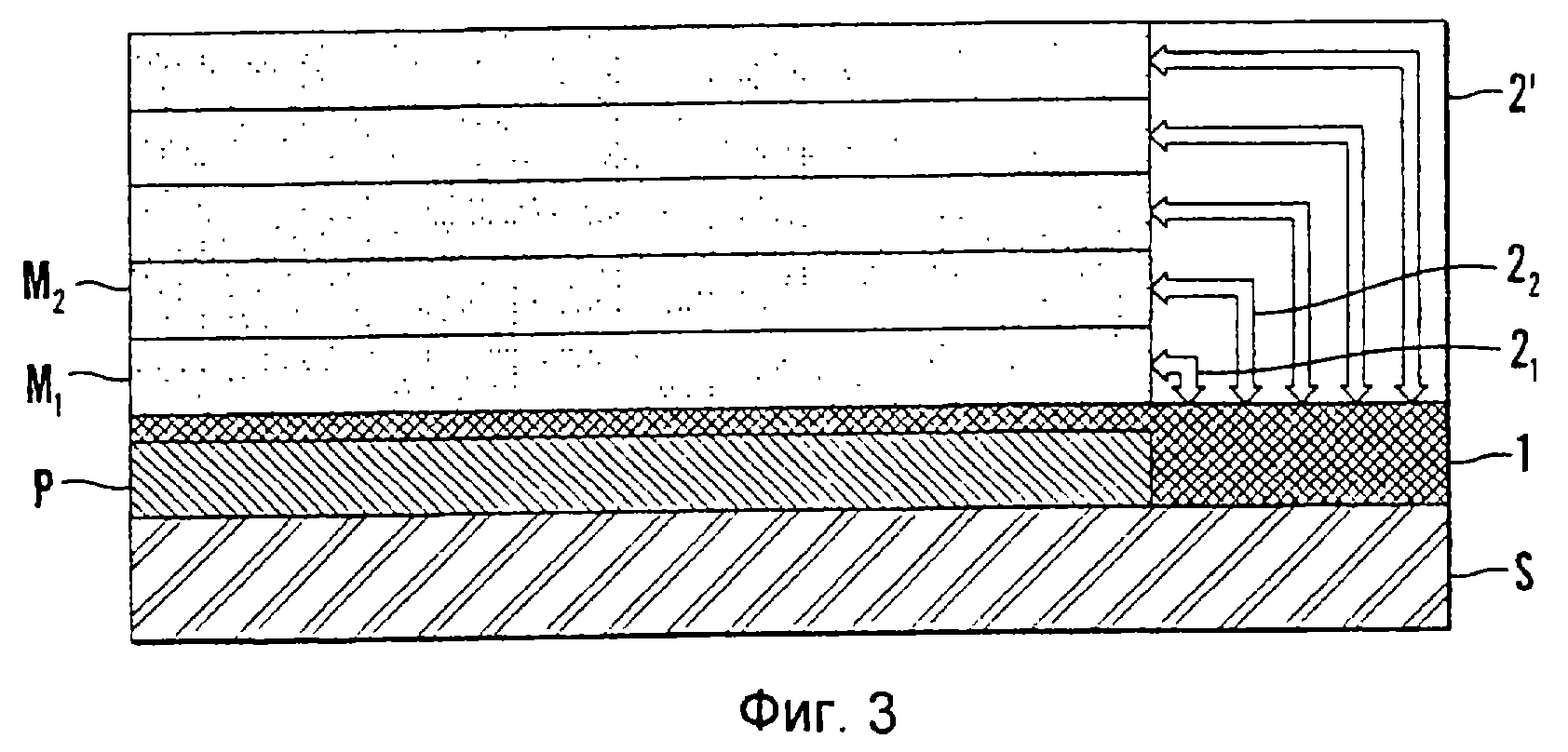

фиг. 3 схематически изображает первый вариант выполнения устройства обработки данных согласно настоящему

изобретению;

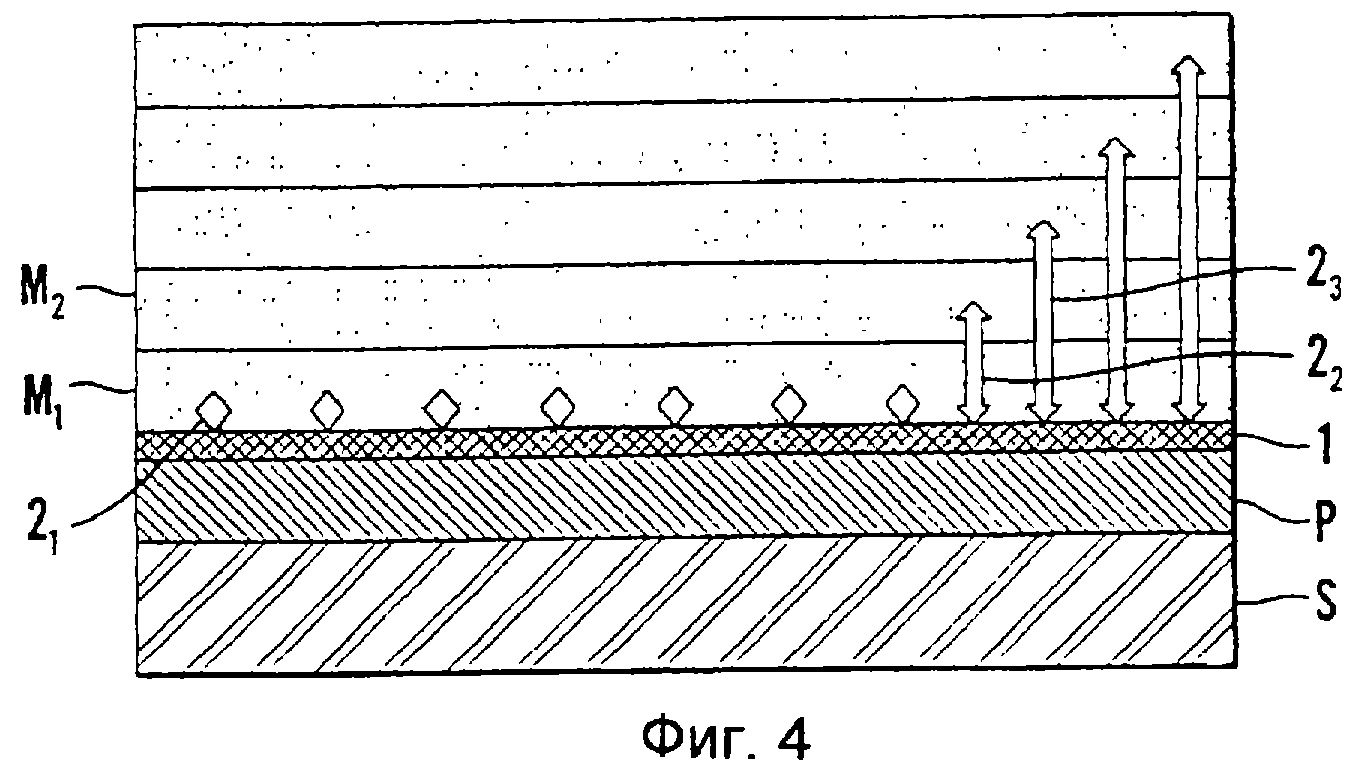

фиг. 4 схематически изображает второй вариант выполнения устройства обработки данных согласно настоящему изобретению;

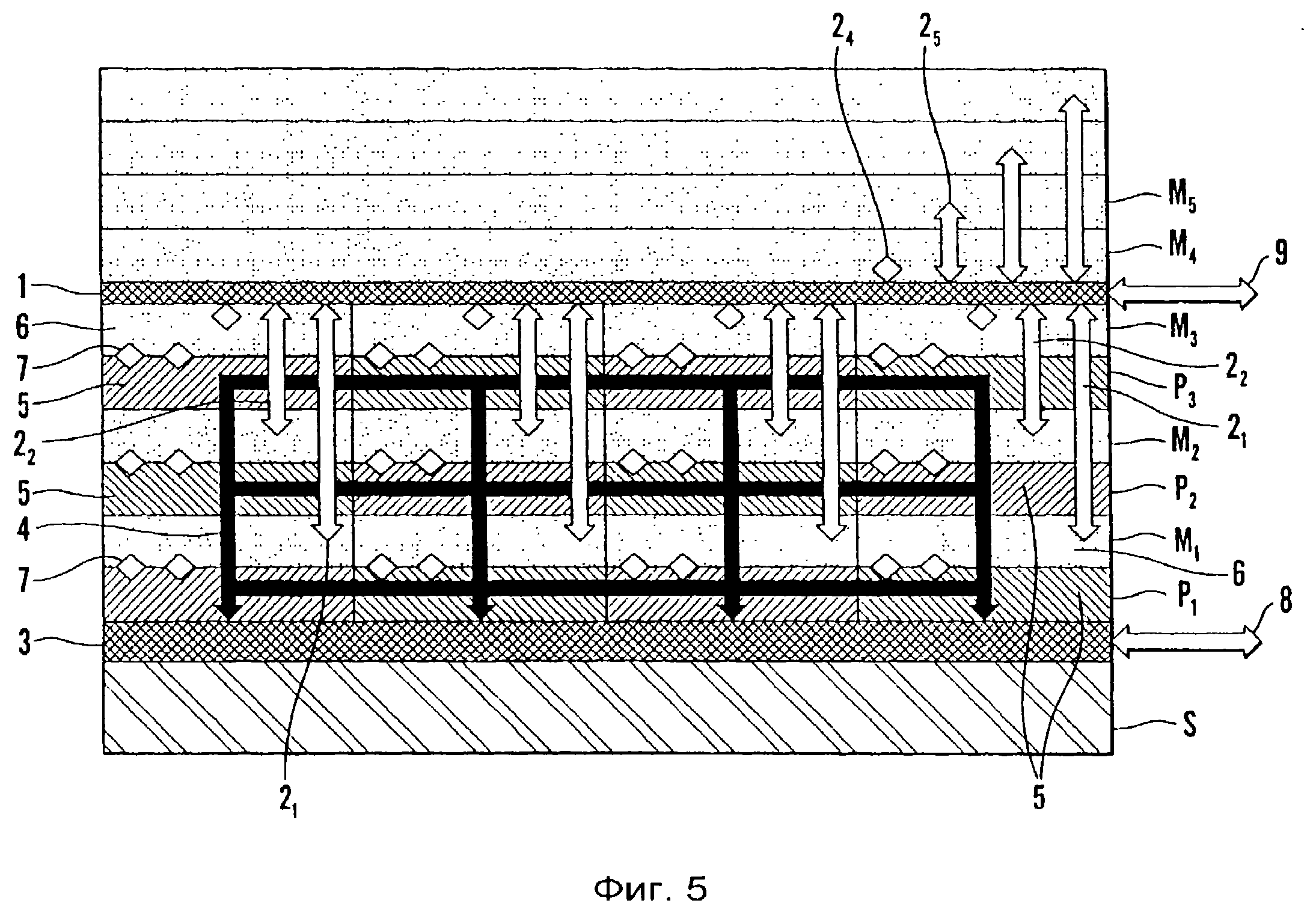

фиг. 5 схематически изображает третий вариант

выполнения устройства обработки данных согласно настоящему изобретению;

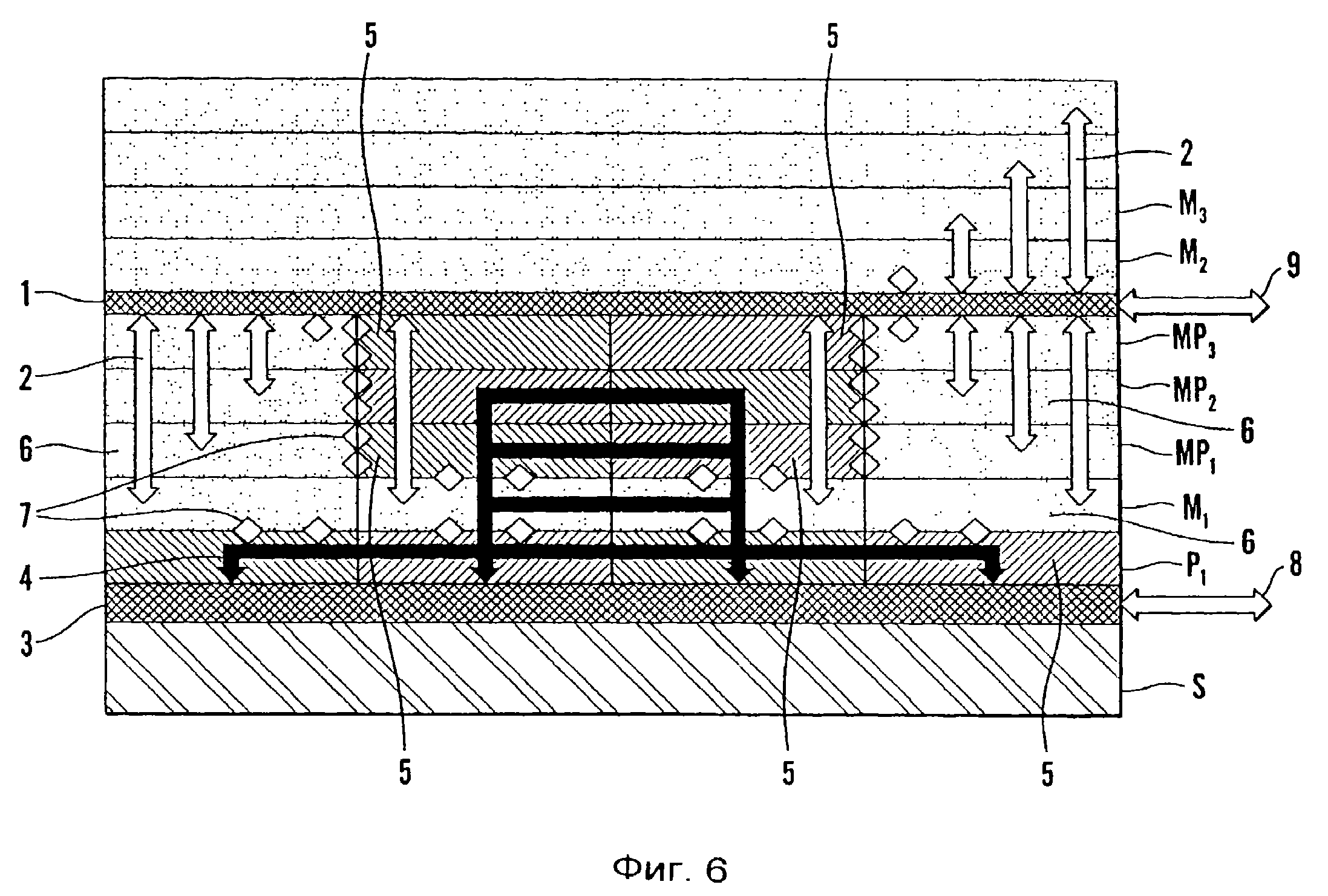

фиг. 6 схематически изображает четвертый вариант выполнения устройства обработки данных согласно настоящему изобретению;

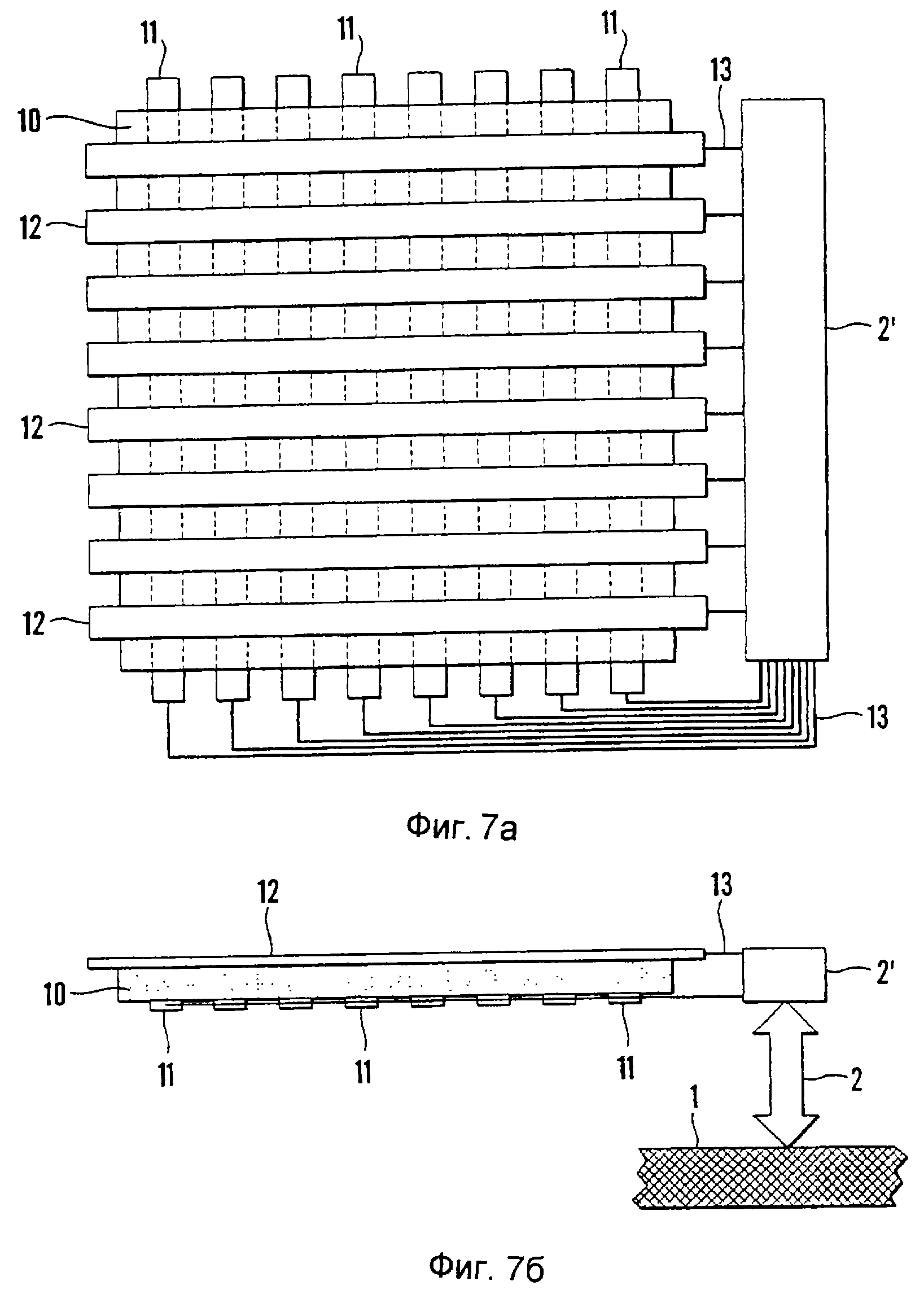

фиг. 7а, б схематически изображают соответственно на виде сверху и в разрезе блок памяти, который может использоваться в запоминающем модуле в устройстве обработки данных согласно настоящему

изобретению;

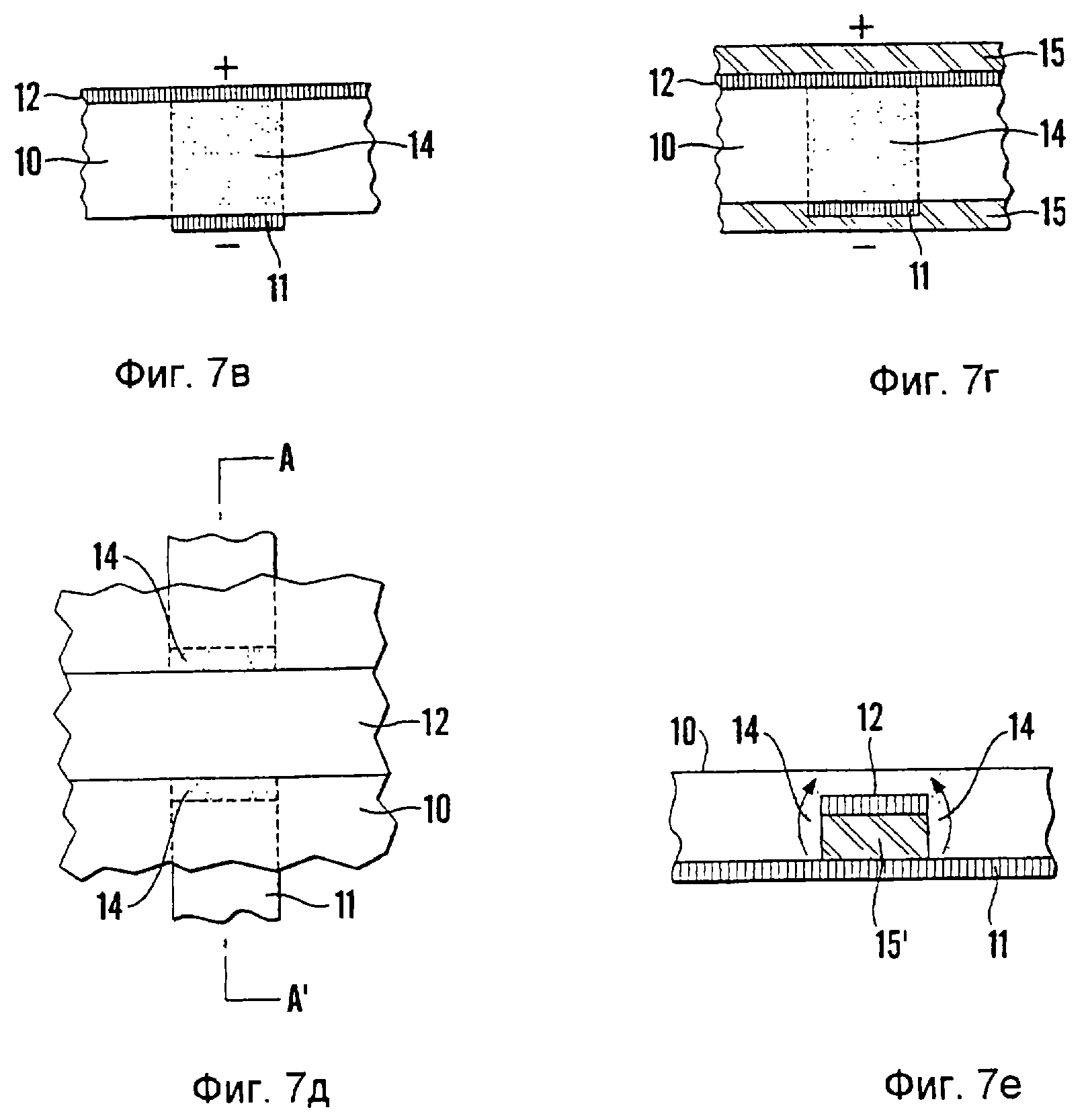

фиг. 7в, г изображают вид в разрезе первого варианта выполнения элемента памяти в блоке памяти с фиг.7а;

фиг.7д изображает вид в разрезе второго варианта выполнения

элемента памяти в блоке памяти с фиг.7а;

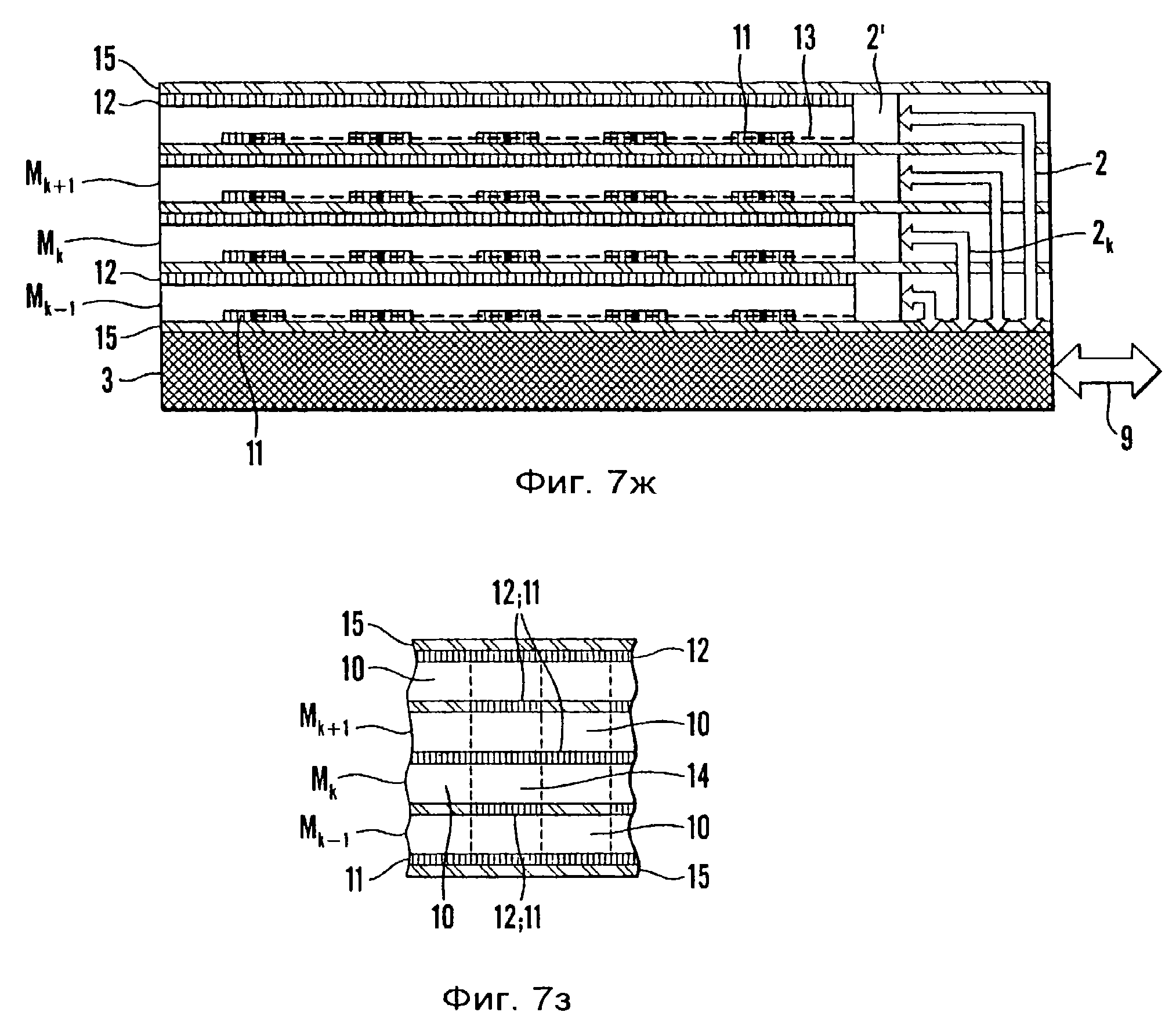

фиг.7ж изображает вид в разрезе запоминающего модуля, содержащего несколько упакованных слоев памяти;

фиг.7з подробно изображает запоминающий

модуль с фиг.7ж;

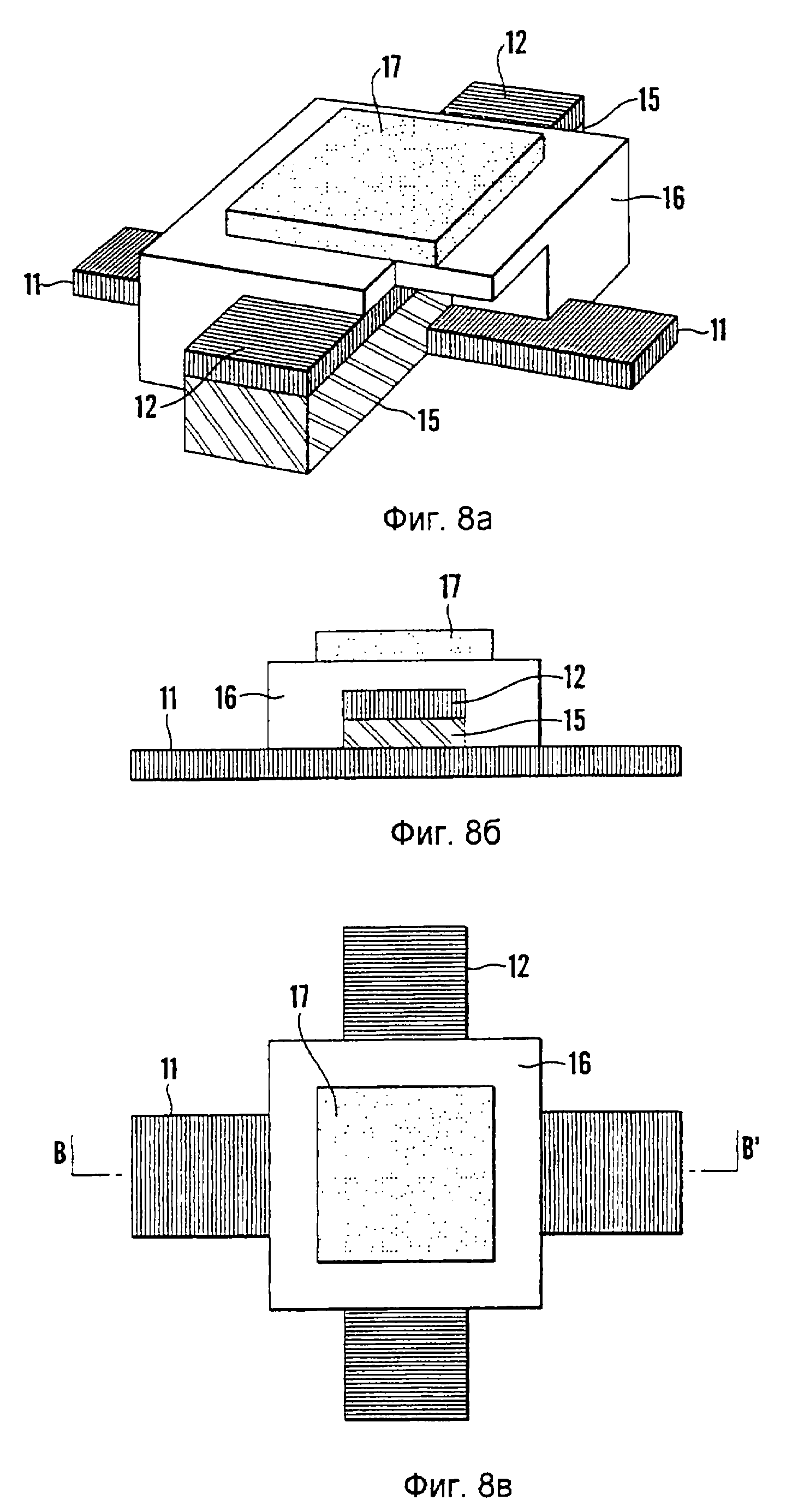

фиг. 8а, 8б, 8в изображают соответственно общий вид, вид в разрезе и вид сверху третьего варианта выполнения элемента памяти, который может использоваться в блоке памяти с

фиг.7а;

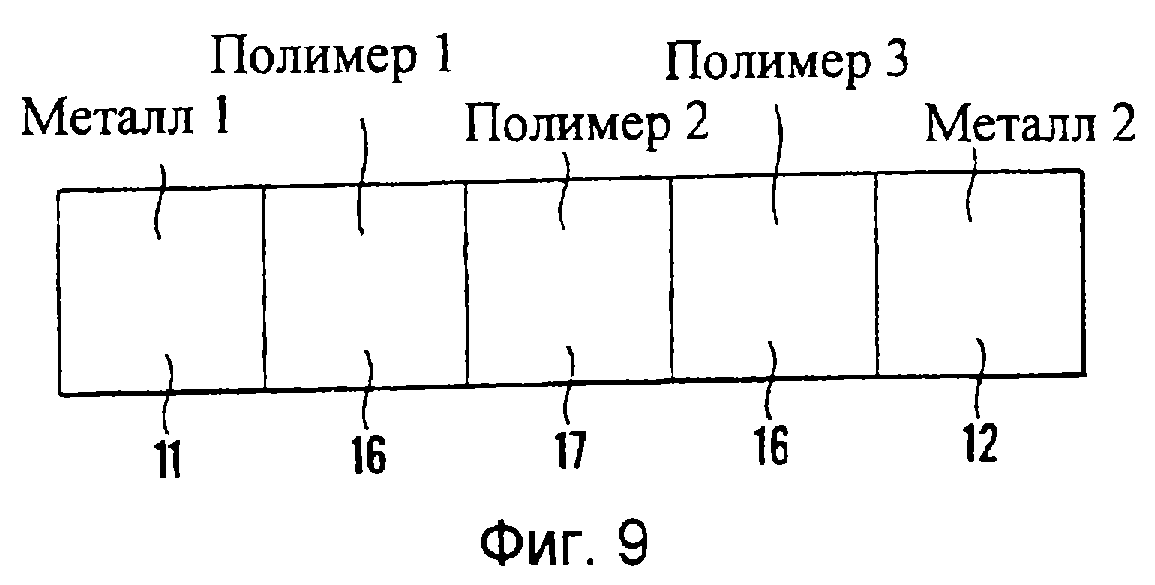

фиг. 9 - основной вариант выполнения элемента памяти, изображенного на фиг.8;

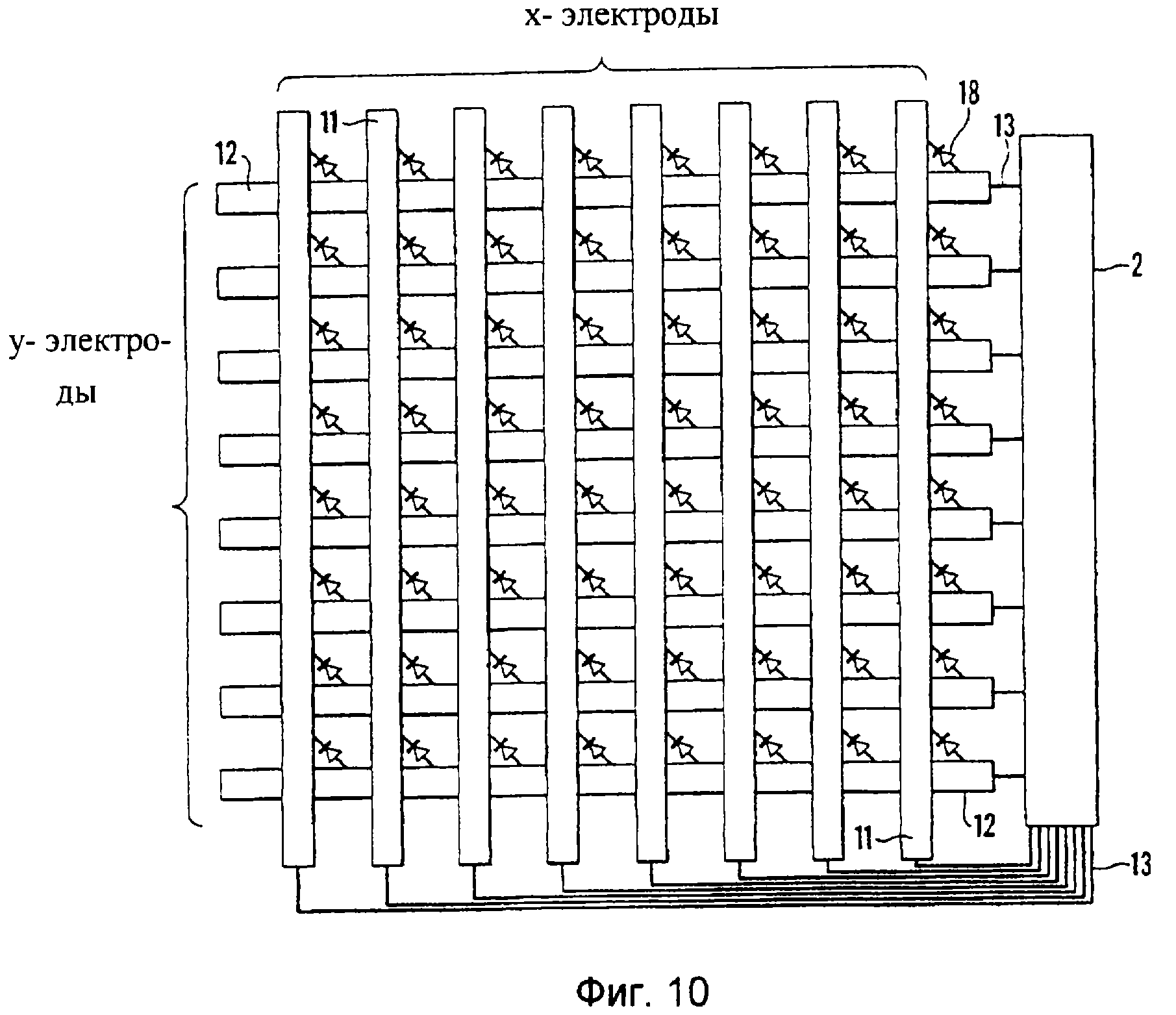

фиг. 10 схематически изображает матрицу электродов, используемую в блоке памяти с фиг.7а и с

использованием элементов памяти аналогично варианту выполнения, изображенному на фиг.8;

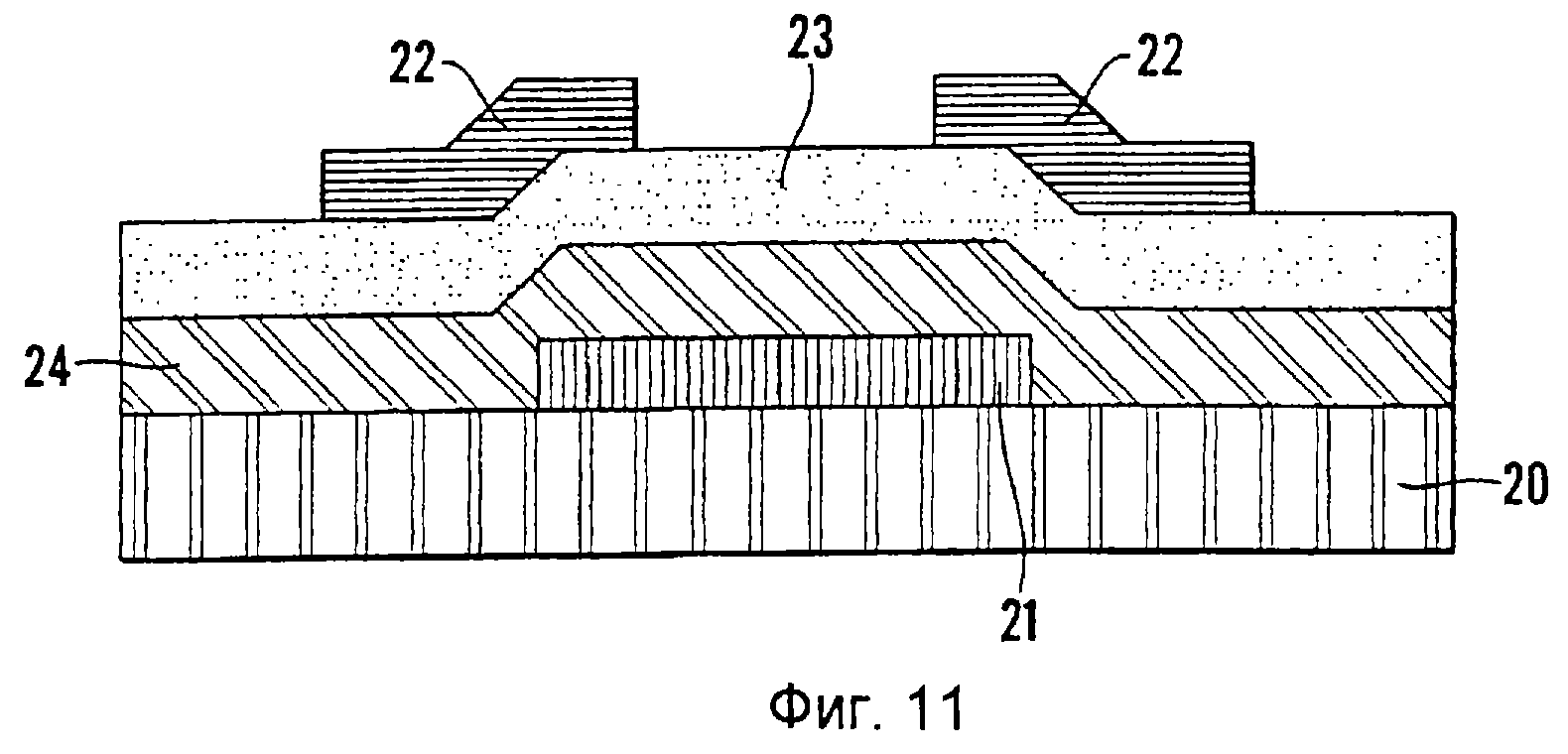

фиг.11 изображает первый полевой транзистор (FET), который может использоваться в устройстве обработки

данных согласно настоящему изобретению;

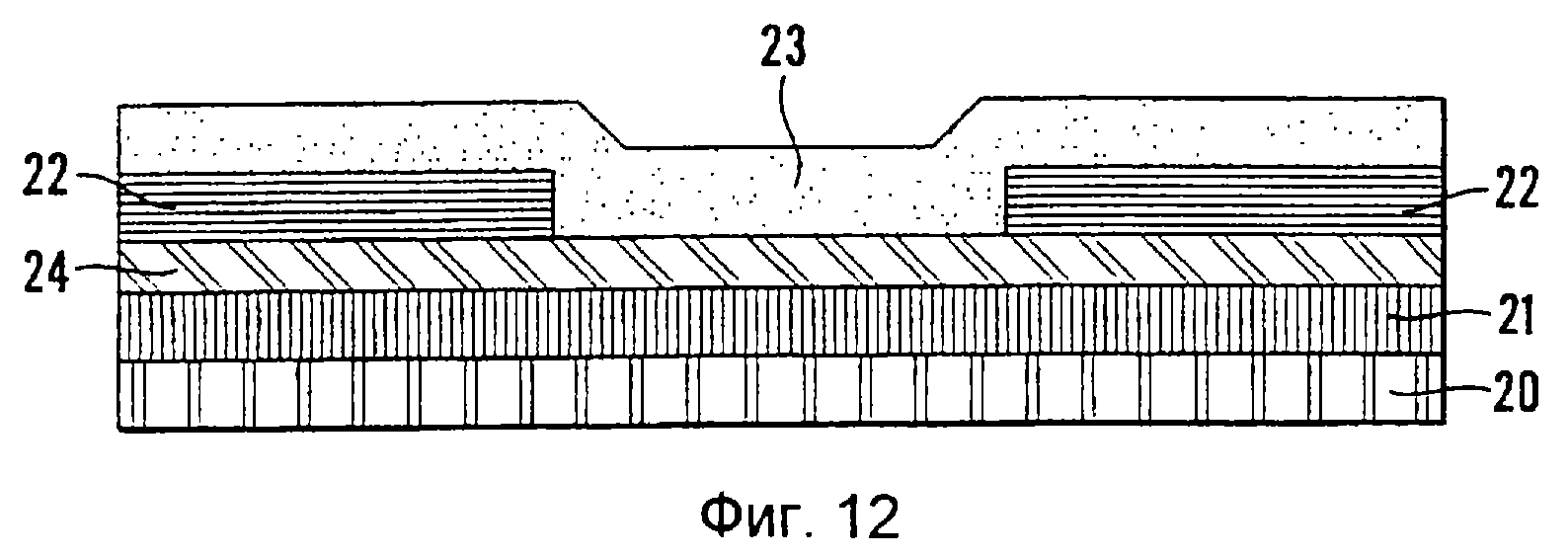

фиг. 12 изображает второй полевой транзистор, который может использоваться в устройстве обработки данных согласно настоящему изобретению;

фиг.

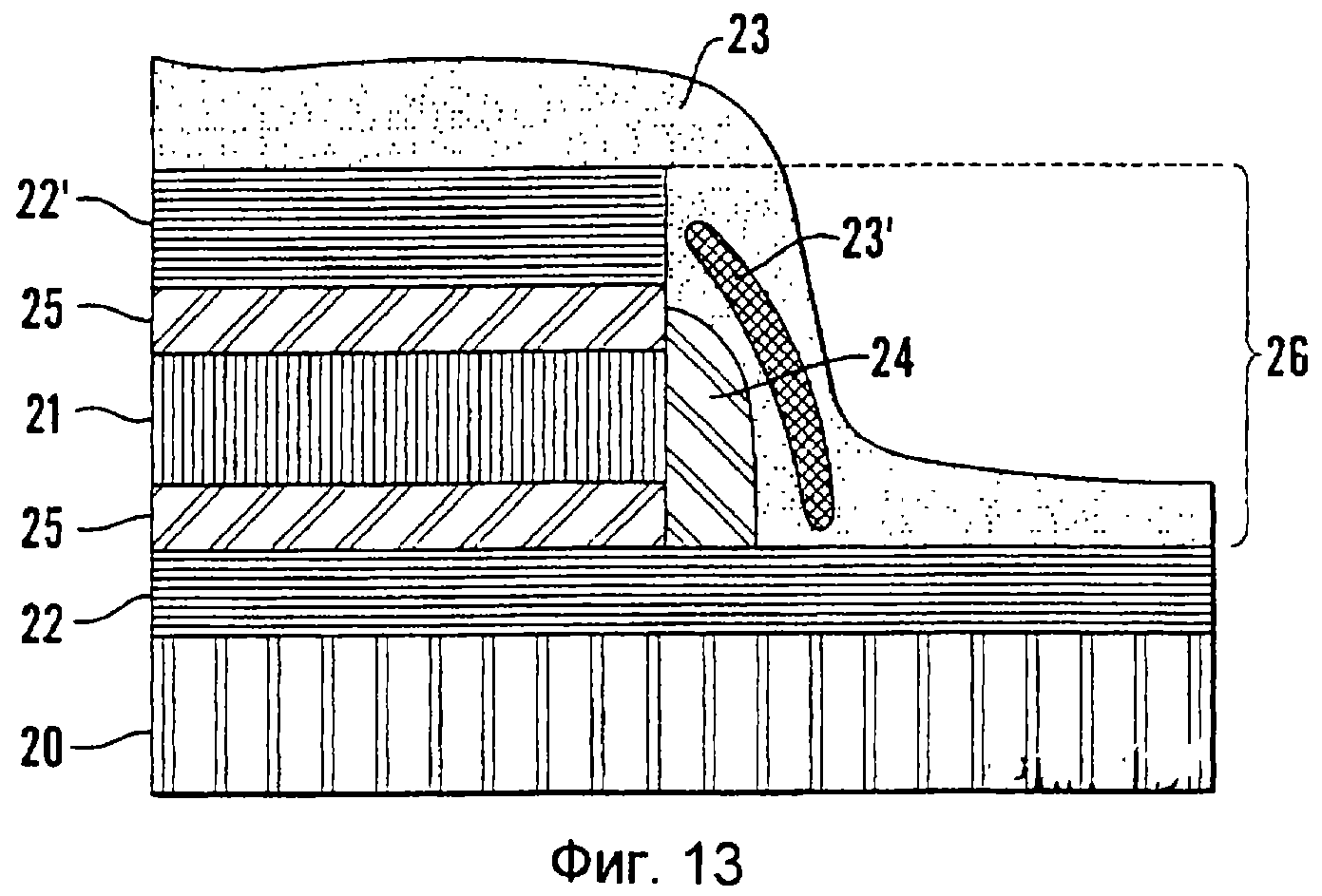

13 изображает третий полевой транзистор, который может использоваться в устройстве обработки данных согласно настоящему изобретению;

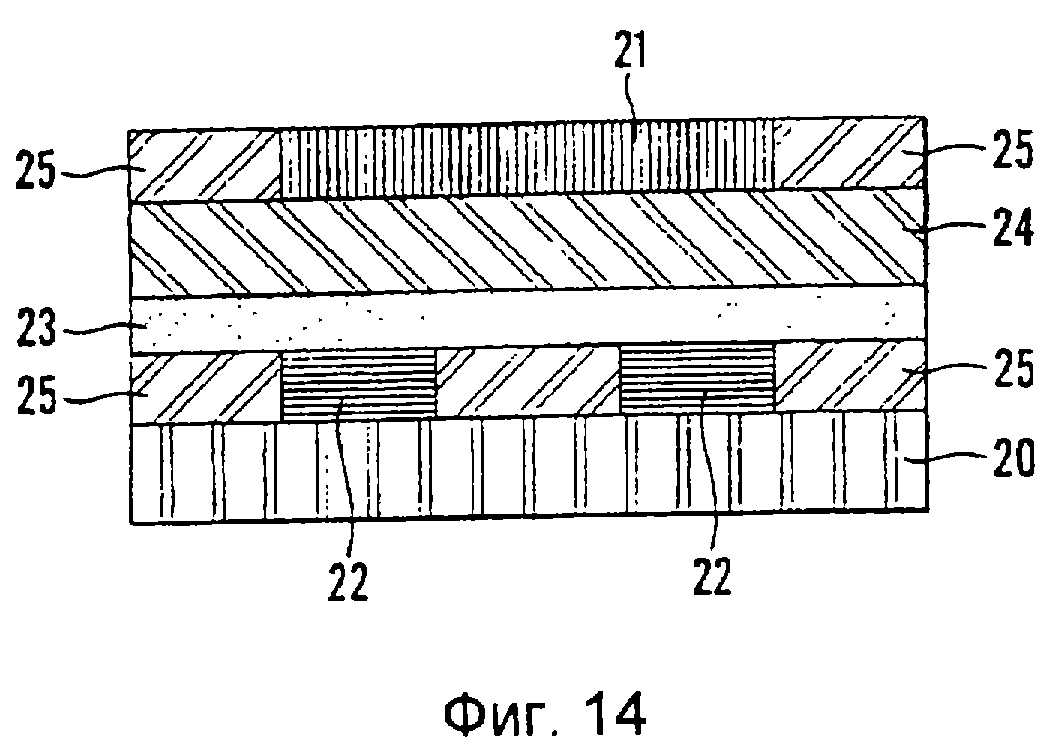

фиг. 14 изображает четвертый полевой транзистор, который

может использоваться в устройстве обработки данных согласно настоящему изобретению;

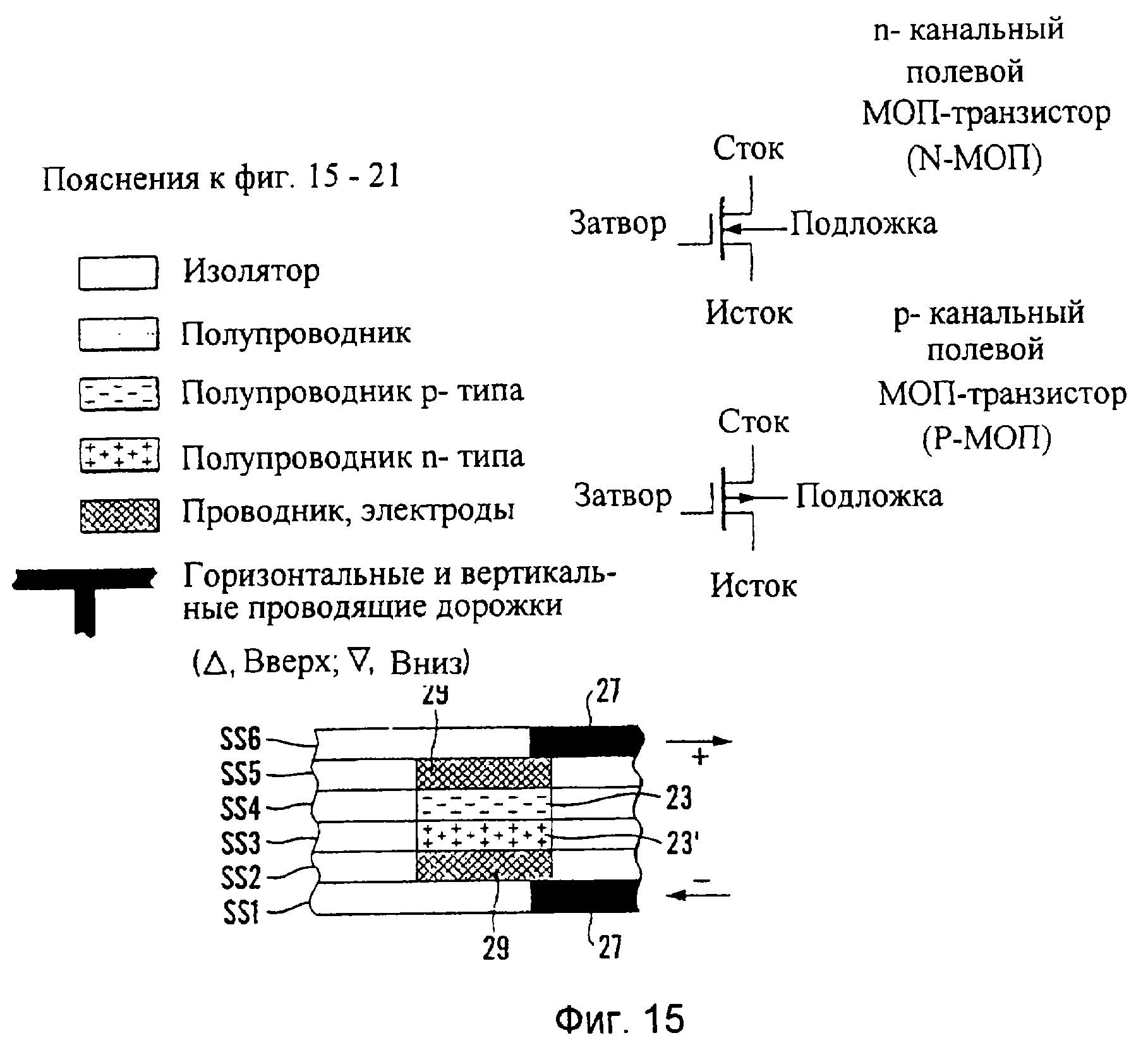

фиг. 15 схематически изображает вид в разрезе диодной структуры, которая создана посредством изменения

состояния материала слоя и которая может использоваться в устройстве обработки данных согласно настоящему изобретению;

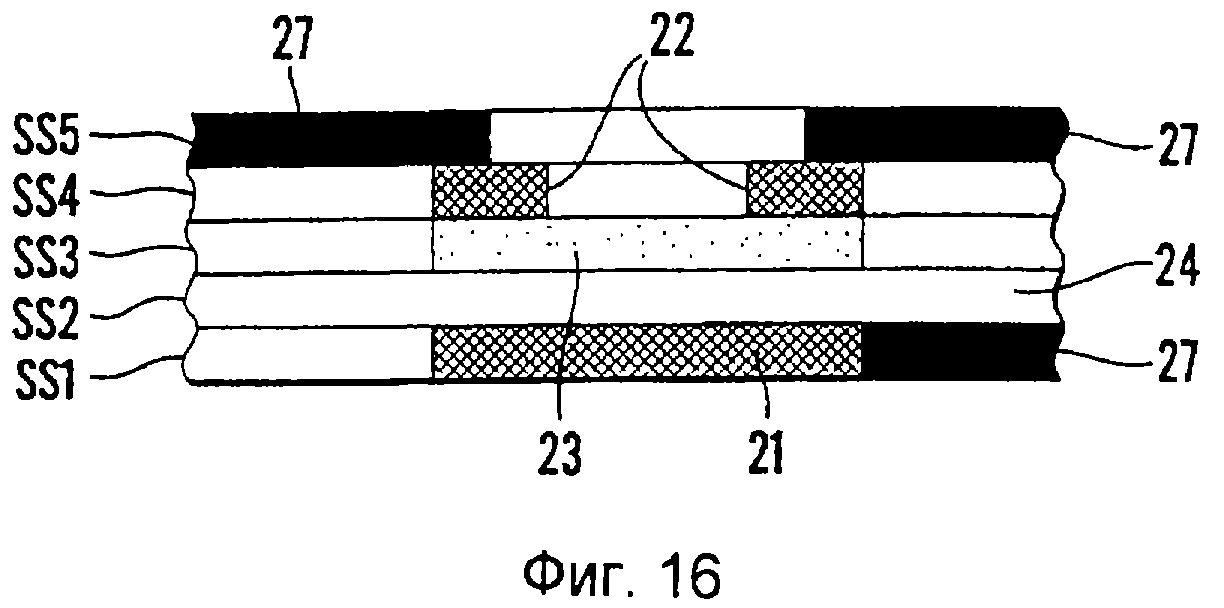

фиг. 16 схематически изображает вид в разрезе структуры полевого

МОП-транзистора (MOSFET), которая создана посредством изменения состояния материала слоя и которая может использоваться в устройстве обработки данных согласно настоящему изобретению;

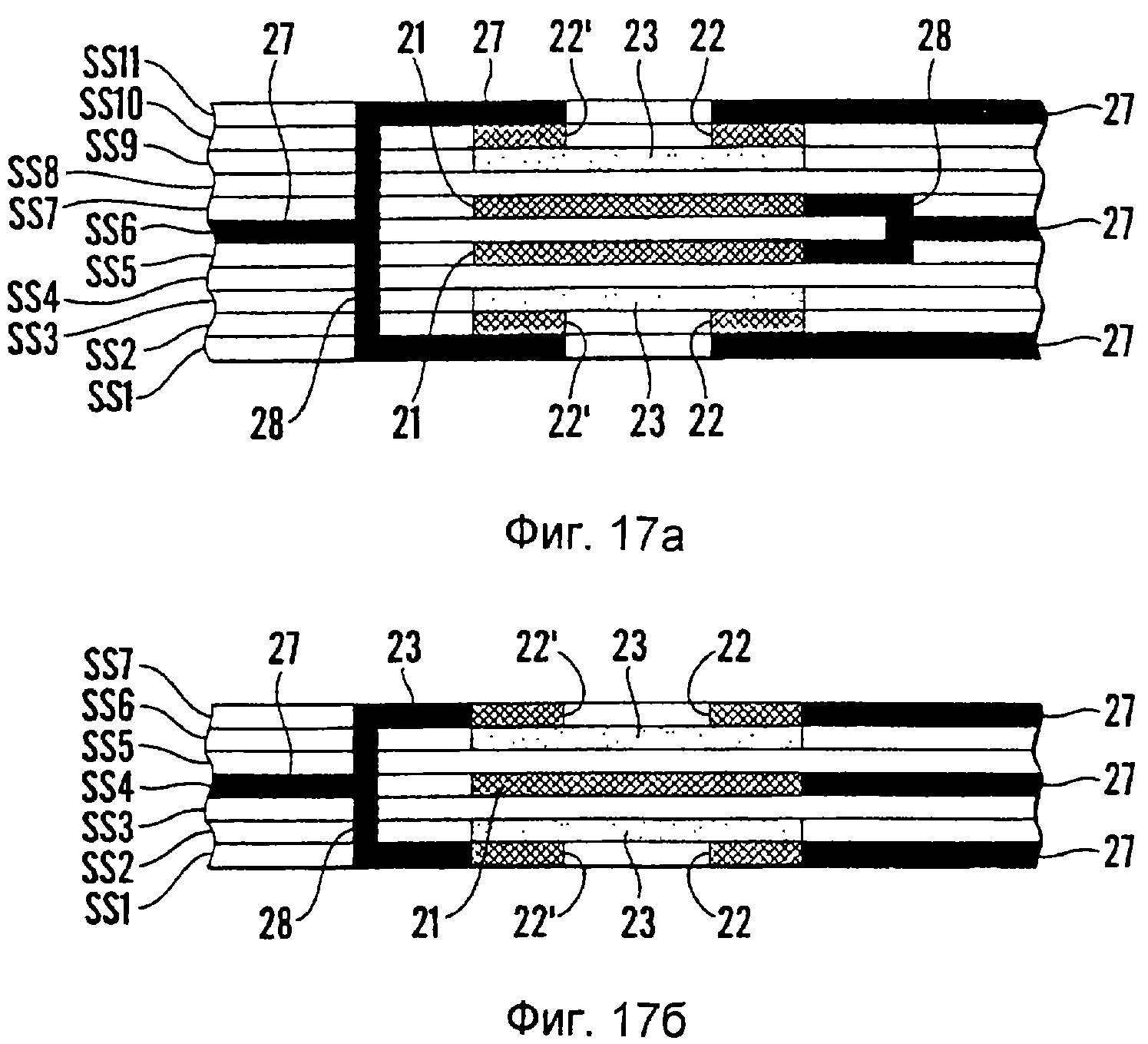

фиг. 17а

схематически изображает вид в разрезе структуры логического инвертора, которая использует структуру полевого МОП-транзистора (MOSFET), изображенного на фиг.16, и которая может использоваться в

устройстве обработки данных согласно настоящему изобретению;

фиг. 17б схематически изображает вид в разрезе варианта выполнения структуры инвертора с фиг.17а;

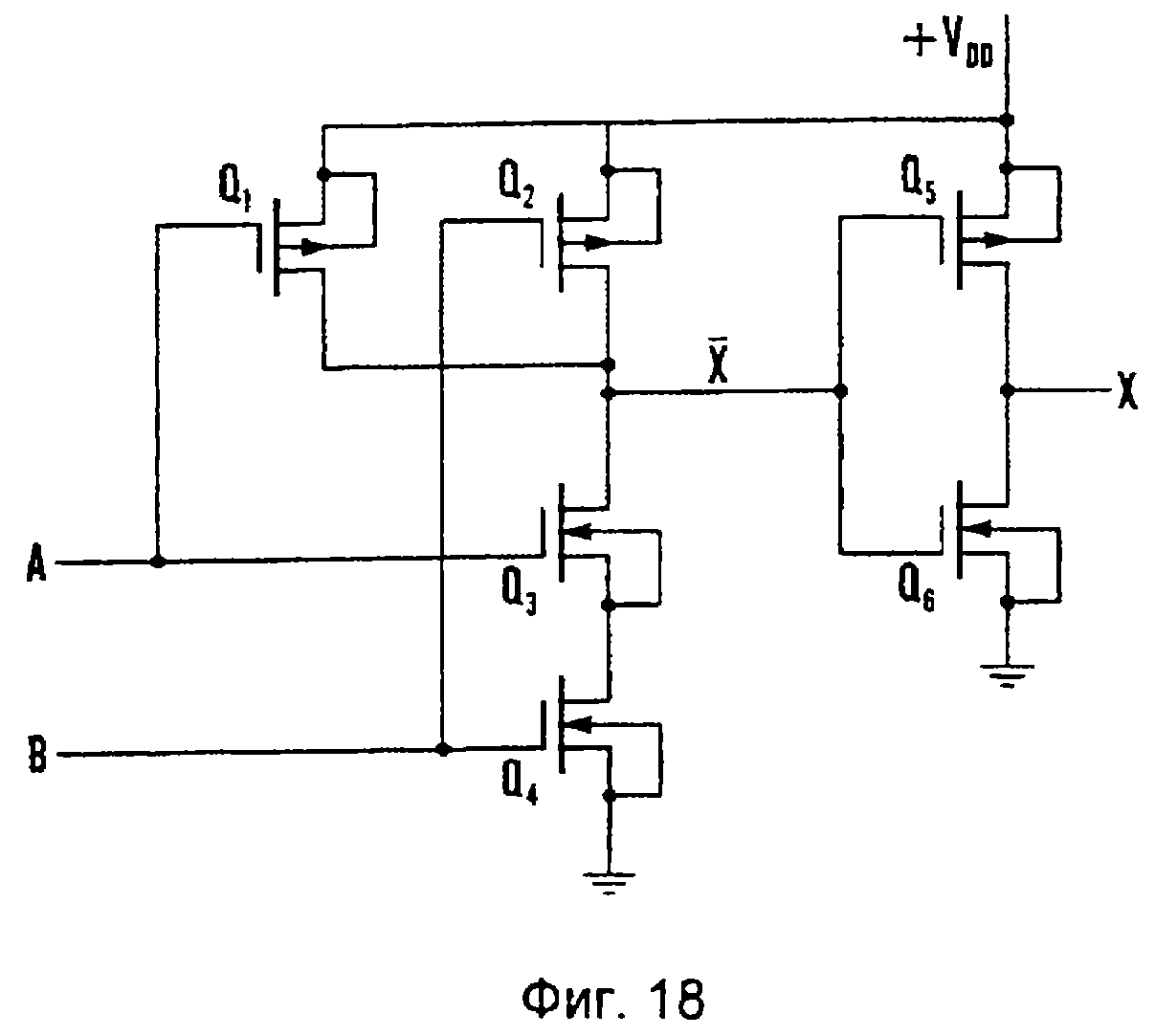

фиг. 18 изображает

эквивалентную схему логического элемента И, реализованного по КМОП (КМОП) технологии;

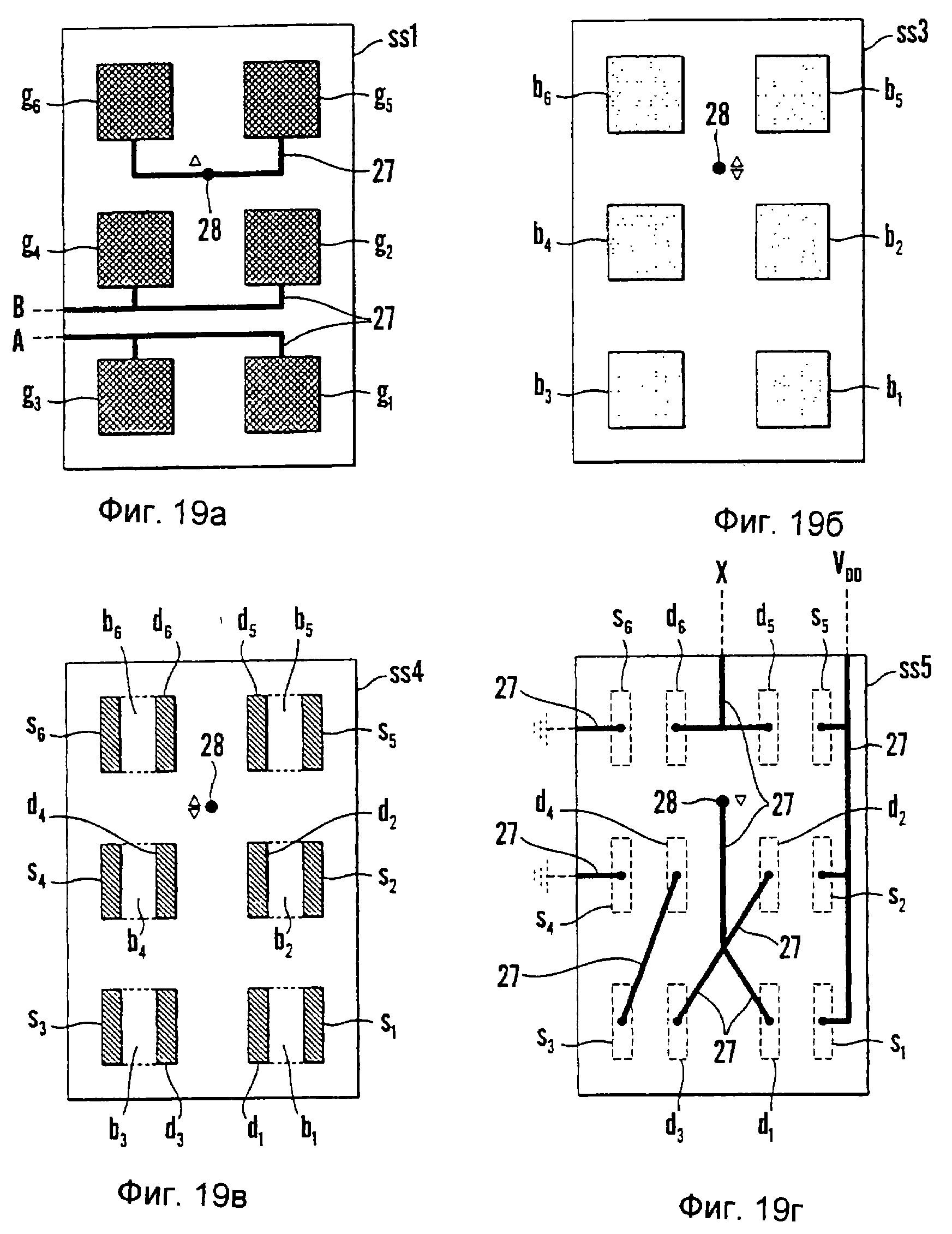

фиг. 19а-г изображает вид сверху подслоев в структуре логического элемента И, реализованного по

тонкопленочной технологии и согласно эквивалентной схеме с фиг.18, с использованием структур полевого МОП-транзистора (MOSFET), аналогичных приведенных на фиг.16;

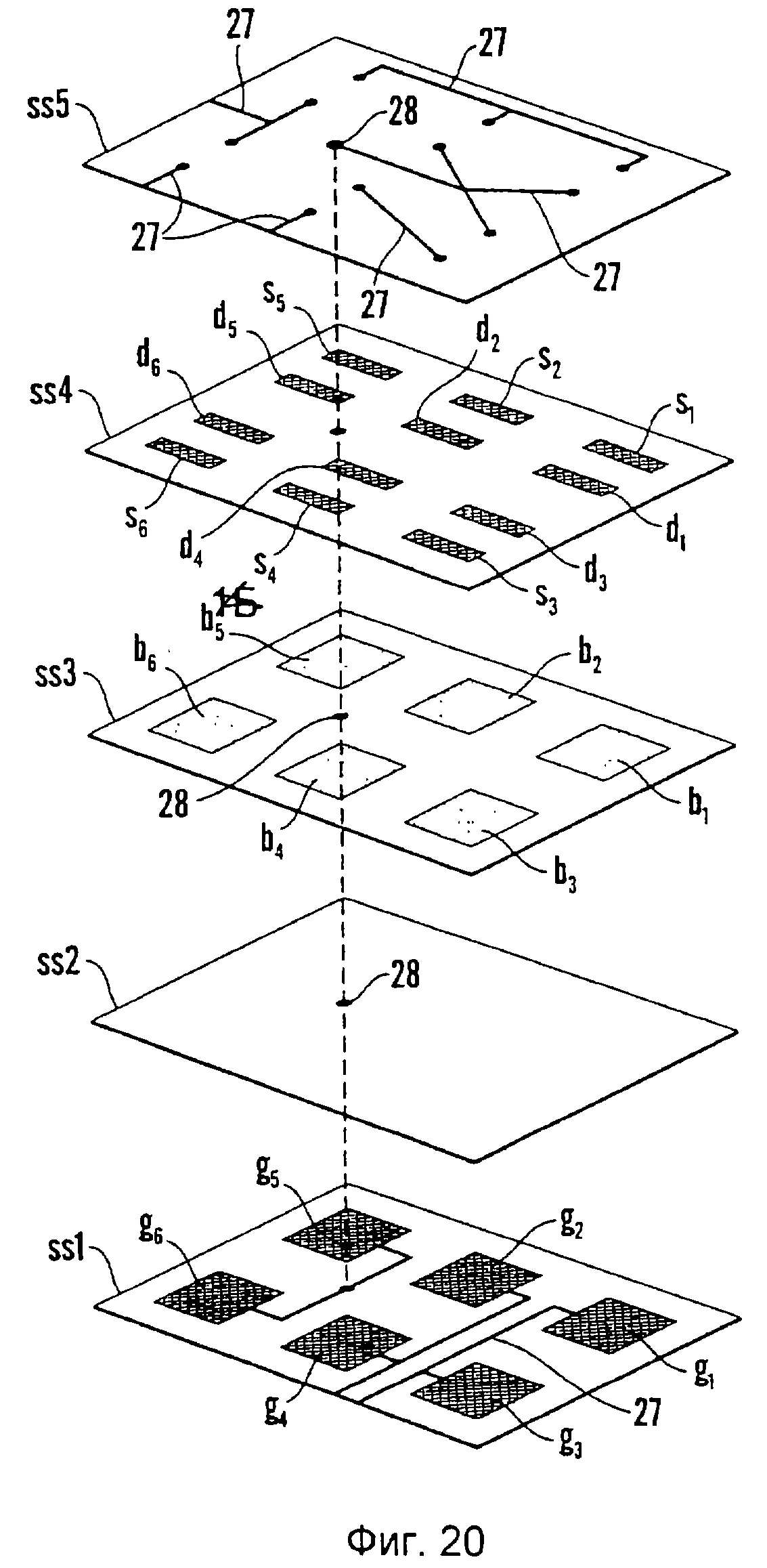

фиг. 20 изображает уложенную

структуру логического элемента И с фиг.19, но разделенную по отдельным подслоям;

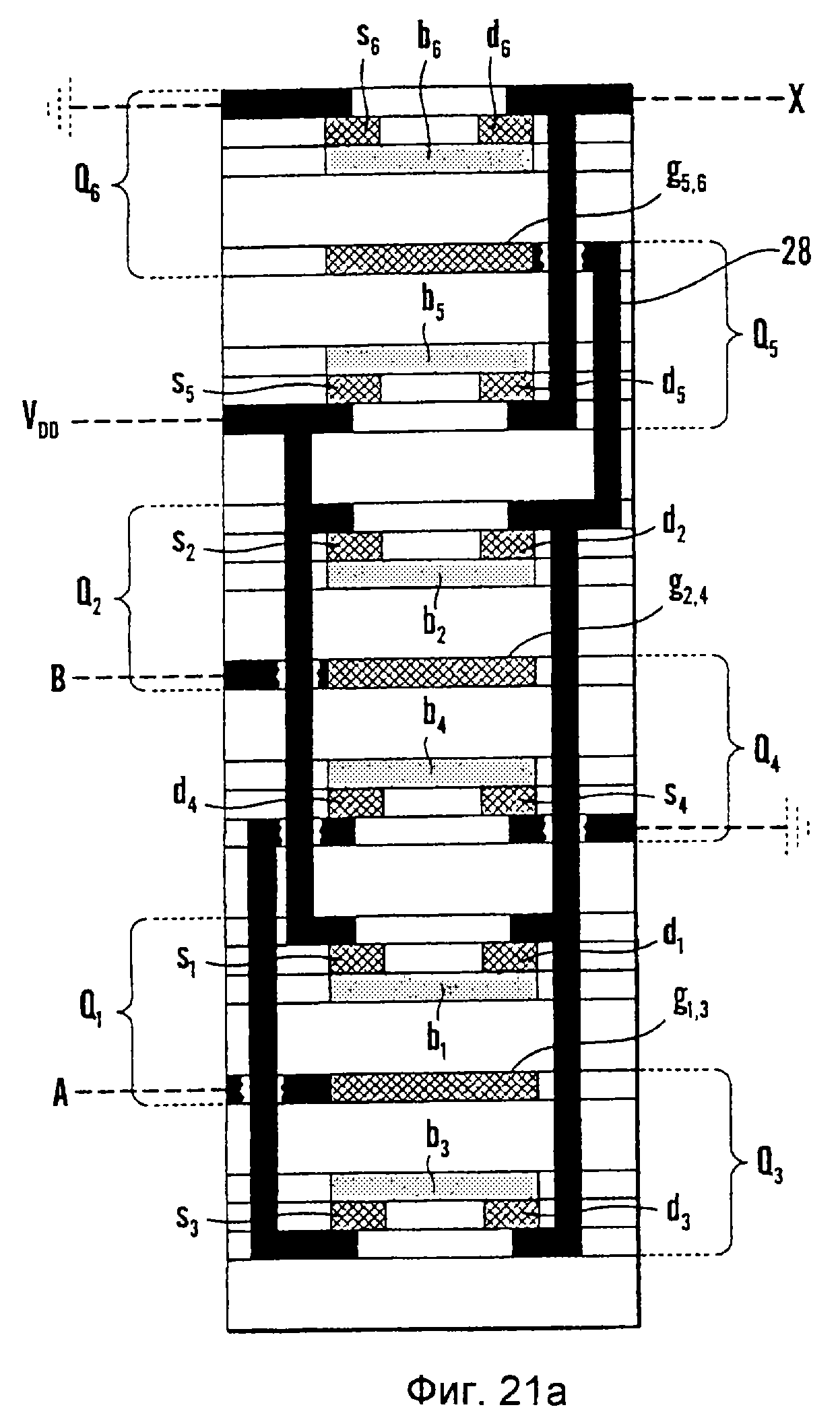

фиг. 21а схематически изображает другой вариант выполнения структур логического элемента И, изображенного на

фиг.20, в котором отдельные структуры полевого МОП-транзистора (MOSFET) формируются друг над другом с вертикальной конфигурацией и соединяются между собой с помощью общего электрода логического

элемента;

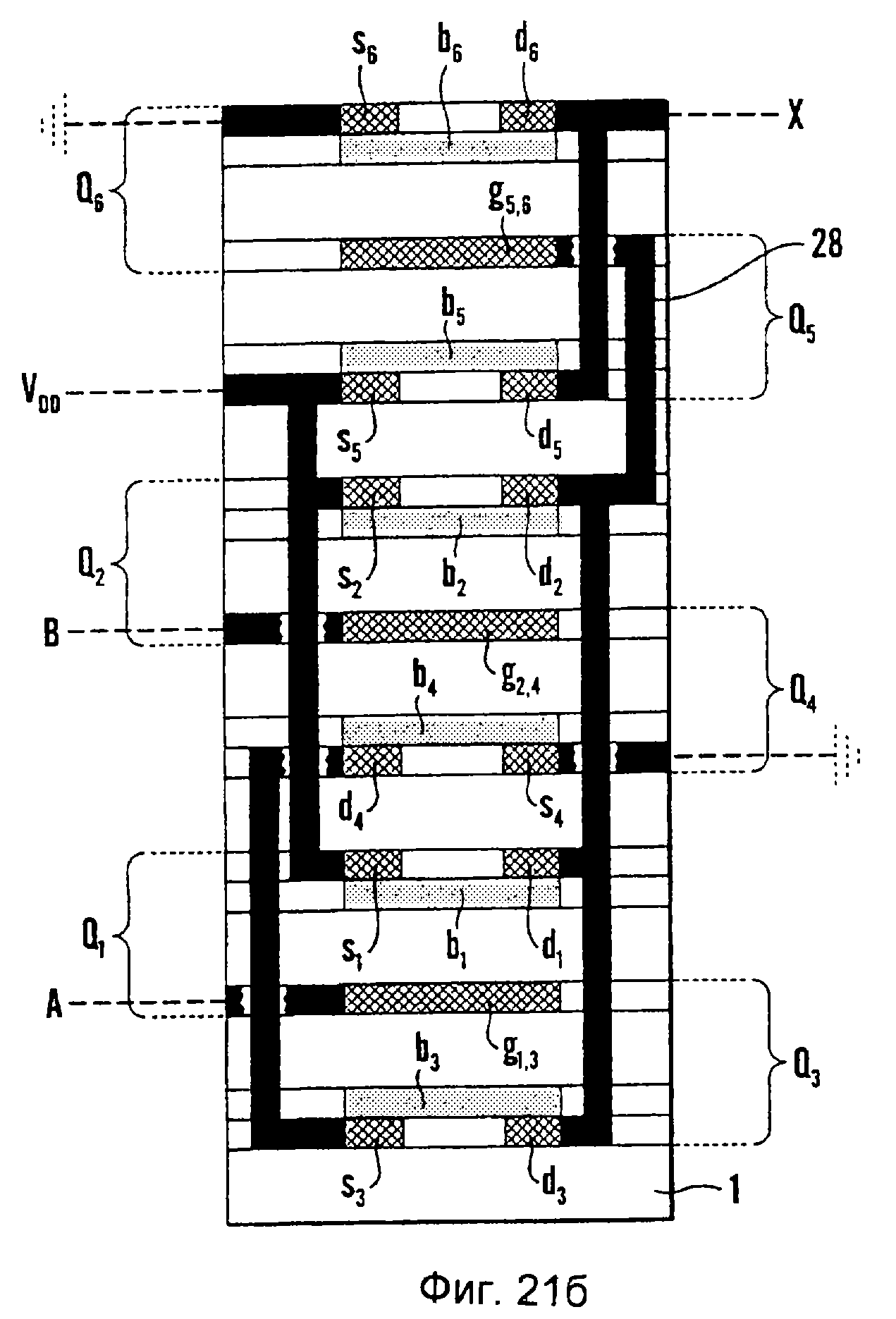

фиг. 21б схематически изображает упрощенный вариант выполнения согласно фиг.21а;

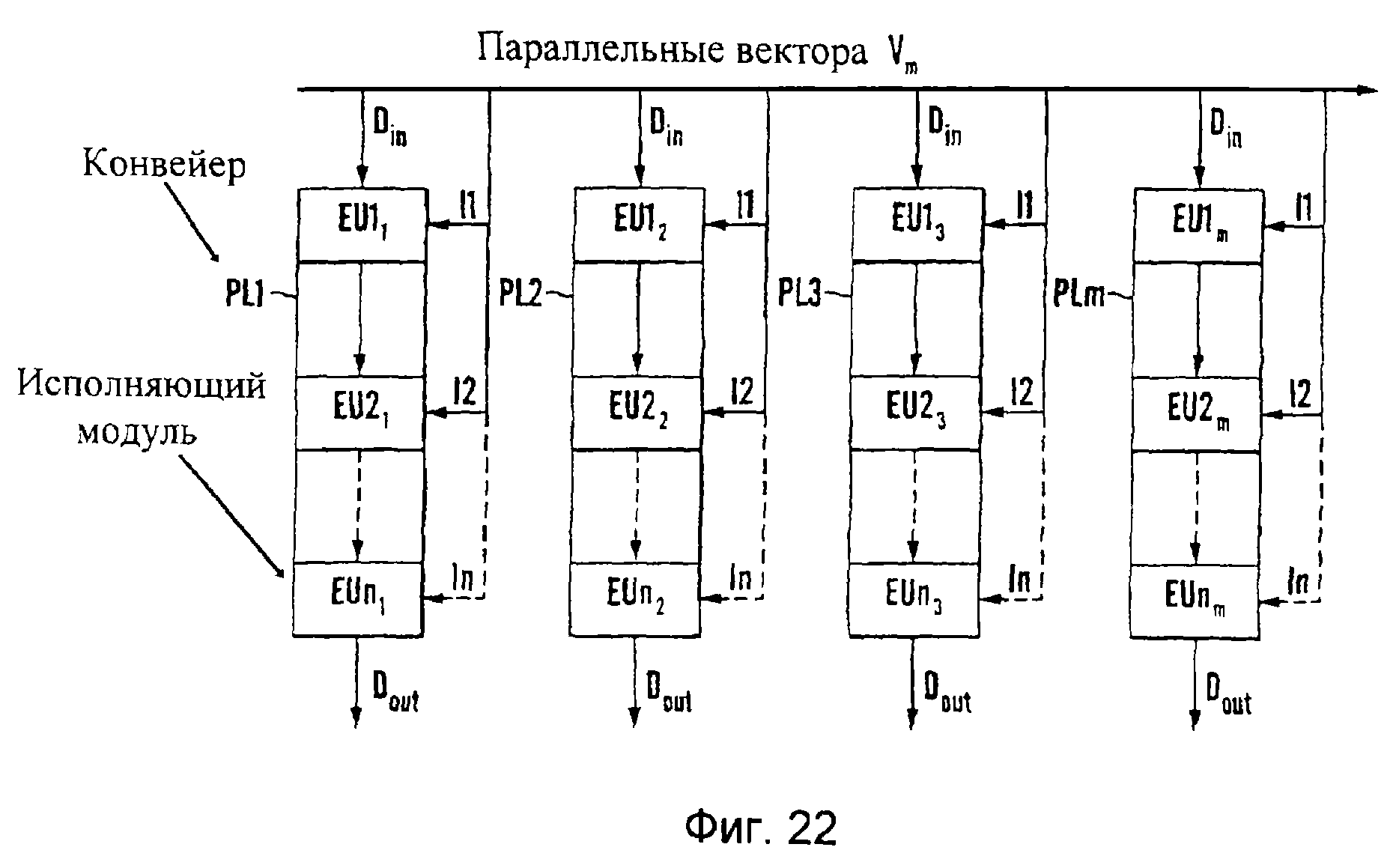

фиг. 22 схематически изображает архитектуру процессора, которая объединяет параллелизм

данных и функциональный параллелизм и которая может использоваться в устройстве обработки данных согласно настоящему изобретению;

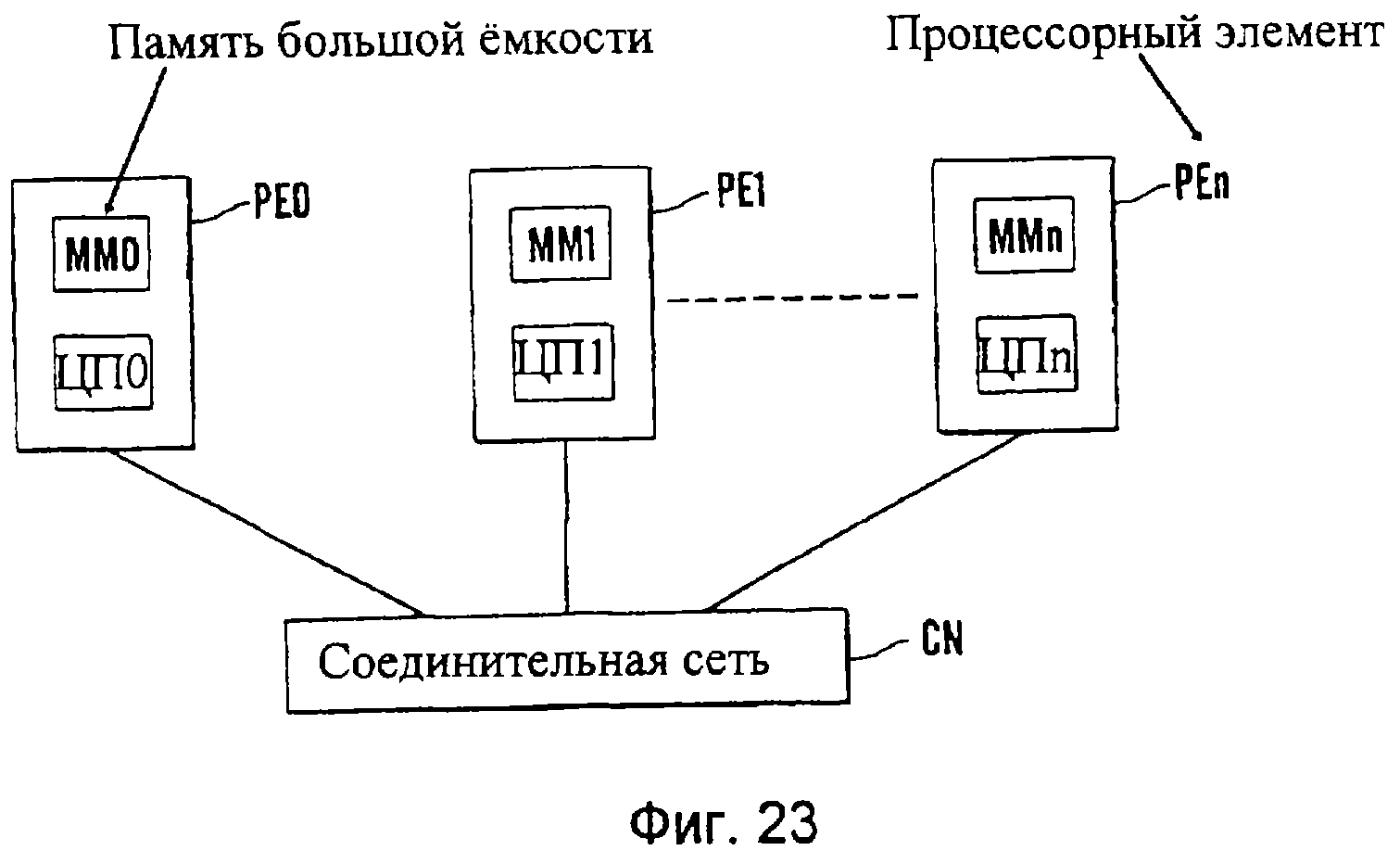

фиг. 23 схематически изображает принцип архитектуры "много

инструкций - много потоков данных" (MIMD) с системой распределенной памяти;

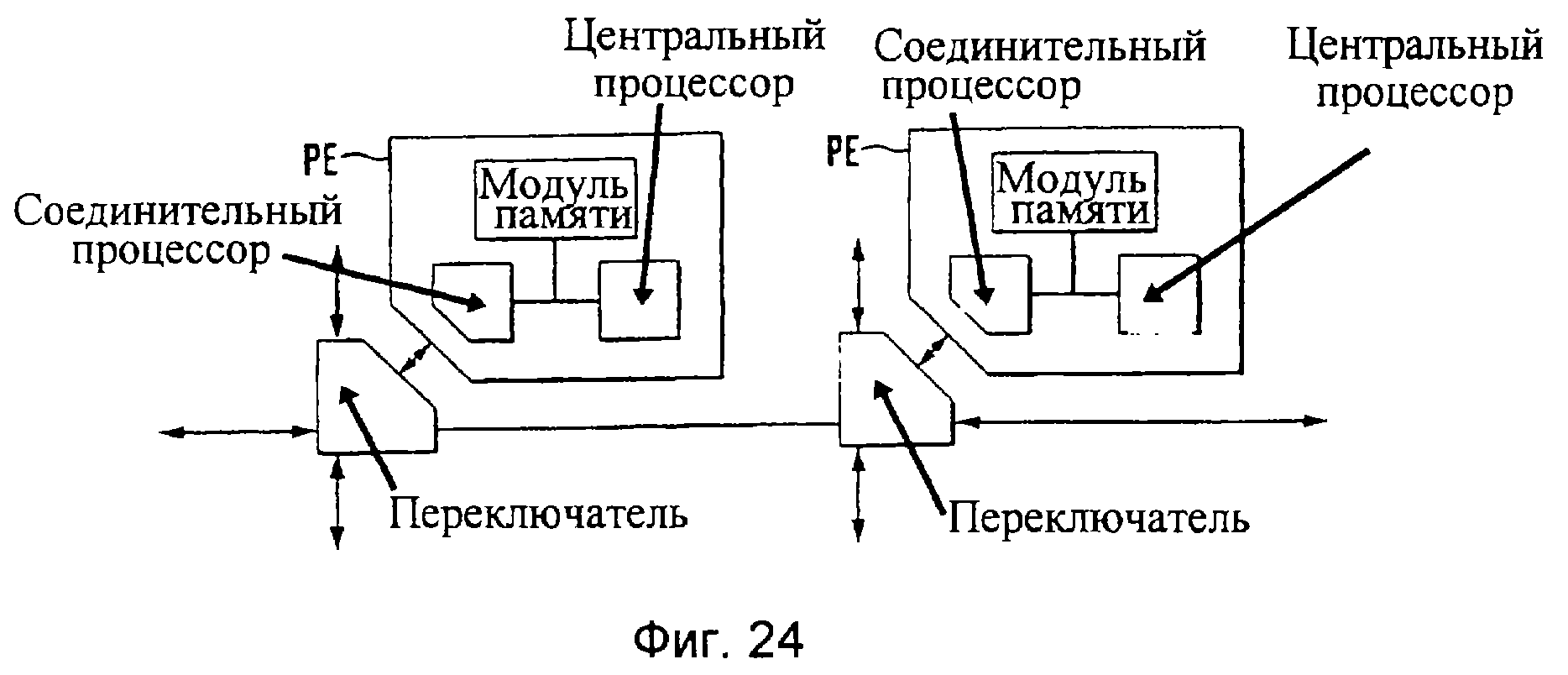

фиг.24 схематически изображает более практический вариант воплощения архитектуры "много инструкций - много потоков

данных" (MIMD) согласно фиг.23;

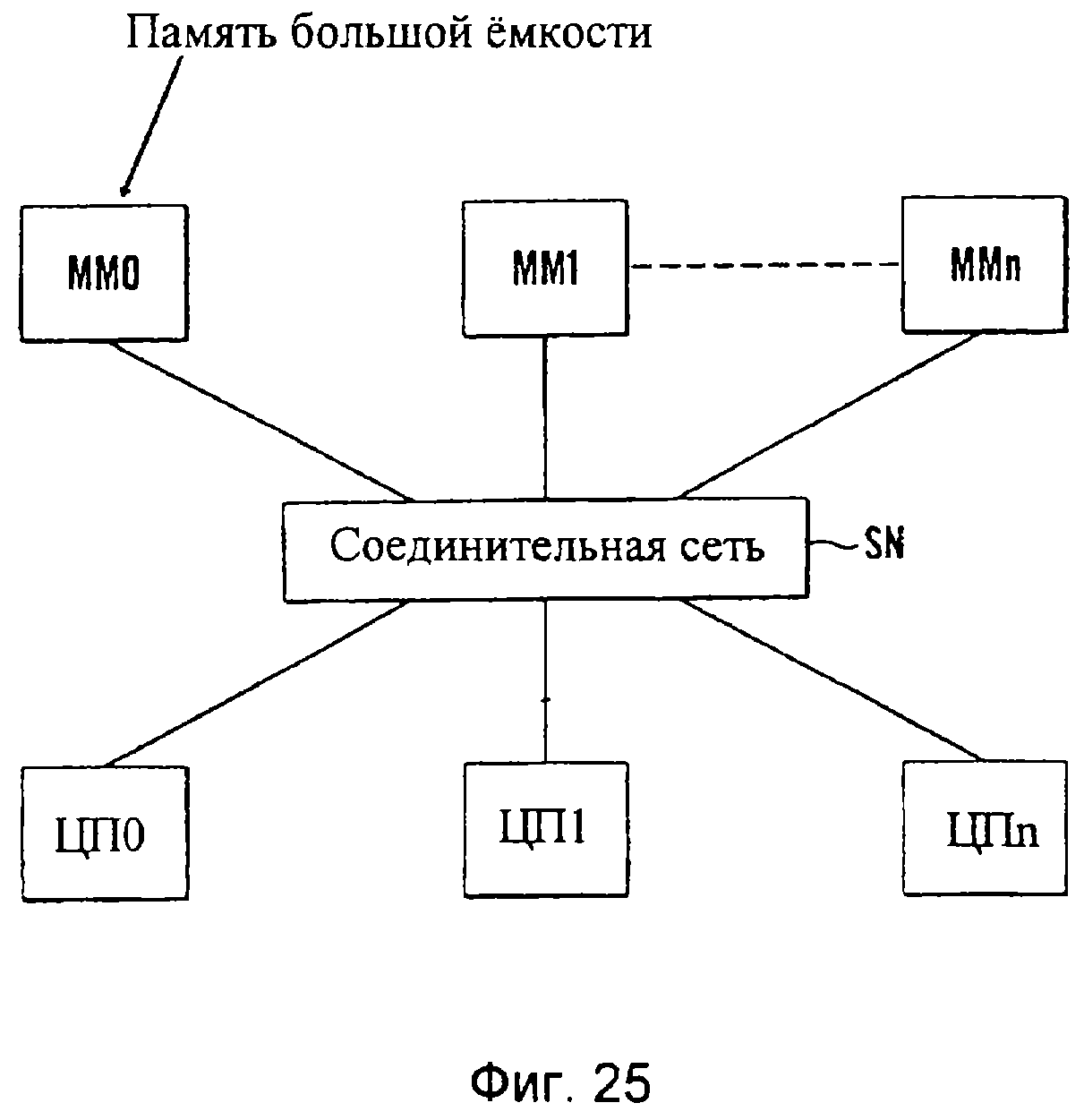

фиг. 25 схематически изображает принцип архитектуры "много инструкций - много потоков данных" (MIMD) с системой совместно используемой памяти;

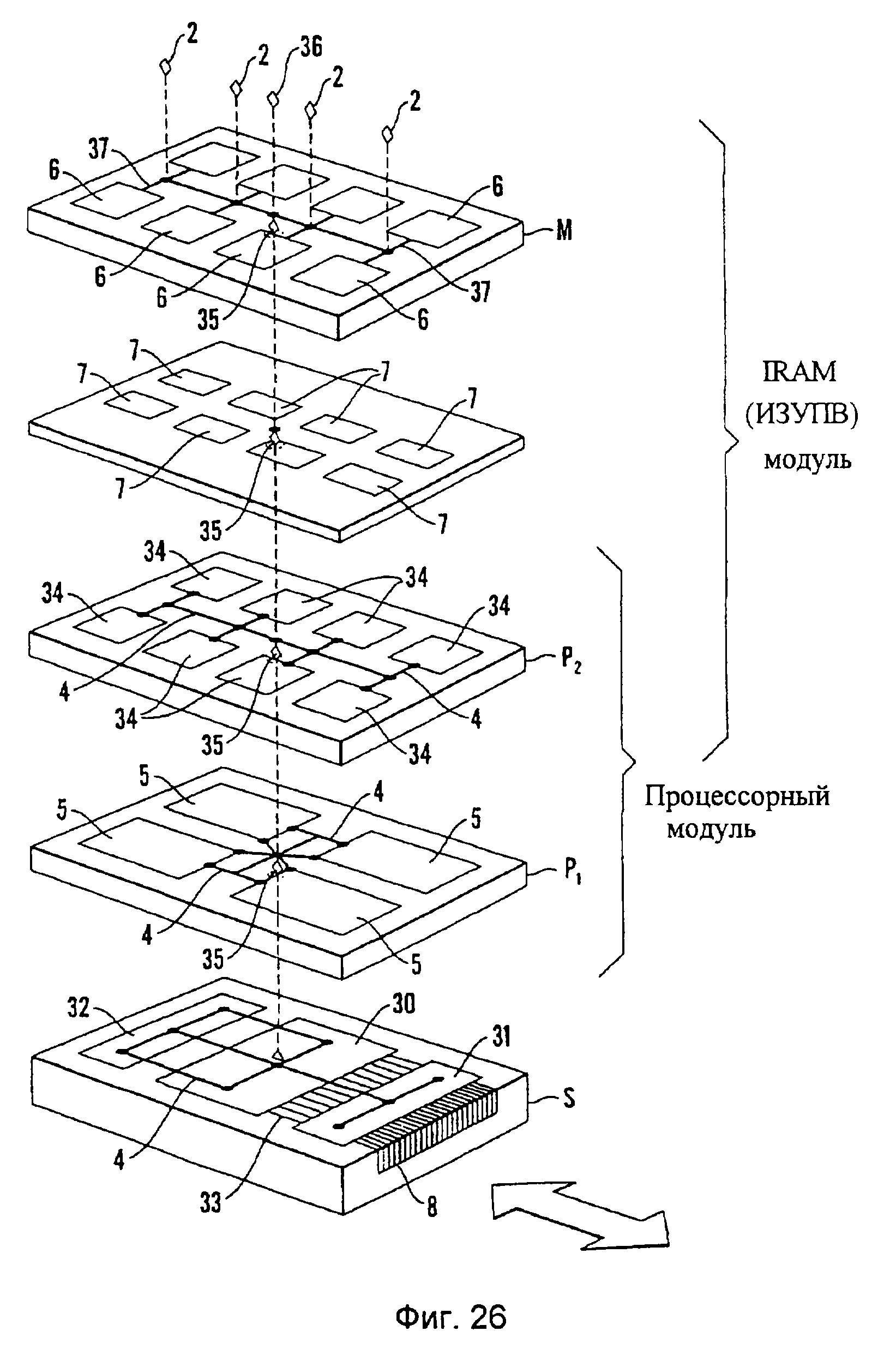

фиг. 26

изображает, каким образом архитектура "много инструкций - много потоков данных" (MIMD) согласно фиг.25 может быть реализована в устройстве обработки данных согласно настоящему изобретению.

Лучший вариант осуществления изобретения

Основной замысел настоящего изобретения заключается в том, что устройство обработки данных согласно настоящему изобретению может быть

реализовано в виде взаимно смежных, по существу параллельных уложенных или упакованных основных слоев, каждый из которых состоит из нескольких подслоев, которые специфическим образом реализуют

определенные электрические свойства в основном слое, при этом ни процессорный модуль, ни запоминающие модули, кроме модулей, находящихся в одном или нескольких слоях, не должны широко использовать

активные устройства. Это стало возможным с началом использования новейших материалов и архитектур, которые будут более подробно описаны ниже. В наиболее общем схематическом виде это показано на фиг.2,

где многослойная структура, состоящая соответственно из слоя Р процессора и ряда слоев ЗУ M1, M2, . .. обеспечивается на подложке S. Подложка S может быть выполнена, например, из

кремния, и сформированные над ней слои Р реализуют слой процессора, в который включен по меньшей мере центральный процессорный модуль (не показан) и, возможно, по меньшей мере один управляющий

процессор и процессор, обрабатывающий данные, поступающие по линии связи. Слой процессора, следовательно, будет содержать активные компоненты и может быть реализован по неорганической

полупроводниковой технологии, например, на кремниевой подложке. Над слоем процессора обеспечиваются в конфигурации уложенные различные слои ЗУ M1, М2,..., которые составляют

запоминающий модуль в устройстве обработки данных, причем отдельные блоки памяти формируют в каждом отдельном слое памяти и компонуются, например, как ЗУПВ (RAM), ПЗУ (ROM), СТИРАЕМОЕ или

ПЕРЕПРОГРАММИРУЕМОЕ запоминающее устройство, причем последняя упомянутая концепция охватывает и стираемые и перепрограммируемое запоминающие устройства. Очевидно, что каждый слой Р, М в устройстве

обработки данных на фиг. 2 содержит электропроводящие структуры, либо горизонтальные, либо вертикальные, которые обеспечивают соединение между компонентами в каждом слое и между самими слоями. Данная

концепция будет более подробно рассмотрена ниже.

На фиг. 3 более подробно изображен первый вариант выполнения устройства обработки данных согласно настоящему изобретению, которое по существу реализуется на первом уровне функциональной иерархии. В данном случае слой Р процессора также сформирован на подложке S и также включает в себя активные компоненты типа транзисторов для того, чтобы реализовать один или более центральных процессоров и, возможно, управляющие процессоры и процессоры, обрабатывающие данные, поступающие по линии связи. Над слоем Р процессора формируют интерфейс 1 памяти, который прокладывают над подложкой S за пределы слоя Р процессора. Над интерфейсом памяти формируют слои памяти M1, М2,.... Все слои, включая слой Р процессора, слои памяти и интерфейс 1 памяти содержат непоказанные горизонтальные электропроводящие структуры, предназначенные для того, чтобы обеспечить соединение между отдельными компонентами, но кроме этого, эти проводящие структуры находятся в слоях памяти М, выведенных к электрическим торцевым соединениям на боковых сторонах слоя ЗУ и к шинам 2 памяти, которые формируются в отдельном модуле 2' шин памяти, как показано на фигуре. Для каждого слоя ЗУ M1, M2,... формируются соответствующие шины памяти 21, 22,..., а они, в свою очередь, могут быть созданы и как горизонтальные и как вертикальные электропроводящие структуры в модуле 2' шин памяти.

Фиг. 4 изображает другой вариант выполнения устройства обработки данных согласно настоящему изобретению. Слой Р процессора также формируется на подложке S, тогда как интерфейс 1 памяти формируется над слоем Р процессора и покрывает его полностью, не контактируя с подложкой S. Отдельные слои памяти M1, M2,... предусмотрены над интерфейсом 1 памяти, но в этом варианте выполнения отдельный модуль шин памяти был исключен. Вместо этого шины 2 памяти во всей своей полноте создаются как вертикальные электропроводящие структуры, которые простираются до слоев M1, M2,... памяти и обеспечивают соединение с интерфейсом 1 памяти. Шины 2 памяти обеспечивают соединение с не показанными на фигуре адресными линиями для блоков памяти в запоминающем модуле, поскольку адресные линии могут быть обеспечены в виде горизонтальных электропроводящих структур в каждом слое М памяти. Предпочтительно, чтобы слой памяти M1, который является ближайшим к слою Р процессора, был реализован с помощью запоминающих устройств записи/считывания (ЗУПВ, RAM) таким образом, чтобы пути сигнала между ЗУПВ и слоем Р процессора стали как можно более короткими. Слой памяти M1 может быть реализован с помощью ряда запоминающих устройств ЗУПВ, а порт ввода/вывода каждого ЗУПВ предусмотрен на шинах 21 памяти, специально сформированных для каждого ЗУПВ, показанного на фигуре. Остальные слои М2,... памяти (ЗУ), которые могут присутствовать в очень большом количестве, могут реализовать память большого объема устройства обработки данных. Однако следует уяснить, что в принципе не должно быть какой-либо разницы между физической реализацией соответственно запоминающих устройств ЗУПВ и ЗУ большого объема, поскольку память в отдельных слоях ЗУ может быть реализована точно по такой же технологии. Следовательно, подобно ЗУПВ, ЗУ большого объема может быть реализовано с помощью блоков памяти, которые во всей своей полноте реализуются как запоминающие устройства записи/считывания, СТИРАЕМЫЕ или ПЕРЕПРОГРАММИРУЕМЫЕ, но могут также содержать запоминающие устройства типа запоминающих устройств с однократной записью и многократным считыванием (WORM).

Представляется предпочтительным, чтобы отдельные основные слои согласно настоящему изобретению, как уже упоминалось выше, реализовывались в виде ряда тонких подслоев по такой технологии и с использованием таких материалов, которые позволили бы реализовать основные слои как объединенные слои процессора и памяти, и по меньшей мере один основной слой по существу - как слой памяти. Эта проблема будет рассмотрена ниже более подробно. В связи с этим представляется целесообразным, чтобы технология, которая используется для реализации основных слоев для этой цели, образовала функциональную иерархию, первый уровень которой в функциональной иерархии функционально компонует слои либо в виде объединенных слоев процессора или памяти, либо в виде отдельных слоев процессора или памяти. Второй уровень в функциональной иерархии будет затем функционально компоновать процессорный модуль в виде по меньшей мере одного процессора или частей процессоров, а последние могут по требованию составлять один или более центральных процессорных модулей и микропроцессоров в устройстве обработки данных, а в случае необходимости процессоров специального назначения или, возможно, могут компоноваться как соответственно управляющие процессоры и процессоры данных, поступающих по линии связи. На третьем уровне функциональной иерархии применяемая технология обеспечивает архитектуру отдельного процессора, например центрального процессорного модуля в виде параллельного процессора с несколькими модулями исполнения, работающими параллельно. Соответственно применяемая технология на втором уровне функциональной иерархии будет функционально компоновать запоминающий модуль как один или более блоков памяти или частей блоков памяти. На третьем уровне функциональной иерархии один или более блоков памяти могут быть реализованы как запоминающие устройства ЗУПВ, а затем соединяться с по меньшей мере одним центральным процессорным модулем, и, возможно, дополнительные блоки памяти могут факультативно компоноваться как быстродействующие блоки памяти, постоянные запоминающие устройства ПЗУ (ROM), запоминающие устройства с однократной записью и многократным считыванием (WORM), СТИРАЕМЫЕ и ПЕРЕПРОГРАММИРУЕМЫЕ запоминающие устройства. Указанные блоки памяти могут в дальнейшем быть включены в память большого объема запоминающего модуля, и, если они компонуются как СТИРАЕМЫЕ и ПЕРЕПРОГРАММИРУЕМЫЕ, то они могут на практике быть способными работать в качестве запоминающих устройств ЗУПВ, но с намного более высокой емкостью хранения, чем та, которая имеет место для известных ЗУПВ. Однако применяемая технология может быть использована и для реализации запоминающих устройств ЗУПВ с емкостями хранения, намного превышающими современные динамические ЗУПВ, основанные на неорганических полупроводниках, и по меньшей мере для реализации запоминающих устройств ЗУПВ с емкостью хранения, которая приближается к емкости ЗУ большой емкости обычных ПК.

Вышеупомянутые признаки и преимущества могут быть реализованы посредством устройства обработки данных согласно настоящему изобретению, по существу основанному на компонентах, реализуемых по тонкопленочной технологии. В частности, подслои окажутся отдельными тонкими пленками и могут быть объединены, например, посредством ламинирования в основные слои, которые являются слоями процессора и/или слоями ЗУ. В активных компонентах типа транзисторов в процессорах могут использоваться полупроводниковые тонкопленочные материалы, которые могут быть неорганическими, органическими, аморфными или поликристаллическими.

В качестве материалов блоков памяти и логических устройств может использоваться энергонезависимый тонкопленочный материал с возможностью сохранения этими компонентами заданного логического состояния в случае перебоев с питанием.

В частности, тонкопленочные материалы, которые используются для реализации блоков памяти в слое памяти, могут спонтанно образовывать диодные переходы, и, кроме того, они также могут быть основаны на анизотропных проводящих тонкопленочных материалах. Это позволит предусмотреть схемы адресации, в которых блоки памяти компонуются как электрически адресуемые пассивные матрицы, которые обеспечивают возможность высокой плотности хранения и большой емкости хранения без необходимости использования каких-либо активных компонентов. В частности, весь слой памяти в каждом отдельном случае может быть реализован в виде модулей памяти, выполненных по тонкопленочной технологии. Известно, как это может быть реализовано технически, например, последовательным нанесением отдельных слоев на общую подложку, или путем соединения отдельных сверхтонких самоподдерживающихся слоев. Данная проблема будет более подробно рассмотрена ниже.

Далее со ссылкой на фиг.5 будет описан третий вариант выполнения устройства обработки данных согласно настоящему изобретению, поскольку фиг.5 более полно изображает представленный вариант осуществления. В этом варианте используется несколько слоев Р процессора. Первый из этих слоев процессора - слой P1 - обеспечивается смежно с интерфейсом 3 процессора, который расположен ближайшим к подложке S. Между первым P1 и вторым P2 слоем процессора, который, как это обозначено на фигуре, может содержать несколько процессоров 5, из чередующихся слоев выполнен первый слой M1 памяти и по меньшей мере одно ЗУПВ 6, приданное процессору 5 в слое P1 процессора. Над слоем M1 памяти следует второй слой Р2 процессора с несколькими процессорами 5 и с приданными ему слоем M2 памяти с одним или более ЗУПВ 6, приданными процессору в слое P2 процессора. Над слоем M2 памяти далее следует третий слой Р3 процессора, который снова может содержать несколько процессоров 5, и затем следует слой М3 памяти с одним или более запоминающими устройствами ЗУПВ 6, приданными процессорам в слое Р3 процессора. Следует понимать, что число слоев Р процессора с приданными слоями ЗУПВ M1, М2, М3 может быть более 3-х, и что вариант выполнения, показанный на фиг.5, служит для иллюстрации.

Над слоем памяти М3 предусмотрен интерфейс 1 памяти, над которым размещено большое число дополнительных слоев памяти М4, M5,..., которые могут хорошо реализовать память большого объема в устройстве обработки данных. Эти дополнительные слои памяти М4, M5 по шинам 2 памяти, реализованным в виде вертикальных электропроводящих структур, выводятся к интерфейсу 1 памяти. Соответственно отдельные ЗУПВ имеются в слоях M1, М2, М3 памяти, также выведенных к интерфейсу 1 памяти через отдельные слои по вертикальным шинам 2 памяти. Кроме того, шины 7 памяти, которые ведут к портам ввода/вывода на отдельных ЗУПВ, предусматриваются между процессорами 5 в слоях процессора P1, Р2, р3 и присваиваются ЗУПВ в слоях M1, M2, М3 памяти. Для каждого процессора 5 две таких шины 7 памяти нарисованы символически, чтобы показать отдельную инструкцию и шины данных. Данное условие не является обязательным. Интерфейс 3 процессора соединяется с возможными внешними модулями по шине 8 ввода/вывода и соответственно для интерфейса 1 памяти обеспечивается шина 9 ввода/вывода.

В частности, в варианте выполнения, показанном на фиг.5, предлагается устройство обработки данных, которое согласно настоящему изобретению компонуется с рядом процессоров 5, и по меньшей мере соответствующее число запоминающих устройств ЗУПВ назначается процессорам. Посредством компоновки процессорного модуля с несколькими процессорами и обеспечения каждого процессора одним или более запоминающих устройств ЗУПВ, где вертикальная конфигурация шин данных одновременно обеспечивает высокую скорость передачи, можно решить проблемы времени ожидания даже с большими значениями ширины полосы частот для портов ввода/вывода запоминающих устройств ЗУПВ.

В случае изготовления запоминающих устройств ЗУПВ с использованием технологий, которые будут более подробно описаны в дальнейшем, в частности технологий, обеспечивающих возможность параллельной адресации при 100 процентном использовании большой ширины полосы частот передачи даже с очень высоким временем цикла, может быть устранена проблема, связанная с вышеупомянутым расхождением между высокими рабочими характеристиками процессора и со значительным временем доступа. В действительности при приемлемой архитектуре может быть реализовано устройство обработки данных с несколькими процессорами, работающими параллельно, так что с соответствующим вариантом выполнения отдельного процессора, например, используя параллельную обработку в самом процессоре, интегрированное устройство обработки данных реализуется с емкостью, которая приближается или превышает известные супер-ЭВМ, выполненные по известной технологии. Как показано на фиг.5, для этой цели используется шина 4 процессора. Как будет упомянуто ниже, использование нескольких процессоров 5, которые, возможно, могут работать параллельно и которые взаимно соединяются по шине 4 процессора и формируются в тесном соединении с по меньшей мере одним запоминающим устройством ЗУПВ, обеспечивает не только вариант выполнения, в большой степени устраняющий проблемы времени ожидания, но также благодаря объемному выполнению устройства обработки данных обеспечивает возможность оптимальной способности взаимного соединения между процессорами и подходящими ЗУПВ. Если сеть процессоров 5 и запоминающих устройств ЗУПВ 6 сформирована, как показано на фиг.5, то она может динамически конфигурироваться для обеспечения емкости, оптимально адаптированной к данной задаче. Компоновка может, например, происходить с конкретным, не показанным на фигуре, управляющим процессором, который может быть предусмотрен в интерфейсе 3 процессора, к которому подсоединяется шина 4 процессора.

Как уже упоминалось выше, процессоры не обязательно должны формироваться в отдельных слоях или слоях Р процессора, и соответственно все блоки памяти в запоминающем модуле не должны формироваться в отдельных слоях или слоях М памяти. Соответственно процессоры и блоки памяти, например ЗУПВ, присвоенные процессорам, можно формировать в одном и том же основном слое, как показано на фиг. 6, которая также изображает вариант выполнения устройства обработки данных согласно настоящему изобретению. Здесь интерфейс 3 процессора с интерфейсом 8 ввода/вывода также формируется на подложке S, и над интерфейсом 3 процессора следует слой P1 процессора с одним или более процессорами. И интерфейс 3 процессора и слой P1 процессора могут быть самыми низкими слоями в устройстве обработки данных на фиг.6 и могут быть реализованы смежными с подложкой по известным, например, полупроводниковым технологиям на основе кремния. Первый слой M1 памяти, который может компоноваться с одним или более запоминающими устройствами ЗУПВ 6, присвоенными процессорам 5 в нижележащем слое P1 процессора, формируется над последним. Однако, как показано на фиг. 6, отдельное ЗУПВ 6 в слое памяти M1 специальным образом не выделяется. С другой стороны, блоки памяти в слое памяти M1 могут быть непосредственно соединены с нижележащим слоем P1 процессора по шинам 7, поскольку конфигурация в виде слоев, уложенных в стопку, позволяет обеспечивать такие шины 7 в больших количествах, посредством их выполнения в виде вертикальных проводящих структур, а также конфигурация слой на слое позволяет обеспечивать значительное количество таких соединений шин между слоем P1 процессора и слоем памяти M1 и, кроме того, с короткими путями для сигнала. Компоновка расположения рядом на поверхности могла бы наоборот потребовать более длинных соединительных дорожек и, следовательно, более длительных времен передачи. Дополнительно в устройстве обработки данных согласно фиг.6 предусмотрены объединенные слои памяти и процессора MP1, МР2 и МР3, оснащенные процессорами, соединенными между собой и с интерфейсом 3 процессора по той же самой шине 4 процессора. Все объединенные слои памяти и процессора МР могут содержать по меньшей мере один процессор 5 и по меньшей мере одно запоминающее устройство ЗУПВ 6. Как и в предыдущем варианте, над объединенными слоями памяти и процессора МР предусмотрен интерфейс 1 памяти с интерфейсом 9 ввода/вывода к внешним модулям, и над интерфейсом 1 памяти следуют слои памяти М2, М3 и т.д. в требуемом количестве, которое ограничивается лишь возможностями ЗУ большого объема устройства обработки данных. В свою очередь, слои памяти M2, М3 соединяются с интерфейсом 1 памяти по шинам памяти, реализованным в виде вертикальных проводящих структур через слои М2, М3. ...

На фиг. 2-6 устройство обработки данных согласно настоящему изобретению показано в разрезе через различные слои устройства, но следует понимать, что слоистая структура устройства обработки данных фактически реализует объемные конфигурации, в которых, например, вертикальные токопроводящие структуры можно формировать распределенными по поверхности и, следовательно, обеспечить большое количество соединений между блоками памяти и процессорами и сопровождающими интерфейсами, и по аналогии шина 4 процессора в каждом случае проходит и в горизонтальном и в вертикальном направлении в различных слоях и может соединять процессоры, которые распределены внутри одного и того же слоя или на различных слоях в трехмерно скомпонованной сети. В связи с этим также следует отметить, что когда для электропроводящих структур используются выражения "горизонтальные" и "вертикальные", то под этим следует понимать, что первое понятие подразумевает, что проводящая структура проходит вдоль слоя и по существу параллельно его верхней и нижней сторонам, а соответственно второе понятие означает, что структура проходит по существу перпендикулярно к верхней и нижней сторонам слоев и пересекает их. Следовательно, чисто практически понятия "горизонтальный" и "вертикальный" также могут относиться к ориентации слоев относительно нижележащей по существу плоской подложки, поскольку слои не только взаимно параллельны, но также и простираются параллельно поверхности подложки S.

Устройство обработки данных согласно настоящему изобретению, за исключением подложки, полностью могло бы быть реализовано с использованием органических материалов, возможно металлоорганических комплексов, и выполнено по тонкопленочной технологии. На практике может быть выгодно сформировать интерфейс 3 процессора и самый нижний слой P1 процессора, смежный с подложкой S, таким образом, чтобы можно было свободно реализовать компоненты в этих слоях по традиционным и хорошо известным полупроводниковым технологиям, например на основе кремния. Однако, конечно, указанные слои могли быть реализованы по органической тонкопленочной технологии.

Далее будет более подробно описано, каким образом блоки памяти в запоминающем модуле могут быть реализованы практически. Аналогично будут приведены примеры вариантов выполнения активных компонентов, например таких как транзисторы, и проводящих структур, в которых также кратко будут оценены различные материалы и технологии для исполнения этих компонентов. Это позволит уяснить, что устройство обработки данных в вариантах выполнения, показанных на фиг.2-6, может быть реализовано с помощью технологий, которые либо доступны либо в настоящее время разрабатываются заявителем наряду с другими.

В описании по патенту Норвегии 972803, которое было передано правопреемнику настоящего заявителя и которое включено в качестве ссылки, раскрывается электрически адресуемое логическое устройство для хранения или обработки данных. На фиг.7а изображен вариант выполнения этого устройства, скомпонованного как блок памяти данных. Блок памяти содержит носитель 10 памяти, который образует слоистую непрерывную структуру, которая может быть реализована в виде слоя в одном из слоев М памяти в настоящем изобретении. Носитель 10 памяти формируется по существу на основе органического материала, который может претерпевать физическое или химическое изменение состояния посредством энергетического влияния. Носитель 10 памяти, как показано на фиг.7а, предусмотрен между матрицей по существу ортогональных пересекающихся электродов 11 и 12 так, что в соединении с носителем памяти образуют по существу ортогональную матрицу электродов, которая непосредственно контактирует с носителем памяти. Очевидно, что электроды 11, 12 могут быть реализованы в виде вышеупомянутых проводящих структур в слое М памяти. На пересечении между вышележащим электродом 11 и нижележащим электродом 12 в материале носителя 10 памяти формируется логическая ячейка, которая под действием напряжения, тока или электрического поля может достигать состояния, которое может представлять предопределенное логическое значение ячейки. Следовательно, указанные логические ячейки составляют элементы памяти в блоке памяти, как показано на фиг.7а. Каждый из электродов 11, 12 соединяется с модулем шин 2' памяти по адресным линиям 13, а модуль шин памяти находится над шиной 2 памяти, соединенной с интерфейсом 1 памяти, который может быть сформирован в другом слое в устройстве обработки данных и пространственно отделен от рассматриваемого слоя памяти, причем шина 2 памяти, предназначенная для этой цели, частично реализуется в виде вертикальных проводящих структур, которые проходят через различные слои в устройстве обработки данных, как это схематически показано на фиг.7б, которая изображает разрез блока памяти с фиг.7а, взятый вдоль одного из электродов 12. Фиг.7в и 7г изображают разрезы отдельной ячейки 14 памяти, которая образуется на пересечении между вышележащим электродом 11 и нижележащим электродом 12. Электроды 12 и 11 могут быть сформированы внутри носителя памяти 10 или на нем и непосредственно контактировать с ним, либо с обеих сторон носителя памяти могут быть обеспечены не показанные на фигуре диэлектрические слои с возможностью косвенного контактирования электродов 11, 12 с носителем 10 памяти. Если к электродам 11, 12 прикладывается напряжение, то в каждом случае получается прямое или косвенное электрическое соединение через элемент памяти, с приведением его в определенное состояние и с возможностью детектирования определенного состояния элемента 14. Изменение состояния элемента 14 памяти может быть изменением характеристик тока или напряжения материала памяти в данном местоположении или изменением в значении импеданса материала. При выборе подходящих материалов специфическое состояние в отсутствие напряжения или электрических полей будет постоянным, так что состояние поддерживается постоянным и, следовательно, блок памяти на фиг.7а реализует энергонезависимое электрически адресуемое запоминающее устройство. Сам по себе материал памяти может быть полимером, например сопряженным полимером, а также может содержать анизотропный электропроводящий материал, являющийся электропроводным только в поперечном направлении между электродами, так что в материале памяти не генерируются электрические токи, распространяющиеся в продольном направлении. Материал носителя 10 памяти также может быть реализован аналогичным путем или добавочные вещества заставляют его переходить из кристаллической в аморфную фазу под действием напряжения или электрических полей, или наоборот, причем вольтамперные характеристики фазового состояния являются различными и обеспечивают возможность детектирования. Электроды 11, 12, которые реализуются в виде горизонтальных проводящих структур в рассматриваемом слое М памяти, могут сами по себе быть проводящим органическим материалом и реализоваться в виде осажденных металлоорганических соединений или в виде металлов на поверхности 10 материала памяти. Далее элемент памяти или логическая ячейка 10, 14 могут быть реализованы в виде выпрямляющего диода между электродами 11, 12, так что запоминающее устройство на фиг.7а образует электрическую сеть таких диодов. Данный вариант будет описан ниже более подробно далее, но диодная сеть этого вида может предотвращать ошибки записи и/или детектирования вследствие паразитных токов между элементами ЗУ в матрице электродов. В частности, может быть использован органический материал 10 ЗУ, который спонтанно формирует диодный переход в элементе 14 памяти. Еще одно преимущество заключается в том, что логическая ячейка реализуется таким образом, что материал 10 ЗУ под действием электрических токов или электрических полей подвергается реакции, которая заставляет изменяться значение сопротивления отдельной логической ячейки. Значение логической ячейки может детектироваться далее посредством измерения импеданса логической ячейки, и это детектирование, конечно. соответствует считыванию содержимого запоминающего устройства, показанного на фиг.7а. Если логическое значение элемента памяти может переключаться обратимо, то запоминающее устройство на фиг.7а реализует память записи/считывания или память СТИРАЕМОГО типа, но логическое значение может переключаться и необратимо таким образом, что запоминающее устройство на фиг.7а за счет этого реализует постоянное запоминающее устройство ПЗУ (ROM) или ЗУ типа запоминающего устройства с однократной записью и многократным считыванием (WORM). Если используется запоминающее устройство, показанное на фиг. 7а в виде уложенных слоев М ЗУ, они должны быть взаимно изолированы, и это можно осуществить, формируя диэлектрические тонкие слои 15 на каждой стороне электродов. Если электроды 11, 12 располагать на поверхности материала памяти, то они одновременно могут быть включены в диэлектрические слои 15, показанные на фиг.7г.

В варианте осуществления запоминающего устройства согласно фиг.7а, где само запоминающее устройство имеет такую же электрическую схему, в качестве материала 10 ЗУ может быть использована тонкая пленка сегнетоэлектрического материала, поскольку сегнетоэлектрический материал этого вида под действием приложенного электрического поля может достигать первого или второго состояния поляризации и переключаться из хаотического состояния в одно из состояний поляризации, и из первого во второе состояние поляризации, или наоборот. Далее логическая ячейка или элемент 14 памяти могут быть реализованы в тонкой пленке сегнетоэлектрического материала между электродами 11, 12. Определенное состояние поляризации, присвоенное логическому элементу 14, представляет собой логическое значение логического элемента или значение данных, сохраненное в элементе памяти. В любом случае логическая ячейка или элемент памяти компонуются, как показано на фиг.7в и 7г. Однако, если логический материал или носитель памяти представляет собой сегнетоэлектрическую тонкую пленку, то логическая ячейка или элемент 14 памяти также может быть реализована, как показано в виде сверху на фиг.7д, а также на фиг.7е в разрезе, взятом по линии А-А' на фиг.7в. Здесь вышележащий электрод 12 располагается отстоящим от нижележащего электрода 11 посредством изолирующей ступеньки 15'. Тогда активный участок в сегнетоэлектрической тонкой пленке окажется выполненным в виде тонких полосок с обеих сторон электрода 12, как показано на фиг.7д, и простирается до нижележащего электрода 12, как показано на фиг. 7е, на которой силовые линии поля обозначены стрелками. При изготовлении запоминающего устройства на основе сегнетоэлектрической тонкой пленки, как уже упоминалось выше, электроды 11 сначала формируются посредством структурирования подходящего материала, например, предусмотренного на не показанной на фигуре изолирующей подложке. Затем над ним формируется непрерывный слой 15 из изолирующего материала и на верхней его части электроды 12, в результате чего получается по существу ортогональная матрица электродов. После нанесения электродов 12 изолирующий материал 15 вытравливается или удаляется другим способом в областях между электродами, и сегнетоэлектрическая тонкая пленка 10 обеспечивается в виде непрерывного слоя над электродами, как показано на фиг.7е. Сегнетоэлектрическая тонкая пленка 10 может быть сформирована из керамического материала или может быть сегнетоэлектрическим жидкокристаллическим материалом, но предпочтительно будет формироваться из полимера или сополимера, например сополимера винилиденфторид/трифторэтилен.

Запоминающее устройство, показанное на фиг.7а, может быть включено в запоминающий модуль в устройстве обработки данных согласно настоящему изобретению и в этом случае оно может быть выполнено, как показано на фиг.7ж, с уложенными слоями Mk-1, mk,... памяти в подходящем количестве. Электроды 11, 12 в отдельных слоях и адресные линии 13 повторно формируются как горизонтальные проводящие структуры и подсоединяются к модулю 2' шин памяти с помощью шин 2 памяти. Шины 2 памяти могут быть либо горизонтальными проводящими структурами, либо вертикальными проводящими структурами и обеспечивают соединение между слоями М памяти и нижележащим интерфейсом 3 памяти и с интерфейсом 9 ввода/вывода, как показано на фиг.7ж. Наиболее предпочтительный вариант воплощения запоминающего устройства, исполненного, как показано на фиг. 7ж, получается с вариантом выполнения, показанным на фиг.7з, которая представляет разрез вдоль параллельных пересекающихся электродов 11, 12 и через пересекающиеся параллельные электроды 11, 12. На изолирующей подложке в первом слое памяти Mk-1, как и в случае рассмотренного варианта выполнения, формируют нижележащий электрод 11, а над ним - вышележащий электрод 12. Вышележащий электрод 12 в первом слое Mk-1 в данном случае представляет собой нижележащий электрод 11 в последующем слое Мk памяти и соответственно вышележащий электрод 12 в слое Мk памяти выполняет функцию нижележащего электрода 11 в вышележащем слое Mk+1. Таким образом, запоминающее устройство, показанное на фиг.7ж и выполненное со слоем М памяти, может оказаться с наборами из n+1 электродов 11, 12 вместо наборов из 2n электродов, как показано в варианте выполнения на фиг.7ж. Конфигурация этого вида электродов в уложенном логическом устройстве или модуле памяти, реализованном в упакованной конфигурации, раскрывается в норвежском патенте 980871, который включен в описание в качестве ссылки и принадлежит правопреемнику настоящего заявителя. Ниже будет описано еще одно техническое решение для реализации логического устройства или запоминающего устройства для использования в устройстве обработки данных согласно настоящему изобретению. Это достигается с помощью средства электрода, которое более подробно раскрывается в норвежском патентном описании 973390 и которое тем самым включено в описание в качестве ссылки и принадлежит правопреемнику настоящего заявителя. Фиг.8а изображает вариант выполнения указанного средства электрода с функциональным элементом 17, который может иметь функцию детектирования, хранения информации и/или индикации информации. Для реализации настоящего изобретения желательно, чтобы функциональный элемент 17 функционировал как логическая ячейка либо с функцией переключения, которая может использоваться для реализации логических компонентов, либо с функцией хранения информации, которая может использоваться для реализации элементов памяти в запоминающем устройстве. В частности, функциональный элемент 17 может быть электрически чувствительным и выполненным с возможностью обеспечения средством электрода возможности пассивной электрической адресации функционального элемента. В средстве, изображенном на фиг.8а, нижележащий электрод 11 формируется, например, на не показанной на фигуре подложке и над этим электродом формируется вышележащий электрод 12, который пересекает нижележащий электрод 11 в конфигурации моста, поскольку между электродами 11, 12 обеспечивается слой 15 из электроизолирующего материала, который также проходит под всем электродом 12 и между электродами, и не показанная на чертеже нижележащая подложка. Над обоими электродами 11, 12 предусмотрен контактный слой 16 из электропроводящего или полупроводникового материала, который электрически контактируют с обоими электродами 11, 12. По двум противоположным боковым торцам электрода 12 и до первого электрода 11 контактный слой образует активные участки в месте скрещивания электродов 11, 12. В частности, материал контактного слоя 16 должен быть анизотропным проводником или полупроводником, и даже более желательно применять анизотропный проводник, который полностью реализуется в полимерных материалах. Причина этого будет упомянута ниже. Над контактным слоем 16 обеспечивается функциональный элемент 17, смежно с электродами 11, 12 или перекрещиваясь с ними. В принципе функциональный элемент 17 можно было бы сформировать как часть пересечения контактного слоя 16 над пересечением электродов 11, 12 и тогда он по существу будет конформным с ними, так что функциональный элемент 17 по существу соответствует активным участкам, которые формируются в контактом слое.

Как показано на фиг.8а, функциональный элемент 17 реализуется как отдельный элемент и обеспечивается на пересечении электродов 11, 12, но только над контактным слоем 16 в верхней его части. Первый электрод 11 может быть выполнен из алюминия, который имеет низкую работу выхода, в то время как другой электрод 12 может быть выполнен из золота, которое имеет более высокую работу выхода, чем алюминий. Фундаментальная структура функционального элемента 17 и контактного слоя 16 показана на фиг.9. В качестве металла 1, составляющего первый и нижележащий электрод 11 в средстве, может быть выбран алюминий. Металл 1 вместе с полимером 1 образует выпрямляющий переход Шотки, в котором металл 1 в электроде 11 составляет катод. Полимер 1 выполнен из первого полимерного материала, который предпочтительно является политиофеном. Металл 2 в электроде 12 составляет анод структуры и образует невыпрямляющий переход в полимере 1. Полимер 2, который выполнен из другого полимерного материала, формирует функциональный элемент 17 и может быть реализован с возможностью изменения своих вольтамперных характеристик под действием приложенного электрического напряжения или электрического поля. Второй полимерный материал, который используется в функциональном элементе 17, предпочтительно является водорастворимым политиофеном (POWT).

Структура на фиг. 9 обеспечивает возможность прямого детектирования состояния проводимости функционального элемента 17 на основе вольтамперных характеристик средства. Средство электрода, показанное на фиг.8, может использоваться в электрическом адресуемом логическом устройстве, в частности пассивном адресуемом запоминающем устройстве, реализованном, как показано на фиг. 10. Множество электродов 11, 12 обеспечивается с возможностью формирования по существу ортогональной матрицы х, y электродов вместе со средством электрода из фиг.8 на каждом пересечении электродов. В случае, когда средство электрода реализуется вместе со структурами, показанными на фиг.9, то в каждом пересечении х электрода и y электрода получается диод 13, который в каждом случае имеет одно и то же направление проводимости. Также возможно, что отдельное средство электрода может быть реализовано с функцией выпрямления. Необходимо, чтобы при реализации функции выпрямления удалось избежать проблем перекрестных помех при адресации средства электрода, используемого в пассивной матрице, показанной на фиг.10. Именно выборочная адресация отдельного средства электрода требует, чтобы в каждом средстве электрода имелся выпрямляющий контакт, например, как уже упоминалось выше, между нижележащим электродом 11 и контактным слоем 16. Когда функциональный элемент 17 должен быть адресован в х, y положении в матрице, не должно быть переноса тока в смежных пересечениях (х+1, y), (х-1, y), (х, y+1) или (х, y-1). В связи с этим должно быть понятно, что диоды 18 на фиг.10 составляют только эквивалентную модель функции выпрямления средства электрода в пересечении между электродами 11, 12.