Устройство полупроводниковой памяти для достижения высокой производительности и способ расположения в нем сигнальных шин - RU2170955C2

Код документа: RU2170955C2

Чертежи

Описание

Известный уровень техники

Изобретение относится к устройству полупроводниковой памяти и, в частности, касается устройства полупроводниковой памяти и способа выполнения в нем сигнальных шин,

которые могут обеспечить высокую производительность благодаря созданию архитектуры кристалла, включающей мультишину ввода-вывода (I/O).

Одним из наиболее важных моментов при проектировании устройств полупроводниковой памяти является выбор подходящей архитектуры кристалла. От архитектуры кристалла зависят такие показатели качества функционирования устройства полупроводниковой памяти, как, например, энергопотребление, быстродействие, размеры кристалла и т. п. Другими словами, исключительная гибкость архитектуры кристалла в значительной степени способствует удовлетворению требований по этим параметрам. Специалистам хорошо известно, что при практической разработке архитектуры кристалла гибкость архитектуры кристалла позволяет поддерживать без изменений базовую структуру в случае изменения и введения дополнительных периферийных устройств и увеличения плотности устройства полупроводниковой памяти. Гибкость архитектуры кристалла помогает легко адаптироваться к этим вариантам. Целью развития устройств полупроводниковой памяти является достижение высокой производительности, соразмерной возможности устройства полупроводниковой памяти высокой плотности. Другими словами, концепция устройства полупроводниковой памяти изменилась от простого устройства памяти высокой плотности к новому устройству памяти, имеющему высокую производительность и синхронизированному по скорости работы системы. Например, в случае когда устройство памяти имеет 64 Мбайт (М) или более, в частности, для динамической оперативной памяти (RAM) с шиной прямого доступа или синхронной динамической (RAM) при базовой версии динамической RAM на 256 М, в течение рабочего цикла должно обрабатываться 256 бит данных. Следовательно, для удовлетворения тенденции развития устройств полупроводниковой памяти в сторону более высокой производительности используемая архитектура устройства памяти с материнской версией 256 бит должна иметь внутреннюю производительность 256 бит (за один цикл). Разработчики устройств памяти всех фирм-производителей ведут поиск архитектуры, имеющей возможно более высокую производительность. Между тем, чем выше плотность устройства памяти, тем больше размер кристалла. В результате возникают трудности со считыванием и записью данных из-за увеличения загрузки каждой шины. Эти трудности делают абсолютно необходимым создание новой архитектуры.

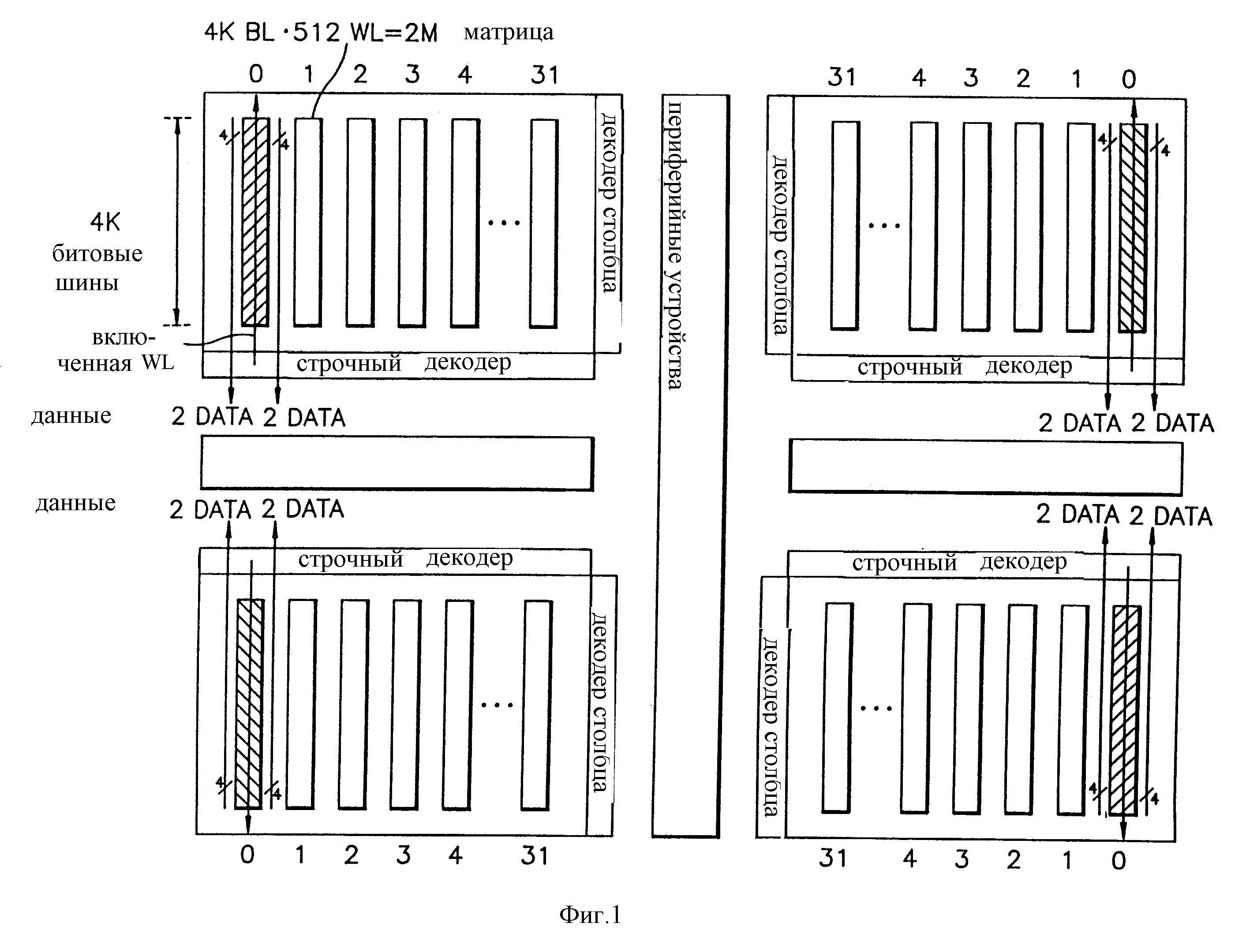

На фиг. 1 показана архитектура кристалла на 256 М в известном устройстве полупроводниковой памяти. Кроме того, схемная реализация внутренних столбцов на основе архитектуры кристалла, показанной на фиг. 1, раскрыта, например, в патенте США N 5247482, озаглавленном "Semiconductor Memory Device With High Speed Write Operation" ("Устройство полупроводниковой памяти с высокоскоростной операцией записи"). При выборе известной структуры со свернутыми битовыми шинами для получения динамической ОЗУ (DRAM) емкостью 256 М потребуются словные шины 32 К (шины на 32 К слов) и битовые шины 16 К (шины на 16 К бит). Конечно, 512 ячеек можно подсоединить к одной битовой шине, но принято подсоединять к одной битовой шине 256 ячеек. Таким образом одной словной шиной может быть активизирована матрица размерности 2 М. Полагая, что цикл обновления соответствует 16 К, две словные шины могут быть включены в продольном направлении кристалла посредством активизации на определенное время стробирующего сигнала строчного адреса

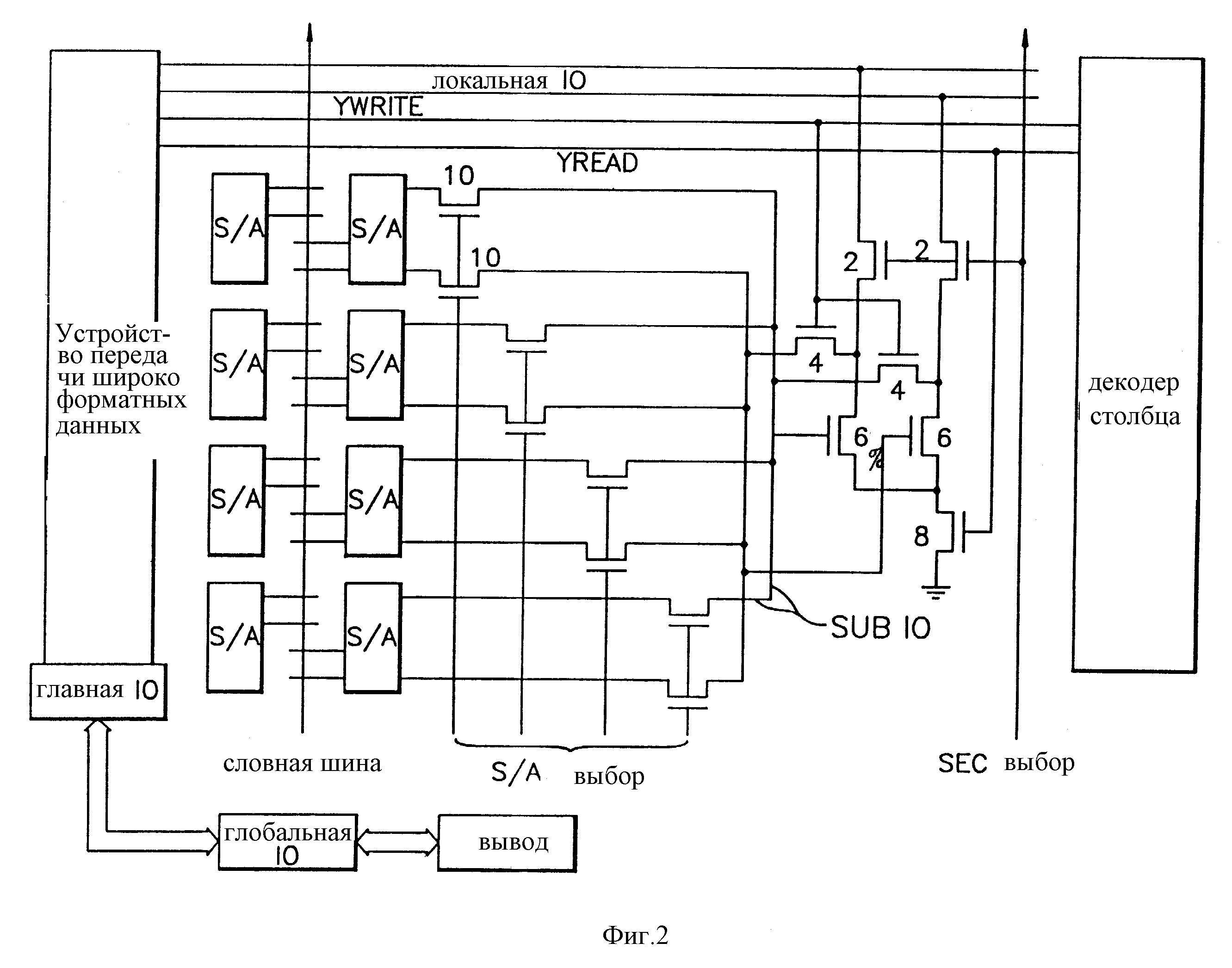

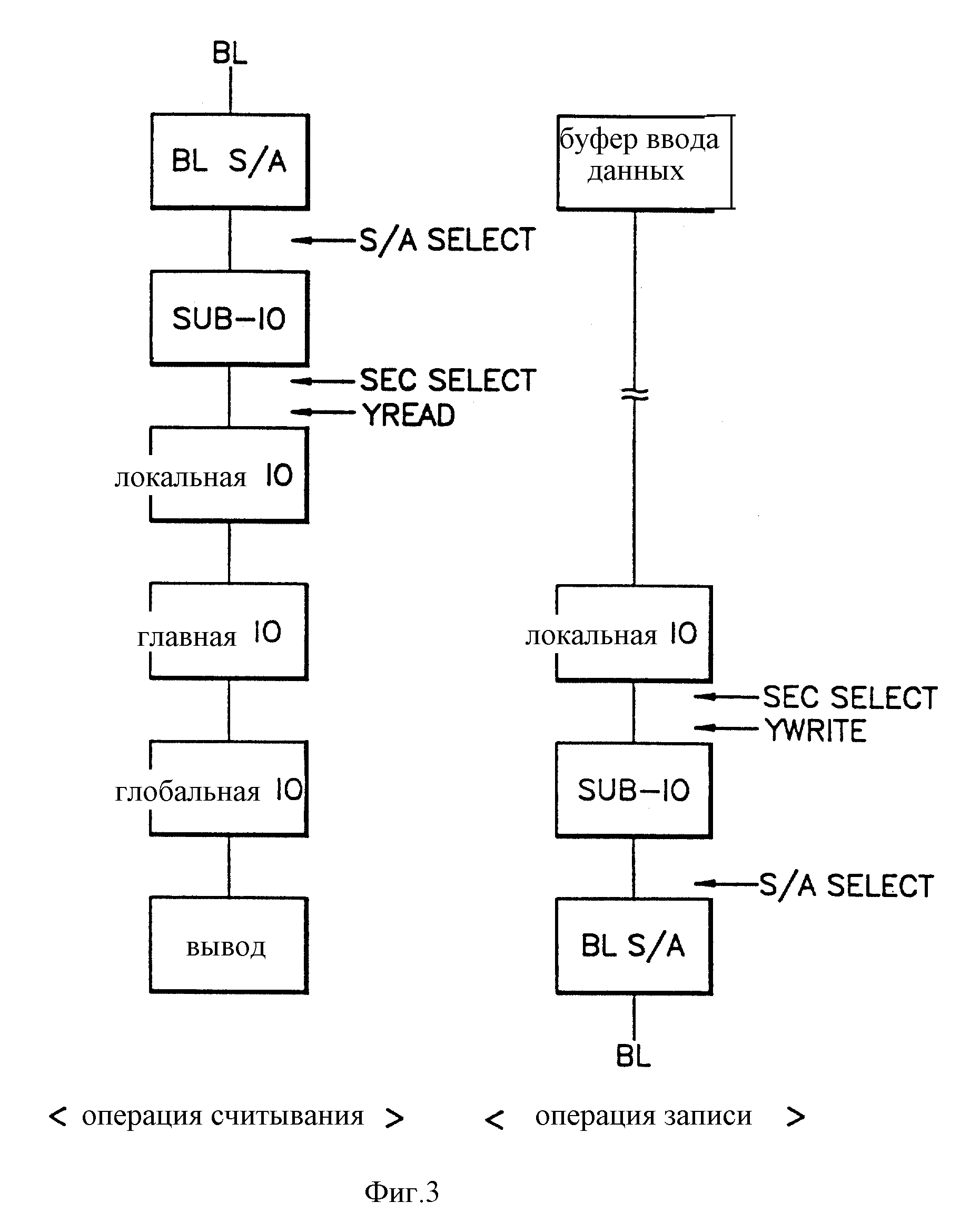

На фиг. 2 показан другой вариант известного устройства полупроводниковой памяти, с помощью которого может быть достигнута более высокая производительность по сравнению со структурой на фиг. 1, и в котором загрузка шин фиг. 1 существенно уменьшается. Схема на фиг. 2 раскрыта в "Circuit Techniques For a Wide Word I/O Path 64 Mega DRAM" на сс. 133-134 статьи "1991 Simposium on VLSI Circuits". Вышеупомянутая статья будет полезной для уяснения деталей фиг. 2. На фиг. 2 загрузка шины ввода-вывода уменьшается путем использования субшины ввода-вывода и локальной шины ввода-вывода. Также заранее определенное число усилителей считывания подключено к субшине ввода-вывода для того, чтобы передавать данные в локальную шину ввода-вывода через дифференциальный усилитель. Этот известный прием дает некоторое повышение внутренней производительности, но имеет недостаток, заключающийся в том, что количество n-МОП (NMOS)-транзисторов, через которые передаются данные, велико при выполнении операции записи. На фиг. 3 представлена блок-схема, показывающая шины ввода-вывода данных на фиг. 2. При выполнении операции записи данные по локальной шине ввода-вывода передаются на транзистор 2 фиг. 2 посредством подачи сигнала SEC SELECT, несущего данные столбца выбранного блока, но если для определения субшины ввода-вывода подан сигнал YWRITE, данные передаются на субшину ввода-вывода через транзистор 4. Если подан информационный сигнал S/A SELECT заданной битовой шины из множества битовых шин, подсоединенных к одной субшине ввода-вывода, данные передаются на битовую шину через транзистор 10. Как было упомянуто выше, при выполнении операции записи передача данных выполняется от шины ввода-вывода к битовой шине только через три n-МОП-транзистора, что является серьезным недостатком при выполнении операции записи в устройстве памяти с высокой степенью интеграции, имеющем большую загрузку шин.

Сущность изобретения

Итак, цель настоящего

изобретения - обеспечить устройство полупроводниковой памяти и способ расположения в нем сигнальных шин, которые реализуются путем создания архитектуры кристалла, в которой может быть достигнута

высокая производительность.

Другая цель настоящего изобретения - обеспечить устройство полупроводниковой памяти и способ расположения в нем сигнальных шин, которые реализуются путем создания архитектуры кристалла, в которой при осуществлении операций считывания и записи может выполняться высокоскоростной доступ к данным.

Еще одна цель настоящего изобретения - обеспечить устройство полупроводниковой памяти и способ расположения в нем сигнальных шин, которые могут решить проблему загрузки битовых шин и шин ввода-вывода при передаче данных.

Еще одна цель настоящего изобретения - обеспечить устройство полупроводниковой памяти и способ расположения в нем сигнальных шин, которые реализуются путем создания архитектуры кристалла, в которой может быть достигнута высокая производительность без использования отдельной локальной шины ввода-вывода для соединения битовой шины и главных шин ввода-вывода, и операция записи может выполняться с высокой скоростью.

Для достижения этих и других целей предлагается устройство полупроводниковой памяти, реализованное путем создания архитектуры кристалла, в которой может быть достигнута требуемая высокая производительность.

Согласно одному аспекту настоящего изобретения устройство полупроводниковой памяти имеет архитектуру, в которой множество битовых шин, передающих данные множества ячеек памяти, подсоединены к соответствующим шинам ввода-вывода данных, каждая из которых подсоединяется независимо от другой, чем достигается высокая производительность.

Согласно другому аспекту настоящего изобретения устройство полупроводниковой памяти включает строчные декодеры для расположения множества словных шин вдоль кристалла и декоры столбцов для расположения множества битовых шин и множества шин выбора столбца в поперечном направлении по отношению к длине кристалла.

Согласно другому аспекту настоящего изобретения устройство полупроводниковой памяти включает архитектуру, в которой множество главных шин ввода-вывода подсоединены одна за одной к множеству шин ввода-вывода данных, которые расположены между битовыми шинами и клеммой ввода-вывода данных кристалла.

Согласно другому аспекту настоящего изобретения устройство полупроводниковой памяти включает матрицы, состоящие из множества опорных блоков, хранящих множество ячеек памяти; множество словных шин, проходящих вдоль кристалла; множество битовых шин, проходящих поперек кристалла, причем каждая пара битовых шин состоит из битовой шины и комплементарной (в дополнительном коде) битовой шины; множество шин ввода-вывода данных, размещенных в верхней части матриц и идущих в поперечном направлении, причем каждая пара шин ввода-вывода данных состоит из шины ввода-вывода данных и комплементарной шины ввода-вывода данных и они одна за другой подсоединены к каждой паре битовых шин; и множество шин выбора столбца, размещенных в поперечном направлении смежно по отношению к шине ввода-вывода данных и комплементарной шине ввода-вывода данных, для управления подсоединением каждой пары битовых шин к шинам ввода-вывода данных.

Согласно другому аспекту настоящего изобретения способ расположения сигнальных шин в устройстве полупроводниковой памяти включает шаги: компоновка матриц, состоящих из множества опорных блоков для хранения множества ячеек памяти, размещенных в матричной форме; расположение множества словных шин для выбора строк ячеек памяти, причем словные шины проходят вдоль кристалла; расположение множества битовых шин, проходящих поперек кристалла, для выбора столбцов ячеек памяти, причем каждая пара битовых шин состоит из битовой шины и комплементарной битовой шины; расположение множества шин ввода-вывода данных, размещенных в верхней части матриц и идущих в поперечном направлении, причем каждая пара шин ввода-вывода данных состоит из шины ввода-вывода данных и комплементарной шины ввода-вывода данных, они подсоединены одна за другой к каждой паре битовых шин; и расположение множества шин выбора столбца, размещенных в поперечном направлении между шиной ввода-вывода данных и комплементарной шиной ввода-вывода данных для управления подсоединением каждой пары битовых шин к шине ввода-вывода данных.

Первым объектом изобретения является устройство полупроводниковой памяти, включающее банки памяти, каждый из которых содержит субматрицы памяти, состоящие из единичных матриц, активизация ячеек памяти вдоль строки которых осуществляется по направлению множества словных шин, при этом множество битовых шин, шин ввода-вывода данных и шин выбора столбца располагают перпендикулярно словным шинам, причем каждая пара из множества битовых шин состоит из битовой шины и комплементарной битовой шины, предназначенных для выбора столбца ячеек памяти, каждая пара из множества шин ввода-вывода состоит из шины ввода-вывода данных и комплементарной шины ввода-вывода данных, при этом между слоем, где находятся шины ввода-вывода данных и шины выбора столбца, и подложкой расположены слой битовых шин и слой словных шин, причем шину выбора столбца располагают смежно по отношению к соответствующим шине ввода-вывода данных и комплементарной шине ввода-вывода данных, причем для подключения словных шин предназначен строчный декодер, для подключения битовывх шин предназначен декодер столбца, а в каждую единичную матрицу дополнительно включена схема битовой шины, в которой для выполнения операции считывания предназначена шина сигнала выбора считывания, посредством которой выбирают одну пару из множества битовых шин, подсоединенную к одной паре шин ввода-вывода в соответствии с введенным адресом столбца, через соответствующие транзисторы считывания, по которой передают данные, хранящиеся в ячейке памяти, для выполнения операции записи предназначена шина сигнала выбора записи, посредством которой выбирают одну пару из множества битовых шин, подсоединенную к одной паре шин ввода-вывода, по которым передают данные в ячейки памяти через соответствующие транзисторы для записи в соответствии с введенным адресом столбца, причем при выполнении операции записи данные сначала передают на главную шину ввода-вывода, а затем через мультиплексор подают в шины ввода-вывода данных.

Вторым объектом изобретения является способ расположения сигнальных шин в устройстве полупроводниковой памяти, согласно которому компонуют матрицу, состоящую из множества ячеек памяти, располагают множество пар словных шин для выбора строк из множества ячеек памяти, причем каждую из множества пар словных шин располагают вдоль кристалла, располагают множество пар битовых шин для выбора столбцов из множества ячеек памяти, причем каждая пара из множества битовых шин состоит из битовой шины и комплементарной битовой шины и ее располагают в поперечном по отношению к длине кристалла направлении, располагают множество пар шин ввода-вывода данных (сигнальных шин) над матрицей в поперечном направлении кристалла, причем каждая пара из множества пар шин ввода-вывода состоит из шины ввода-вывода данных и комплементарной шины ввода-вывода данных, и каждая из которых способна к подсоединению к каждой паре из множества пар битовых шин, при этом располагают множество шин выбора столбца (сигнальных шин) смежно по отношению к парам шин ввода-вывода данных и комплементарных шин ввода-вывода данных.

Краткое описание чертежей.

Сущность изобретения

иллюстрируется ссылкой на прилагаемые чертежи, в которых одинаковые позиции указывают на одинаковые или подобные элементы:

фиг. 1 - блок-схема, иллюстрирующая конфигурацию архитектуры

кристалла в известном устройстве полупроводниковой памяти;

фиг. 2 - схема, иллюстрирующая конфигурацию шин ввода-вывода данных в известном устройстве полупроводниковой памяти;

фиг. 3

- схема шин ввода-вывода данных;

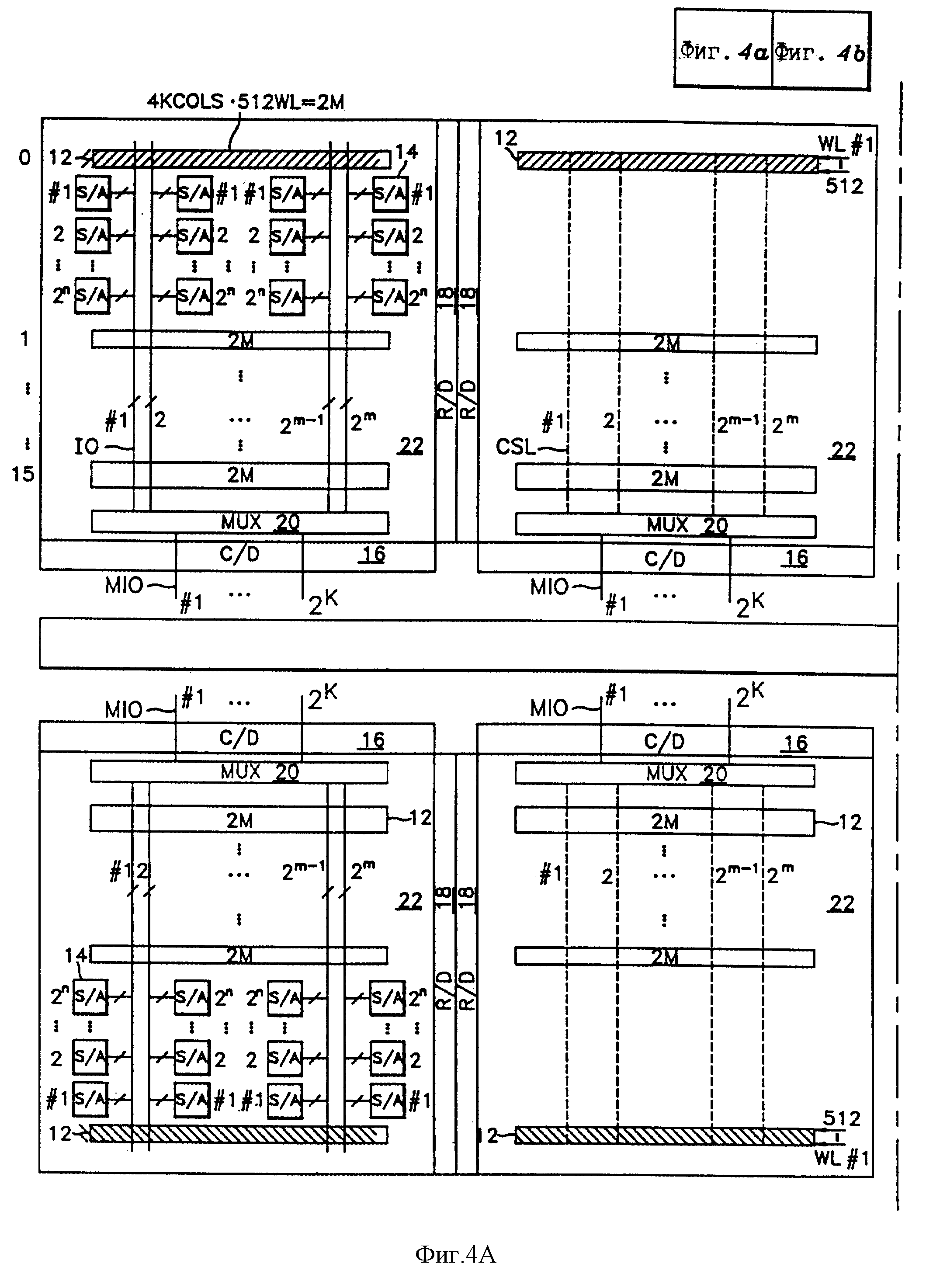

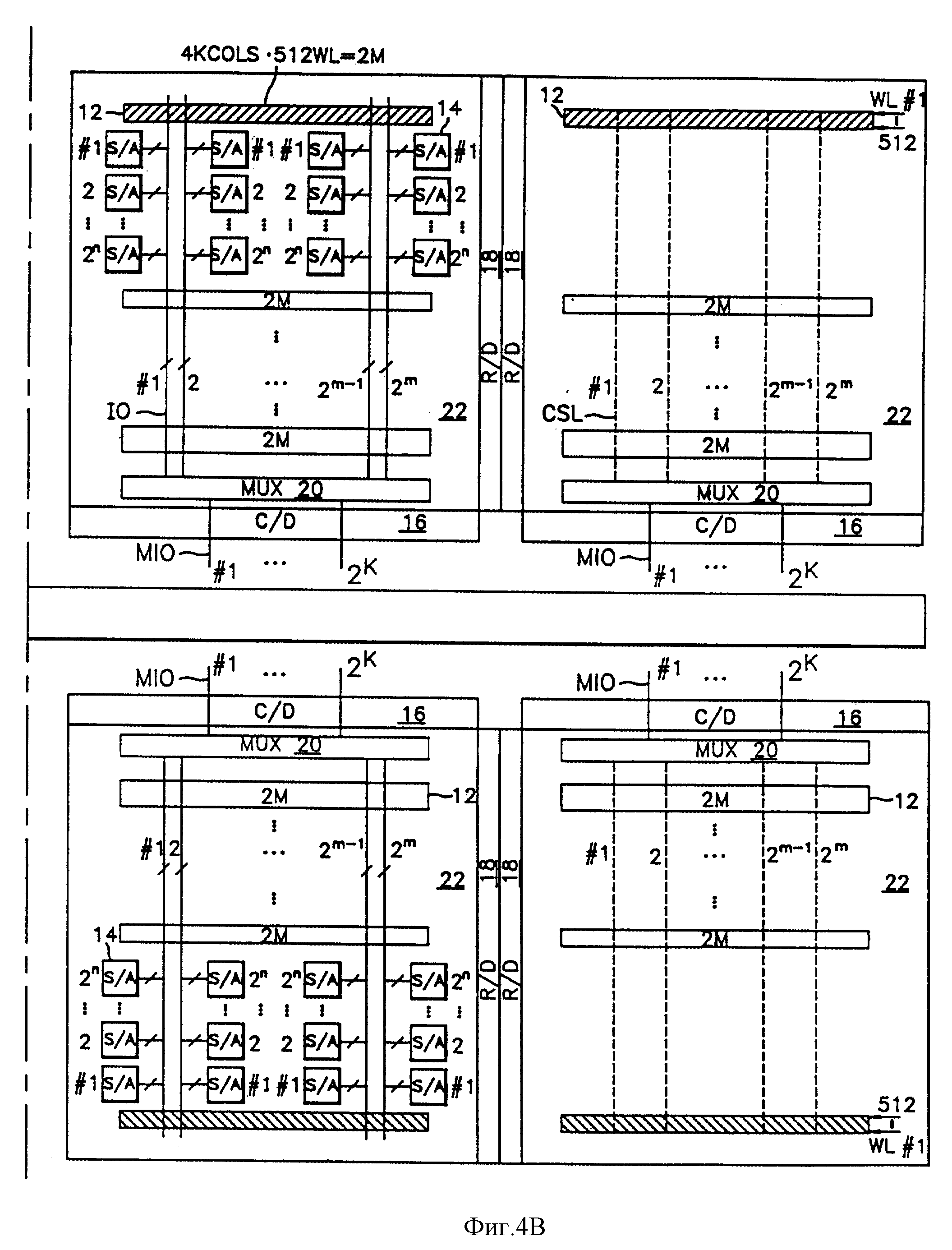

фиг. 4 - блок-схема, иллюстрирующая конфигурацию архитектуры кристалла с мультишиной ввода-вывода устройства полупроводниковой памяти в соответствии с

принципами настоящего изобретения, причем фиг. 4 состоит из фиг. 4A и 4B, расположенных параллельно;

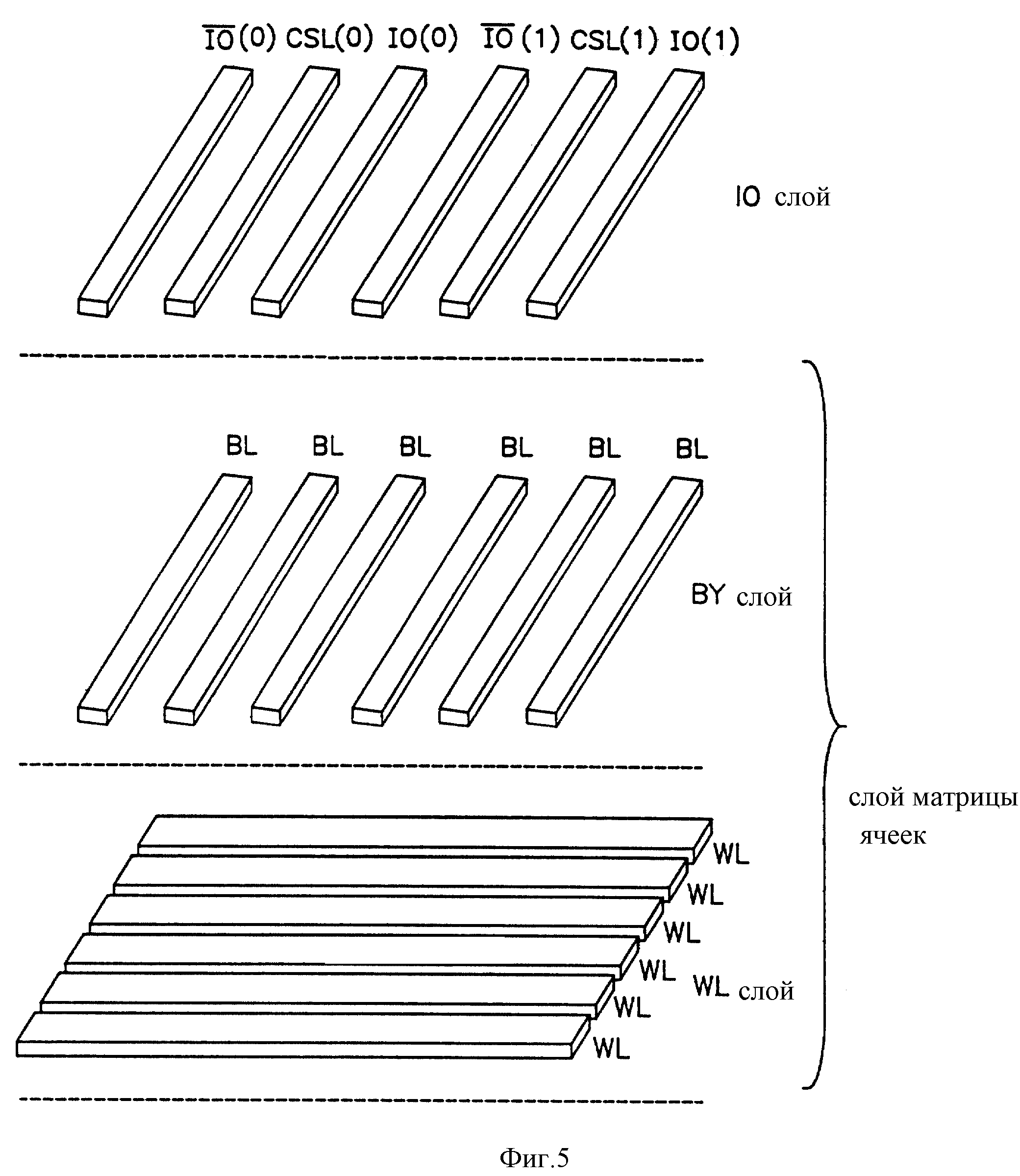

фиг. 5 - иллюстрация примера реализации способа расположения шин ввода-вывода данных и шин

выбора столбца фиг. 4;

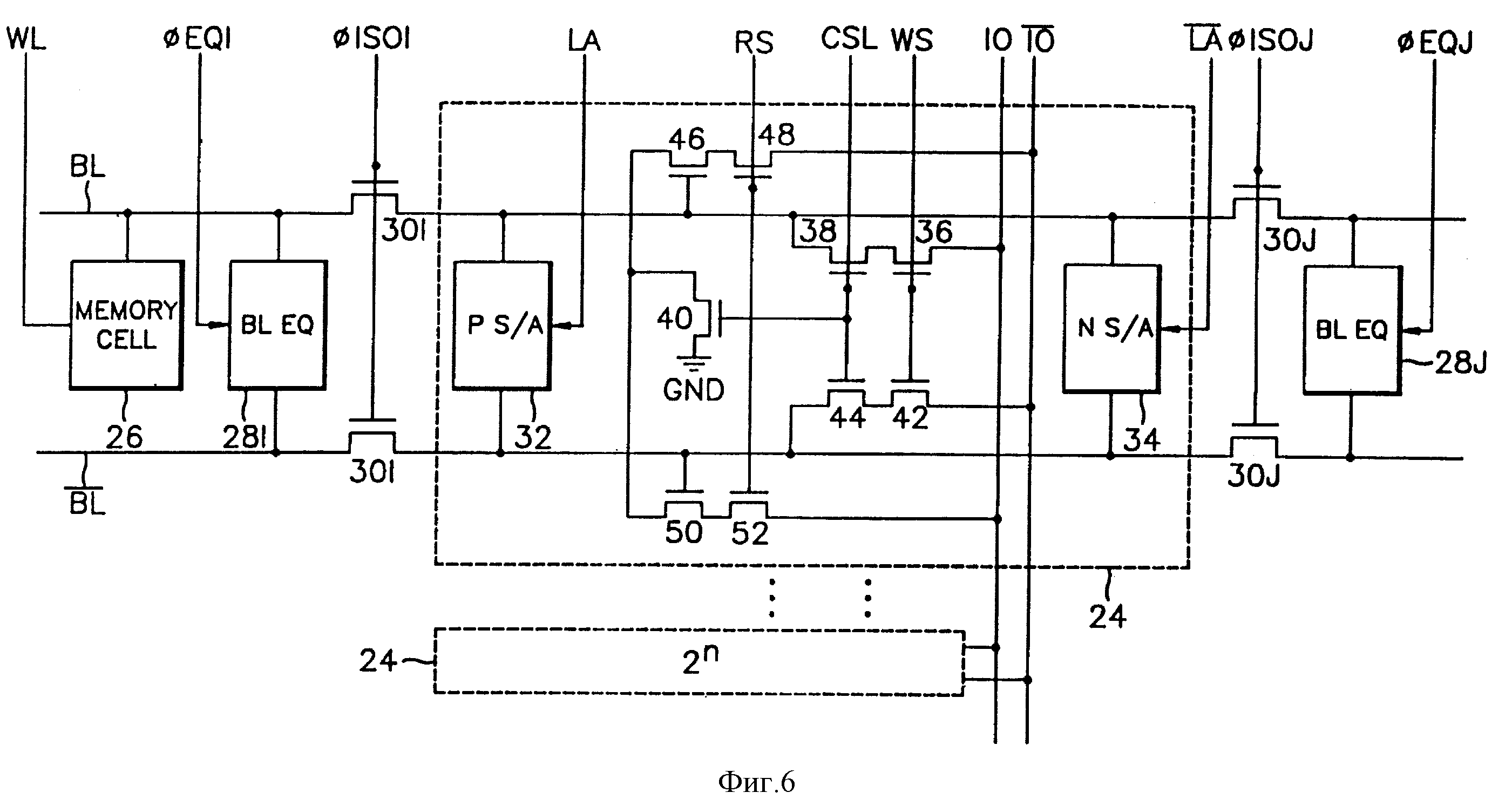

фиг. 6 - детальная схема, иллюстрирующая вариант реализации схемы управления столбцами в архитектуре кристалла на фиг. 4;

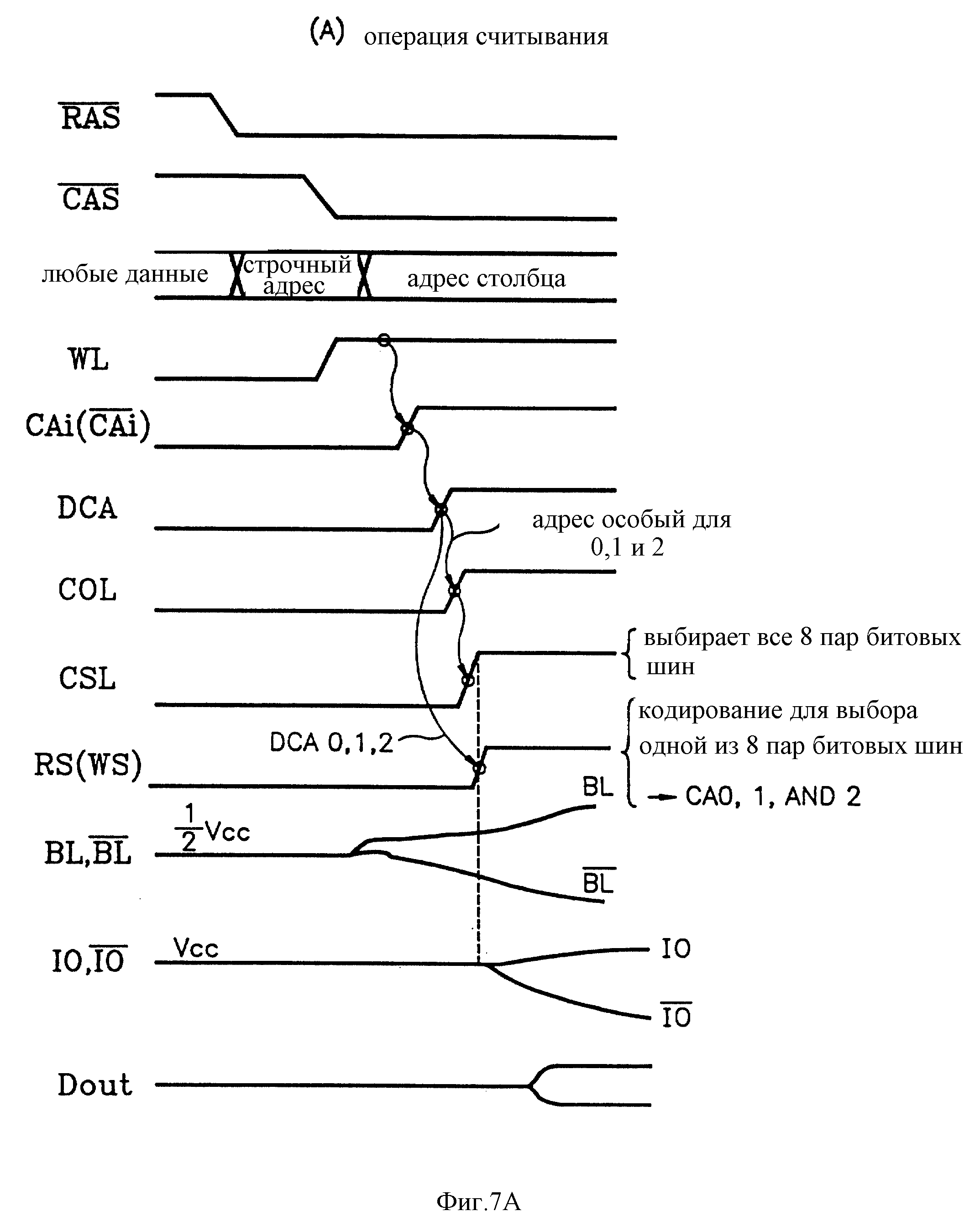

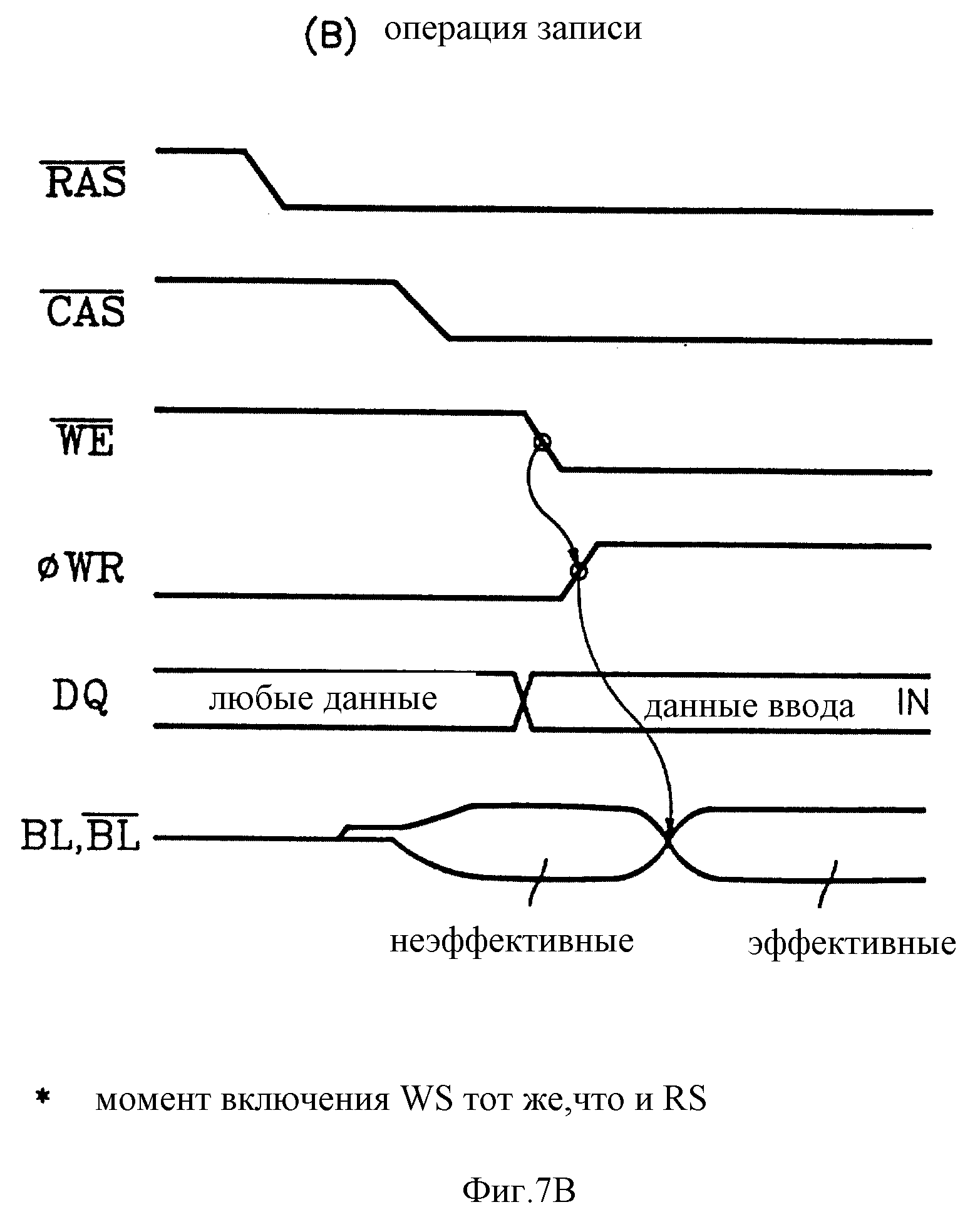

фиг. 7A и 7B - временные диаграммы,

иллюстрирующие операции считывания и записи, выполняемые схемой считывания битовой шины 24 фиг. 6;

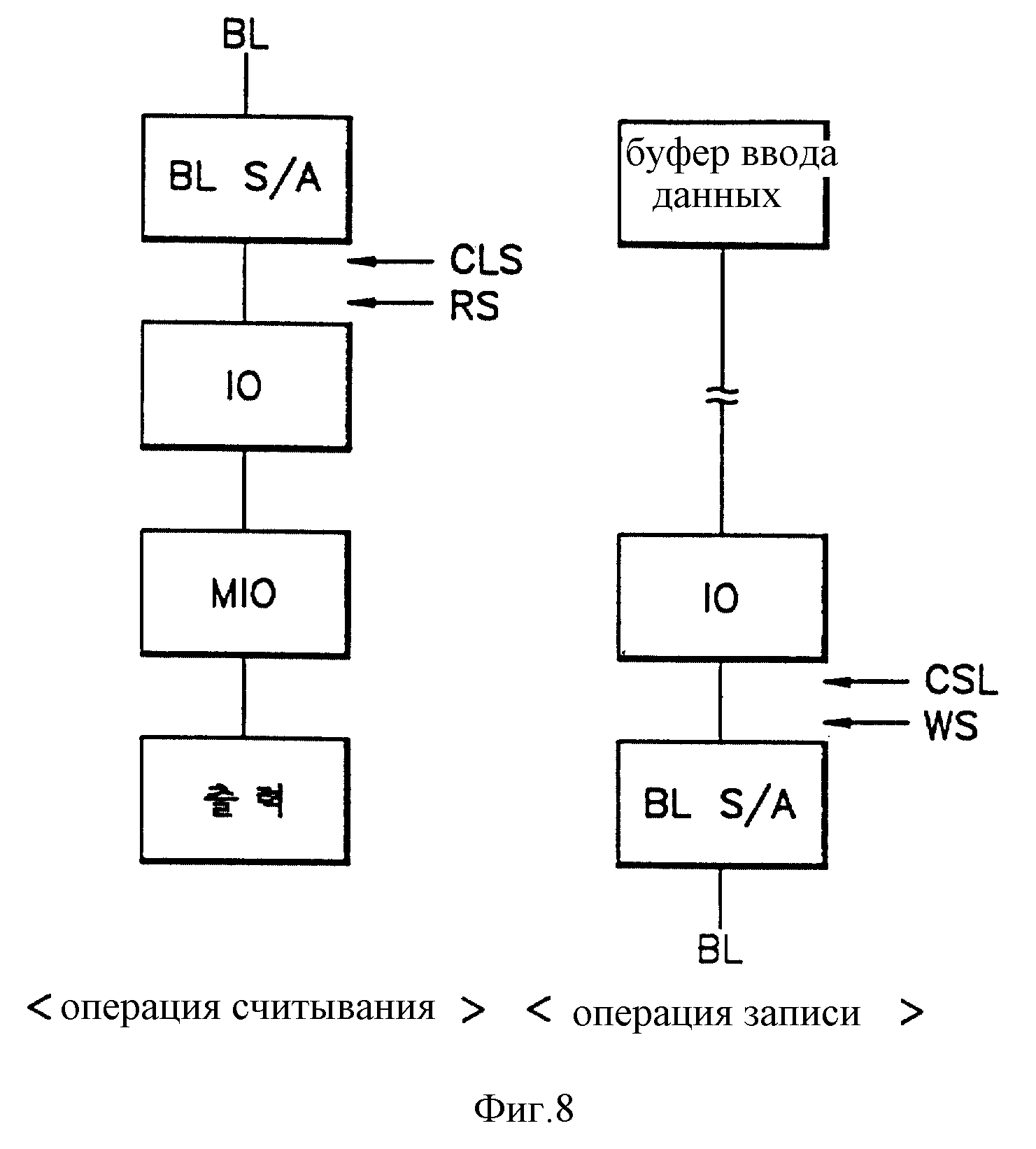

фиг. 8 - блок-схема, иллюстрирующая пути ввода-вывода данных на фиг. 6;

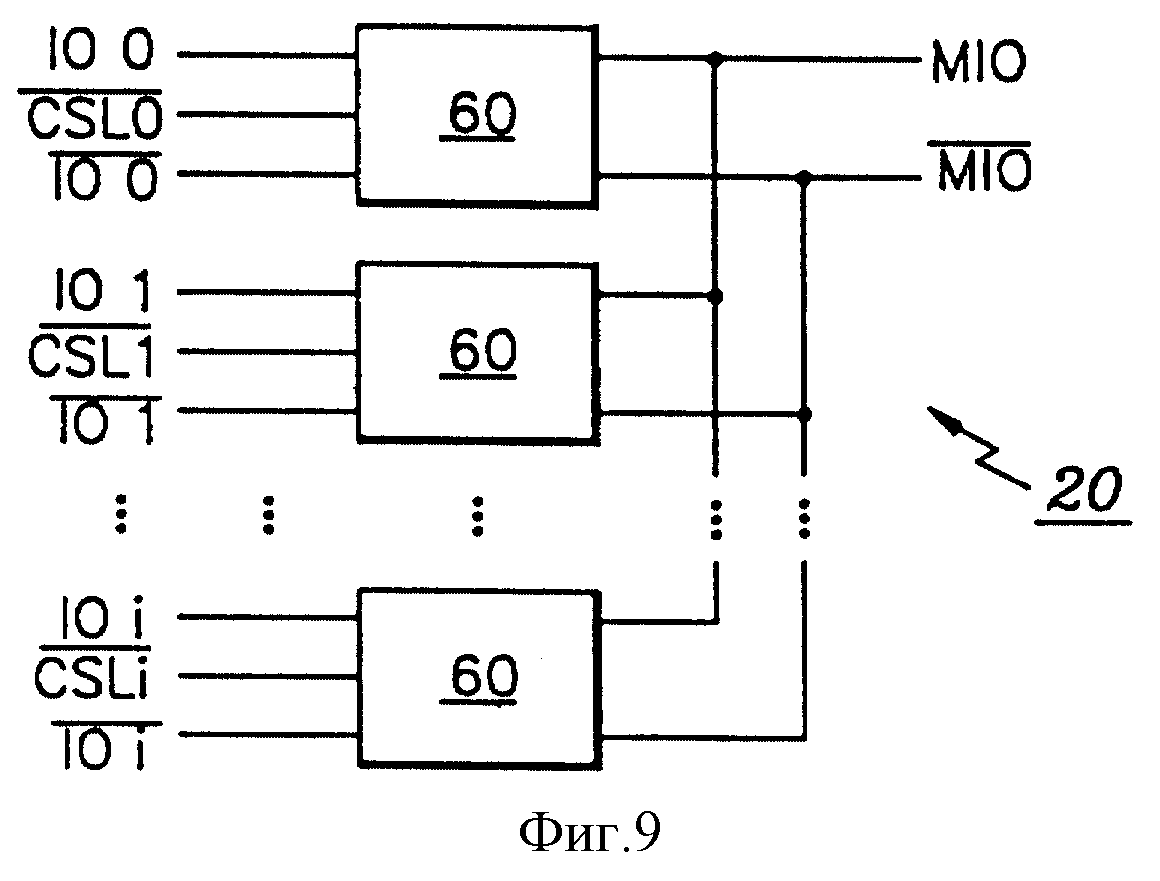

фиг. 9

- блок-схема, иллюстрирующая вариант реализации мультиплексора 20 на фиг. 4;

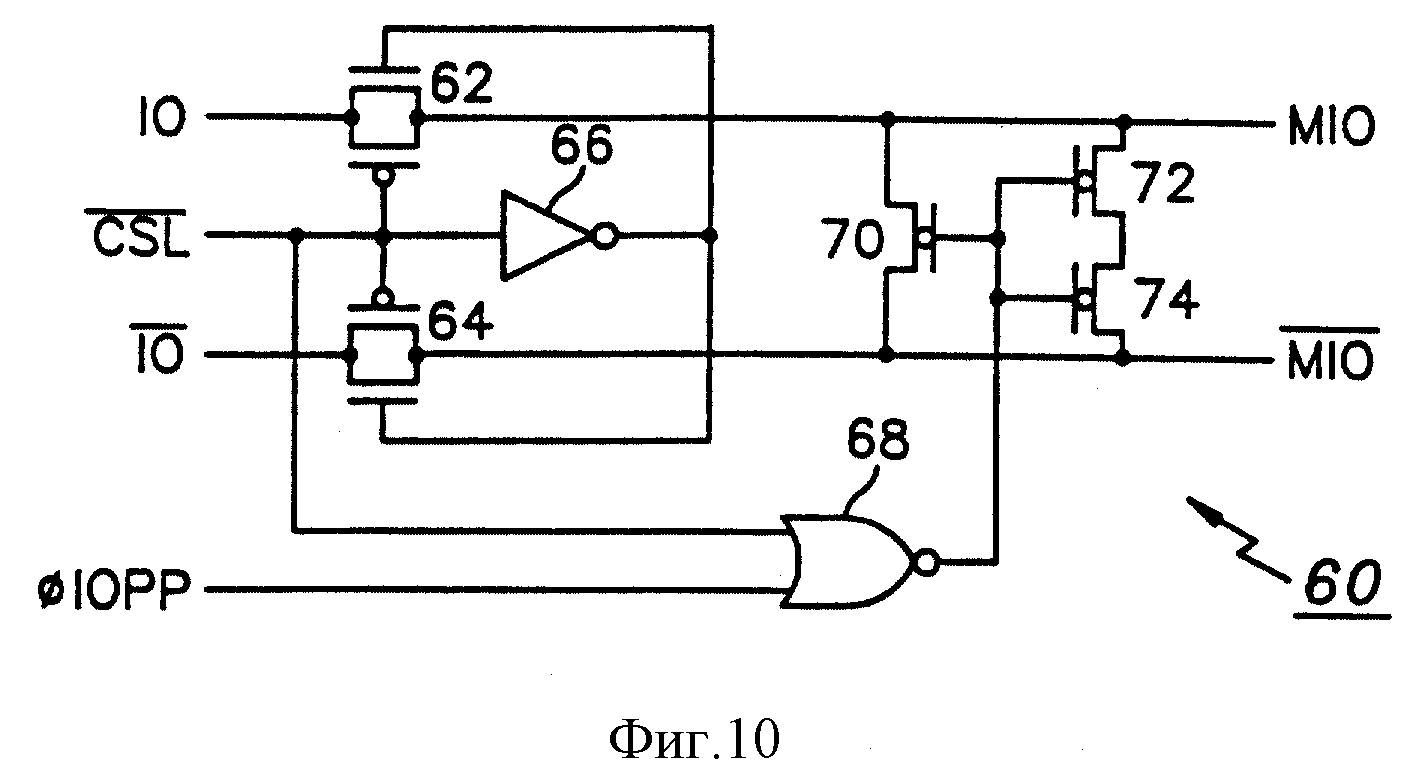

фиг. 10 - схема, являющаяся иллюстрацией варианта реализации единичного мультиплексора 60 в мультиплексоре 20 на

фиг. 9; и

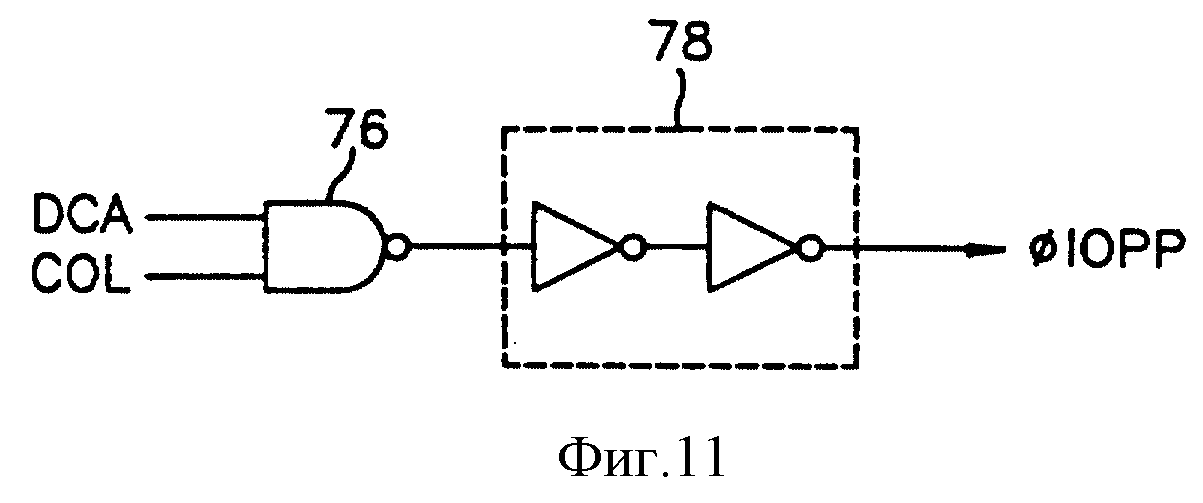

фиг. 11 - вариант схемной реализации генерирования сигнала ⌀ IOPP, поступающего на мультиплексор 20 фиг. 10.

Детальное описание предпочтительных вариантов реализации.

В последующем описании ряд конкретных деталей, таких как вертикальная структура шин ввода-вывода, схема считывания битовой шины, мультиплексор и т. д. , введены для того, чтобы обеспечить всестороннее понимание настоящего изобретения. Специалистам должно быть понятно, что могут быть предложены и другие варианты реализации настоящего изобретения без этих частных деталей, либо с альтернативными частными деталями.

Используемый здесь термин "единичная матрица" относится к матрице ячеек, которая может быть активизирована посредством одной словной шины. Термин "субматрица" используется для описания матрицы ячеек, которая может быть отобрана одной строчной группой декодеров и одной группой декодеров столбца, причем такая субматрица состоит из множества единичных матриц, имеющих общую шину ввода-вывода данных, подсоединенную к одной группе мультиплексоров.

Фиг. 4 представляет блок-схему, иллюстрирующую конфигурацию архитектуры кристалла, имеющую мультишину ввода-вывода устройства полупроводниковой памяти в соответствии с принципами настоящего изобретения, причем эта фигура состоит из фиг. 4A и 4B, расположенных в кристалле параллельно. Последующее описание архитектуры на фиг. 4A, 4B проводится в сравнении с известной архитектурой кристалла, показанной на фиг. 1. На фиг. 4 представлена архитектура нового кристалла согласно принципам настоящего изобретения, где в качестве варианта реализации рассматривается DRAM емкостью 256 М. На фигуре имеется четыре банка, два из которых размещены в верхней и нижней частях фиг. 4A, а два других размещены в верхней и нижней частях фиг. 4B. Цифровая ссылка 22 обозначает одну субматрицу, а 12 обозначает одну единичную матрицу. Как показано на фигуре, в банке находятся две субматрицы 23, а в одной субматрице 12 содержится 16 единичных матриц 12. Одна единичная матрица 12 составляет здесь 2 М (М равно 220), одна субматрица 22 содержит 32 М, а один банк содержит 64 М. В то же время строчный декодер 18 расположен в вертикальном направлении по отношению к длине кристалла (посредством него 64 М делится на 32 М), а активизация ячеек памяти, как показано на фиг. 4, производится по направлению словных шин. Таким образом, активизируются единичные матрицы, находящиеся по отношению одна к другой на одной и той же шине вдоль кристалла.

В рассмотренной выше конфигурации битовые шины, шины ввода-вывода данных и шины выбора столбца соответственно располагаются перпендикулярно словным шинам. Для двух смежных субматриц 22 в одном из банков на фиг. 4A или 4B на одной матрице показаны только шины ввода-вывода данных 10, а на другой показаны только шины выбора столбца CSL. Это сделано для облегчения понимания конфигурации шин ввода-вывода 10 и шин выбора столбца CSL. Каждая субматрица 22 имеет одно и то же количество шин ввода-вывода данных 10 и шин выбора столбца CSL, что показано на фигуре. В то же время для того, чтобы избежать взаимного влияния сигналов, желательно, чтобы шины выбора столбца, а также шина ввода-вывода данных 10 и комплементарная шина ввода-вывода данных

Здесь и далее обсуждается способ достижения высокой производительности в архитектуре кристалла, построенной в соответствии с настоящим изобретением по вышеописанной конфигурации. Единичные матрицы 12, как базовые блоки, образуют субматрицу 22 на 32 М, состоящую из 16 наборов из 128 К блоков, включающих 512 словных и 512 битовых шин (то есть, 256 пар битовых шин). Одна единичная матрица 12 включает 4096 (256 столбцов Х 16) пар битовых шин. Здесь в случае выполнения операции обновления данных блоком 16 K в одном банке на 64 М активизируется одна словная шина и матрица 2 М, а количество шин ввода-вывода данных в матрице 2 М составит: Если 2n пар битовых шин подсоединено к одной шине ввода-вывода, то образуется 4096/2n (равно 2m) пар шин ввода-вывода. Если через мультиплексор 20 объединяется заранее определенное количество шин ввода-вывода, может быть получено число 2k главных шин ввода-вывода M10 (в виде пар). Другими словами, в момент активизации сигнала строчного адреса

Фиг. 5 демонстрирует пример реализации способа расположения шин ввода-вывода данных и шин выбора столбца фиг. 4 и полезна для уяснения архитектуры, показанной на фиг. 4. На фиг. 5 каждая из шин выбора столбца CSL располагается между каждой из шин ввода-вывода данных 10 и каждой из комплементарных шин ввода вывода данных

На фиг. 6 представлена детальная схемная реализация варианта управления столбцами, то есть, схема считывания битовой шины архитектуры кристалла на фиг. 4. На фиг. 6 схема считывания битовой шины, выделенная пунктирным блоком 24, непосредственно связана с операцией считывания битовой шины. В конфигурации схемы считывания битовой шины 24 усилитель считывания состоит из усилителя считывания p (положительного)-типа 32 и усилителя считывания n (отрицательного)-типа 34, которые установлены на битовых шинах BL и

В то же время, кроме описанных выше элементов, имеется ячейка памяти 26, которая выбирается посредством активизации словной шины WL, схема выравнивания 281 для выравнивания уровня сигналов левых битовых шин BL и

Объяснение таких операций, как операции считывания и записи данных в ячейке, выполняемых схемой считывания битовой шины 24, будет подробно дано со ссылками на фиг. 7A и 7B.

Во-первых, хорошо известно, что при выполнении операции считывания (фиг. 7A) строчный адрес и адрес столбца вводятся синхронно с активизацией строб-сигнала строчного адреса

Поскольку в единичную матрицу 12 включено 16 базовых блоков 128 К и в то же время количество главных шин ввода-вывода данных M 10, передающих данные на один базовый блок, равно 4, через 64 главные шины ввода-вывода данных M 10 можно получить 64 бита данных в одной субматрице 22 (см. фиг. 4).

С другой стороны, при выполнении операции записи (фиг. 7B), когда определенные данные принимаются через буфер ввода данных (не показан) извне кристалла и затем передаются на главную шину ввода-вывода M 10 или

Фиг. 8 - блок-схема иллюстрирующая путь ввода-вывода данных фиг. 6, где схематически показаны процессы выполнения операций считывания и записи.

Если архитектура построена в соответствии с принципом настоящего изобретения, ясно, что для достижения высокой производительности 256 бит локальная шина ввода-вывода данных, показанная на фигуре, не потребуется. Следовательно, решение проблемы загрузки шин может быть найдено путем использования только главных шин ввода-вывода данных и шин ввода-вывода данных, что снижает остроту проблемы загрузки по сравнению с вариантом на фиг. 2. Кроме того, архитектура, построенная в соответствии с принципом настоящего изобретения, имеет очевидные преимущества с точки зрения повышения скорости записи и уменьшения размеров устройства памяти высокой плотности по сравнению с архитектурой на фиг. 2. В известном прототипе в направлении столбцов расположены пять сигнальных шин, например, локальная шина ввода-вывода данных LOCAL I/O, субшина ввода-вывода данных SUB 10, сигнальная шина включения записи YWRITE, сигнальная шина включения считывания YREAD и шина выбора столбца CSL. Однако в настоящем изобретении установлены три сигнальные шины, например, главная шина ввода-вывода M 10, шина ввода-вывода 10 и шина выбора столбца CSL. Это способствует более высокой степени интеграции устройства полупроводниковой памяти. Также, если архитектура построена в соответствии с принципом настоящего изобретения, словная шина WL, шина выбора считывания RS и шина выбора записи WS устанавливаются по направлению вдоль устройства памяти, а битовая шина, шина ввода-вывода данных 10 и шина выбора столбца CSL устанавливаются в направлении, перпендикулярном словной шине, позволяя тем самым эффективно принимать и генерировать множество бит данных. Как было описано ранее, в случае соединения 2n пар шин ввода-вывода данных с парой шин ввода-вывода данных, потребуется 2m пар шин ввода-вывода данных и 2m пар шин выбора столбца соответственно. Таким образом, базовый блок согласно настоящему изобретению имеет компоновку, в которой пара шин ввода-вывода данных и одна шина выбора столбца регулярно располагаются в направлении, перпендикулярном словной шине. Это приводит к уменьшению площади разводки, необходимой для извлечения множества данных ввода-вывода.

Между тем структура для мультиплексирования шин ввода-вывода данных 10 и главных шин ввода-вывода данных M 10 будет описана со ссылками на фиг. 9. На этой фигуре показан вариант реализации мультиплексора 20 фиг. 4, в котором множество отдельных мультиплексоров 60 входит в состав единого мультиплексора 20. Поскольку архитектура на фиг. 4 построена для вывода 256 бит данных, здесь можно принять, что один единичный мультиплексор 60 приходится на восемь пар шин ввода-вывода.

На фиг. 10 показана схема, иллюстрирующая вариант реализации единичного мультиплексора 60 в мультиплексоре 20 фиг. 9. При такой конфигурации имеется передающий ключ 62, установленный между шиной ввода-вывода данных 10 и главной шиной ввода-вывода данных M 10, который пропускает сигнал выбора столбца CSL и его комплементарный сигнал

На фиг. 11 показан вариант реализации схемы для генерирования сигнала ⌀ IOPP, который вводится в мультиплексор 20 фиг. 10. На фиг. 11 процессы активизации входных сигналов DSA и COL были описаны со ссылками на фиг. 7.

Хотя здесь был показан и описан предпочтительный вариант реализации настоящего изобретения, специалистам должно быть понятно, что допустимы изменения по форме и в деталях, если не приводящие к отклонению от существа и объема настоящего изобретения.

Как было пояснено ранее, устройство полупроводниковой памяти и способ расположения в нем сигнальных шин, которые воплощены с помощью соответствующей архитектуры кристалла, позволяют достигнуть высокой производительности без увеличения размеров кристалла. Кроме того, устройство полупроводниковой памяти и способ расположения в нем сигнальных шин имеют преимущества, заключающиеся в том, что компоновка шин как в направлении столбцов, так и в направлении строк может быть произведена простым образом посредством активизации матрицы в продольном направлении кристалла, а острота проблемы загрузки шин может быть снижена, так как потребуются только две шины ввода-вывода данных, служащих для передачи данных между матрицей ячеек и терминалами ввода-вывода кристалла. Кроме того, устройство полупроводниковой памяти и способ расположения в нем сигнальных шин имеет преимущество, заключающееся в том, что требуемый высокий уровень производительности может быть достигнут путем изменения способов подсоединения битовых шин и шин ввода-вывода данных, а также шин ввода-вывода данных и главных шин ввода-вывода данных.

Реферат

Изобретение относится к устройству полупроводниковой памяти. Техническим результатом является высокая производительность указанного устройства без использования отдельной локальной шины ввода-вывода для соединения битовой шины и главных шин ввода-вывода. Устройство содержит банки памяти, множество битовых шин, шин ввода-вывода данных (сигнальных шин), шин выбора столбца (сигнальных шин), словных шин, главную шину ввода-вывода данных, транзисторы считывания, транзисторы для записи, мультиплексор. Способ описывает расположение в нем сигнальных шин. 2 с. и 1 з.п. ф-лы, 13 ил.

Комментарии