Система для восприятия и воспроизведения последовательности анимированных видеоизображений в реальном масштабе времени - RU2140668C1

Код документа: RU2140668C1

Чертежи

Описание

Изобретение относится к системе для восприятия и воспроизведения последовательности анимированных изображений в реальном масштабе времени, содержащей, по меньшей мере, одну ступень восприятия данных, состоящую из блока памяти и ступени считывания/записи, состоящей в виде экрана или контроллера изображений, управляемого блоком центрального процессора для считывания и записи цифровой информации в блоке памяти, соответствующем, по меньшей мере, одной последовательности изображения, и ступени воспроизведения данных.

В общем случае такая система предназначена для восприятия, хранения и воспроизведения в реальном масштабе времени большого количества изображений высокого качества. При этом предполагается, что изображение состоит из набора точек или "пикселей", причем каждый пиксель закодирован 16-ю или 32-мя битами и что термин "реальный масштаб времени" означает возможность переключения целых изображений 25-30 раз в секунду с частотой кадров электронного изображения.

Для этого система должна иметь большой объем памяти, чтобы обеспечить необходимую емкость хранимой информации этого типа.

В системе восприятия и воспроизведения указанного выше типа устройство записи/считывания, образованное контроллером экрана в ступени восприятия данных, использует макрокоманды, выдаваемые центральным процессором для управления данными в блоке памяти, в частности, в случае операций считывания, записи и обновления. Параллельно ступень воспроизведения должна быть также в состоянии управлять доступом к блоку памяти, чтобы считывать с него информацию, соответствующую, по меньшей мере, одной последовательности изображений и затем воспроизводить эту последовательность на экране в аналоговой форме.

Ступень восприятия данных и ступень воспроизведения данных должны таким образом обе иметь доступ к блоку памяти, даже если они не способны осуществлять это одновременно на практике. В настоящее время не существует устройств памяти, обеспечивающих одновременный доступ, и поэтому применяются различные решения проблемы доступа к памяти.

Первое решение состоит в использовании арбитражной системы, устанавливающей последовательность и выделяющей часть полосы пропускания блока памяти (т. е. полное количество битов, которое может быть считано или записано за единицу времени) операциям считывания, записи и обновления, которые выполняются экранным контроллером ступени восприятия данных, и передающей остальную часть полосы пропускания ступени воспроизведения данных, чтобы позволить ей считывать последовательность изображений и воспроизводить ее на экране.

Второе решение состоит в использовании блока памяти, образованного динамическими видеоячейками оперативной памяти, имеющими специальный признак наличия сдвигового регистра, который работает в качестве интерфейса между блоком памяти и ступенью воспроизведения данных. Информация, обмениваемая между блоком памяти и ступенью воспроизведения данных, полностью проходит через этот регистр. В такой системе загрузка и/или разгрузка сдвигового регистра производится во время обратного хода луча развертки на экране, так что большая часть полосы пропускания блока памяти используется для управления данными в блоке памяти со стороны контроллера экрана.

Таким образом, оба описанные выше решения решают проблему двойного доступа к блоку памяти посредством попеременного доступа для управления данными в блоке памяти и доступов, нужных для графического воспроизведения данных, записанных в этот блок памяти.

Указанные решения приводят к системам с ограниченными возможностями в плане используемой мощности воспроизведения на экране, т.е. возможности сделать изображения движущимися ограничены. В таких системах время доступа в режиме считывания или режиме записи для управления записанными данными или данными, подлежащими записи в блок памяти, сравнительно велико, и в результате операции записи данных, связанные с записью новых последовательностей изображений в блок памяти, производятся с частотой, меньшей частоты воспроизведения точек изображения на экране (частота "пикселей"). На практике, такие системы работают на частотах порядка 3000000-4000000 пикселей в секунду, что сильно ограничивает возможности воспроизведения подвижных изображений в реальном масштабе времени.

Кроме того, технология оперативной памяти видеотипа является дорогостоящей по сравнению со стандартной динамической памятью, производимой в массовых масштабах.

Известна система для восприятия и воспроизведения последовательности анимированных изображений в реальном масштабе времени, содержащая по меньшей мере одну ступень восприятия данных, образованную блоком памяти и устройством считывания/ записи, выполненным в виде контроллера экрана или изображения, подключенного к центральному блоку управления, и ступень воспроизведения данных (см., например, заявку Японии 63-072277).

Согласно указанной заявке Японии, контроллер предназначен для поочередного переключения обоих блоков памяти с целью записи и считывания данных, так что контроллер не может одновременно считывать и записывать в двух блоках памяти.

В основу изобретения поставлена задача усовершенствования методов двойного доступа к блоку памяти и создания системы, обеспечивающей повышенное качество в плане мощности воспроизведения при меньшей, по сравнению с существующими системами, стоимости.

Поставленная задача решается тем, что предложена система для восприятия и воспроизведения последовательности анимированных изображений в реальном масштабе времени, содержащая по меньшей мере одну ступень восприятия данных, образованную блоком памяти и устройством считывания/ записи, выполненным в виде контроллера экрана или изображения, подключенного к центральному блоку управления, причем блок памяти ступени восприятия данных состоит, по меньшей мере, из двух автономных блоков памяти, один из которых связан с контроллером экрана или изображения, в которой, согласно изобретению, каждый из остальных автономных блоков памяти связан с соответствующим одним из дополнительно введенных контроллеров экрана или изображения, при этом автономные блоки памяти ступени восприятия данных с соответствующими контроллерами экрана или изображения выполнены с возможностью предназначения одного автономного блока памяти с соответствующим контроллером экрана или изображения для ступени восприятия данных, а другого автономного блока памяти с соответствующим контроллером экрана или изображения для ступени воспроизведения данных.

Целесообразно, чтобы ступень воспроизведения содержала по меньшей мере одно устройство преобразования для преобразования цифровых данных, взятых из автономного блока памяти и соответствующих последовательности изображений, в аналоговый или цифровой сигнал по телевизионному стандарту.

Полезно, чтобы каждый автономный блок памяти состоял из стандартных динамических устройств памяти с произвольным доступом синхронного или асинхронного типа.

Полезно также, чтобы каждый контроллер изображения был включен между автономным блоком памяти, с которым он связан, и центральным блоком управления и соединен с устройством преобразования.

Выгодно, чтобы контроллеры напрямую были соединены с периферийным устройством, выполненным в виде вспомогательного ЗУ или ЗУ на жестком диске.

Целесообразно, чтобы один из автономных блоков памяти ступени восприятия данных был подключен через относящийся к нему контроллер к вспомогательному ЗУ или блоку на жестком диске и параллельно другой автономный блок памяти ступени восприятия через относящийся к нему контроллер был подключен к ступени воспроизведения.

Такая конфигурация ведет к тому, что каждый контроллер образует точку пересечения, или переключающее устройство в

смысле считывания и записи относительно четырех отдельных операционных блоков, являющихся периферийными для контроллера, а именно:

блока памяти типа DRAM,

блока центрального

процессора,

вспомогательного блока памяти типа FIFO или SRAM или блока памяти с твердым диском и

аналого-цифрового и цифроаналогового преобразователя ступени воспроизведения.

Система восприятия и воспроизведения по изобретению позволяет улучшить качество анимированных изображений при снижении стоимости оборудования.

Такая система делает возможным осуществлять высококачественную анимацию на практически всей площади экрана со скоростью порядка 12000000 пикселей в секунду, когда графическая анимация может представлять движения частей изображения или многих графических объектов вдоль осей плоскости изображения относительно фона, который может быть как неподвижным, так и движущимся.

Дополнительно предлагаемая система сделала возможным найти альтернативу использованию видеопамяти малой емкости и прежде всего, высокой стоимости, на основе использования стандартных блоков видеопамяти и без введения специальных аппаратурных ограничений.

Другим преимуществом заявленного изобретения является возможность оборудовать систему памятью, имеющей минимальную емкость 256 мегабайт (MB), указанная память может быть установлена, в частности, на печатной плате с максимальной площадью для введения в микрокомпьютер, например, по стандартам ISA, MCA, EISA или NUBUS.

В дальнейшем изобретение поясняется

описанием вариантов его выполнения со ссылками на чертежи, на которых:

фиг. 1 изображает упрощенную блок-схему системы по известному уровню техники для восприятия и воспроизведения

последовательностей изображений,

фиг. 2 - упрощенную блок-схему системы, являющейся воплощением изобретения для восприятия и воспроизведения последовательностей изображений, и

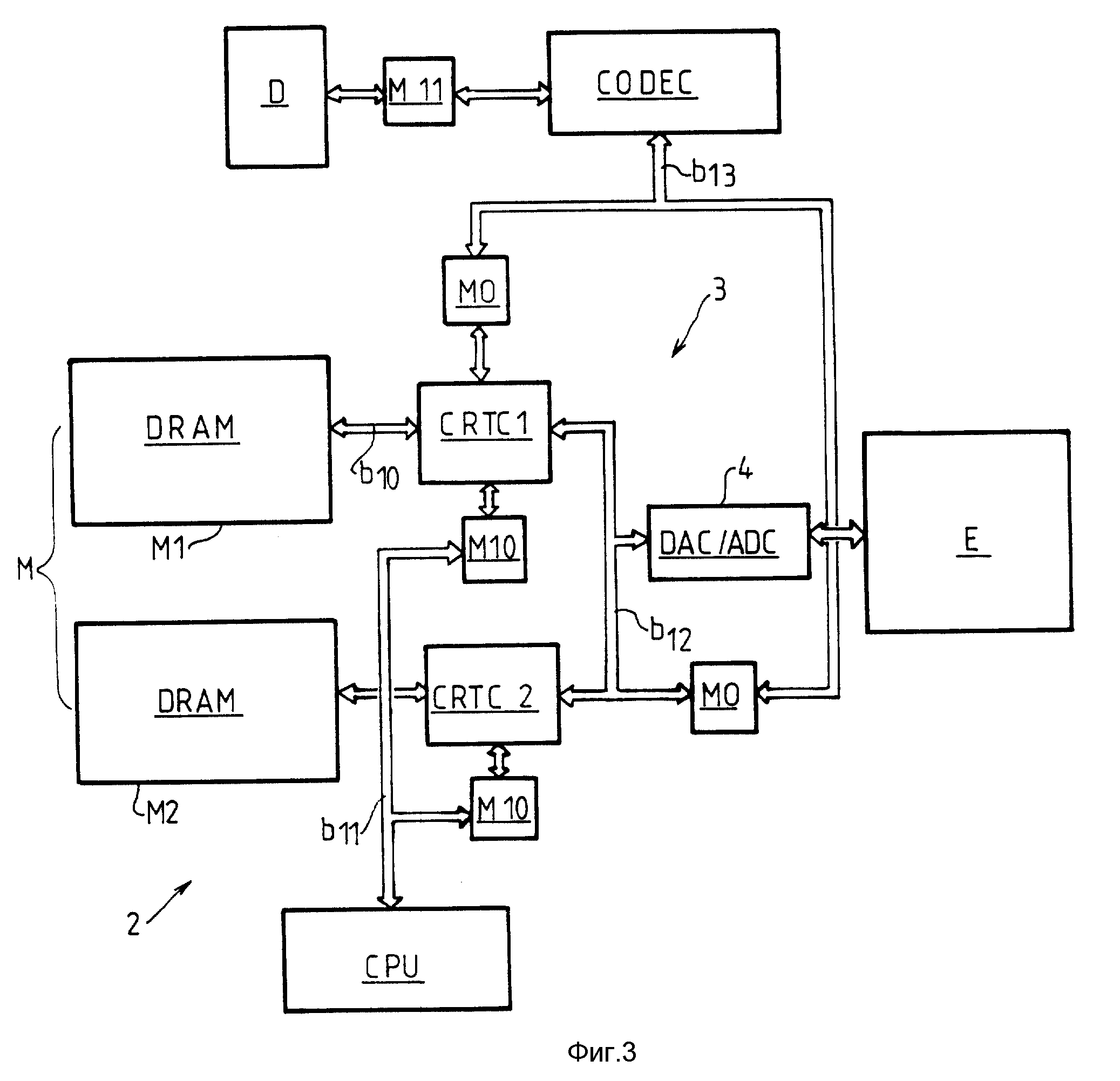

фиг. 3

- упрощенную блок-схему варианта выполнения изобретения.

Система по известному уровню техники изображена на фиг. 1 и содержит ступень 2 восприятия данных, а также ступень 3 для графического воспроизведения этих данных.

Ступень 2 восприятия данных содержит блок памяти М и устройство считывания/записи, состоящее из контроллера экрана CRTC, управляемого центральным блоком управления CPU. Блок памяти М выполнен на видеопамяти с произвольным доступом VRAM, связанным со сдвиговым регистром RG. Контроллер экрана CRTC сообщается с блоком памяти М по интерфейсной шине b1 для осуществления операций считывания/записи в памяти типа VRAM, и с центральным блоком управления CPU по шине b2, и с интерфейсом ввода/вывода, связанным с шиной b2, для осуществления соединения с периферийной аппаратурой (не показана).

Ступень 3 воспроизведения данных содержит устройство преобразования 4, в которое входит преобразователь цифра-аналог DAC и преобразователь аналог-цифра ADC. Устройство преобразования 4 шиной b3 соединено со сдвиговым регистром RG блока памяти М и шиной b4 с экраном телевизионного типа E с разверткой времени.

Указанная система поочередно распределяет блок памяти M между ступенью восприятия данных 2 и ступенью воспроизведения 3 для воспроизведения информации со всеми недостатками, которые вытекают из такой очередности.

Система по изобретению для восприятия и воспроизведения анимированной последовательности изображений в реальном масштабе времени, как показано на фиг. 2, содержит также ступень 2 для восприятия данных в цифровой форме и ступень 3 для графического воспроизведения этих данных.

Ступень 2 восприятия данных содержит блок памяти M, который разделен на, по меньшей мере, два автономных блока памяти M1 и M2, каждый из которых состоит из стандартного динамического устройства памяти с произвольным доступом DRAM, которое может быть синхронного или асинхронного типа. Каждый из блоков памяти M1 и M2 связан с устройством считывания/записи, являющимся экранным контроллером или контроллером изображения CRTC1 или CRTC2. Два контроллера управляются от центрального блока управления CPU. Каждый блок памяти M1 и M2 соединен соответствующей шиной b10 с соответствующим контроллером CRTC1 или CRTC2. Центральный блок управления CPU соединен шиной b11 с обоими контроллерами CRTC1 и CRTC2.

Ступень 3 воспроизведения данных в данном примере выполнения того же общего типа, что и описанная согласно фиг. 1, и содержит устройство преобразования 4 цифра-аналог DAC и/или аналог-цифра DAC вместе в экраном E. Устройство преобразования 4 соединено шиной b12 с обоими контроллерами CRTС1 и CRTC2. Устройство преобразования 4 используется, например, для преобразования цифровых данных, снимаемых с блока памяти и соответствующих последовательности изображений в аналоговый или цифровой телевизионный сигнал по соответствующему стандарту.

Дополнительно, два контроллера CRCT1 и CRСT2 соединены шиной b15 с периферийным элементом, таким как вспомогательная память MO с целью прямого приема данных, получающихся при компандировании последовательностей изображений, подлежащих воспроизведению.

Таким образом, при работе возможно разместить один из блоков памяти, например, блок M1 и относящийся к нему контроллер CRTC1 в ступени 2 восприятия данных с целью осуществления операций над данными, которые были записаны или которые еще подлежат записи в блок памяти M1, поочередно с другим блоком памяти M2 и относящимся к нему контроллером CRTC2, которые помещаются в ступени 3 воспроизведения данных для графического воспроизведения на экране E последовательностей изображений, которые записаны в блоке памяти M2.

При функционировании ступень 3 воспроизведения данных может иметь постоянный доступ к одному или другому из блоков памяти M1 или M2 без доступа к одному блоку памяти поочередно во времени ступени восприятия 2 и ступени воспроизведения 3.

Таким образом, в то время как последовательности изображений воспроизводятся и анимируются на экране E на основе цифровых данных, взятых с одного из блоков памяти, новые последовательности изображений могут записываться в другой блок памяти, прежде чем они будут воспроизведены и анимированы, что делает возможным обеспечить совершенную непрерывность анимации на экране.

На фиг. 3 приведен пример выполнения изобретения, позволяющий расширить возможности заявленного решения.

В данном варианте каждый из контроллеров CRTC1 и CRTC2 соединен с процессором CPU и через вспомогательную или буферную память M10, имеющую ширину 16 или 32 бита с двумя управляющими потоком информации в двух направлениях битами, например, для увеличения скорости процессирования, а также с вспомогательной или буферной памятью MO, причем две памяти MO соединены шиной b13 с кодирующе-декодирующим устройством CODEC, которое, в свою очередь, соединено с жестким диском D, т.е. с промежуточной вспомогательной или буферной памятью М11.

Таким образом, для операций компандирования - сжатия данных или экспандирования - расширения данных - последовательностей изображений, с применением межкадрового способа, подчиняющегося стандарту (например, MPEC I, MPEC II или CCITT H.261), используется устройство кодирования/декодирования CODEC, которое должно одновременно обрабатывать, по меньшей мере, три потока данных, так чтобы процессировать изображение i+1 на основе ранее процессированного изображения i.

В режиме компандирования последовательности изображений устройство кодирования-декодирования CODEC выполняет следующие операции: обрабатывает первый

входной поток данных - видеосигналов, которые оцифрованы и запомнены в плоскости или блоке памяти М1 контроллером CRTC1, причем указанный входной поток поступает от внешнего источника, например

видеокамеры;

обрабатывает второй входной поток данных - видеосигналов, которые оцифрованы и запомнены в блоке памяти М2 контроллером CRTC2, причем эти сигналы соответствуют предыдущему

изображению i, и

обрабатывает третий выходной поток оцифрованных сигналов, которые были компандированы и обработаны кодирующе-декодирующим устройством и которые позволяют преобразовать

изображение i+1 на основе изображения i, причем эти сигналы засылаются на твердый диск D.

В режиме экспандирования кодирующе-декодирующее устройство CODEC выполняет следующие

операции:

- обрабатывает первый входной поток, соответствующий потоку компандированных цифровых сигналов, считанных с твердого диска D;

- обрабатывает второй входной поток,

соответствующий оцифрованным сигналам, которые были экспандированы в предыдущем этапе и которые берут с одной или другой памяти М1 или М2, и подают на CODEC через контроллер экрана, связаны с

соответствующим блоком памяти М1 или М2, и

- обрабатывает третий выходной поток процессированных и экспандированных оцифрованных сигналов, соответствующих изображению i+1 и посылаемых на

другой контроллер потока для воспроизведения на экране.

Указанные операции компандирования и экспандирования значительно облегчаются наличием двух контроллеров CRTC1 и CRTC2.

Устройство может работать в противоположной последовательности в том смысле, что графические изображения не воспроизводятся, а берутся с экрана E для записи в блоки памяти М1 и М2 и последующего хранения их, например, во вспомогательной памяти.

Таким образом, ступень 3 воспроизведения данных может воспринимать данные, соответствующие последовательности изображений, и может хранить эти данные альтернативно в блоке памяти М1 или М2 через связанный с ним контроллер CRTC1 или CRTC2, а ступень 2 восприятия данных может считывать эти данные альтернативно с другого блока памяти М2 или М1 через связанный с ним контроллер CRTC2 или CRTC1 и хранить эти данные во вспомогательной памяти или в блоке памяти с твердым диском.

Оборудование для анимирования в реальном масштабе времени на телевизионном экране может использоваться, например, в диалоговых играх потребителями.

Реферат

Изобретение относится к вычислительной технике. Его использование в системах воспроизведения изображений позволяет повысить качество воспроизведения при меньшей стоимости системы. Система для восприятия и воспроизведения последовательности анимированных изображений в реальном масштабе времени содержит по меньшей мере одну ступень восприятия данных, образованную блоком памяти и устройством считывания/записи, выполненным в виде контроллера экрана или изображения, подключенного к центральному блоку управления, причем блок памяти ступени восприятия данных состоит по меньшей мере из двух автономных блоков памяти, один из которых связан с контроллером экрана или изображения. Технический результат достигается благодаря тому, что каждый из остальных автономных блоков памяти связан с соответствующим одним из дополнительно введенных контроллеров экрана или изображения, при этом автономные блоки памяти ступени восприятия данных с соответствующими контроллерами экрана или изображения выполнены с возможностью предназначения одного автономного блока памяти с соответствующим контроллером экрана или изображения для ступени восприятия данных. 5 з.п. ф-лы, 3 ил.

Комментарии