Устройство для определения оптимального периода технического обслуживания и ремонта изделия - RU182820U1

Код документа: RU182820U1

Чертежи

Описание

Полезная модель относится к вычислительной технике, в частности к контрольным устройствам и может быть использовано в научных исследованиях и технике, где необходимо определять время наступления постепенного отказа, оптимальный и очередной периоды регламентированного технического обслуживания и ремонта, и коэффициент готовности изделия по значениям как прямых, так и диагностических параметров, осуществляя стратегию ремонта по техническому состоянию.

Известно устройство для определения оптимального периода технического обслуживания изделия содержащее блок памяти, два блока деления блок нелинейности, два блока умножения, вычитатель, четыре элемента задержки, таймер, три сумматора, два компаратора, мультивибратор, элемент ИЛИ, три элемента памяти, три ключа, причем первый выход блока памяти соединен с первым входом второго блока деления, второй вход которого подключен к выходу второго блока умножения, первый и второй вход которого объединены и подключены к входу первого элемента задержки, входу таймера, первому входу интегратора, первому входу вычитателя, выход второго блока деления соединен с входом блока нелинейности, выход которого подключен к второму входу интегратора и второму входу первого блока умножения, первый вход которого подключен к второму выходу блока памяти, выход интегратора подключен к второму входу вычитателя и второму входу третьего сумматора, первый вход которого подключен к выходу второго сумматора, первому входу первого блока деления, входу четвертого блока задержки, второй вход второго сумматора соединен с входом с выходом вычитателя, первый вход второго сумматора подключен к выходу первого сумматора и первому входу первого компаратора, второй вход которого подключен к четвертому выходу блока памяти, первый и второй входы первого сумматора подключены к третьему выходу блока памяти и выходу первого блока умножения соответственно, второй вход первого компаратора подключен к четвертому входу блока памяти, первый вход первого блока умножения подключен ко второму выходу блока памяти, первый вход таймера соединен с управляющими входами первого, второго, третьего элементов памяти, первого, второго, третьего ключей, вторым входом триггера, выходом мультивибратора, второй вход таймера соединен с выходом второго элемента задержки, вход которого подключен к первому входу к первому входу триггера, вход которого соединен с пятым входом блока памяти, выход третьего сумматора подключен ко второму входу первого блока деления, выход которого подключен к входу третьего элемента задержки и второму входу второго компаратора, выход которого соединен с вторым входом элемента ИЛИ, выход которого подключен к входу мультивибратора, первый вход второго компаратора соединен с выходом третьего элемента задержки и входом второго элемента памяти, выход которого подключен к входу второго ключа, выход которого является вторым выходом устройства, выход вычитателя подключен к входу четвертого элемента задержки, выход которого соединен с входом третьего элемента памяти, выход которого подключен к входу третьего ключа, выход которого является третьем выходом устройства, выход первого элемента задержки соединен с входом первого элемента памяти, выход которого подключен к входу первого ключа, выход которого является первым выходом устройства [1].

Устройство позволяет определить период технического обслуживания, изделия с учетом интенсивности постепенных отказов (интенсивность распределена по закону Релея, который не всегда приемлем) и не учитывает внезапные отказы, возникающие при работе изделия под током и в выключенном состоянии.

Известно также устройство для определения оптимального периода технического обслуживания изделия, содержащие блок памяти, таймер, четыре вычитателя, четыре блока деления, два блока определения абсолютного значения, два сумматора, компаратор, ключ, элемент памяти, три умножителя, блок извлечения квадратного корня при этом первый выход блока памяти подключен к входу таймера, первый вход первого вычитателя подключен к третьему выходу блока памяти, вторые входы первого и второго вычитателей объединены и подключены ко второму выхода блока памяти, первый вход второго вычитателя подключен к четвертому выходу блока памяти, первый и второй входы блока первого блока деления, подключены соответственно к шестому и пятому выходам блока памяти, выходы первого и второго вычитателей через первый и второй блоки определения абсолютного значения подключены к первым входам второго и третьего блоков деления соответственно, второй вход второго блока деления подключен к выходу таймера и второму входу ключа, второй вход третьего блока деления подключен к пятому выходу блоку памяти, выходы второго и третьего блоков деления подключены соответственно к первому и второму входу третьего вычитателя, выход которого подключен к первому входу четвертого блока деления, на второй вход которого поступает сигнал с выхода первого блока деления, выход четвертого блока деления подключен к второму входу компаратора, первый вход которого подключен к седьмому выходу блока памяти, выход компаратора соединен с первым входом ключа и первым входом элемента памяти, выход ключа подключен к второму входу элемента памяти выход которого является первым выходом устройства, второй вход первого сумматора подключен к восьмому выходу блока памяти, девятый и десятый выходы блока памяти подключены к первому и второму входам четвертого вычитателя соответственно, первый и второй входы первого

умножителя подключены к одиннадцатому и двенадцатому выходам блока памяти, выход четвертого вычитателя и первого блока умножения подключены к первому и второму входам второго блока умножения соответственно, выход которого подключен к первому входу первого сумматора, выход которого соединен с первым и вторым входами второго сумматора, выход которого подключен к второму входу третьего блока умножения, на первый вход которого поступает сигнал с выхода элемента памяти, выход третьего блока умножения подключен к входу блока извлечения квадратного корня, выход которого является вторым выходом устройства [2].

Устройство позволяет определить время наступления постепенного отказа и с учетом этого, оптимальный период технического обслуживания изделия, но не определяет очередной период регламентированного технического обслуживания и коэффициент готовности изделия.

Наиболее близким по технической сущности к предлагаемому техническому решению является устройство для определения оптимального периода технического обслуживания изделия, содержащее блок памяти, таймер, четыре вычитателя, четыре блока деления, два блока определения абсолютного значения, два сумматора, компаратор, ключ, элемент памяти, три умножителя, блок извлечения квадратного корня, при этом первый выход блока памяти подключен к входу таймера, первый вход первого вычитателя соединен с третьим выходом блока памяти, вторые входы первого и второго вычитателей объединены и подключены ко второму выходу блока памяти, первый вход второго вычитателя соединен с четвертым выходом блока памяти, первый и второй входы блока первого блока деления, подключены соответственно к шестому и пятому выходам блока памяти, выходы первого и второго вычитателей через первый и второй блоки определения абсолютного значения соединены с первыми входами второго и третьего блоков деления соответственно, второй вход второго блока деления подключен к выходу таймера и второму входу ключа, второй вход третьего блока деления соединен с пятым выходом блока памяти, выходы второго и третьего блоков деления подключены соответственно к первому и второму входу третьего вычитателя, выход которого подключен к первому входу четвертого блока деления, на второй вход которого поступает сигнал с выхода первого блока деления, выход четвертого блока деления соединен с вторым входом компаратора, первый вход которого подключен к седьмому выходу блока памяти, выход компаратора соединен с первым входом ключа и первым входом элемента памяти, выход ключа подключен к второму входу элемента памяти, выход которого является первым выходом устройства, второй вход первого сумматора подключен к восьмому выходу блока памяти, девятый и десятый выходы блока памяти подключены к первому и второму входам четвертого вычитателя соответственно, первый и второй входы первого блока умножения подключены к одиннадцатому и двенадцатому выходам блока памяти, выход четвертого вычитателя и первого блока умножения подключены к первому и второму входам второго блока умножения соответственно, выход которого подключен к первому входу первого сумматора, выход которого соединен с первым и вторым входами второго сумматора, выход которого подключен к второму входу третьего блока умножения, первый вход которого связан с выходом элемента памяти, выход третьего блока умножения соединен с входом блока извлечения квадратного корня, выход которого является вторым выходом устройства, отличающееся тем, что в него введены пятый и шестой блоки деления, блок выделения целой части, вычитающий счетчик, четвертый блок умножения, третий сумматор, второй и третий элементы памяти, второй ключ и второй компаратор, причем тринадцатый выход блока памяти подключен к первым входам пятого блока деления и четвертого блока умножения, второй вход пятого блока деления соединен с выходом блока извлечения квадратного корня, восьмой выход блока памяти связан с первым входом третьего сумматора, второй вход которого подключен к выходу четвертого блока умножения и входу второго элемента памяти, выход пятого блока деления, через блок выделения целой части, подключен к первому входу вычитающего счетчика, выход которого соединен со вторым входом четвертого блока умножения, выход третьего сумматора связан с первым входом шестого блока деления, второй вход которого подключен к выходу первого элемента памяти, четырнадцатый выход блока памяти соединен со вторым входом второго компаратора, первый вход которого связан с выходом шестого блока деления и первым входом третьего элемента памяти, первый выход второго компаратора соединен со вторым входом вычитающего счетчика, второй выход второго компаратора подключен ко вторым входам второго ключа и третьего элемента памяти, первый вход второго ключа соединен с выходом второго элемента памяти, выход второго ключа является третьим выходом устройства, выход третьего элемента памяти является четвертым [3].

Устройство позволяет определять время наступления постепенного отказа, оптимальный период технического обслуживания, очередной период регламентированного технического обслуживания и коэффициент готовности изделия, но применение устройства становится не возможным, когда у определяющего параметра отсутствует граничное значение, что приводит к исключению из определяющих параметров части диагностических параметров.

Задачей, на решение которой направлена заявляемая полезная модель, является расширение функциональных возможностей устройства за счет вычисления граничных значений контролируемого параметра устройства, что делает возможным не только контролировать техническое состояние изделия по диагностическим параметрам не имеющих граничных значений, но и применять устройство для определения его потребности в ремонте.

Для достижения указанного технического результата в известное устройство, содержащее блок памяти, таймер, четыре вычитателя, четыре блока деления, два блока определения абсолютного значения, два сумматора, компаратор, ключ, элемент памяти, три умножителя, блок извлечения квадратного корня, при этом первый выход блока памяти подключен к входу таймера, первый вход первого вычитателя соединен с третьим выходом блока памяти, вторые входы первого и второго вычитателей объединены и подключены ко второму выходу блока памяти, первый вход второго вычитателя соединен с четвертым выходом блока памяти, первый и второй входы блока первого блока деления, подключены соответственно к шестому и пятому выходам блока памяти, выходы первого и второго вычитателей через первый и второй блоки определения абсолютного значения соединены с первыми входами второго и третьего блоков деления соответственно, второй вход второго блока деления подключен к выходу таймера и второму входу ключа, второй вход третьего блока деления соединен с пятым выходом блока памяти, выходы второго и третьего блоков деления подключены соответственно к первому и второму входу третьего вычитателя, выход которого подключен к первому входу четвертого блока деления, на второй вход которого поступает сигнал с выхода первого блока деления, выход четвертого блока деления соединен с вторым входом компаратора, первый вход которого подключен к седьмому выходу блока памяти, выход компаратора соединен с первым входом ключа и первым входом элемента памяти, выход ключа подключен к второму входу элемента памяти, выход которого является первым выходом устройства, второй вход первого сумматора подключен к восьмому выходу блока памяти, девятый и десятый выходы блока памяти подключены к первому и второму входам четвертого вычитателя соответственно, первый и второй входы первого блока умножения подключены к одиннадцатому и двенадцатому выходам блока памяти, выход четвертого вычитателя и первого блока умножения подключены к первому и второму входам второго блока умножения соответственно, выход которого подключен к первому входу первого сумматора, выход которого соединен с первым и вторым входами второго сумматора, выход которого подключен к первому входу третьего блока умножения, первый вход которого связан с выходом элемента памяти, выход третьего блока умножения соединен с входом блока извлечения квадратного корня, выход которого является вторым таймера, первый вход первого вычитателя соединен с третьим выходом блока памяти, вторые входы первого и второго вычитателей объединены и подключены ко второму выходу блока памяти, первый вход второго вычитателя соединен с четвертым выходом блока памяти, первый и второй входы блока первого блока деления, подключены соответственно к шестому и пятому выходам блока памяти, выходы первого и второго вычитателей через первый и второй блоки определения абсолютного значения соединены с первыми входами второго и третьего блоков деления соответственно, второй вход второго блока деления подключен к выходу таймера и второму входу ключа, второй вход третьего блока деления соединен с пятым выходом блока памяти, выходы второго и третьего блоков деления подключены соответственно к первому и второму входу третьего вычитателя, выход которого подключен к первому входу четвертого блока деления, на второй вход которого поступает сигнал с выхода первого блока деления, выход четвертого блока деления соединен с вторым входом компаратора, первый вход которого подключен к седьмому выходу блока памяти, выход компаратора соединен с первым входом ключа и первым входом элемента памяти, выход ключа подключен к второму входу элемента памяти, выход которого является первым выходом устройства, второй вход первого сумматора подключен к восьмому выходу блока памяти, девятый и десятый выходы блока памяти подключены к первому и второму входам четвертого вычитателя соответственно, первый и второй входы первого блока умножения подключены к одиннадцатому и двенадцатому выходам блока памяти, выход четвертого вычитателя и первого блока умножения подключены к первому и второму входам второго блока умножения соответственно, выход которого подключен к первому входу первого сумматора, выход которого соединен с первым и вторым входами второго сумматора, выход которого подключен к второму входу третьего блока умножения, первый вход которого связан с выходом элемента памяти, выход третьего блока умножения соединен с входом блока извлечения квадратного корня, выход которого является вторым объединены и подключены к выходу блока задержки, вход седьмого блока деления соединен с выходом четвертого сумматора, вход третьего блока деления подключен к выходу пятого вычитателя, выход третьего блока деления соединен с входом пятого блока умножения, первые выходы пятого сумматора и шестого вычитателя объединены и подключены к выходу седьмого блока деления, вторые входы пятого сумматора и шестого вычитателя объединены и соединены с выходом пятого блока умножения, выходы пятого сумматора и шестого вычитателя подключены к первому и второму входу блоку выбора минимального значения, выход блока выбора минимального значения соединен со вторым вход третьего ключа, выход третьего ключа подключен к первому входу первого вычитателя.

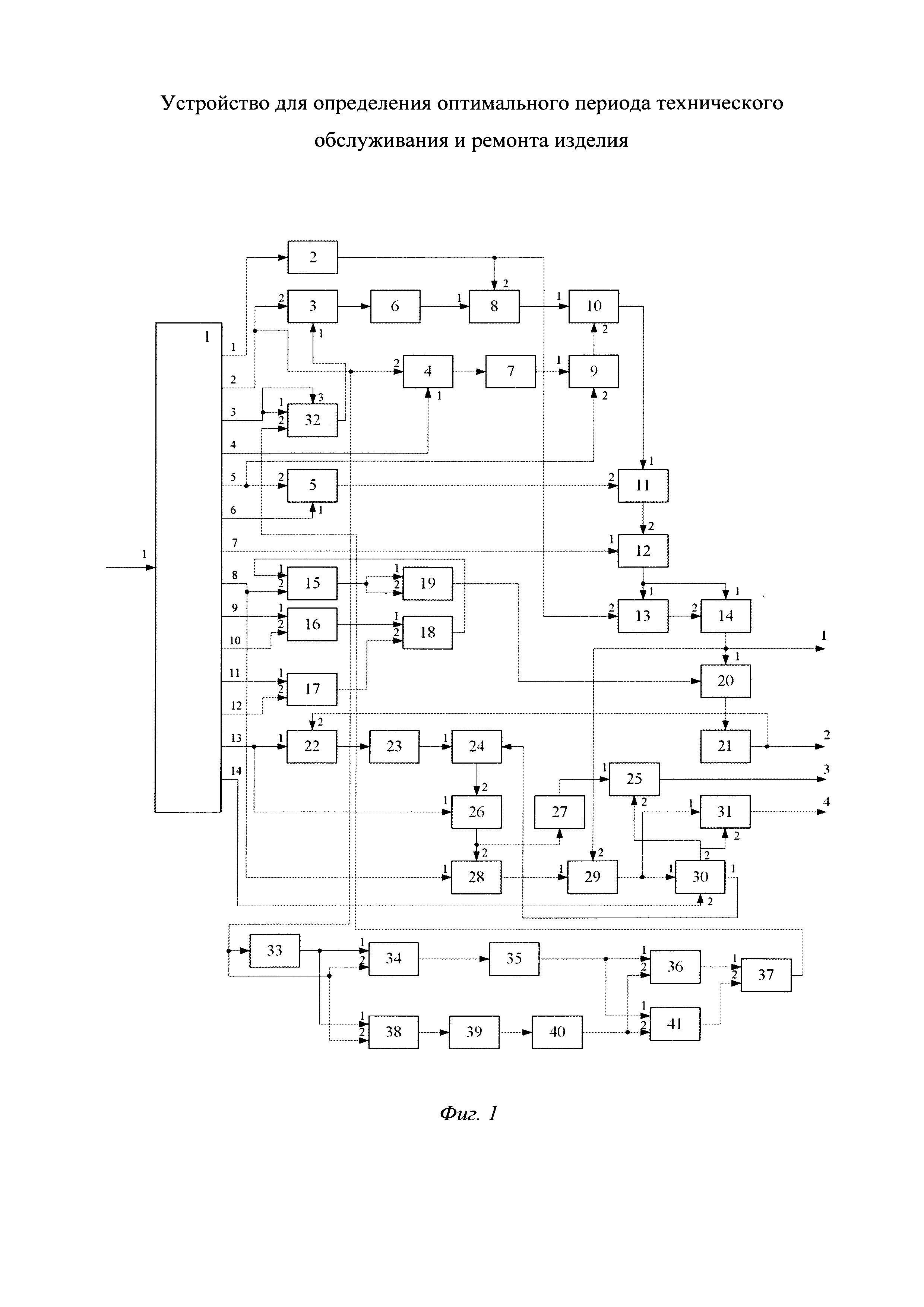

На фиг. 1 приведена схема предлагаемого устройства; на фиг. 2 - схема блока памяти.

Устройство содержит блок памяти 1, таймер 2, первый и второй вычитатели 3 и 4 соответственно, первый блок деления 5, первый и второй блоки определения абсолютного значении 6 и 7 соответственно, второй и третий блоки деления 8 и 9 соответственно, третий вычитатель 10, четвертый блок деления 11, первый компаратор 12, первый ключ 13, первый элемент памяти 14, первый сумматор 15, четвертый вычитатель 16, первый и второй блоки умножения 17 и 18 соответственно, второй сумматор 19, третий блок умножения 20, блок извлечения квадратного корня 21, пятый блок деления 22, блок выделения целой части 22, вычитающий счетчик 24, второй ключ 25, четвертый блок умножения 26, второй элемент памяти 27, третий сумматор 28, шестой блок деления 29, второй компаратор 30, третий элемент памяти 31, третий ключ 32, блок задержки 33, четвертый сумматор 34, седьмой блок деления 35, пятый сумматор 36, блок выбора минимального значения 37, пятый вычитатель 38, третий блок определения абсолютного значения 39, пятый блок умножения 40, шестой вычитатель 40, причем первый выход блока памяти 1 подключен к датчику таймера 2, третий выход блока памяти 1 подключен к первому и третьему входу третьего ключа 32, выход третьего объединены и подключены к выходу блока задержки, вход седьмого блока деления соединен с выходом четвертого сумматора, вход третьего блока деления подключен к выходу пятого вычитателя, выход третьего блока деления соединен с входом пятого блока умножения, первые входы пятого сумматора и шестого вычитателя объединены и подключены к выходу седьмого блока деления, вторые входы пятого сумматора и шестого вычитателя объединены и соединены с выходом пятого блока умножения, выходы пятого сумматора и шестого вычитателя подключены к первому и второму входу блоку выбора минимального значения, выход блока выбора минимального значения соединен со вторым вход третьего ключа, выход третьего ключа подключен к первому входу первого вычитателя.

На фиг. 1 приведена схема предлагаемого устройства; на фиг. 2 - схема блока памяти.

Устройство содержит блок памяти 1, таймер 2, первый и второй вычитатели 3 и 4 соответственно, первый блок деления 5, первый и второй блоки определения абсолютного значении 6 и 7 соответственно, второй и третий блоки деления 8 и 9 соответственно, третий вычитатель 10, четвертый блок деления 11, первый компаратор 12, первый ключ 13, первый элемент памяти 14, первый сумматор 15, четвертый вычитатель 16, первый и второй блоки умножения 17 и 18 соответственно, второй сумматор 19, третий блок умножения 20, блок извлечения квадратного корня 21, пятый блок деления 22, блок выделения целой части 22, вычитающий счетчик 24, второй ключ 25, четвертый блок умножения 26, второй элемент памяти 27, третий сумматор 28, шестой блок деления 29, второй компаратор 30, третий элемент памяти 31, третий ключ 32, блок задержки 33, четвертый сумматор 34, седьмой блок деления 35, пятый сумматор 36, блок выбора минимального значения 37, пятый вычитатель 38, третий блок определения абсолютного значения 39, пятый блок умножения 40, шестой вычитатель 40, причем первый выход блока памяти 1 подключен к датчику таймера 2, третий выход блока памяти 1 подключен к первому и третьему входу третьего ключа 32, выход третьего ключа 32 соединен с первым входом первого вычитателя 3, вторые входы первого 3, второго вычитателей 4, вход блока задержки 33, вторые входы четвертого сумматора 34 и пятого вычитателя 38 объединены и подключены ко второму выходу блока памяти 1, первые входы четвертого сумматора 34 и пятого вычитателя 38 объединены и подключены к выходу блока задержки 33, вход седьмого блока деления 35 соединен с выходом четвертого сумматора 34, вход третьего блока абсолютного значения 39 подключен к выходу пятого вычитателя 38, выход третьего блока абсолютного значения 39 соединен с входом пятого блока умножения 40, первые входы пятого сумматора 36 и шестого вычитателя 41 объединены и подключены к выходу седьмого блока деления 35, вторые входы пятого сумматора 36 и шестого вычитателя 41 объединены и соединены с выходом пятого блока умножения 40, выходы пятого сумматора 36 и шестого вычитателя 41 подключены к первому и второму входу блоку выбора минимального значения 37, выход блока выбора минимального значения 37 соединен со вторым входом третьего ключа 32, выход третьего ключа 32 подключен к первому входу первого вычитателя 3 вторые входы первого 3 и второго 4 вычитателей объединены и подключены ко второму выходу блока памяти 1, первый вход второго вычитателя 4 соединен с четвертым выходом блока памяти 1, первый и второй входы первого блока деления 5, подключены соответственно к шестому и пятому выходам блока памяти 1, выходы первого 3 и второго 4 вычитателей через первый 6 и второй 7 блоки определения абсолютного значения соединены с первыми входами второго 8 и третьего 9 блоков деления соответственно, второй вход второго блока деления 8 подключен к выходу таймера 2 и второму входу ключа 13, второй вход третьего блока деления 9 соединен с пятым выходом блока памяти 1, выходы второго 8 и третьего 9 блоков деления подключены соответственно к первому и второму входу третьего вычитателя 10, выход которого подключен к первому входу четвертого блока деления 11, второй вход которого связан с выходом первого блока деления 5, выход четвертого блока деления 11 соединен со вторым входом компаратора 12,счетчика 24, второй выход второго компаратора 30 подключен ко вторым входам второго ключа 25 и третьего элемента памяти 31, первый вход второго ключа 25 соединен с выходом второго элемента памяти 27, выход второго ключа 25 является третьем выходом устройства, выход третьего элемента памяти 31 является четвертым выходом устройства.

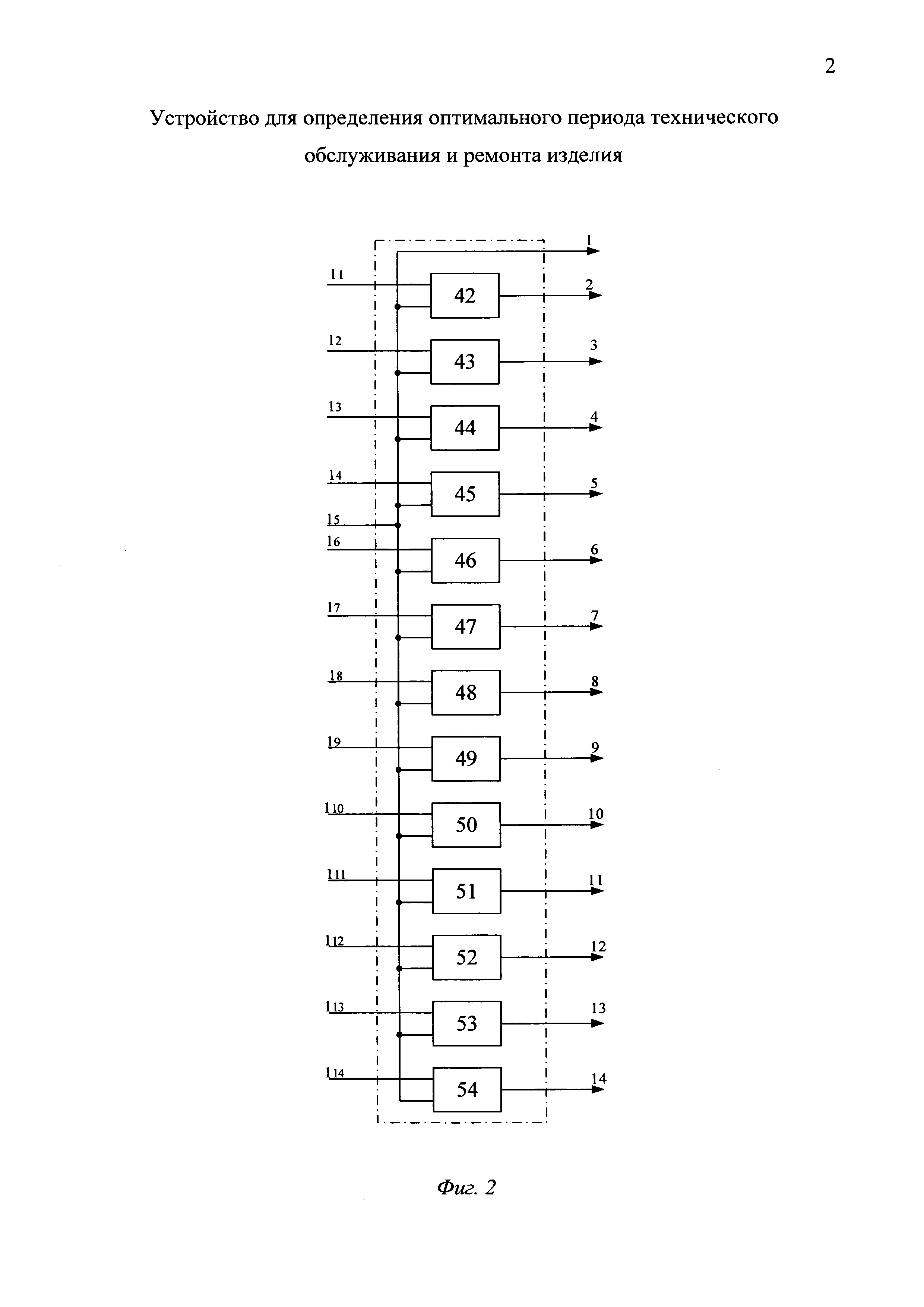

Блок памяти 1 содержит третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый и четырнадцатый элементы памяти 42-54 соответственно.

Устройство работает следующим образом.

На вход 11 блока памяти 1 поступает номинальное значение определяющего параметра

Таким образом предлагаемое устройство позволяет определять время наступления постепенного отказа, оптимальный и очередной периоды регламентированного технического обслуживания и ремонта, и коэффициент готовности изделия по значениям как прямых, так и диагностических параметров, осуществляя стратегию ремонта по техническому состоянию. Устройство успешно прошло испытание и используется при планировании технического обслуживания и ремонта изделий.

Источники, принятые во внимание при составлении описания полезной модели:

1. Патент РФ №2347272, МПК G07C 3/08, 2009 г.

2. Патент РФ №111327, МПК G07C 3/00, 2011 г.

3. Патент РФ №139086, МПК G07C 3/00, 2013 г.

Реферат

Полезная модель относится к вычислительной технике, в частности к контрольным устройствам, и может быть использована в научных исследованиях и технике, где необходимо определять время наступления постепенного отказа, оптимальный и очередной периоды регламентированного технического обслуживания и ремонта, и коэффициент готовности изделия по значениям как прямых, так и диагностических параметров, осуществляя стратегию ремонта по техническому состоянию.Устройство для определения оптимального периода технического обслуживания и ремонта изделия содержит блок памяти, таймер, шесть вычитателей, семь блоков деления, три блока определения абсолютного значения, пять сумматоров, два компаратора, три ключа, три элемента памяти, пять блоков умножения, блок извлечения квадратного корня, блок выделения целой части, вычитающий счетчик, блок задержки, блок выбора минимального значения сигнала, при этом первый выход блока памяти подключен к входу таймера, третий выход блока памяти подключен к первому и третьему входу третьего ключа, выход третьего ключа соединен с первым входом первого вычитателя, вторые входы первого, второго вычитателей, вход блока задержки, вторые входы четвертого сумматора и пятого вычитателя объединены и подключены ко второму выходу блока памяти, первые входы четвертого сумматора и пятого вычитателя объединены и подключены к выходу блока задержки, вход седьмого блока деления соединен с выходом четвертого сумматора, вход третьего блока абсолютного значения подключен к выходу пятого вычитателя, выход третьего блока абсолютного значения соединен с входом пятого блока умножения, первые выходы пятого сумматора и шестого вычитателя объединены и подключены к выходу седьмого блока деления, вторые входы пятого сумматора и шестого вычитателя объединены и соединены с выходом пятого блока умножения, выходы пятого сумматора и шестого вычитателя подключены к первому и второму входу блоку выбора минимального значения, выход блока выбора минимального значения соединен со вторым вход третьего ключа, выход третьего ключа подключен к первому входу первого вычитателя, первый вход второго вычитателя соединен с четвертым выходом блока памяти, первый и второй входы блока первого блока деления, подключены соответственно к шестому и пятому выходам блока памяти, выходы первого и второго вычитателей через первый и второй блоки определения абсолютного значения соединены с первыми входами второго и третьего блоков деления соответственно, второй вход второго блока деления подключен к выходу таймера и второму входу ключа, второй вход третьего блока деления соединен с пятым выходом блока памяти, выходы второго и третьего блоков деления подключены соответственно к первому и второму входу третьего вычитателя, выход которого подключен к первому входу четвертого блока деления, на второй вход которого поступает сигнал с выхода первого блока деления, выход четвертого блока деления соединен со вторым входом компаратора, первый вход которого подключен к седьмому выходу блока памяти, выход компаратора соединен с первым входом ключа и первым входом элемента памяти, выход ключа подключен к второму входу элемента памяти, выход которого является первым выходом устройства, второй вход первого сумматора подключен к восьмому выходу блока памяти, девятый и десятый выходы блока памяти подключены к первому и второму входам четвертого вычитателя соответственно, первый и второй входы первого блока умножения подключены к одиннадцатому и двенадцатому выходам блока памяти, выход четвертого вычитателя и первого блока умножения подключены к первому и второму входам второго блока умножения соответственно, выход которого подключен к первому входу первого сумматора, выход которого соединен с первым и вторым входами второго сумматора, выход которого подключен к первому входу третьего блока умножения, первый вход которого связан с выходом элемента памяти, выход третьего блока умножения соединен с входом блока извлечения квадратного корня, выход которого является вторым выходом устройства, тринадцатый выход блока памяти подключен к первым входам пятого блока деления и четвертого блока умножения, второй вход пятого блока деления соединен с выходом блока извлечения квадратного корня, восьмой выход блока памяти связан с первым входом третьего сумматора, второй вход которого подключен к выходу четвертого блока умножения и входу второго элемента памяти, выход пятого блока деления через блок выделения целой части подключен к первому входу вычитающего счетчика, выход которого соединен со вторым входом четвертого блока умножения, выход третьего сумматора связан с первым входом шестого блока деления, второй вход которого подключен к выходу первого элемента памяти, четырнадцатый выход блока памяти соединен со вторым входом

Комментарии