Устройство и способ обработки данных с использованием наборов команд - RU2137183C1

Код документа: RU2137183C1

Чертежи

Описание

Изобретение относится к области обработки данных. Конкретнее, данное изобретение относится к обработке данных, использующей множество наборов командных слов программы.

Системы обработки данных используют процессорное ядро, работающее под управлением командных слов программы, которые после декодирования обеспечивают формирование управляющих сигналов для управления различными элементами в процессорном ядре для выполнения необходимых функций при обработке определяемой командным словом программы.

Типовое процессорное ядро имеет информационные магистрали за заданное количество ограничивающие длину информационных слов, которыми можно манипулировать в ответ на данную команду. Тенденцией в области обработки давних является постоянное увеличение разрядности этих магистралей данных, например, постепенный переход от 8-разрядной архитектуры к 16-разрядной, 32-разрядной и 64-разрядной архитектуре. Одновременно с нарастанием разрядности магистралей данных наборы команд возрастают по числу возможных команд (как для компьютеров с полной системой команд - CISC, так и для компьютеров с сокращенным набором команд -RISC) и по разрядной длине этих команд. Например, имеет место переход от использования 16-разрядиой архитектуры с набором 16-разрядных команд к использованию 32-разрядной архитектуры с наборами 32-разрядных команд.

Проблема, связанная c увеличением разрядности используемой архитектуры, состоит в желании сохранить преемственность c программным обеспечением, написанным для предшествующих поколений машин. Одним из путей достижения этого является снабжение новых систем режимом совместимости. К примеру, компьютеры YAXII компании Digital Equipment Corporation имеют режим совместимости, который позволяет им декодировать команды для более ранних компьютеров PDPII. Хотя это и позволяет использовать предшествующее программное обеспечение, однако такое использование не обеспечивает полной выгоды от возросших возможностей новой системы обработки, на которой оно работает, например, может использоваться только многоступенчатая 16-разрядная арифметика, тогда как аппаратное обеспечение способно поддерживать 32-разрядную арифметику.

Другая проблема, связанная с такими изменениями в аппаратной ширине (разрядности) магистралей, состоит в том, что размер компьютерных программ, использующих новые наборы команд с увеличенной разрядной шириной, имеет тенденцию к увеличению (32-разрядное командное слово программы занимает в два раза большее пространство памяти, чем 16-разрядное командное слово программы). Хотя это увеличение размера до некоторой степени компенсируется тем, что задается единственная команда для определения операции, которая могла раньше требовать более одной короткой команды, тенденцией все же остается увеличение размера программ.

Одним из путей решения этой проблемы является определение пользователем своего собственного набора команд. Компьютеры IBM370, выпускаемые компанией Интернейшнл Бизнес Машинз Корпорейшн, имеют в своем составе управляемую перезаписью память, используя которую пользователь может установить свой собственный индивидуальный набор команд, отображающий командные олова программы в желательные действия посредством различных частей процессорного ядра. Хотя этот подход обладает достаточно хорошей гибкостью, однако при его использовании трудно обеспечить высокоскоростную работу, а управляемая перезаписью память занимает излишне большую область интегральной схемы. Кроме того, разработка заранее заданного эффективного набора команд представляет собой весьма трудоемкую задачу для пользователя.

Опубликованная заявка на Европейский патент EP-A-0169565 раскрывает систему с 16-разрядный процессорным ядром. В первом режиме система работает на 16-разрядных командах, которые определяют операции по обработке данных 16-разрядных данных. Во втором режиме система работает на 8-разрядных командах, которые определяют операции по обработке 8-разрядных данных. 8-разрядная команда отображается с использованием программируемой памяти в 16-разрядную команду, которая затем декодируется. Эта декодированная 16-разрядная команда затем выполняет определенную операцию по обработке 8-разрядных данных.

Известны также системы, в которых единственный набор команд имеет командные слова программы различных длин. Примером такого подхода является микропроцессор 6502, выпускаемый по МОП-технологии. Этот процессор использует 8-разрядные операционные коды, которые сопровождаются различным числом байтов операндов. Код операции должен быть декодирован прежде чем операнды будут идентифицированы и команда исполнена. Это требует множества выборок из памяти и представляет значительное ограничение характеристик системы, связанное с командными словами программы (т. е. операционным кодом и любыми операндами) постоянной известной длины.

Известна система, которая преобразует 17-разрядные команды в 20-разрядные команды (см. IBM Technical Bulletin Vol. 15, No. 3 August 1972, стр. 920).

Опубликованная заявка на Европейский патент EP-A- 0199173 раскрывает микропроцессор, включающий в себя декодер команд.

Согласно одному из аспектов изобретения, предложено устройство

для обработки данных, содержащее

процессорное ядро с N-разрядными магистралями данных, выполненное с возможностью реагирования на множество управляющих сигналов ядра,

первое

декодирующее средство, выполненное с возможностью декодирования X-разрядных программных командных слов из первого постоянного набора команд для генерирования упомянутых управляющих сигналов ядра для

запуска обработки с использованием N-разрядных магистралей данных,

второе декодирующее средство, выполненное с возможностью Y-разрядных программных командных слов: из второго постоянного

набора команд для генерирования управляющих сигналов ядра для запуска обработки с использованием N-разрядных магистралей данных, причем Y меньше X, и

переключатель наборов команд для выбора

либо первого режима обработки с использованием первого декодирующего средства при приеме программных командных слов, либо второго режима обработки с использованием второго декодирующего средства при

приеме программных командных слов.

Изобретение исходит из того факта, что в системе с широким стандартным набором X-разрядных команд и N-разрядных магистралей данных (к примеру, набор 32-разрядных команд, используемый совместно с 32-разрядными магистралями данных) полные возможности набора X-разрядных команд часто не используются в обычном программировании. Примером этого служит 32 -разрядная команда ветвления. Команда ветвления может иметь диапазон в 32 Мегабайта, который используется очень нерегулярно. Таким образом, в большинстве случаев ветвление будет иметь место только для небольшого числа команд, и большинство разрядов в 32-разрядной команде не переносит никакой информации. Многие программы, записанные с использованием набора 32-разрядных команд, имели бы низкую плотность кода и использовали бы больше пространства для хранения программы, чем необходимо.

Изобретение решает эту проблему обеспечением отдельного постоянного набора Y-разрядных команд, где Y меньше X, который все же работает на полных N-разрядных магистралях данных. Таким образом, используется производительность N-разрядных магистралей данных, и при этом увеличивается плотность кода за счет прикладных задач, которые не требуют усложненного набора X-разрядных команд.

Использование двух постоянных наборов команд обеспечивает синергический эффект. Пользователю предоставляется гибкость в чередовании набора команд, которые используются для удовлетворения условиям программы, при этом оба набора команд эффективно реализуются изготовителем (что критично в высокоэффективных системах, таких как RISC-процессоры, где критично относительное согласование по времени) и без снижения эффективности использования N-разрядных магистралей данных.

Другим преимуществом такого выполнения является то, что, поскольку меньше байтов программного кода будет проходить в единицу времени при работе с набором Y-разрядных команд, менее строгие требования предъявляются к переносу данных для запоминающих систем, хранящих программный код. Это снижает сложность и стоимость.

Изобретение, таким образом, имеет направленность, противоположную обычной тенденции в данной области. Эта тенденция состоит в том, что с каждым новым поколением процессоров все больше команд добавляется к наборам команд, причем наборы команд соответственно расширяются. В противоположность этому изобретение исходит из использования широкого усложненного набора команд, а затем добавляет дополнительный более узкий набор команд (с меньшим пространством для большого числа команд) для использования в ситуациях, где не требуется полный объем широкого набора команд.

Следует отметить, что первый набор команд и второй набор команд могут быть полностью зависимыми. Однако в предпочтительных выполнениях изобретения упомянутый второй набор команд обеспечивает поднабор операций, обеспечиваемых упомянутым первым набором команд.

Это дает возможность более эффективной работы, поскольку элементы аппаратной части процессорного ядра могут быть выполнены с большей легкостью для удовлетворения требований обоих наборов команд.

Когда набор команд из программных командных слов увеличенной разрядной длины добавляется к существующему набору программных команд, можно обеспечить, чтобы программные командные слова из двух наборов команд были ортогональны. Однако переключатель наборов команд позволяет обойти это ограничение и реализовать системы, в которых упомянутый второй набор команд неортогонален упомянутому первому набору команд.

Свобода в использовании неортогональных наборов команд облегчает задачу системного разработчика и обеспечивает более эффективную реализацию иных аспектов разработки набора команд.

Переключатель наборов команд может быть выполнен как переключатель аппаратного типа, устанавливаемый посредством некоторого ручного вмешательства. Однако в предпочтительных выполнениях изобретения упомянутый переключатель наборов команд содержит средство, выполненное с возможностью срабатывания на флаг набора команд, устанавливаемый при управлении посредством пользовательской программы.

Обеспечение использования переключателя наборов команд для переключения между первым набором команд и вторым набором команд, устанавливаемого под управлением программы, является значительным преимуществом. К примеру, программист может использовать второй набор команд с его Y-разрядными программными командными словами вследствие увеличенной плотности кода для большей части программы и временно переключаться на первый набор команд с его X-разрядными программными командными словами для тех малых частей программы, которые требуют увеличенной производительности и усложненности первого набора команд.

Обеспечение двух независимых наборов команд может обусловить дополнительное усложнение системы. В предпочтительных выполнениях изобретения упомянутое процессорное ядро содержит регистр программного состояния для хранения данных состояния обработки, осуществляемой в текущий момент, и регистр сохраненного программного состояния, при этом регистр сохраненного программного состояния используется для хранения данных состояния обработки, связанных с главной программой, когда возникает исключительное программное состояние, вызывающее исполнение программы обработки исключительных состояний, причем упомянутый флаг является частью данных состояния обработки.

Обеспечение флага набора команд как части данных состояния программы гарантирует, что он сохраняется, когда возникает исключительное состояние. Таким образом, единственный манипулятор (программа обработки) исключительных состояний может манипулировать исключительными состояниями для обоих программных режимов, и может быть разрешено обращение к флагу сохраненного набора команд в регистре состояния сохраненной программы, если это важно при обработке исключительного состояния. Кроме того, программа обработки исключительных состояний может обеспечивать использование любого набора команд для улучшения либо его скорости, либо плотности кода, как того требуют ограничения разработки.

Для того, чтобы обеспечивать обработку различных разрядных длин различных наборов команд, предпочтительные выполнения изобретения предусматривают, что процессорное ядро содержит регистр программного счетчика и формирователь приращений программного счетчика для формирования приращений значения в программном счетчике, хранимого в регистре программного счетчика, для указания следующего программного командного слова, причем формирователь приращений программного счетчика в первом режиме обработки применяет шаг приращения, отличный от шага приращения во втором режиме обработки.

Следует отметить, что более короткие программные командные слова второго набора команд не могут содержать столько же информации, как и программные командные слова первого набора команд. Для учета этого предпочтительно, чтобы во втором наборе команд области сохранялись за счет сокращения диапазона операндов, что может быть определено в программном командном слове.

В предпочтительном осуществлении изобретения процессорное ядро связано с системой памяти посредством Y-разрядной шины данных, так что программные командные слова из второго набора команд требуют единственного цикла выборки, а программные командные слова из упомянутого первого набора команд требуют множества циклов выборки.

Использование Y-разрядной шины данных и запоминающей системы позволяет построить менее дорогую общую систему, обеспечивающую при этом единственный цикл выборки для каждого программного командного слова по меньшей мере для второго набора команд.

Первое декодирующее средство и второе декодирующее средство могут быть полностью раздельными. Однако в предпочтительном осуществлении изобретения второе декодирующее средство выполнено с возможностью повторного использования по меньшей мере части первого декодирующего средства.

Повторное использование по меньшей мере части первого декодирующего средства вторым декодирующим средством снижает общую площадь схемы. Кроме того, поскольку первый набор команд в общем случае менее сложен, чем второй набор команд, и управляется тем же самым процессорным ядром, значительная часть второго декодирующего средства может быть повторно использована.

В предпочтительном осуществлении заявленное устройство может быть выполнено в виде интегральной схемы.

Согласно другому аспекту изобретения, заявлен способ обработки данных,

включающий операции, при которых

выбирают либо первый режим обработки, при котором X-разрядные программные командные слова используют для генерирования управляющих сигналов ядра, либо второй

режим обработки, при котором Y-разрядные программные командные слова используют для генерирования управляющих сигналов ядра, для процессорного ядра с N-разрядными магистралями данных, осуществляющего

обработку данных в ответ на множество упомянутых управляющих сигналов ядра,

декодируют в первом режиме обработки X-разрядные программные кодовые слова из первого постоянного набора команд для

генерирования упомянутых управляющих сигналов ядра для запуска обработки данных в процессорном ядре с использованием N-разрядных магистралей данных, и

декодируют во втором режиме обработки

Y-разрядные программные кодовые слова из второго постоянного набора команд для генерирования управляющих сигналов ядра для запуска обработки данных в процессорном ядре, причем Y меньше X.

Изобретение поясняется на примерах его осуществления, иллюстрируемых чертежами.

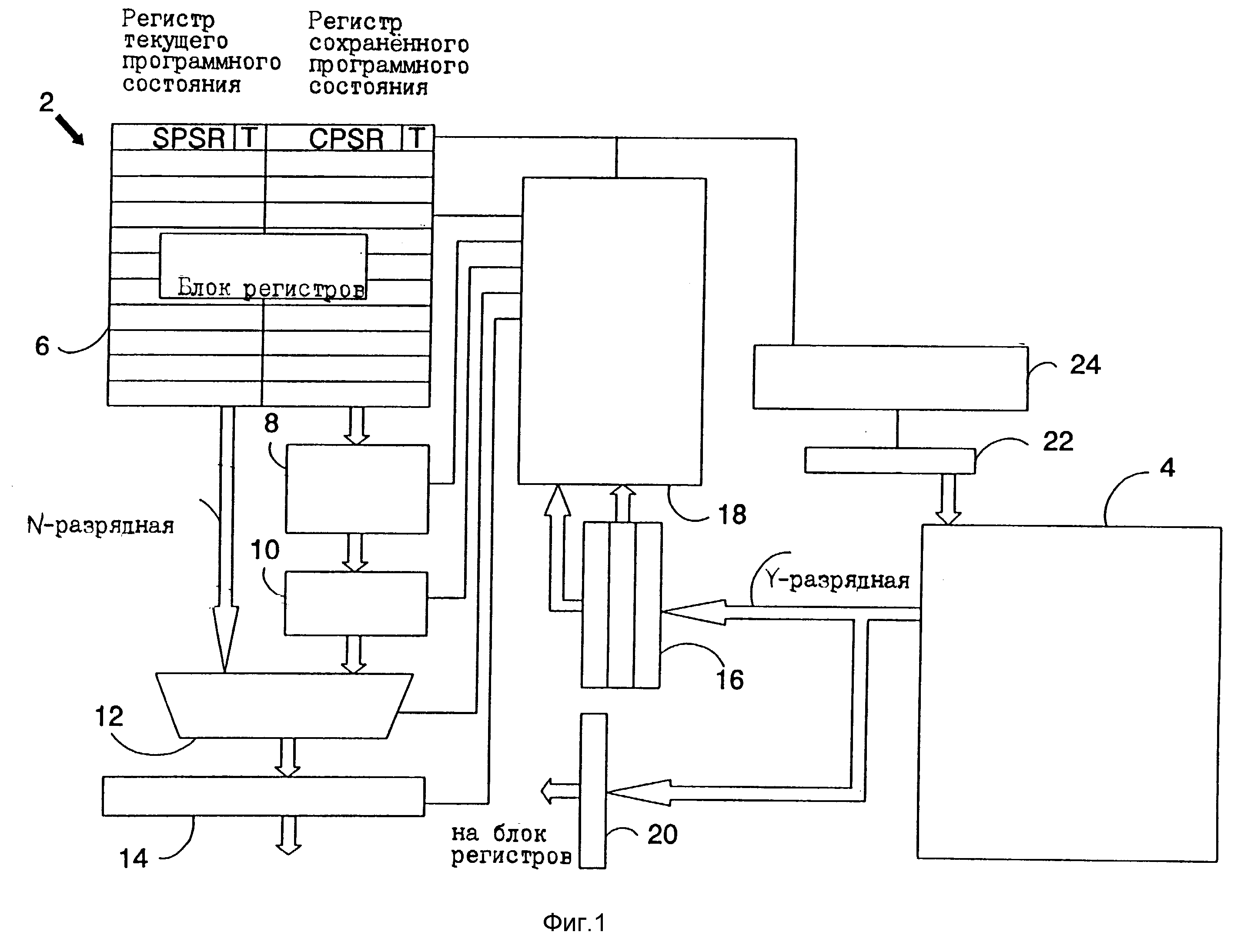

Фиг. 1 схематически представляет устройство для обработки данных, включающее в себя процессорное ядро и запоминающую систему.

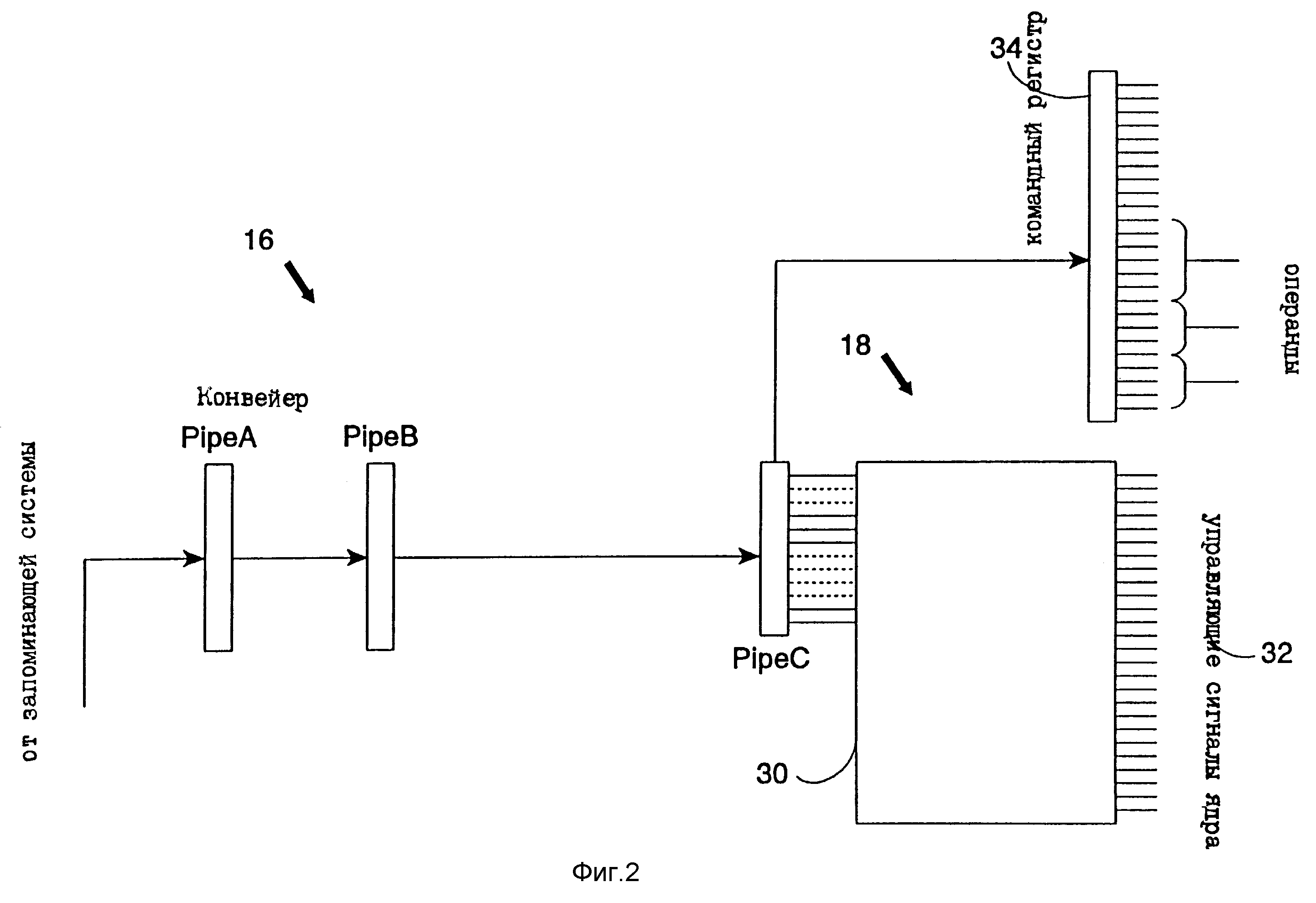

Фиг. 2 схематически представляет команды и командный декодер для системы с единственным набором команд.

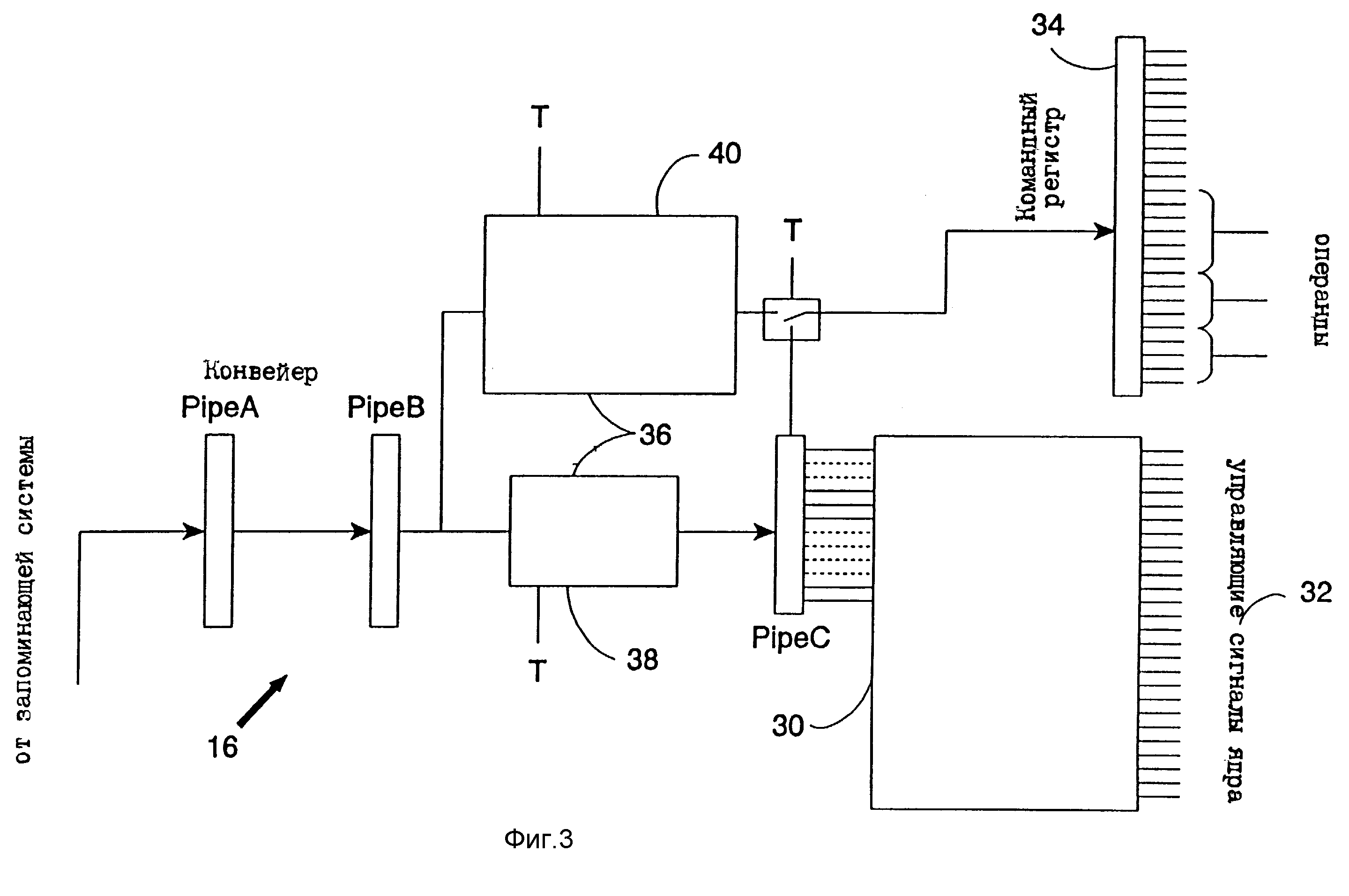

Фиг. 3 представляет командный конвейер и командные декодеры для использования в системе с двумя наборами команд.

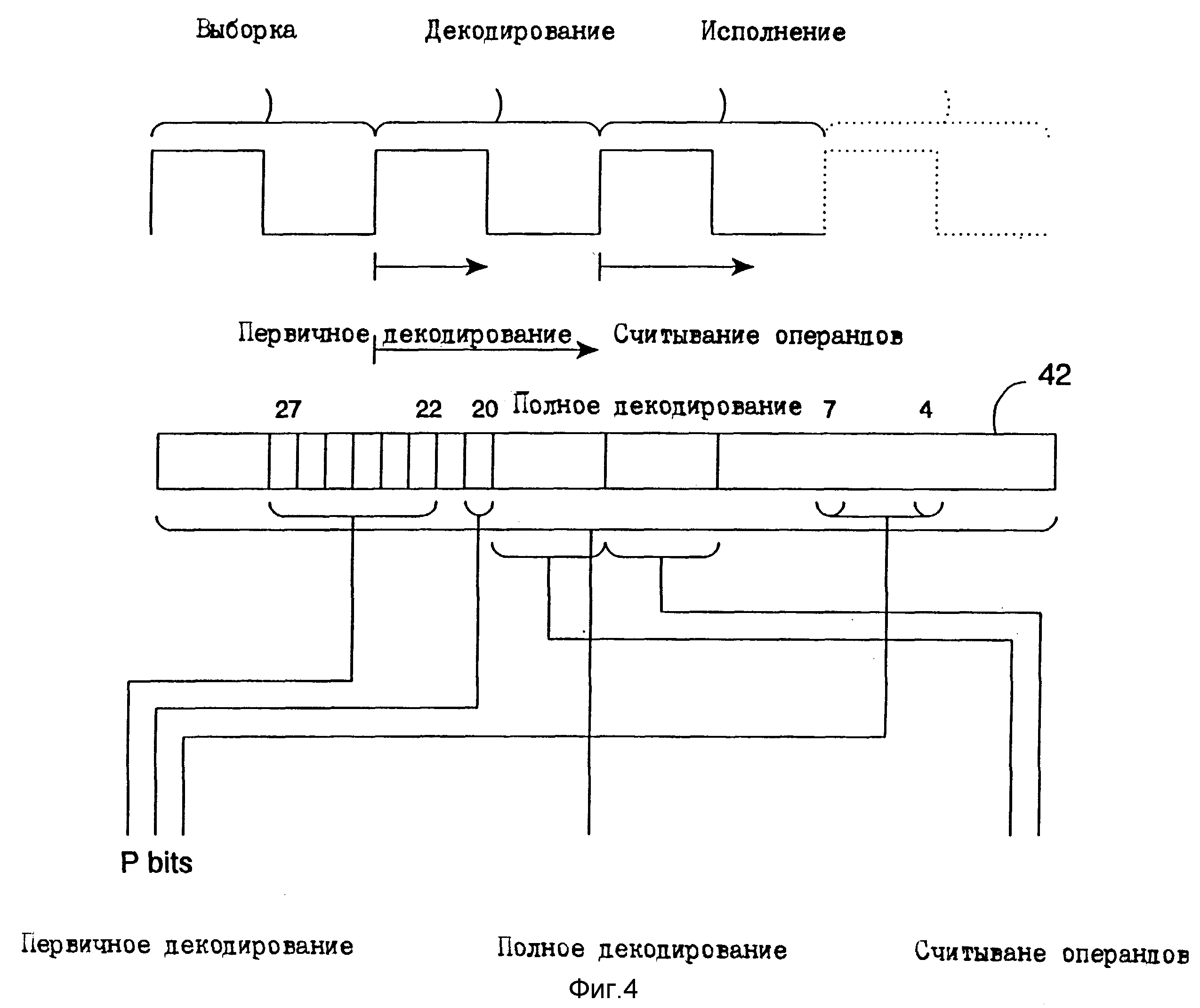

Фиг. 4 иллюстрирует декодирование X-разрядкого программного командного слова.

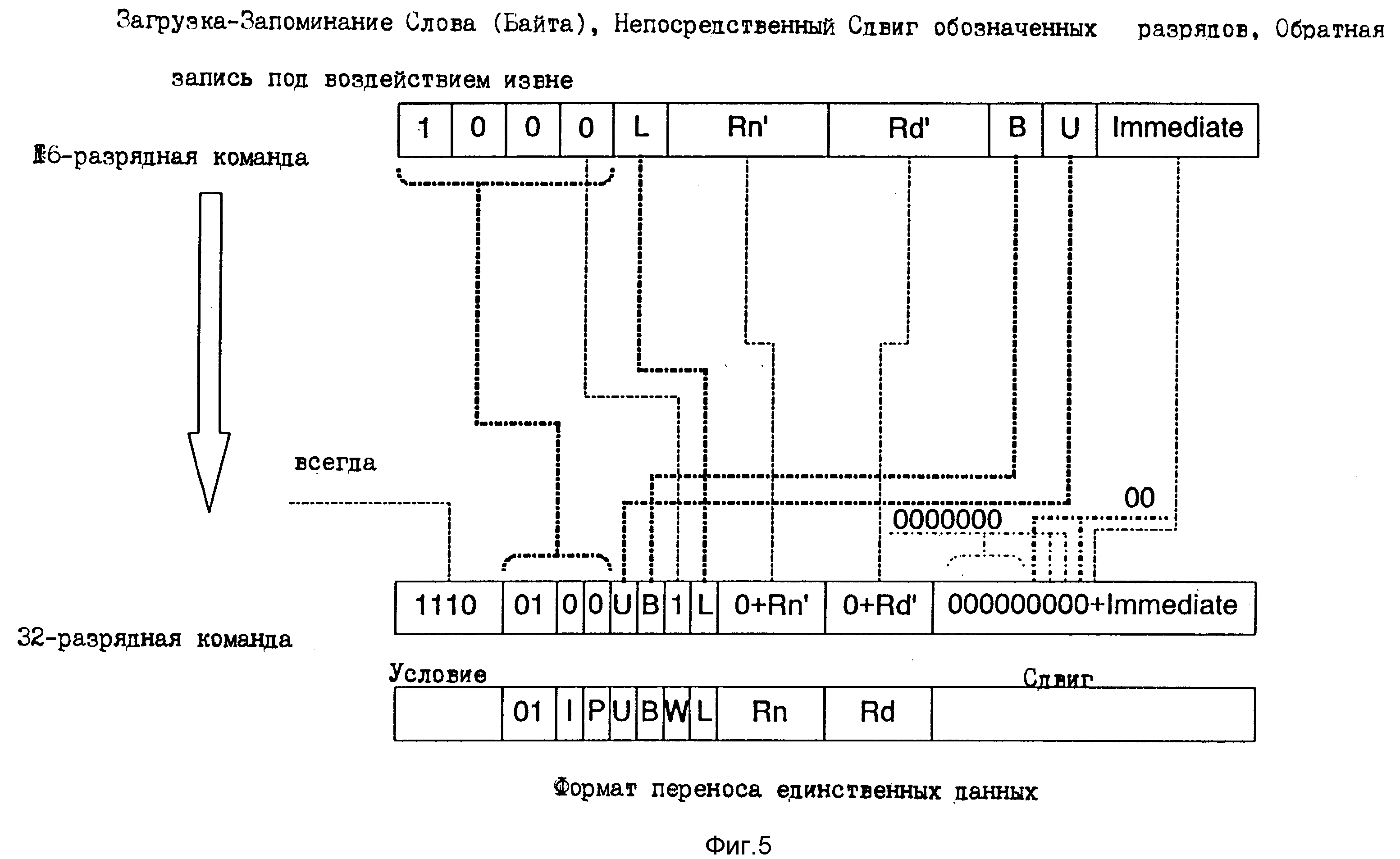

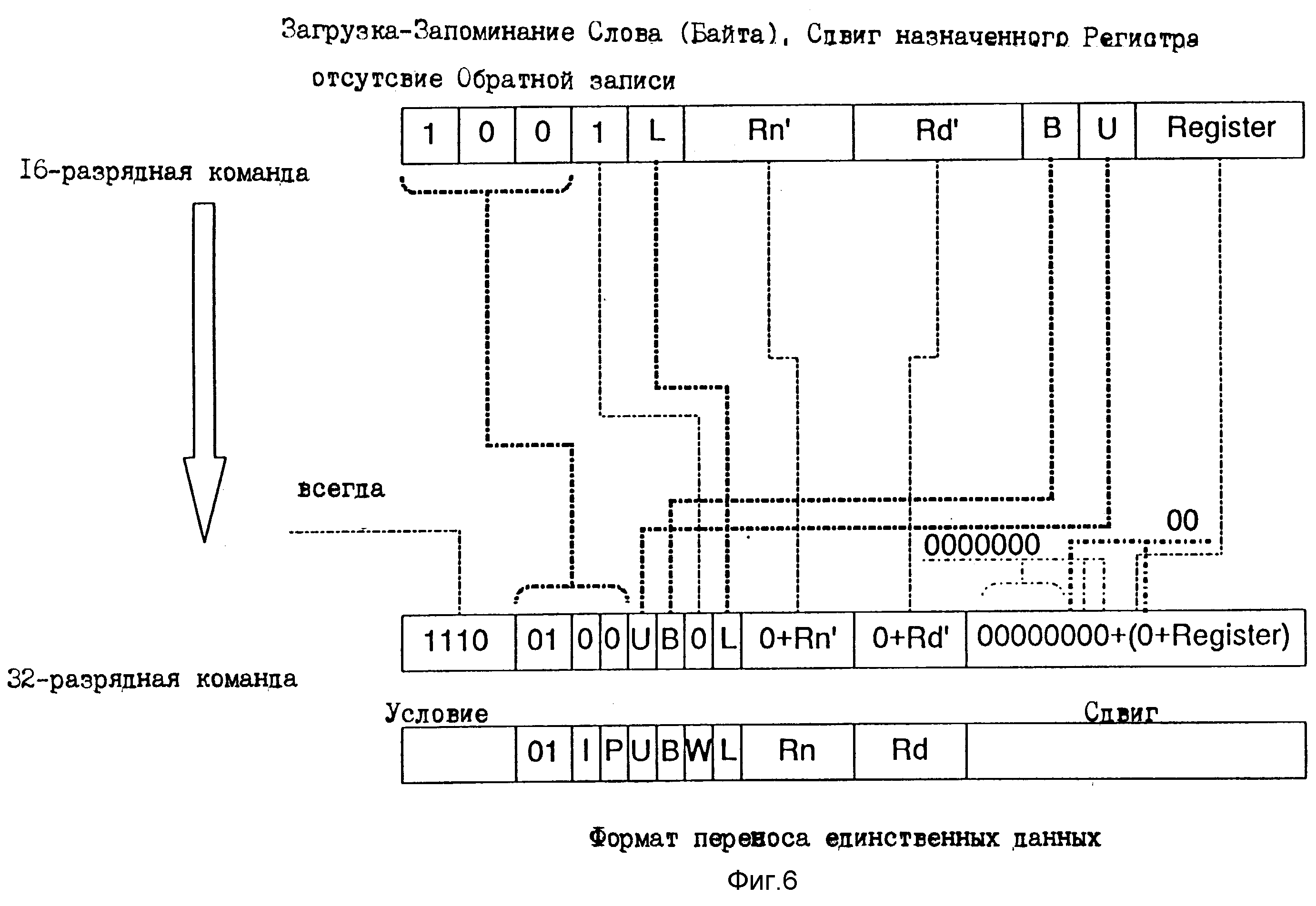

Фиг. 5 и 6 иллюстрируют отображение Y-разрядных программных командных слов в X-разрядные программные командные олова.

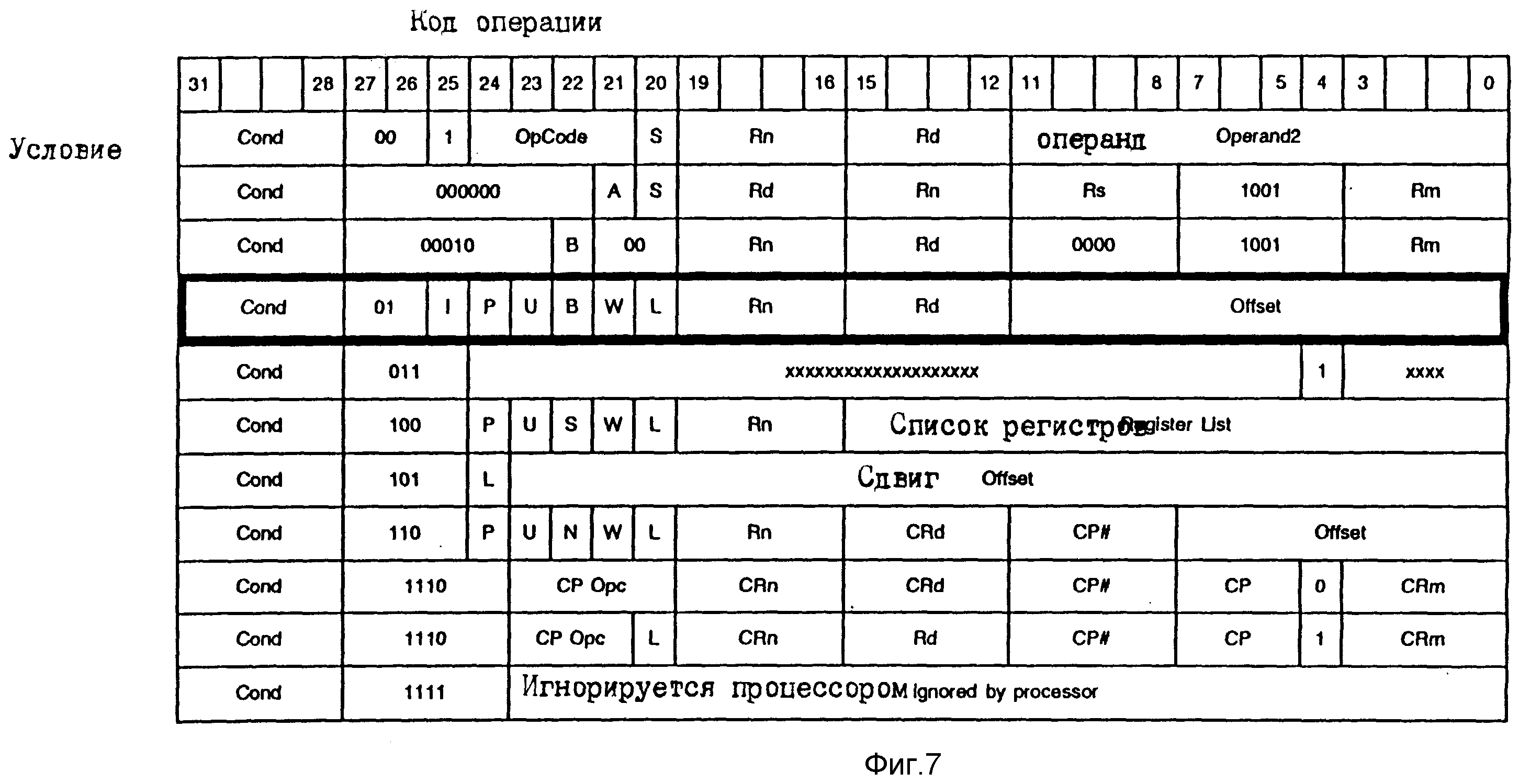

Фиг. 7 представляет набор X-разрядных команд.

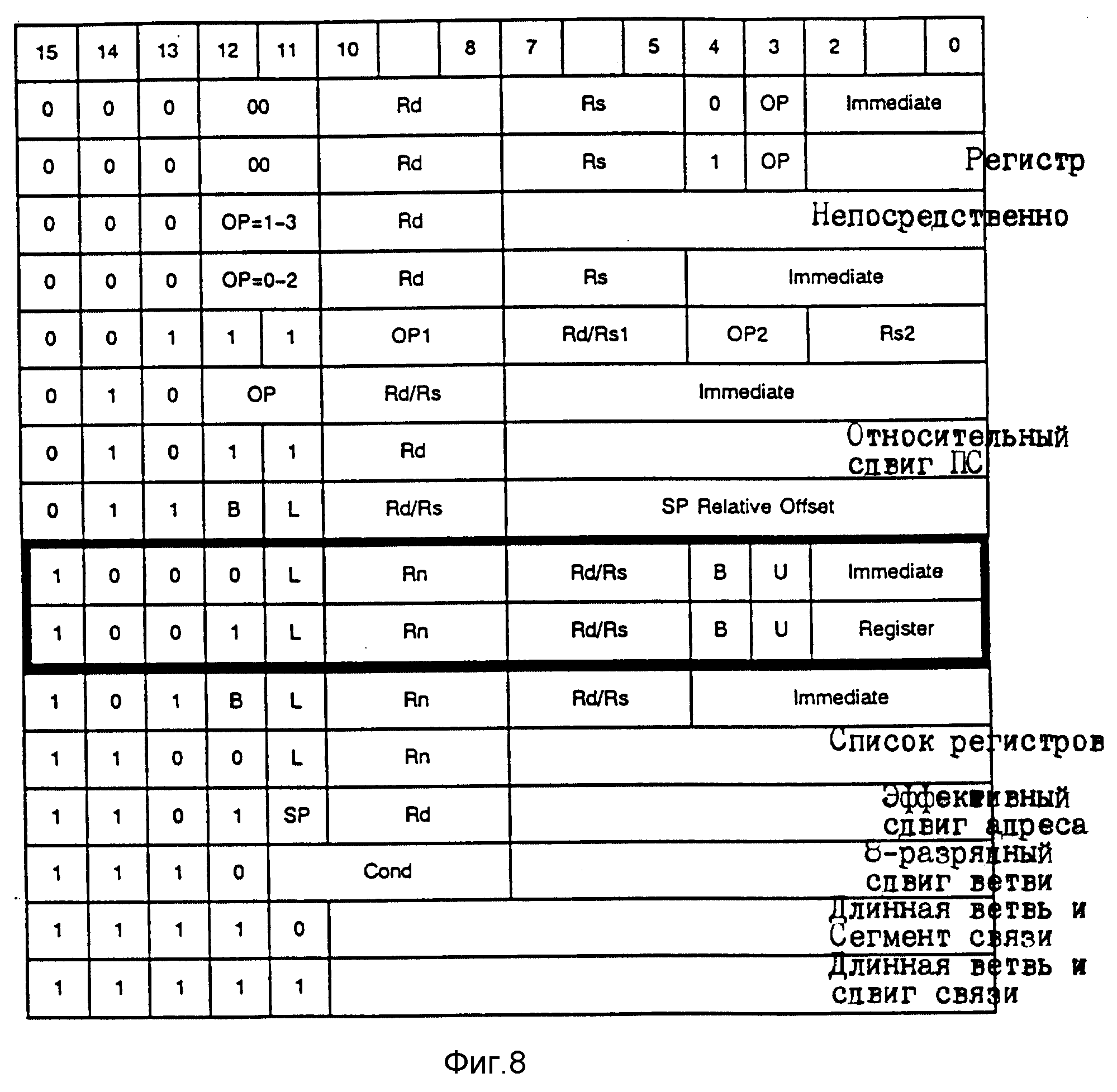

Фиг. 8 представляет набор Y-разрядных команд.

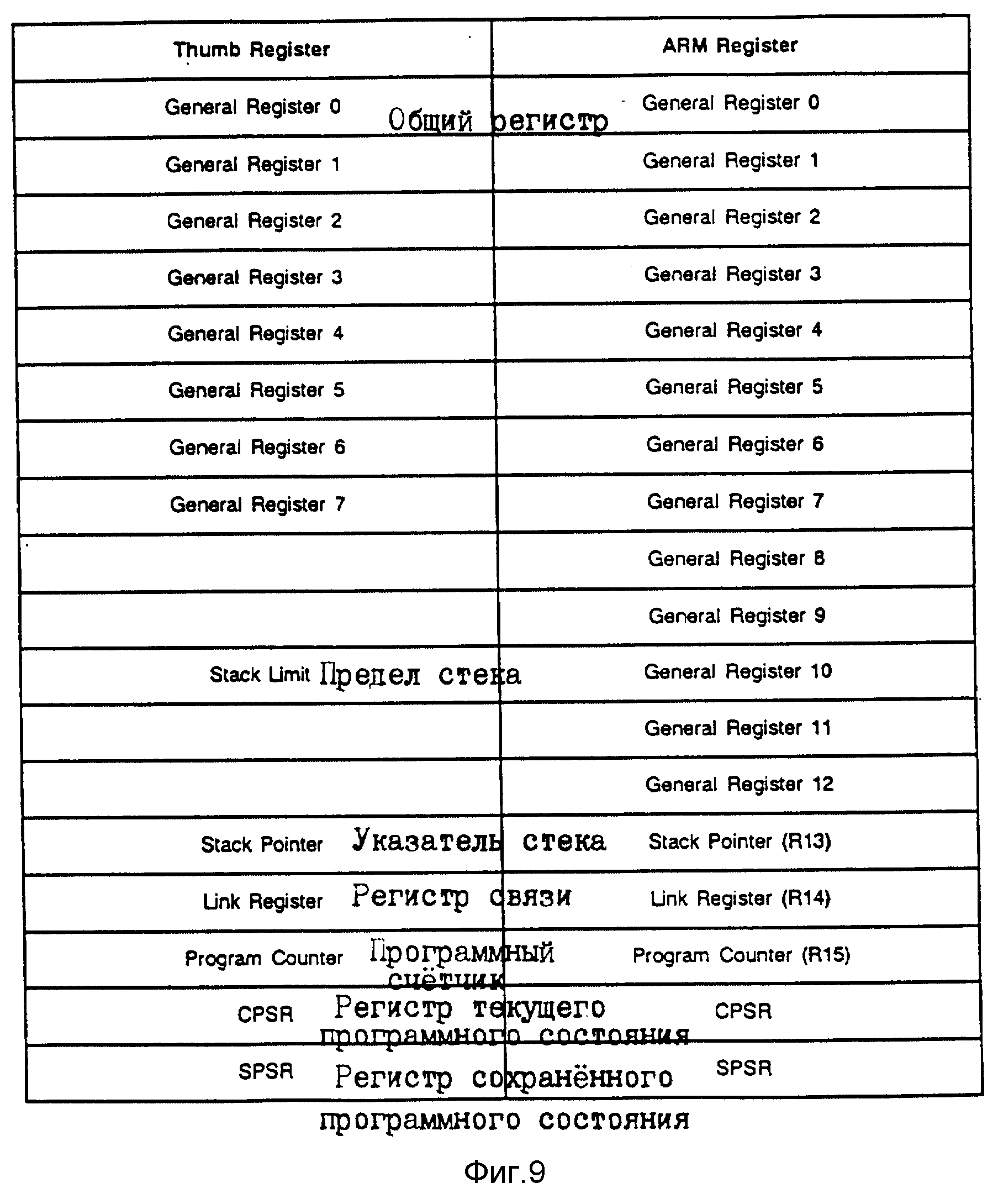

Фиг. 9 представляет регистры обработки, доступные для первого набора команд и для второго набора команд.

Фиг. 1 представляет систему обработки денных (которая выполнена как часть интегральной схемы), содержащую процессорное ядро 2, подключенное к Y- разрядной запоминающей системе 4. В данном случае Y равно 16.

Процессорное ядро 2 включает в себя блок 6 регистров, перемнежитель 8 Бутса, циклический сдвиговый регистр 10, 32-разрадиый арифметико-логический блок 12 и регистр 14 записываемых данных. Между процессорным ядром 2 и запоминающей системой 4 введен командный конвейер 16, командный декодер 18 и регистр 20 считываемых данных. Регистр 22 программного счетчика, который является частью процессорного ядра 2, показан адресующим запоминающую систему 4. Формирователь 24 приращений программного счетчика служит для приращения значения программного счетчика в регистре 22 программного счетчика по мере того, как выполняется каждая команда и следует выбрать новую команду для командного конвейера 16.

Процессорное ядро 2 включает в себя N-разрядные магистрали данных (в данном случае 32-разрядные магистрали данных) между различными функциональными блоками. В процессе работы команды в командном конвейере 16 декодируются командным декодером 18, который вырабатывает различные управлявшие сигналы ядра, поступающие на различные функциональные элементы в процессорном ядре 2. В ответ на эти управляющие сигналы ядра различные части процессорного ядра проводят 32-разрядные операции обработки, такие как 32-разрядные перемножение, 32-разрядное сложение и 32-paзpядныe логические операции.

Блок 6 регистров включают в себя регистр 26 текущего программного состояния и регистр 28 сохраненного программного состояния, регистр 26 текущего программного состояния хранит различные флаги условия и состояния для процессорного ядра 2. Эти флаги могут включать в себя флаги режимов обработки (например, системный режим, пользовательский режим, режим выбрасывания ив памяти и т. п. ), а также флаги, указывающие на появление нулевых результатов в арифметических операциях, переносы и тому подобное. Регистр 28 сохраненного программного состояния (который может быть одним из блоковой группы таких регистров сохраненного программного состояния) используется для временного хранения содержимого регистра 26 текущего программного состояния, если имеет место особая ситуация которая вызывает срабатывание переключателя режимов обработки. Таким образом, обработка особой ситуации может выполняться быстрее и более эффективно.

В регистр 26 текущего программного состояния включен флаг Т набора команд, который действует совместно с переключателем наборов команд. Переключатель наборов команд реагирует на флаг Т набора команд и осуществляет выбор либо первого режима обработки, использующего первое декодирующее средство при приеме программного командного слова, либо второго режима обработки, использующего второе декодирующее средство при приеме программного кодового слова. Флаг набора команд подается на командный декодер 18 и формирователь 24 приращений программного счетчика. Когда этот флаг Т набора команд установлен, система работает с командами из второго набора команд (т.е. с Y- разрядными программными командными словами, в данном случае с 16- разрядными программными командными словами). Флаг Т набора команд управляет формирователем 24 приращений программного счетчика для выбора меньшего шага приращений при работе со вторым набором команд. Это связано с тем, что программные командные слова из второго набора команд имеют меньший размер и поэтому расположены более тесно в ячейках памяти запоминающей системы 4.

Как упомянуто выше, запоминающая система 4 представляет собой 16-разрядную запоминающую систему, подключенную 16-разрядными шинами данных к регистру 20 считываемых данных и командному конвейеру 16. Такие 16-разрядные запоминающие системы проще и дешевле по отношению к 32-разрядным запоминающим системам с более высокими характеристиками. При использовании такой 16-разрядной запоминающей системы 16-разрядные программные командные слова могут выбираться за единственный цикл. Однако, если из второго набора команд должны использоваться 32- разрядные команды (как указано флагом Т набора команд), то для подачи единственной 32-разрядной команды в командный конвейер 16 требуются две выборки команд.

Когда требуемые программные командные слова извлечены из запоминающей системы 4, они декодируются командным декодером 18 для инициирования 32-paзpяднoй обработки в процессорном ядре 2 безотносительно к тому, являются ли команды 16-разрядными или 32- разрядными.

Командный декодер 18 представлен на фиг. 1 как единственный блок. Однако для того, чтобы иметь дело более чем с одним набором команд, командный декодер 18 имеет более сложную конструкцию, как будет рассмотрено в связи с фиг. 2 и 3.

Фиг. 2 представляет командный конвейер 16 и командный декодер 19 для работы с единственным набором команд. В этом случае командный декодер 18 включает в себя только первое декодирующее средство 30, которое обеспечивает декодирование 32-раарядиых команд. Это декодирующее средство 30 декодирует первый набор команд (набор команд РАО - режима асинхронного ответа (АRМ)) с использованием программируемой логической матрицы (ПЛМ) (PLА) для выработки множества управляющих сигналов 32 ядра, которые подается на процессорное ядро 2. Программное командное олово, которое декодируется в настоящий момент (т. е. производит текущие управляющие сигналы 32 ядра), также хранится в командном регистре 34. Функциональные моменты в процессорном ядре 2 (например, перемножитель 8 Бутса иди блок 6 (регистров) считывают операнды необходимые для их операций обработки, непосредственно из этого командного регистра 34.

Особенностью работы такого устройства является то, что первое декодирующее средство 30 требует некоторые из своих входных сигналов (P разрядов, показанные сплошной линией, выходящей из конвейерной ступени PipeC) раньше в тактовом цикле, в котором работает первое декодирующее средство. Это необходимо, чтобы гарантировать, чтобы управляющие сигналы 32 ядра генерировались во время, чтобы возбуждать необходимые элементы в процессорном ядре 2. Первое декодирующее средство 30 является относительно большой и медленной структурой из программируемых логических матрицах, и поэтому такие условия согласования по времени важны.

Разработка таких структур на программируемых логических матрицах для выполнения декодирования команд является обычной в технике. Набор входных сигналов определяется вместе с желательными выходными сигналами, генерируемыми из этих входных сигналов. Затем используется коммерчески доступное программное обеспечение, чтобы разработать структуру ПЛМ, которая будет генерировать определенный набор выходных сигналов, исходя из определенного набора входных сигналов.

Фиг. 3 представляет систему по фиг. 2, измененную для того, чтобы декодировать первый набор команд и второй набор команд. Когда первый набор команд выбирается посредством флага Т набора команд, система работает, как описано выше в связи с фиг. 2. Когда флаг Т набора команд указывает, что в командном конвейере 16 имеются команды из второго набора команд, активизируется второе декодирующее средство 36.

Это второе декодирующее средство декодирует 16-разрядные команды (команды Thumb) с использованием быстрой ПЛМ 38 и параллельной медленной ПЛМ 40. Быстрая ПЛМ 38 служит для отображения поднадбора (Q разрядов) разрядов 16-разрядных команд Thumb 6 с P разрядами соответствующих 32-разрядных команд PAO, которые требуются для возбуждения первого декодирующего средства 30. Поскольку для осуществления этого отображения требуется относительно малое число разрядов, быстрая ПЛМ 38 может быть относительно небольшой и поэтому работать достаточно быстро, чтобы дать первому декодирующему средству достаточно времени для генерирования управляющих сигналов 32 ядра в ответ на содержимое конвейера PipeC. Можно считать, что быстрая ПЛМ 38 действует, "подделывая" критические разряды соответствующей 32-paзpядной команды для первого декодирующего средства без затрат какого-либо ненужного времени на отображение полной команды.

Однако полная 32-paзpяднaя команда все же требуется процессорному ядру 2, если оно должно быть способно работать без коренных изменений и значительных дополнений схемными элементами. Вместе с критическим по времени отображением, выполняемым быстрой ПЛМ 38, включенная в параллель медленная ПЛМ 40 служит для отображения 16- разрядной команды на соответствующую 32-разрядную команду и помещения ее в командный регистр 34. Это более сложное отображение может осуществляться за полное время, требуемое для работы быстрой ПЛМ 38 и первого декодирующего средства 30. Важным фактором является то, что 32-paзpяднaя команда должна присутствовать в командном регистре 34 достаточное время, чтобы любой операнд мог быть считан оттуда в ответ на управляющие сигналы 32 ядра, действующие на процессорное ядро 2.

Следует иметь в виду, что общее действие системы по фиг. 8 при декодировании второго набора команд состоит в переводе 16-разрядных команд из второго набора команд в 32-разрядные команды из первого набора команд по мере их поступления по командному конвейеру 16. Практически возможность этого обеспечивается представлением второго набора команд поднабором первого набора команд, чтобы гарантировать, что имеется отображение один к одному команд из второго набора команд в команды в первом наборе команд.

Обеспечение флага Т набора команд позволяет второму набору быть неортогональным с первым набором команд. Это практически полезно в обстоятельствах, где первый набор команд является существующим набором команд без каких-либо свободных разрядов, которые можно использовать для обеспечения набора дополнительных ортогональных команд, подлежащих обнаружению и декодированию.

Фиг. 4 иллюстрирует декодирование 32-разрядной команды. В верхней части фиг. 4 представлены следующие друг за другом тактовые периоды обработки, в которые осуществляются операция выборки, операция декодирования и, наконец, операция исполнения. Коли требуется конкретная команда (например, команда перемножения) то могут быть добавлены один или более исполнительных периодов.

32-Разрядная команда состоит из группы различных полей. Границы между этими полями будут отличатся для разных команд, как будет позже показано на фиг. 7.

Некоторые из разрядов в команде 42 требуют декодирования в первоначальной фазе декодирования. Этими P разрядами являются разряды с 4 по 7, 20 и с 22 по 27. Это разряды, которые требуются первому декодирующему средству 30 и которые должны быть "подделаны" быстрой ПЛМ 38. Эти разряды должны подаваться на первое декодирующее средство и декодироваться, тем самым генерируя соответствующие управляющие сигналы 32 ядра к концу первой части периода декодирования. Декодирование полной команды может, если потребуется, занять время до конца периода декодирования. В конце периода декодирования операнды в команда считываются из командного регистра 34 процессором 2 в течение исполнительного периода. Эти операнды могут быть регистровыми определителями, сдвигами и другими переменными.

Фиг. 5 показывает отображение примера 16-разрядной команды в 32-разрядную команду. Толстые линии начинаются от Q разрядов в 16-разрядной команде, которые требуют отображения в P разрядов в 32- разрядной команде, чтобы они могли подаваться на первое декодирующее средство 30, можно видеть, что большинство этих разрядов либо копируются непосредственно, либо включают простое отображение. Операнды Rn, Rd и Immediate ("Непосредственный") в 16-разрядной команде требуют заполнения нулями их старших разрядов для получения 32-paзpяднoй команды. Это заполнение необходимо из-за того, что операнды 32-разрядной команды имеют больший диапазон, нежели операнды 16-разрядной команды.

Из обобщенной формы 32-разрядной команды, приведенной в нижней части фиг. 5, видно, что 32-разрядная команда обеспечивает значительно большую гибкость, чем поднабор тех команд, которые представлены 16-разрядной командой. К примеру, 32-разрядные команды предваряются кодами условия Cond., которые задают команду, исполняемую при определенном условии. В противоположность этому, 16-разрядные команды не несут в себе каких-либо кодов условия, и коды условия 32-разрядных команд, в которые они отображаются, устанавливаются в значение "1110", что эквивалентно состоянию исполнения по условию "всегда".

Фиг. 6 иллюстрирует другое такое отображение команд. В этом случае 16-разрядная команда имеет вид команды Загрузка-Запоминание, отличающийся от вида, представленного на фиг. 5. Однако эта команда все же является поднабором единственной команды передачи данных из набора 32-разрядных команд.

Фиг. 7 представляет схематически форматы одиннадцати различных видов команд для

набора 32-разрядных команд. Этими командами являются по очереди:

1) Перенес РПС (регистра программного состояния -PSК) обработки данных;

2) Перемножение;

3) Обмен

единственными данными;

4) Перенос единственных данных;

5) Неопределенная;

6) Перенос блочных данных:

7) Ветвление;

8) Перенос данных сопроцессора;

9) Обработка данных сопроцессора;

10) Перенос в регистр сопроцессора;

11) Прерывание программного обеспечения.

Полное описание этого набора команд можно найти в Листе данных процессора A M6, выпускаемого Эдванст РИСК Машина Лимитед. Команда, выделенная на фиг. 7, та же, что и представленная на фиг. 5 и 6.

Фиг. 8 иллюстрирует набор 16-раврядных команд, который представлен в дополнение к набору 32-разрядных команд. Команды, выделенные в этом наборе команд, те же, что и представленные на фиг. 5 и 6 соответственно. В этом наборе 16- разрядных команд выбраны такие команды, которые могут быть все отображены в единственную 32-разрядную команду и сформировать таким образом поднабор набора 32-разрядных команд.

Форматы поочередно

рассматриваемых в этом наборе команд определяют следующее:

Формат 1: Ор=0,1. Оба операнда устанавливают флаги кодов условия.

0: ADD Rd. Rs. #Immediate3

1: SUB Rd, Rs.

#Immediate3

Формат 2: Оp=0,1. Оба операнда устанавливают флаги кодов условия.

0: ADD Rd. Rm, Rn

1: SUB Rd. Rm, Rn

Формат 3: 3 кода операции. Используются для

построения больших непосредственных операндов.

1 = ADD Rd, Rd, #Immediate 8<<8

2 = ADD Rd, Rd. #Immediate 8<<16

3 = ADD Rd. Rd. #Immediate

8<<24

Формат 4: Op дает 3 кода операции, все операции являются MOVS Rd, Rs SHIFT # Immediate 5, где SHIFT есть, 0 есть LSL, 1 есть LSR, 2 есть ASR. Сдвиги на ноль - как

определено на ARM.

Формат 5: Ор1*8+Ор2 дает 32 кода операций АЛУ,Rd=Rdор Rn,

Все операции устанавливают флаги кодов условия. Операциями являются AND, OR, EOR, BIC

(AND NOT), NEGATE, CMP, CMN, MUL TST, TEQ, MOV, MVN (NOT), LSL, LSR, ASR, ROR

Выпадение ADC, SBC, MULL. Сдвиги на ноль и больше 31 - как определено ARM.

8 специальных кодов операции, LO определяет Reg 0-7, H1 определяет регистр 8-15.

SPECIAL в CPSR или SPSR

MOV H1, LO (сдвиг скрытого регистра в видимый регистр)

MOV LO, H1 (сдвиг видимого

регистра в скрытый регистр)

MOV H1, H1 (например, возврат процедуры)

MOVS H1, H1 (например, возврат исключительной ситуации)

MOVS H1, LO (например, возврат прерывания, может

быть SUВS, H1, H1, #4)

MOV SPECIAL, LO (MSR)

MOV LO, SPECIAL (MRS)

CMP H1, H1 (проверка предела стека) 8 свободных кодов операций

Формат 6: Ор дает 4 кода операций.

Все операции устанавливают флаги кодов условия

0: MOV Rd, #Immediate 8

1: CMP Rs, #Immediate 8

2: ADD Rd, Rd, #Immediate 8

Возможно поменять ADD на ADD Rd, Rs,

#Immediate 5

Формат 7: Загрузки слова PC + Offset (256 слов, 1024 байта) Отметим, что сдвиг (offset) должен быть подчеркнутым словом

LDR Rd, [PC,#+102]

Эта команда

используется для выбора следующего буквенного накопителя, для загрузки констант, адресов и т.п.

Формат 8: Загрузить и Запомнить Слово из SP (r7) + 256 слов (1024 байта)

Загрузить и Запомнить Слово из SP (r7) + 256 байтов

LRD Rd, [SP, #+102)

LDRB Rd, [SP, #+256]

Эти команды служат для выбора стека и кадра

Формат 9: Загрузить и

Запомнить Слово (или Байт), обозначенные 3 разряда Непосредственно Сдвинуть (Post lnc/Dec), Обратная запись под воздействием Вмешательства (в работу) L есть Загрузить-Запомнить, U есть Вверх- Вниз

(сдвиг сложения-вычитания, B есть Байт-Слово

LDR {В} Rd, [Rb],#+/-Offset3

STR {В} Rd, [Rb],#+/-0ffset3

Эти команды предназначены для выбора матрицы Сдвиг декодирует 0- 7 для

байтов и 0,4-28 для слов

Формат 10: Загрузить и запомнить Слово (или Байт) с обозначенным Сдвигом Регистра (Pre Inc/Dec), Обратной записи нет L есть Загрузить-Запомнить, U есть Вверх-Вниз

(сдвиг сложения-вычитания) B есть Байт-Слово

LDR Rd, [Rb, +/-Ro, LSL#2]

STR Rd, [Rb, +/-Ro, LSL#2]

LDRB Rd, [Rb, +/-Ro]

STRB Rd, [Rb. +/-Ro]

Эти команды

предназначены для выбора указателей базы + сдвига и, комбинируясь с 8-разрядными MOV,

ADD, SUB, дают очень быструю непосредственную выборку сдвига.

Формат 11: Загрузить и

Запомнить Слово (или Байт) с обозначенными 5 разрядами Непосредственного сдвига (Pre Inc/Dec), Обратной записи нет L есть Загрузить-Запомнить, B есть Байт-Слово

LDR{B} Rd, [Rb, #+Offset5]

STR{B} Rd, [Rb, #+Offset5]

Эти команды предназначены для выборки структуры Сдвиг декодирует 0 - 31 для байтов и 0,4- 124 для слов

Формат 12: 3агрузить и Запомнить Множество

(Обратная запись под воздействием вмешательства в работу)

LDMIA Rb!, {Rlist}

STMIA Rb!, {Rlist}

Rlist определяет регистры r0-r7

Подклассом этих команд является пара

команд вызова и возврата подпрограммы.

Для LDM, если r7 является базовым и разряд 7 установлен в rlist, загружается PC

Для STM, если r7 является базовым и разряд 7 установлен

в rlist, запоминается LR

Если r7 используется в качестве базового регистра, вместо него используется sp

В обоих случаях Полностью Спущенный Стек воплощает ie LDM подобна LDMFD в ARM,

STM подобна STMFD в ARM

Поэтому для копирования блока используйте r 7 в качестве конечного указателя. Ели r 7 не является базовым, LDM и STM подобны LDMIA и STMIA В ARM.

Формат 13: 3агрузить адрес. Эта команда добавляет 8-разрядную необозначенную константу либо к PC, либо к стековому указателю и запоминает результаты в регистре назначения

ADD Rd,sp + 256

байтов

ADD Rd,pc + 256 слов (1024 байта)

Разряд SP указывает, является ли источником SP или PC. Если источником является SP, а r 7 определен как регистр назначения, SP используется

как регистр назначения.

Формат 14: Ветвление по условию, +/- 128 байтов, где со определяет код условия (как в ARM) cond = 15 кодируется как SWI (только 256, должно быть достаточно).

Формат 15: Установки разрядов 22:12 длинной ветви и связи.

WOV lr, #offset <<12.

Формат 16: Выполнения длинной ветви и связи. Операцией является SUB newlr, pc, # 4; ORR pc, oIdIr, #offset << 1. NewIr и oIdIr означает регистр Ir до и после операции.

Как упомянуто выше, набор 16-разрядных команд имеет уменьшенные диапазоны операндов по сравнению с набором 32-разрядных команд. В соответствии с этим, набор 16-разрядных команд используют поднабор регистров 6 (см. фиг. 1), которые предназначены для полного набора 32-разрядных команд. Фиг. 9 представляет поднабор регистров, которые используются набором 16-разрядных команд.

Реферат

Изобретение относится к вычислительной технике, а конкретнее к обработке данных с использованием множества наборов командных слов программы. Техническим результатом является повышение производительности за счет использования двух наборов команд. Устройство содержит процессорное ядро, два декодирующих средства, переключатель наборов команд. Способ описывает функционирование устройства обработки данных. 2 с. и 9 з.п.ф-лы, 9 ил.

Комментарии