Способ формирования s-блока - RU2607613C2

Код документа: RU2607613C2

Чертежи

Описание

Область техники, к которой относится изобретение

Предполагаемое изобретение относится к области обработки информации и криптографии и, в частности, к способам формирования S-блоков замены с минимальным количеством логических элементов, для последующего использования в аппаратуре систем обработки данных и криптографической защиты информации.

Уровень техники

Операции замены

Способы формирования S-блоков с минимальным количеством логических элементов известны и зависят от состава логических элементов схемотехнической реализации.

Так, для набора логических элементов, реализующих логические операции И (&), ИЛИ (V), НЕ (¬), известны метод Квайна-МакКласки, алгоритм Блейка – Порецкого и др. [1]. Однако, известные методы предназначены для оптимизации одной булевой функции, а не набора из

Известен способ минимизации булевой функции для набора логических элементов {&, ⊕}, предложенный как составная часть процесса запоминания цифровой информации [2]. Однако, этот способ также предназначен для минимизации только одной булевой функции и не учитывает возможности совместной оптимизации нескольких булевых функций, представляющих S-блок. При этом, в данном способе оптимизируется суммарное число элементов & и ⊕ и не принимается во внимание, что схемотехнические затраты на реализацию операций & и ⊕ могут существенно отличаться друг от друга.

Наиболее близким по своей технической сущности к заявляемому является известный способ эффективной реализации S-блока, используемого в стандарте криптографической защиты информации AES [3], в котором, наряду с оптимизацией времени вычисления S-блока, решается и задача минимизации числа логических элементов {&, ⊕} при реализации данного S-блока.

Известный способ [3] выбирается в качестве прототипа.

Основным недостатком прототипа является то, что он предназначен исключительно для S-блоков частного вида, а именно, для S-блоков, задаваемых несколькими (небольшим числом) операций в конечном поле

Другим недостатком (ограничением) прототипа является то, что он осуществляет минимизацию числа логических элементов {&, ⊕} для реализации S-блока в несколько тактов/шагов (для итеративной схемы реализации). При этом число итераций при вычислениях S-блока возрастает с увеличением размера m конечного поля

Раскрытие изобретения

Техническим результатом предлагаемого способа является

1) уменьшение схемотехнических затрат при реализации S-блока с помощью логических элементов & и ⊕,

2) возможность учета различных схемотехнических затрат на реализацию элементов & и ⊕ в процессе минимизации результирующей логической схемы S-блока.

В заявленном способе также отсутствуют ограничения на значения

S-блок осуществляет замену входного двоичного вектора

S-блок однозначно задается аналитически координатными булевыми функциями

В предлагаемом способе рассматривается представление координатных булевых функций S-блока через приведенные многочлены Жегалкина: каждая функция

где

Существуют и другие, отличные от приведенного многочлена Жегалкина, формы представления булевых функций, например: таблица истинности, дизъюнктивная нормальная форма (ДНФ), конъюнктивная нормальная форма (КНФ). Процессы перехода от одного вида представления к другому хорошо известны. Например, в известном способе [4] приведена последовательность перехода от таблицы истинности к представлению булевой функции через приведенный многочлен Жегалкина. В заявляемом способе не имеет значения, каким образом формируется исходное аналитическое представление S-блока через приведенные многочлены Жегалкина:

Для построения оптимальной логической схемы реализации S-блока через операции & и ⊕ в заявляемом способе используются предварительные аналитические вычисления, использующие операции над множествами. Для получаемого в результате схемотехнического решения не имеет значения, какие используются представления множеств (характеристический вектор, список элементов, в том числе упорядоченный список, и т.д.) и с помощью каких преобразований осуществляются операции над множествами.

Прямой способ реализации S-блока (1), заданного множеством приведенных многочленов Жегалкина

1. Составляют множество

где

Каждый моном

2. Каждый многочлен

В этом способе схема реализации монома

Аналогично, схема реализации многочлена

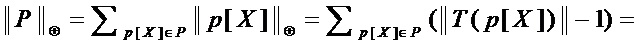

Тем самым, аддитивная сложность

где

Если схемотехнические затраты на реализацию операции & составляют

Заявляемый способ состоит из аналитического этапа, на котором выполняется последовательная декомпозиция исходных многочленов, задающих S-блок, на суммы и произведения более простых многочленов, для реализации которых требуется меньше суммарных схемотехнических затрат, этапа синтеза, на котором создаются схемы реализации этих, далее не упрощаемых, многочленов и на основе этих схем в порядке обратном декомпозиции строится итоговая логическая схема реализации S-блока, и третьего этапа, в ходе которого итоговая логическая схема реализуется в электронной схеме.

На каждом шаге декомпозицию множества многочленов осуществляют одним из двух следующих преобразований.

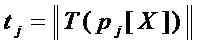

Преобразование 1 определяется парой многочленов

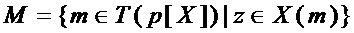

• выделяют множество

• вычисляют мощность

• если

• если

• вычисляют, в качестве декомпозиции многочленов

в которых слагаемые, равные 0, обозначают, что операцию ⊕ реализовывать не требуется;

• формируют результирующее множество многочленов

• вычисляют эффективность преобразования (величину уменьшения схемотехнических затрат) в виде

Преобразование 2 определяется параметром

• для рассматриваемого многочлена

• вычисляют мощность

• если

• если

◯ из мономов множества

причем моном

◯ из мономов множества

◯ вычисляют многочлен

◯ приводят подобные члены в

◯ если число мономов многочлена

то в качестве декомпозиции многочлена

▪ включают в результирующее множество многочленов

▪ принимают значение сложности декомпозиции

◯ если же

то в качестве декомпозиции многочлена

▪ включают в результирующее (формируемое) множество многочленов

▪ принимают значение сложности декомпозиции

Эффективность преобразования 2 (величину уменьшения схемотехнических затрат) для рассматриваемого множества многочленов

где значения

Для минимизации схемотехнических затрат на реализацию мономов из множества

Преобразование 3 состоит из следующих вычислений и операций:

• осуществляют во множестве мономов

где

• если

• если

• составляют мономы

в которых сомножители, равные 1, обозначают, что операцию & реализовывать не требуется;

• формируют результирующее множество мономов

Предлагаемый способ минимизации схемотехнических затрат на реализацию S-блока, заданного многочленами Жегалкина

1. Исходное множество многочленов

последовательно преобразовывают с использованием преобразований 1 и 2:

где каждый переход имеет эффективность больше нуля (т.е. приводит к снижению оценки суммарных схемотехнических затрат и осуществляется к результирующему множеству многочленов, формируемому в ходе этих преобразований). Результирующее множество

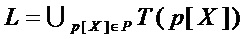

2. Затем, по результирующему множеству

где

3. Затем осуществляют разложение мономов множества

Поскольку переменные

4. Построение логической схемы S-блока начинают проходом по цепочке

5. После построения логических схем мономов из множества

6. Далее осуществляют проход по цепочке

7. Выходы логических схем многочленов множества

В описанном способе минимизации схемотехнических затрат не специфицированы параметры, которые используются для переходов

В заявляемом способе предлагается выбирать параметры перехода так, чтобы на каждом переходе

Необходимо отметить, что построение (формирование) логической схемы, реализующей соответствующую булеву функцию, является известным процессом (этот процесс описан, например, в [1, 4]).

Реализация электронной схемы на основе полученной логической схемы также является известным процессом и может быть выполнена как на дискретных элементах, так и с использованием интегральных микросхем, в том числе программируемых логических интегральных микросхем (ПЛИС), по выбору разработчика.

Краткое описание чертежей

На фиг. 1 показана начальная логическая схема для примера реализации способа.

На фиг. 2 показана промежуточная логическая схема для примера реализации способа.

На фиг. 3 показана промежуточная логическая схема для примера реализации способа.

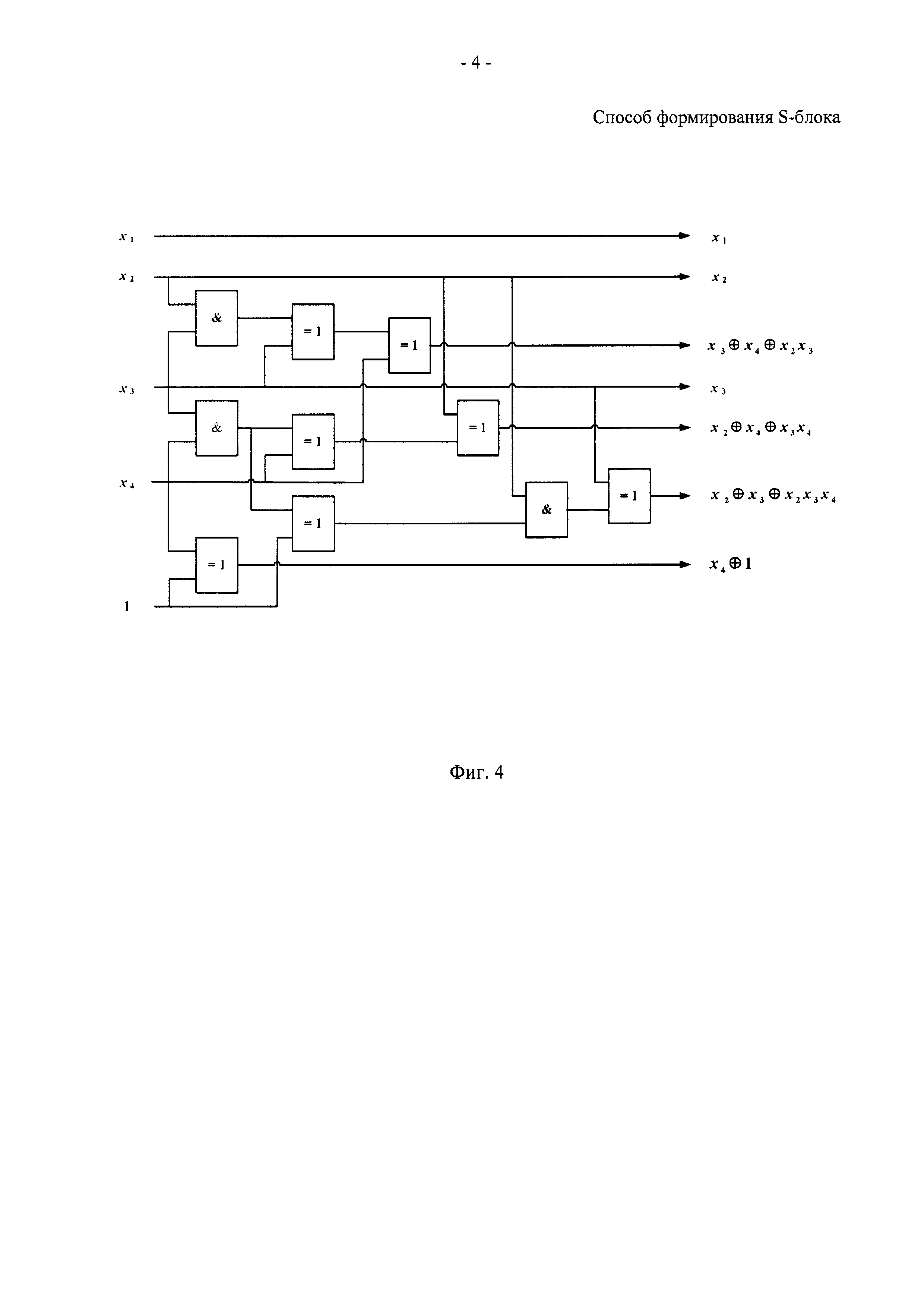

На фиг. 4 показана промежуточная логическая схема для примера реализации способа.

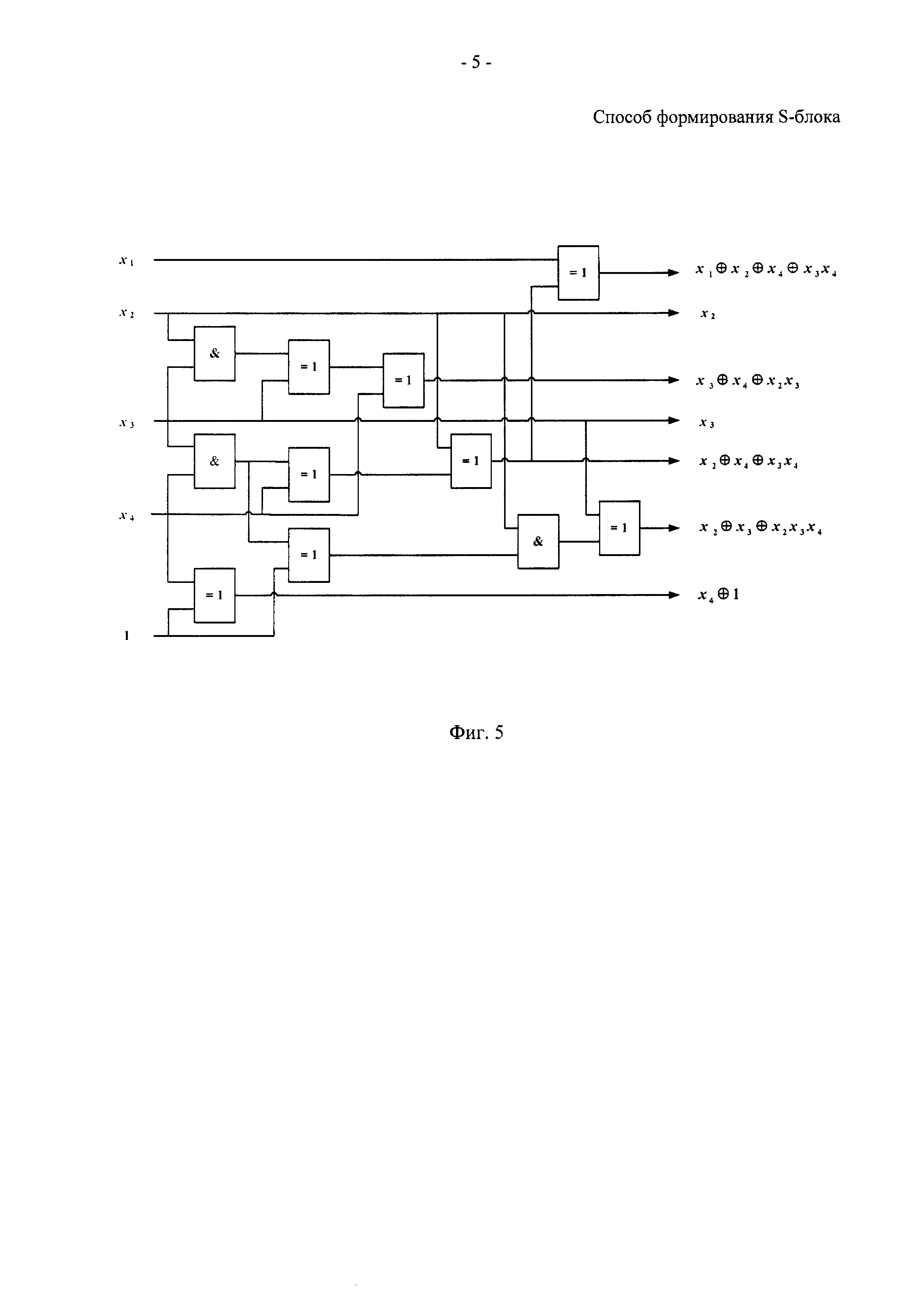

На фиг. 5 показана промежуточная логическая схема для примера реализации способа.

На фиг. 6 показана финальная логическая схема для примера реализации способа.

Осуществление изобретения

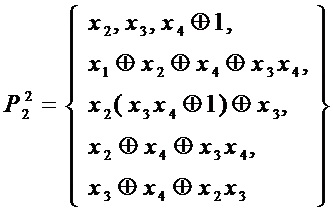

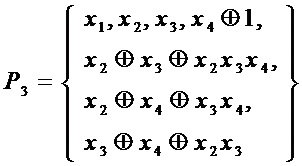

Рассмотрим пример реализации предложенного способа для S-блока, имеющий

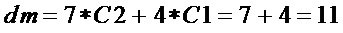

Прямой способ реализации этого S-блока требует 11 операций & для формирования мономов

Рассмотрим применение предлагаемого способа в условиях, когда схемотехнические затраты на реализацию операций & и ⊕ совпадают, т.е.

Число общих мономов у любой пары многочленов не превышает 1, поэтому способ из прототипа не дает выигрыша по количеству операций, т.е. не приводит к снижению схемотехнических затрат.

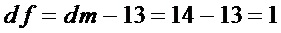

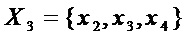

В предлагаемом способе этому S-блоку соответствуют исходные значения:

У любых двух многочленов из множества

и величину имеющегося снижения сложности

С этапа А3 до этапа А4 по очереди перебирают переменные

или

в записи которого меньше операций

Для рассматриваемого множества многочленов

Для

сложность

Для

сложность

Для

сложность

Для

сложность

Наибольшее снижение сложности (значение

Для множества многочленов

На этапе А2 вычисляют сложность прямой реализации множества многочленов

и снижение сложности за счет выделения общего слагаемого

На этапах с А3 по А4 разложение многочленов множества

Для

сложность

Для

сложность

Для

сложность

Наибольшее снижение сложности (значение

Поэтому на этапе А4 при переходе на этап А1 при

Число общих мономов у любой пары многочленов из множества

и сложность прямой реализации

На этапах с А3 по А4 разложение многочленов множества

Для

сложность

Для

сложность

Для

сложность

Наибольшее снижение сложности имеет место при

Число общих мономов у любой пары многочленов из множества

Никакой из двух вариантов разложения не приводит к снижению оценки сложности, поэтому формируют множество мономов

и переходят к этапу А5 при

На этапе А5 при

В множестве мономов

Схема для множества

Переход к схеме для множества

При переходе к схеме для множества многочленов

При переходе от схемы для множества многочленов

При переходе от схемы для множества многочленов

Переход от схемы для множества многочленов

В полученной финальной схеме реализации S-блока (фиг. 8) использовано 11 операций ⊕ и 6 операций &, что меньше исходных значений 13 операций ⊕ и 11 операций &.

Таким образом, предлагаемый способ уменьшает схемотехнические затраты – количество элементов, реализующих операции & и ⊕ при формировании заданного S-блока.

В случае исходного S-блока большой размерности процедуру построения логической схемы, согласно предложенному способу, целесообразно автоматизировать путем составления программы для ЭВМ, что вполне может выполнить специалист по программированию (программист) на основе знания действий способа.

Последующая схемотехническая реализация полученного S-блока может быть осуществлена известными методами, предпочтительной формой для использования в современной компьютерной технике является реализация на ПЛИС, но это необязательно. Конкретный выбор варианта схемотехнической реализации зависит от разработчика.

Источники информации, принятые во внимание при формировании заявки

1. Самофалов К.Г. и др. Прикладная теория цифровых автоматов (учебник), Киев, Вища Школа, 1987.

2. Патент РФ № 2331937, приоритет от 24.08.2006 г.

3. Патент США № 7421076, приоритет от 17.09.2003 г.

4. Спирин П.А. Спирина М.С. Дискретная математика (учебник), Издательский центр “Академия”, 2004

Реферат

Изобретение относится к области обработки информации и криптографии и, в частности, к способам формирования S-блоков замены с минимальным количеством логических элементов. Техническим результатом является уменьшение схемотехнических затрат при реализации S-блока с помощью логических элементов & и ⊕ (XOR), обеспечение возможности учета различных схемотехнических затрат на реализацию элементов & и ⊕ в процессе минимизации результирующей логической схемы S-блока. Заявляемый способ состоит из аналитического этапа, на котором выполняется последовательная декомпозиция исходных многочленов, задающих S-блок, на суммы и произведения более простых многочленов, для реализации которых требуется меньше суммарных схемотехнических затрат, этапа синтеза, на котором создаются схемы реализации этих далее не упрощаемых многочленов и на основе этих схем в порядке обратном декомпозиции строится итоговая логическая схема реализации S-блока, и третьего этапа, в ходе которого итоговая логическая схема реализуется в электронной схеме. 6 ил.

Комментарии