Двухпороговый компаратор диапазона двоичных бит - RU2758205C1

Код документа: RU2758205C1

Чертежи

Описание

ОБЛАСТЬ ТЕХНИКИ

Изобретение относится к области вычислительной техники, в частности к устройствам обработки данных, и может быть использовано для построения средств автоматики и функциональных узлов систем управления, а также для обработки результатов физических экспериментов, сигналов и изображений.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Известно устройство для определения количества единиц (нулей) в двоичном числе (RU №2446442, МПК G06F 7/50, Н03К 21/00, заявлено 11.04.2011, опубликовано 27.03.2012, Бюл. №9), содержащее блок управляемой инверсии, состоящий из n-элементов «ИСКЛЮЧАЮЩЕЕ ИЛИ» (n - количество разрядов входного числа), элементы ИЛИ и модули, состоящие из элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента И, которые объединены в группы, состоящие из ярусов, и объединены в k-каскадов (k=]log2n[), так, что каждый i-й каскад содержит g(i)=n/2i групп (i=1, …, k), каждая группа i-го каскада разделена на j ярусов (j=1, …, i), при этом первый ярус каждой группы i-го каскада содержит i модулей, а каждый j-й ярус каждой группы i-го каскада (j=2, … i,) содержит (i-j) модулей и элемент «ИЛИ».

Недостатком данного устройства является определение только общего количества единиц (нулей) в двоичном числе, а не выявление групп диапазона единичных бит.

Известен указатель старшей единицы (Угрюмов Е.П. Цифровая схемотехника. - СПб.: БХВ-Петербург, 2000. - 528 с., рис. 2.8 с. 50-54), содержащий группу элементов И и группу элементов запрета И с одним инверсным входом. В данном устройстве реализована цепочечная схема передачи сигнала опроса путем последовательного опроса, начиная со старшего разряда, и прекращения дальнейшего опроса при выявлении первой же единицы.

Известен указатель старшей единицы (Схемотехника ЭВМ. Сборник задач: учебное пособие. М: НИЯУ МИФИ, 2012. - 240 с., рис. 53, с. 55-56), содержащий группу элементов ИЛИ объединенных в цепочку и группу элементов запрета И с одним инверсным входом.

Недостатком данных устройств является выявление только одного старшего единичного бита.

Известно устройство для детектирования диапазона единичных бит (RU №2717631, МПК G06F 7/74, заявлено 07.11.2019, опубликовано 24.03.2020, Бюл. №9), содержащее N разрядов входной шины D - D1, D2, …, DN, N разрядов выходной шины Q - Q1, Q2, …, QN, первую группу из (N-2) элементов ИЛИ 11, 12, …, 1(N-2), вторую группу из (N-2) элементов ИЛИ 21, 22, …, 2(N-2) и группу из (N-2) элементов И 31, 32, …, 3(N-2). Причем первая группа элементов ИЛИ 11, 12, …, 1(N-2), объединенных в цепочку, формирует упорядоченную группу подряд идущих единиц в младших разрядах, вторая группа элементов ИЛИ 21, 22, …, 2(N-2) формирует упорядоченную группу единиц в старших разрядах, а в группе элементов И 31, 32, …, 3(N-2) осуществляется проверка единичных значений в одноименных разрядах упорядоченных групп единиц.

Недостатком данного устройства является только выявление диапазона единичных бит и формирование между единичным левым (младшим) и правым (старшим) упорядоченной группы единичных бит.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является устройство для детектирования границ диапазона единичных бит (RU №2717934, МПК G06F 7/74, Н03К 21/00, заявлено 19.12.2019, опубликовано 27.03.2020, Бюл. №9), содержащее N разрядную входную шину D, выходную шину QR номера младшего разряда и выходную шину QL номера старшего разряда содержащие по М разрядов, где M=]log2 (N+1)[(большее целое), группу из (N-1) элементов ИЛИ 11, 12, …, 1(N-1), группу из (N-1) элементов ИЛИ-НЕ 21, 22, …, 2(N-1), первый 31 и второй 32 блоки счета младших упорядоченных единиц, а также внутреннюю шину SR сдвига вправо и внутреннюю шину SL сдвига влево, которые содержат по N разрядов.

Недостатком данного устройства является только детектирование границ диапазона единичных бит - выявление номера левого (старшего) единичного бита и номера правого (младшего) единичного бита во входных данных и отсутствие средств для подсчета единичных бит в выявленном диапазоне единиц.

ЗАДАЧА ИЗОБРЕТЕНИЯ

Задачей изобретения является детектирование и подсчет единичных бит как внутри диапазона бит, заданного нижней и верхней границами, так и вне границ.

При обработке результатов физических экспериментов устройство предназначено для выявления и подсчета количества событий внутри заданного диапазона, так и событий выходящие за пределы диапазона.

Техническим результатом изобретения является расширение функциональных возможностей в части возможности в определения количества единичных бит в заданном диапазоне между нижней и верхней границами и количество единичных бит вне диапазона.

КРАТКОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Указанный технический результат при осуществлении изобретения достигается тем, что двухпороговый компаратор диапазона двоичных бит содержит N разрядную входную шину D, входную шину нижнего порога (границы) GL и входную шину верхнего порога (границы) GM содержащие по М разрядов, где M=]log2(N+1)[(большее целое), выходную шину QL количества единичных бит до нижней границы, выходную шину QC количества единичных бит внутри диапазона и выходную шину QM количества единичных бит выше верхней границы, содержащие также по М разрядов, флаг FL единичных бит до нижней границы, флаг FC единичных бит внутри диапазона, флаг FM единичных бит выше верхней границы, а также внутреннюю шину UL младших упорядоченных единиц, внутреннюю шину UC упорядоченных единиц внутри диапазона, внутреннюю шину UM старших упорядоченных единиц, содержащие по М разрядов,

дешифратор нижней границы 1, дешифратор верхней границы 2, первую группу 31, 32, …, 3N-1 и вторую группу 41, 42, …, 4N-1 каждая из которых содержит (N-1) элементов ИЛИ, группу 51, 52, …, 5N из N элементов ИЛИ-НЕ, первую группу 61, 62, …, 6N, вторую группу 71, 72, …, 7N и третью группу 81, 82, …, 8N, каждая из которых содержит N элементов И, первый 91, второй 92 и третий 93 блоки счета единиц, а также первый 101, второй 102 и третий 103 элементы ИЛИ,

причем входная шина нижней границы GL соединена с входами дешифратора нижней границы 1, выходы которого, начиная с первого до (N-1)-го выхода, соединены с первыми входами соответствующих одноименных (N-1)-го элементов первой группы 31, 32, …, 3N-1 из (N-1) элементов ИЛИ, при этом вторые входы (N-2) элементов 31, 32, …, 3N-2 из первой группы элементов ИЛИ, начиная с первого до (N-2) элементов, соединены с выходами соответствующих последующих (N-2) элементов 32, 33, …, 3N-1 из первой группы элементов ИЛИ, начиная со второго до (N-1) элементов, а второй вход последнего (N-1)-го элемента 3N-1 из первой группы элементов ИЛИ соединен с последним N-м выходом дешифратора нижней границы 1,

кроме того выходы всех (N-1) элементов ИЛИ первой группы 31, 32, …, 3N-1 являются соответствующими одноименными (N-1) разрядами внутренней шины UL младших упорядоченных единиц, у которой старший N-й разряд соединен с N-м выходом дешифратора нижней границы 1,

причем входная шина верхней границы GM соединена с входами дешифратора верхней границы 2, выходы которого, начиная со второго до N-го выхода, соединены со вторыми входами соответствующих (N-1)-го элементов второй группы элементов 41, 42, … 4N-1 из (N-1) элементов ИЛИ, при этом первые входы (N-2) элементов 42, 43, …, 4N-1 из второй группы ИЛИ, начиная с второго до (N-1) элементов, соединены с выходами соответствующих предыдущих (N-2) элементов 41, 42, …, 4N-2 из второй группы элементов ИЛИ, начиная с первого до (N-2) элементов, а первый вход первого элемента 41 из второй группы элементов ИЛИ соединен с первым выходом дешифратора верхней границы 2,

кроме того выходы всех (N-1) элементов ИЛИ второй группы 41, 42, …, 4N-1 являются соответствующими (N-1) разрядами внутренней шины UM старших упорядоченных единиц, начиная со второго до N-го разряда, а младший первый разряд шины UM старших упорядоченных единиц соединен с первым выходом дешифратора верхней границы 2,

причем одноименные разряды внутренней шины UL младших упорядоченных единиц и внутренней шины UM старших упорядоченных единиц соединены соответственно с первыми и вторыми входами соответствующих одноименных элементов группы 51, 52, …, 5N из N элементов ИЛИ-НЕ, выходы которых являются

соответствующими одноименными N разрядами внутренней шины UC упорядоченных единиц внутри диапазона, которые соединены со вторыми входами соответствующих одноименных элементов второй группы 71, 72, …, 7N из N элементов И,

кроме того N разрядов внутренней шины UL младших упорядоченных единиц соединены со вторыми входами соответствующих одноименных элементов первой группы 61, 62, …, 6N из N элементов И, а N разрядов внутренней шины UM старших упорядоченных единиц соединены со вторыми входами соответствующих одноименных элементов третьей группы 81, 82, …, 8N из N элементов И,

причем первые входы одноименных элементов первой группы 61, 62, …, 6N, второй группы 71, 72, …, 7N и третьей группы 81, 82, …, 8N каждая из N элементов И соединены между собой, а также подключены к соответствующим одноименным N разрядам входной шины D,

кроме того выходы элементов первой группы 61, 62, …, 6N, второй группы 71, 72, …, 7N и третьей группы 81, 82, …, 8N, каждая из N элементов И, соединены соответственно с входами первого 91, второго 92 и третьего 93 блоков счета единиц, выходы которых подключены соответственно к первому 101, второму 102 и третьему 103 элементам ИЛИ,

причем выходы первого 91, второго 92 и третьего 93 блоков счета единиц являются соответствующими разрядами соответственно выходной шины QL количества единичных бит до нижней границы, выходной шины QC количества единичных бит внутри диапазона и выходной шины QM количества единичных бит выше верхней границы,

выходы первого 101, второго 102 и третьего 103 элементов ИЛИ являются соответственно флагом FL единичных бит до нижней границы, флагом FC единичных бит внутри диапазона и флагом FM единичных бит выше верхней границы.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

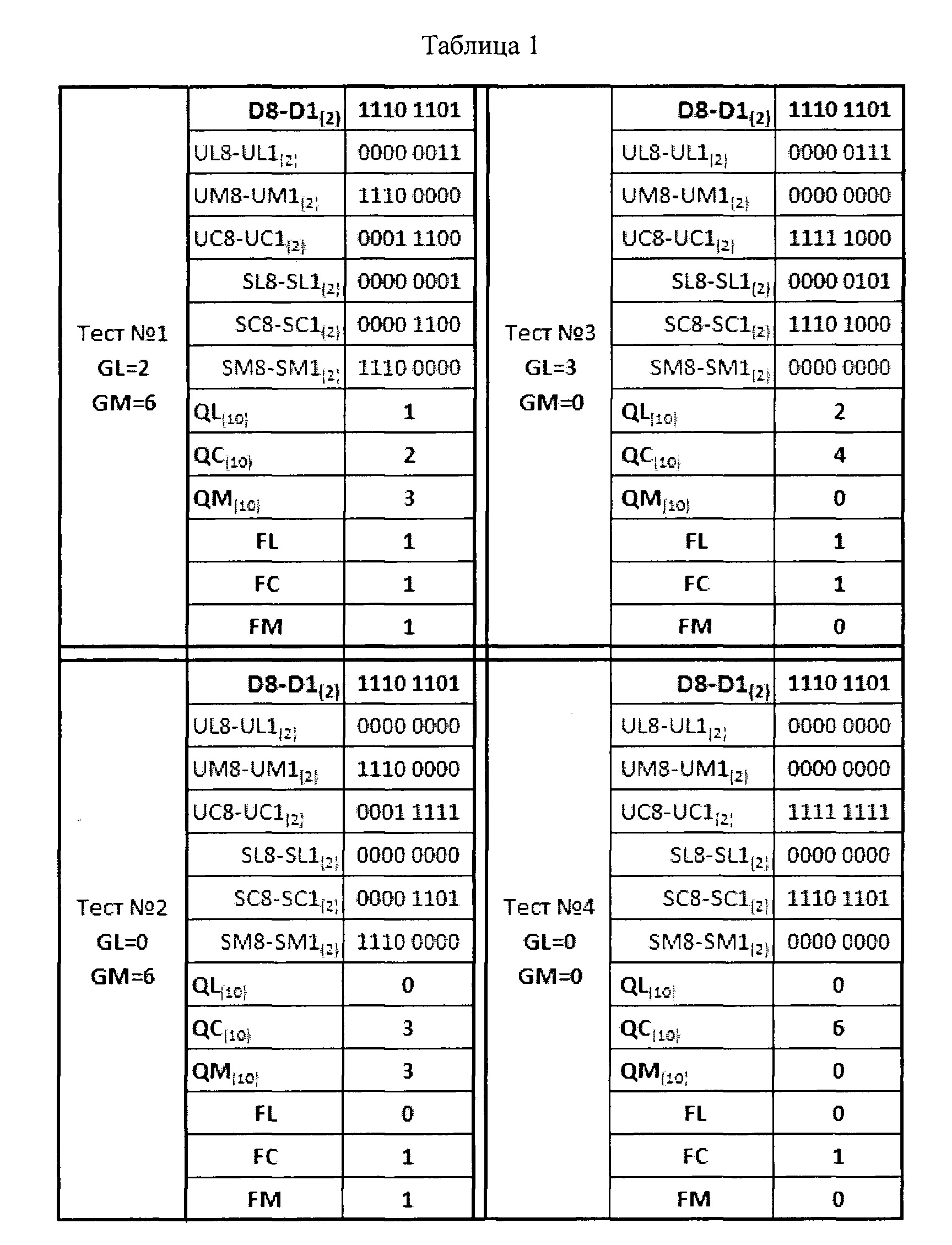

На фиг. 1 представлена функциональная схема предлагаемого двухпорогового компаратора диапазона двоичных бит. В таблице 1 приведены тестовые примеры при количестве разрядов входных данных N=8.

На фиг. 1, в таблице 1 и в тексте введены следующие обозначения:

D - N разрядная входная шина;

D1, D2, …, D8 (DN) - двоичные разряды входной шины (при N=8);

GL - М разрядный нижний порог (граница) диапазона,

где M=]log2 (N+1)[(большее целое);

GML - М разрядный верхний порог (граница) диапазона;

QL - М разрядная выходная шина количества единичных бит до нижней границы;

QM - М разрядная выходная шина количества единичных бит выше верхней границы;

QC - М разрядная выходная шина количества единичных бит внутри диапазона;

FL - флаг единичных бит до нижней границы;

FM - флаг единичных бит выше верхней границы;

FC - флаг единичных бит внутри диапазона;

UL - N разрядная внутренняя шина младших упорядоченных единиц;

UM - N разрядная внутренняя шина старших упорядоченных единиц;

UC - N разрядная внутренняя шина упорядоченных единиц внутри диапазона;

SL - N разрядная внутренняя шина единичных бит в младших разрядах;

SM - N разрядная внутренняя шина единичных бит в старших разрядах;

SC - N разрядная внутренняя шина единичных бит внутри диапазона;

1 - дешифратор нижней границы;

2 - дешифратор верхней границы;

31, 32, …, 3N-1 - первая группа из (N-1) элементов ИЛИ (OR);

41, 42, …, 4N-1 - вторая группа из (N-1) элементов ИЛИ (OR);

51, 52, …, 5N - группа из N элементов ИЛИ-НЕ (NOR);

61, 62, …, 6N - первая группа из N элементов И (AND);

71, 72, …, 7N - вторая группа из N элементов И (AND);

81, 82,…, 8N - первая группа из N элементов И (AND);

91, 92, 93 - первый, второй и третий блоки счета единиц;

101, 102, 103 - первый, второй и третий элементы ИЛИ (OR).

Предлагаемый двухпороговый компаратор диапазона двоичных бит содержит N разрядную входную шину D, входную шину нижнего порога (границы) GL и входную шину верхнего порога (границы) GM содержащие по М разрядов, где M=]log2(N+1)[(большее целое), выходную шину QL количества единичных бит до нижней границы, выходную шину QC количества единичных бит внутри диапазона и выходную шину QM количества единичных бит выше верхней границы, содержащие также по М разрядов, флаг FL единичных бит до нижней границы, флаг FC единичных бит внутри диапазона, флаг FM единичных бит выше верхней границы, а также внутреннюю шину UL младших упорядоченных единиц, внутреннюю шину UC упорядоченных единиц внутри диапазона, внутреннюю шину UM старших упорядоченных единиц, содержащие по М разрядов.

Кроме того двухпороговый компаратор диапазона двоичных бит содержит дешифратор нижней границы 1, дешифратор верхней границы 2, первую группу 31, 32, …, 3N-1 и вторую группу 41, 42, …, 4N-1, каждая из которых содержит (N-1) элементов ИЛИ, группу 51, 52, …, 5N из N элементов ИЛИ-НЕ, первую группу 61, 62, …, 6N, вторую группу 71, 72, …, 7N и третью группу 81, 82, …, 8N, каждая из которых содержит N элементов И, первый 91, второй 92 и третий 93 блоки счета единиц, а также первый 101, второй 102 и третий 103 элементы ИЛИ.

Причем входная шина нижней границы GL соединена с входами дешифратора нижней границы 1, выходы которого, начиная с первого до (N-1)-го выхода, соединены с первыми входами соответствующих одноименных (N-1)-го элементов первой группы 31, 32, …, 3N-1 из (N-1) элементов ИЛИ. При этом вторые входы (N-2) элементов 31, 32, …, 3N-2 из первой группы элементов ИЛИ, начиная с первого до (N-2) элементов, соединены с выходами соответствующих последующих (N-2) элементов 32, 33, …, 3N-1 из первой группы элементов ИЛИ, начиная со второго до (N-1) элементов. Второй вход последнего (N-1)-го элемента 3N-1 из первой группы элементов ИЛИ соединен с последним N-м выходом дешифратора нижней границы 1.

Кроме того выходы всех (N-1) элементов ИЛИ первой группы 31, 32, …, 3N-1 являются соответствующими одноименными (N-1) разрядами внутренней шины UL младших упорядоченных единиц, у которой старший N-й разряд соединен с N-м выходом дешифратора нижней границы 1.

Причем входная шина верхней границы GM соединена с входами дешифратора верхней границы 2, выходы которого, начиная со второго до N-го выхода, соединены со вторыми входами соответствующих (N-1)-го элементов второй группы элементов 41, 42, …, 4N-1 из (N-1) элементов ИЛИ. При этом первые входы (N-2) элементов 42, 43, …, 4N-1 из второй группы ИЛИ, начиная с второго до (N-1) элементов, соединены с выходами соответствующих предыдущих (N-2) элементов 41, 42, …, 4N-2 из второй группы элементов ИЛИ, начиная с первого до (N-2) элементов. Первый вход первого элемента 41 из второй группы элементов ИЛИ соединен с первым выходом дешифратора верхней границы 2.

Кроме того выходы всех (N-1) элементов ИЛИ второй группы 41, 42, …, 4N-1 являются соответствующими (N-1) разрядами внутренней шины UM старших упорядоченных единиц, начиная со второго до N-го разряда. Младший первый разряд шины UM старших упорядоченных единиц соединен с первым выходом дешифратора верхней границы 2.

Причем одноименные разряды внутренней шины UL младших упорядоченных единиц и внутренней шины UM старших упорядоченных единиц соединены соответственно с первыми и вторыми входами соответствующих одноименных элементов группы 51, 52, …, 5N из N элементов ИЛИ-НЕ, выходы которых являются

соответствующими одноименными N разрядами внутренней шины UC упорядоченных единиц внутри диапазона, которые соединены со вторыми входами соответствующих одноименных элементов второй группы 71, 72, …, 7N из N элементов.

Кроме того N разрядов внутренней шины UL младших упорядоченных единиц соединены со вторыми входами соответствующих одноименных элементов первой группы 61, 62, …, 6N из N элементов И. N разрядов внутренней шины UM старших упорядоченных единиц соединены со вторыми входами соответствующих одноименных элементов третьей группы 81, 82, …, 8N из N элементов И.

Причем первые входы одноименных элементов первой группы 61, 62, …, 6N, второй группы 71, 72, …, 7N и третьей группы 81, 82, …, 8N, каждая из которых содержит N элементов И соединены между собой, а также подключены к соответствующим одноименным N разрядам входной шины D.

Кроме того выходы элементов первой группы 61, 62, …, 6N, второй группы 71, 72, …, 7N и третьей группы 81, 82, …, 8N, каждая из которых содержит N элементов И, соединены соответственно с входами первого 91, второго 92 и третьего 93 блоков счета единиц, выходы которых подключены соответственно к первому 101, второму 102 и третьему 103 элементам ИЛИ.

Причем выходы первого 91, второго 92 и третьего 93 блоков счета единиц являются соответствующими разрядами соответственно выходной шины QL количества единичных бит до нижней границы, выходной шины QC количества единичных бит внутри диапазона и выходной шины QM количества единичных бит выше верхней границы.

Выходы первого 101, второго 102 и третьего 103 элементов ИЛИ являются соответственно флагом FL единичных бит до нижней границы, флагом FC единичных бит внутри диапазона и флагом FM единичных бит выше верхней границы.

ПОДРОБНОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Принцип работы предлагаемого устройства состоит в следующем.

Предлагаемое устройство позволяет детектировать единичные биты на входной шине данных D внутри и вне заданных границ диапазона. На выходах устройства формируются числа соответствующие количеству единичных разрядов внутри диапазона QC, а также количеству единичных разрядов до нижней границы (порога) QL и выше верхней границы QM. Одновременно устанавливаются флаги наличия единичных разрядов (событий) в соответствующих полях входной шины данных: флаг FC - внутри диапазона, флаг FL - до нижней границы диапазона, флаг FM - выше верхней границы диапазона.

На входы устройства поступают все N двоичных разрядов входной шины D - D1, D2, …, DN. Одновременно на входы дешифраторов границ 1 и 2 поступают соответствующие значения М-разрядных двоичных кодов (где M=]log2 (N+1)[(большее целое)) нижней границы (порога) GL и верхней границы (порога) QM заданного диапазона. При этом N двоичных разрядов входной шины D делятся на три группы (поля): младшая группа - младшие разряды с первого до GL-го разряда соответствуют разрядам до нижней границы (порога), средняя группа - разряды с (GL+1)-го до (GM-1)-го разряда соответствуют разрядам внутри диапазона между нижней и верхней границами, старшая группа - разряды с GM-го до N-го разряда соответствуют разрядам выше диапазона (выше верхней границы GM).

На выходах дешифраторов формируются унитарные коды «1 из N», при отсутствии нулевого выхода. Единичное значение с выхода дешифратора нижней границы 1, соответствующее нижней границе GL, передается на вход соответствующего элемента 3GL первой группы элементов ИЛИ 31, 32, …, 3(N-1), и далее последовательно передается по цепочке элементов ИЛИ в сторону младших разрядов и упорядоченная последовательность единичных значений (унитарный позиционный ряд) устанавливается на выходах соответствующих младших элементов первой группы ИЛИ, начиная с первого элемента до GL-го элемента. Единичное значение с выхода дешифратора верхней границы 2, соответствующее верхней границе GM, передается на вход соответствующего элемента 4(GL-1) второй группы элементов ИЛИ 41, 42, …, 4(N-1), и далее последовательно передается по цепочке элементов ИЛИ в сторону старших разрядов и упорядоченная последовательность единичных значений (унитарный позиционный ряд) устанавливается на выходах соответствующих старших элементов второй группы ИЛИ, начиная с (GM-1)-го элемента до (N-1)-го элемента. Далее значения с выходов первой группы элементов ИЛИ 31, 32, …, 3(N-1) поступают на внутреннюю шину UL младших упорядоченных единиц, а значения с выходов второй группы элементов ИЛИ 41, 42, …, 4(N-1) поступают на внутреннюю шину UM старших упорядоченных единиц.

Далее значения соответствующих разрядов с шин UL младших и UM старших упорядоченных единиц поступают соответственно на первые и вторые входы одноименных элементов группы из N элементов ИЛИ-НЕ 51, 52, …, 5N. При этом на двух входах группы элементов ИЛИ-НЕ, начиная с элемента 5(GL+1) до элемента 5(GM-1), устанавливаются нулевые значения и поэтому на выходах данных элементов будут установлены единичные значения, которые поступают на внутреннюю шину UC упорядоченных единиц внутри диапазона.

Далее значения с внутренних шин младших UL, внутри диапазона UC и старших UM упорядоченных единиц поступают на вторые входы одноименных элементов соответственно первой 61, 62, …, 6N, второй 71, 72, …, 7N и третьей 81, 82, …, 8N групп элементов И, в каждой из которых первые входы соединены с соответствующими одноименными разрядами входной шины D. На выходах элементов первой 61, 62, …, 6N, второй 71, 72, …, 7N и третьей 81, 82, …, 8N групп элементов И формируются единичные значения, соответствующие одноименным парам единичных значений с шин упорядоченных единиц и входных данных D, которые поступают на соответствующие внутренние шины единичных бит в младших разрядах SL, внутри диапазона SC и старших разрядов SM.

Далее значения с внутренних шин единичных бит в младших разрядах SL, внутри диапазона SC и старших разрядов SM поступают соответственно на входы первого 91, второго 92 и третьего 93 блоков счета единиц, на выходах которых формируются коды чисел соответствующие количеству единичных бит (событий) в полях входных данных, которые передаются на внешние выходные шины соответственно количества единичных бит (событий) до нижней границы QL, внутри диапазона QC и выше верхней границы QM.

Значения с выходов первого 91, второго 92 и третьего 93 блоков счета единиц также передаются на входы соответственно первого 101, второго 102 и третьего 103 элементов ИЛИ, на выходах которых формируются единичные значения при наличии событий в соответствующих полях входных данных D. Выходы первого 101, второго 102 и третьего 103 элементов ИЛИ являются соответствующими флагами единичных событий: до нижней границы FL, внутри диапазона FC и выше верхней границы FM.

Предлагаемое устройство работает следующим образом.

На входную шину шины D одновременно поступают N разрядов - D1, D2, …, DN. Значения с N разрядов входной шины D поступают на первые входы одноименных элементов первой 61, 62, …, 6N, второй 71, 72, …, 7N и третьей 81, 82, …, 8N групп элементов И. Одновременно на входы дешифраторов границ 1 и 2 поступают соответствующие значения М-разрядных двоичных кодов (где M=]log2 (N+1)[ (большее целое)) нижней границы (порога) GL и верхней границы (порога) GM заданного диапазона.

На выходах дешифраторов формируются унитарные коды «1 из N», при отсутствии нулевого выхода. В соответствии со значениями нижней GL и верхней GM границ (порогов) на выходах первой группы элементов ИЛИ 31, 32, …, 3(GL), второй группы элементов ИЛИ 4(GL+1), …, 4(GM-1) и третьей группы элементов ИЛИ 4(GM-1), …, 4(N-1) формируются соответствующие упорядоченные последовательности единичных значений (унитарные позиционные ряды), которые передаются на соответствующие внутренние шины младших UL, внутри диапазона UC и старших UM упорядоченных единиц.

Далее на выходы первой 61, 62, …, 6N, второй 71, 72, …, 7N и третьей 81, 82, …, 8N групп элементов И передаются соответствующие единичные значения с N разрядов входной шины D в соответствии с упорядоченными последовательностями единичных значений на соответствующих внутренних шинах младших UL, внутри диапазона UC и старших UM упорядоченных единиц. Далее первым 91, вторым 92 и третьим 93 блоками счета единиц осуществляется подсчет с соответствующих внутренних шин единичных бит (событий) в младших разрядах SL, внутри диапазона SC и старших разрядов SM. Значения с выходов первого 91, второго 92 и третьего 93 блоков счета единиц передаются на выходные шины количества единичных событий до нижней границы QL, внутри диапазона QC и выше верхней границы QM.

Одновременно формируются единичные значения флагов для полей (групп) до нижней границы FL, внутри диапазона FC и выше верхней границы FM при наличии единичных бит (событий) в соответствующих полях входных данных D или нулевые значения флагов при отсутствии соответствующих единичных бит (событий).

В таблице 1 приведены тестовые примеры счета единичных значений разрядов в полях (группах) входных данных D при количестве разрядов N=8, в соответствии с задаваемыми нижней GL и верхней GM границами (порогами) исследуемого диапазона и формирования соответствующих флагов до нижней границы FL, внутри диапазона FC и выше верхней границы FM. В таблице 1 в скобках указано представление значений в двоичном коде (2) или десятичном коде (10).

Во всех тестовых примерах на входную шину D поступает значение 1110 1101.

В тесте №1 задаются значения нижней GL=2 и верхней GM=6 границ диапазона. Поэтому формируются соответствующие последовательности единичных значений (унитарные позиционные ряды) на внутренних шинах младших UL=0000 ООП, внутри диапазона UC=0001 1100 и старших UM=1110 0000 упорядоченных единиц. Далее с входной шины D передаются значения на внутренние шины единичных бит (событий) в младших разрядах SL=0000 0001, внутри диапазона SC=0000 1100 и в старших разрядах SM=1110 0000, подсчет которых осуществляется соответственно в первом 91, втором 92 и третьем 93 блоках счета единиц и на выходных шинах формируются значения кодов количества единичных событий до нижней границы QL=1, внутри диапазона QC=2 и выше верхней границы QM=3, и так как единичные события присутствуют во всех полях (группах) входных данных D, то формируются соответствующие единичные значения флагов до нижней границы FL=1, внутри диапазона FC=1 и выше верхней границы FM=1.

В тесте №2 задаются нулевое значение GL=0 нижней границы и значение GM=6 верхней границы диапазона. Так как значение нижней границы равно нулю, то на внутренней шине UL младших упорядоченных единиц формируются все нулевые значения UL=0000 0000, и значения на внутренних шинах внутри диапазона UC=0001 1111 и старших им=1110 0000 упорядоченных единиц, по которым далее с входной шины D соответствующие значения бит передаются на внутренние шины единичных событий в младших разрядах SL=0000 0000, внутри диапазона SC=0000 1101 и старших разрядов SM=1110 0000, подсчет которых осуществляется соответственно в первом 91, втором 92 и третьем 93 блоках счета единиц и на выходных шинах формируются значения кодов количества единичных бит (событий) до нижней границы QL=0, внутри диапазона QC=3 и выше верхней границы QM=3, по которым формируются соответственно нулевое значение флага до нижней границы FL=0 и единичные значения флагов внутри диапазона FC=1 и выше верхней границы FM=1.

В тесте №3 задаются значение GL=3 нижней границы и нулевое значение GM=0 верхней границы диапазона. Так как значение верхней границы равно нулю, то на внутренней шине UM старших упорядоченных единиц формируются все нулевые значения UM=0000 0000, и значения на внутренних шинах младших UL=0000 0111 и внутри диапазона UC=1111 1000 упорядоченных единиц, по которым далее с входной шины D соответствующие значения передаются на внутренние шины единичных бит (событий) в младших разрядах SL=0000 0101 и внутри диапазона SC=1110 1000, и нулевые значения в старших разрядах SM=0000 0000, подсчет которых осуществляется соответственно в первом 91, втором 92 и третьем 93 блоках счета единиц и на выходных шинах формируются значения кодов количества единичных бит (событий) до нижней границы QL=2, внутри диапазона QC=4 и выше верхней границы QM=0, по которым формируются соответственно единичные значения флага до нижней границы FL=1 и флага внутри диапазона FC=1 и нулевое значение флага выше верхней границы FM=0.

В тесте №4 задаются нулевые значения GL=0 нижней границы и GM=0 верхней границы диапазона, т.е. все N разрядов входной шины D являются разрядами диапазона - отсутствуют младшая и старшая группы (поля). Поэтому нулевые значения формируются на внутренних шинах младших UL=0000 0000 и старших UM=0000 0000 разрядов и все единичные значения внутри диапазона UC=1111 1111 упорядоченных единиц. Далее с входной шины D выявленные единичные бит передаются только на внутреннюю шину единичных бит (событий) внутри диапазона SC=1110 1101 и нулевые значения устанавливаются на шинах единичных бит (событий) в младших разрядах SL=0000 0000 и в старших разрядах SM=0000 0000. Далее в результате подсчета соответственно в первом 91, втором 92 и третьем 93 блоках счета единиц на выходных шинах формируются значения кодов количества единичных бит (событий) до нижней границы QL=0, внутри диапазона QC=6 и выше верхней границы QM=0, по которым формируются соответственно единичное значение флага внутри диапазона FC=1 и нулевые значения флагов до нижней границы FL=0 и выше верхней границы FM=0.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство решает поставленную задачу и соответствует заявляемому техническому результату -детектирует единичные бит и определяет количество единичных бит в заданном диапазоне между внутренней и верхней границами, количество единичных бит вне диапазона и устанавливает соответствующие флаги.

Реферат

Изобретение относится к области вычислительной техники. Техническим результатом изобретения является обеспечение возможности определения количества единичных бит в заданном диапазоне между нижней и верхней границами и количества единичных бит вне диапазона. Раскрыт двухпороговый компаратор диапазона двоичных бит, содержащий N-разрядную входную шину D, входную шину нижнего порога (границы) GL и входную шину верхнего порога (границы) GM, содержащие по М разрядов, где M=]log2(N+1)[ (большее целое), выходную шину QL количества единичных бит до нижней границы, выходную шину QC количества единичных бит внутри диапазона и выходную шину QM количества единичных бит выше верхней границы, содержащие также по М разрядов, флаг FL единичных бит до нижней границы, флаг FC единичных бит внутри диапазона, флаг FM единичных бит выше верхней границы, а также внутреннюю шину UL младших упорядоченных единиц, внутреннюю шину UC упорядоченных единиц внутри диапазона, внутреннюю шину UM старших упорядоченных единиц, содержащие по М разрядов, дешифратор нижней границы 1, дешифратор верхней границы 2, первую группу 31, 32, …, 3N-1и вторую группу 41, 42, …, 4N-1, каждая из которых содержит (N-1) элементов ИЛИ, группу 51, 52, …, 5Nиз N элементов ИЛИ-НЕ, первую группу 61, 62, …, 6N, вторую группу 71, 72, …, 7Nи третью группу 81, 82, …, 8N, каждая из которых содержит N элементов И, первый 91, второй 92и третий 93блоки счета единиц, а также первый 101, второй 102и третий 103элементы ИЛИ. 1 ил., 1 табл.

Формула

Документы, цитированные в отчёте о поиске

Устройство для детектирования границ диапазона единичных бит

Устройство для детектирования диапазона единичных бит

Комментарии