Логический модуль для параллельной реализации пяти простых симметричных булевых функций от пяти аргументов - RU186743U1

Код документа: RU186743U1

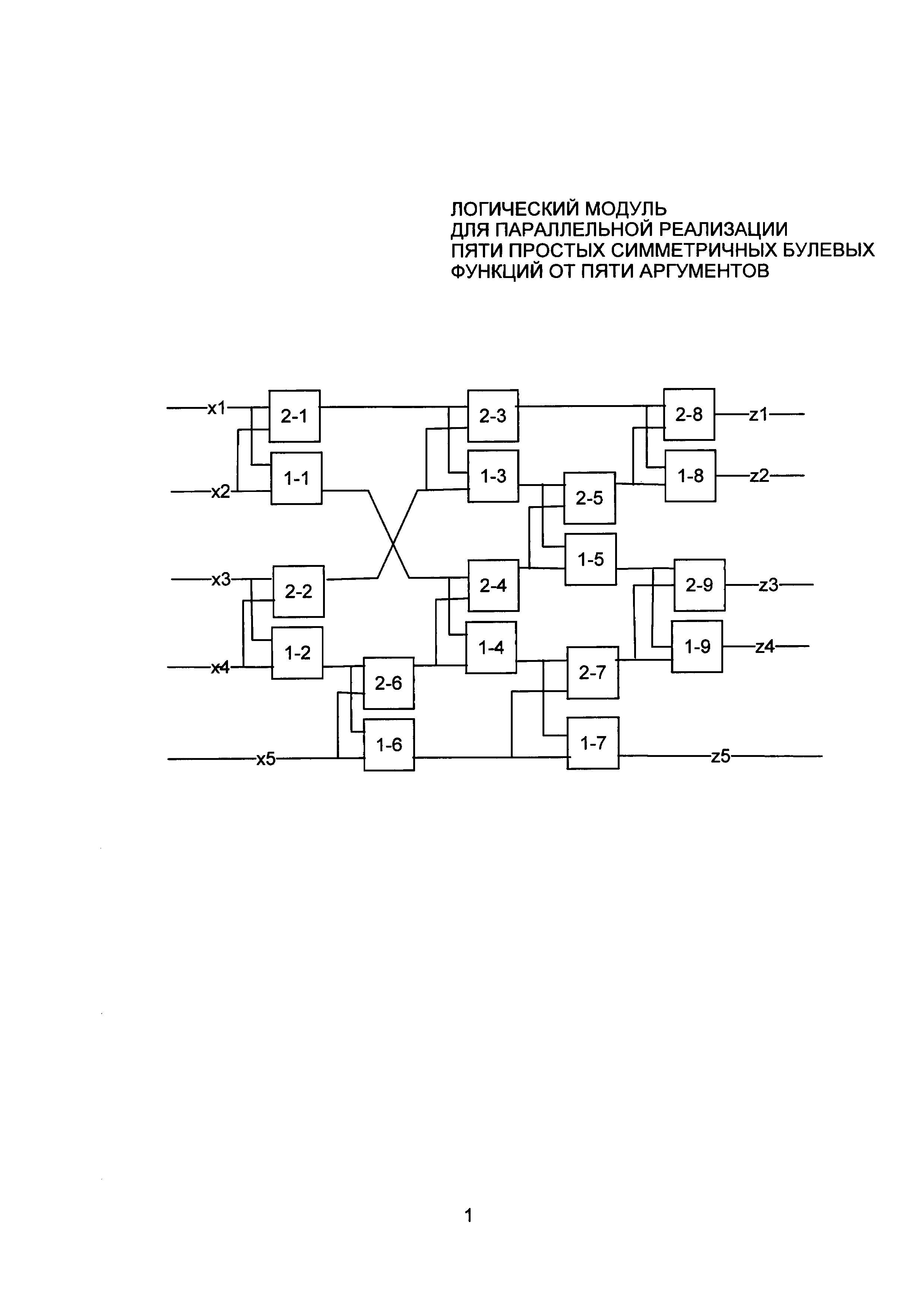

Чертежи

Описание

Предлагаемая полезная модель относится к вычислительной технике и может быть использована для построения средств автоматики, функциональных узлов систем управления и как средство преобразования кодов.

Известен логический модуль, который реализует любую из четырех простых симметричных булевых функций от четырех аргументов - входных двоичных сигналов (см. патент РФ 2286594, кл. G06F 7/57, 2006 г.). Для практики простые симметричные булевы функции интересны тем, что они являются собственными функциями мажоритарных логических элементов типа к из n, где к от 1 до n включительно (см. стр. 126 в книге Поспелов Д.А. Логические методы анализа и синтеза схем. М.: Энергия, 1974).

Известный логический модуль обладает ограниченными функциональными возможностями, обусловленными тем, что не выполняется реализация простых симметричных булевых функций от пяти аргументов.

Известен логический модуль (см. патент РФ 2621376, кл. G06F 7/57, 2017 г.), предназначенный для реализации любой из пяти простых симметричных булевых функций от пяти аргументов.

Известный логический модуль обладает тем недостатком, что в нем не выполняется параллельная реализация пяти простых симметричных булевых функций от пяти аргументов.

По совокупности сходных существенных признаков наиболее близким к предложенной полезной модели является логический модуль (см. патент РФ 2630394, кл. G06F 7/00, 2017 г.) для параллельной реализации пяти простых симметричных булевых функций от пяти аргументов, содержащий девять двухвходовых логических элементов И и девять двухвходовых логических элементов ИЛИ, в котором помимо прочих соединений все первые входы i-x логических элементов И (i от 1 до 9 включительно) соединены с первыми входами i-x логических элементов ИЛИ, а вторые входы i-x логических элементов И (i от 1 до 9 включительно) соединены со вторыми входами i-x логических элементов ИЛИ.

Недостатком известного логического модуля является то, что он не содержит возможного альтернативного (двойственного) способа соединения элементов модуля между собой, соответствующего одновременной замене в модуле всех элементов И на элементы ИЛИ и всех элементов ИЛИ на элементы И, который может быть более предпочтительным для практики, например, для реализации логического модуля в виде интегральной микросхемы.

Перед заявленной полезной моделью была поставлена задача реализации другого (альтернативного) способа соединений элементов логического модуля между собой при сохранении функциональных возможностей.

Поставленная задача решается тем, что предложен логический модуль для параллельной реализации пяти простых симметричных булевых функций от пяти аргументов - входных двоичных сигналов, содержащий девять двухвходовых логических элементов И и девять двухвходовых логических элементов ИЛИ, в котором все первые входы i-x логических элементов И (i от 1 до 9 включительно) соединены с первыми входами i-x логических элементов ИЛИ, а вторые входы i-x логических элементов И (i от 1 до 9 включительно) соединены со вторыми входами i-x логических элементов ИЛИ.

Новым в предложенном устройстве является то, что выходы первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого и девятого логических элементов И подключены соответственно к первому входу третьего, ко второму входу третьего, к первому входу восьмого, ко второму входу пятого, ко второму входу восьмого, ко второму входу четвертого, ко второму входу девятого логических элементов И, к первому выходу и к третьему выходу логического модуля, а выходы первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого и девятого логических элементов ИЛИ подключены соответственно к первому входу четвертого, первому входу шестого, первому входу пятого, первому входу седьмого, первому входу девятого, второму входу седьмого логических элементов И, к пятому, второму и четвертому выходам логического модуля, первый, второй, третий, четвертый и пятый входы которого подключены соответственно к первому входу первого, второму входу первого, первому входу второго, второму входу второго и второму входу шестого логических элементов И.

Технический результат заявленной полезной модели состоит в сохранении функциональных возможностей логического модуля при другом (альтернативном) способе соединения его элементов, который может оказаться более предпочтительным для практики.

На фигуре представлена функциональная блок-схема заявленного устройства.

Заявленное устройство содержит логические элементы ИЛИ 1-1, …, 1-9 и логические элементы И 2-1, …, 2-9, причем первый и второй входы элемента 1-m (m от 1 до 9 включительно) соединены соответственно с первым и вторым входами элемента 2-m. Первый, второй входы элемента 2-3 и первый вход элемента 2-4 подключены соответственно к выходам элементов 2-1, 2-2 и 1-1. Первые входы элементов 2-5, 2-6, 2-7, 2-9 и 2-8 соединены соответственно с выходами элементов 1-3, 1-2, 1-4, 1-5 и 2-3. Вторые входы элементов 2-4, 2-5, 2-8, 2-9 и 2-7 подключены соответственно к выходам элементов 2-6, 2-4, 2-5, 2-7 и 1-6, а первый, второй входы элемента 2-1, первый, второй входы элемента 2-2 и второй вход элемента 1-6 соединены соответственно с первым, вторым, третьим, четвертым и пятым информационными входами логического модуля, первый, второй, третий, четвертый и пятый выходы которого подключены соответственно к выходам элементов 2-8, 1-8, 2-9, 1-9 и 1-7.

Заявленное устройство работает следующим образом.

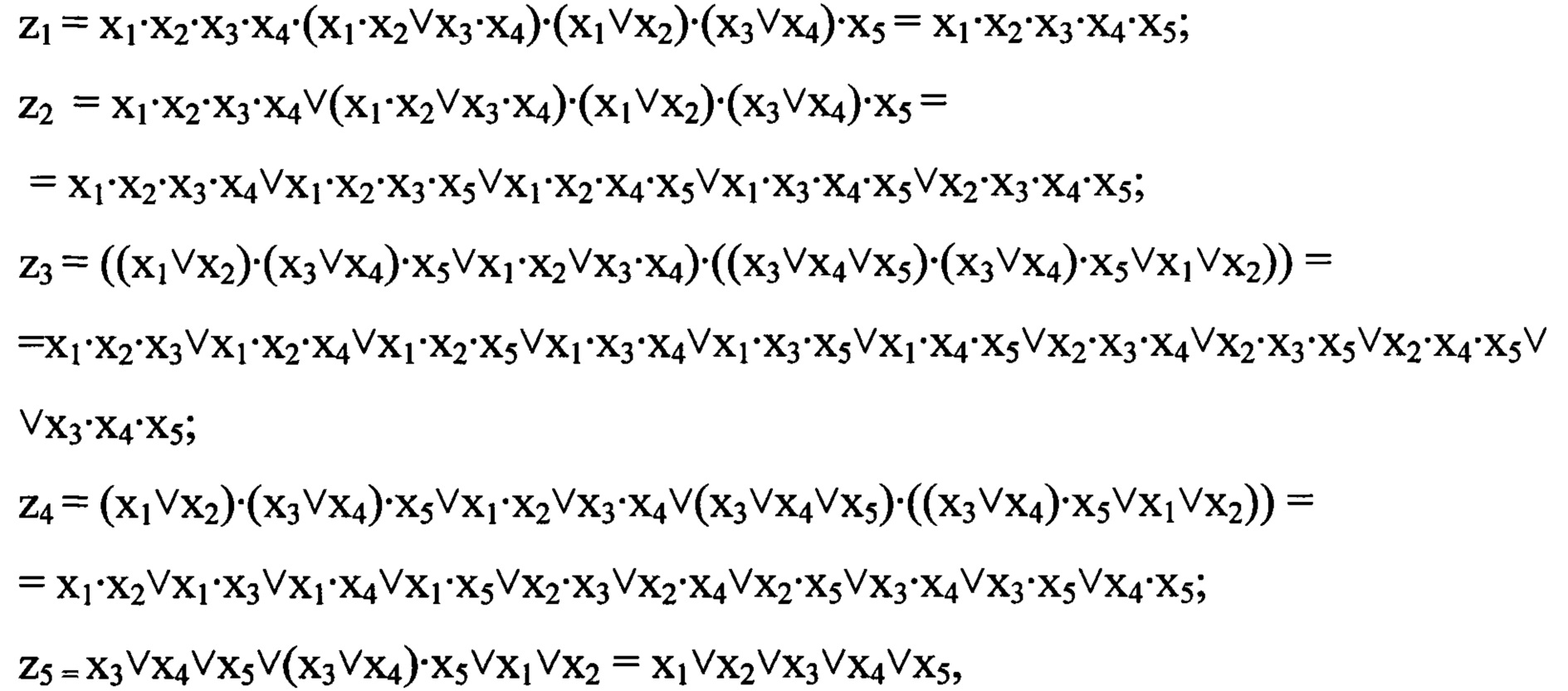

На его первый, …, пятый информационные входы подаются соответственно двоичные сигналы х1, …, х5. На выводах предлагаемого модуля получим:

где V, ⋅ - есть символы логических операций ИЛИ, И соответственно.

Таким образом, предлагаемый логический модуль имеет точно такие же функциональные возможности, что и прототип при том же составе элементов, но при другом способе их соединений, что позволяет сделать вывод о том, что он обладает всеми признаками полезной модели.

Реферат

Полезная модель предназначена для параллельной реализации пяти простых симметричных булевых функций, зависящих от пяти аргументов - входных двоичных сигналов, и может быть использована для построения средств автоматики и функциональных узлов систем управления, а также в системах цифровой вычислительной техники как средство преобразования кодов. Техническим результатом является сохранение всех функциональных возможностей устройства и состава его элементов при другом альтернативном способе их соединений. Логический модуль содержит девять элементов ИЛИ (1-1, …, 1-9) и девять элементов И (2-1, …, 2-9) и связи между ними. 1 ил.

Формула

Документы, цитированные в отчёте о поиске

Логический модуль

Комментарии