Арифметическое устройство - RU2625528C1

Код документа: RU2625528C1

Чертежи

Описание

Изобретение относится к цифровой вычислительной технике и может применяться в составе арифметических устройств цифровых вычислительных машин.

Известно арифметическое устройство, предназначенное для решения задач с большим числом тригонометрических функций, содержащее сдвиговые регистры, сумматоры-вычитатели и коммутирующие блоки, элемент И [А.с. СССР 547765, 1977 г.].

Недостатком устройства является отсутствие в его наборе команд, операции вычисления произведения двух двоичных чисел за одну операцию.

Наиболее близким по технической сущности к предлагаемому является арифметическое устройство [А.с. СССР 746508, 1980 г.], выполняющее в том числе и умножение двух двоичных чисел. Оно содержит три сдвиговых регистра, два коммутирующих блока, три сумматора-вычитателя и первый элемент И, причем разрядные выходы первого и второго сдвиговых регистров соединены с соответствующими входами соответственно первого и второго коммутирующих блоков, управляющие входы которых подключены к первому управляющему входу устройства, выходы младших разрядов каждого из сдвиговых регистров подключены к первым входам соответствующих сумматоров-вычитателей, выходы которых являются выходами устройства, и подключены к входам старших разрядов соответствующих сдвиговых регистров и ко второму, третьему и четвертому управляющим входам устройства, второй вход первого сумматора-вычитателя соединен с выходом первого элемента И, первый вход которого подключен к выходу второго коммутирующего блока, второй вход - к запрещающему входу устройства, управляющие входы первого и третьего сумматоров-вычитателей соединены с пятым управляющим входом, устройства, второй вход третьего сумматора-вычитателя подключен к первому разрешающему входу устройства, второй и третий элементы И, выходы которых подключены ко второму и третьему входам второго сумматора-вычитателя.

Однако точность работы такого арифметического устройства в режиме вычисления произведения низкая ввиду того, что в нем не производится оптимальное округление множимого после сдвига его вправо перед подсуммированием частичных сумм произведения.

Задачей настоящего изобретения является повышение точности функционирования арифметического устройства.

Технический результат предлагаемого изобретения - возможность получения более точного произведения двух двоичных чисел за одну операцию.

Технический результат достигается предложенным арифметическим устройством, которое содержит три сдвиговых регистра, два коммутирующих блока, три сумматора-вычитателя, первый, второй и третий элементы И, причем разрядные выходы первого и второго сдвиговых регистров соединены с соответствующими входами соответственно первого и второго коммутирующих блоков, управляющие входы которых подключены к первому управляющему входу устройства, выходы младших разрядов каждого из сдвиговых регистров подключены к первым входам соответствующих сумматоров-вычитателей, выходы которых являются выходами устройства, и подключены к входам старших разрядов соответствующих сдвиговых регистров и ко второму, третьему и четвертому управляющим входам устройства, второй вход первого сумматора-вычитателя соединен с выходом первого элемента И, второй вход - к запрещающему входу устройства, управляющие входы первого и третьего сумматоров-вычитателей соединены с пятым управляющим входом устройства, второй вход третьего сумматора-вычитателя подключен к первому разрешающему входу устройства, выходы второго и третьего элементов И подключены ко второму и третьему соответственно входам второго сумматора-вычитателя, при этом в арифметическое устройство дополнительно введены комбинационный сумматор, элемент временной задержки и логический элемент И, по входу соединенный с младшим разрядом первого сдвигового регистра и через элемент временной задержки с первым входом устройства, а по выходу - с младшим разрядом первого входа комбинационного сумматора, на остальные (n-1) разряды которого поданы логические "0", а на второй вход - код множимого от первого сдвигового регистра.

Введение комбинационного сумматора, элемента временной задержки и логического элемента И с их связями с другими блоками позволило провести оптимальное округление множимого после его очередного сдвига вправо перед подсуммированием частичных сумм произведения.

Предложенное устройство имеет изобретательский уровень, так как из опубликованных научных данных и существующих технических решений явным образом не следует, что заявляемая совокупность блоков, узлов и связей между ними позволяют повысить точность функционирования устройства при определении произведения двух чисел.

Предложенное арифметические устройство промышленно применимо, поскольку его техническая реализация возможна с использованием типовых элементов микроэлектронной техники (интегральных логических схем).

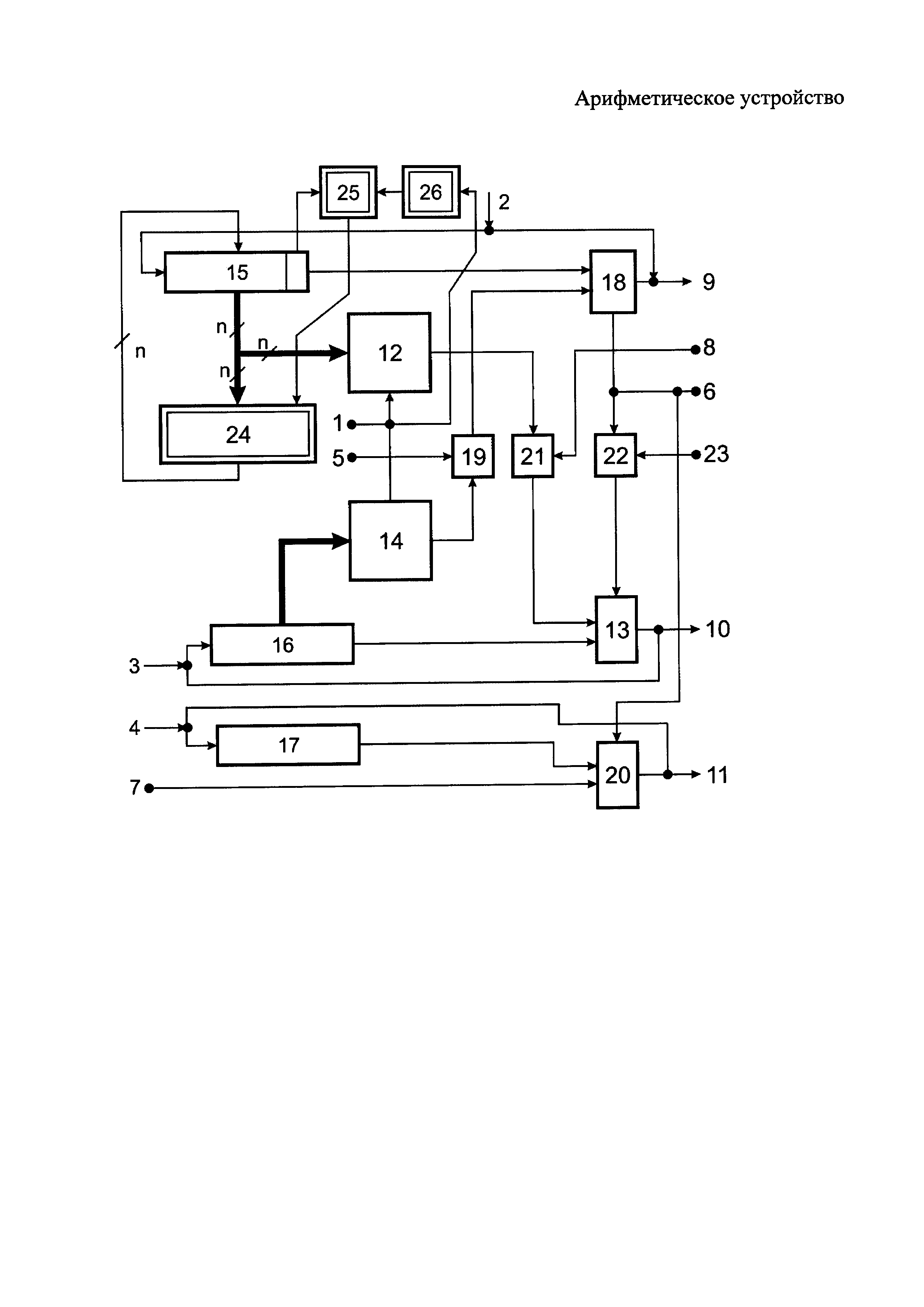

На фиг. показана структурная схема арифметического устройства. Устройство содержит входы 1, 2, 3, 4, 5, 6, 7 и 8, выходы устройства 9, 10 и 11, первый коммутирующий блок 12, второй сумматор-вычитатель 13, второй коммутирующий блок 14, первый сдвиговый регистр 15, второй сдвиговый регистр 16, третий сдвиговый регистр 17, первый сумматор-вычитатель 18, первый элемент 19 И, третий сумматор-вычитатель 20, второй элемент 21 И, третий элемент 22 И, запрещающий вход 23 устройства, кроме того, оно содержит комбинационный сумматор 24, логический элемент И 25 и элемент временной задержки 26.

В предлагаемое устройство при вычислении произведения на вход 1 поступают управляющие сигналы, по которым в коммутирующих блоках 12 и 14 осуществляются сдвиги вправо чисел, содержащихся в первом и втором сдвиговых регистрах 15 и 16, а на вход 5 подается сигнал запрета. Во внешнем блоке управления вход 6 устройства соединяется с входом устройства 8 и на оба эти входа подается управляющий оператор, получаемый на выходе устройства 11 и анализируемый во внешнем блоке управления. На вход 7 устройства подается из устройства управления сигнал запрета только на втором шаге вычисления.

В исходном состоянии множимое А содержится в первом сдвиговом регистре 15, множитель В - в третьем сдвиговом регистре 17, а второй сдвиговый регистр 16 находится в нулевом состоянии. В процессе вычисления во втором сдвиговом регистре 16 происходит накопление сдвинутых множимых и в конце вычисления содержится окончательный результат.

При подаче на вход 5 сигнала "Запрет" на второй вход первого сумматора-вычитателя 18 с выхода первого элемента 19 И поступает сигнал, равный нулю. Благодаря этому множимое А, поданное на вход 2, в процессе вычисления сохраняется в первом сдвиговом регистре 15 неизменным при установках первого 18 сумматора-вычитателя как на сложение, так и на вычитание. Управляющий оператор устанавливает второй сумматор-вычитатель 13 на противоположное действие по сравнению с первым 18 и третьим 20 сумматорами-вычитателями. Вычисление произведения Z=А⋅В выполняется за (n+1) шагов, где n - число разрядов в сдвиговых регистрах арифметического устройства.

На первом шаге проверяется знак множителя В. Из устройства управления на управляющие входы 6 и 8 поступает сигнал запрета. Этот сигнал закрывает второй и третий элементы 21 И и 22 И и устанавливает третий сумматор-вычитатель 20 на сложение. На второй вход второго сумматора-вычитателя 13 поступает "0", второй сдвиговый регистр 16 при выполнении первого шага продолжает сохранять нулевое состояние, значение сигнала на входе 7 устройства при выполнении первого шага безразлично.

На вход 7 устройства из блока памяти поступает константа 2n, которая суммируется третьим сумматором-вычитателем 20 с множителем В, находящимся в третьем сдвиговом регистре 17. На выходе 11 третьего сумматора-вычитателя 20 образуется сумма Bi=В+2°, которая вновь засылается в третий сдвиговый регистр 17. В зависимости от Bi≥0 или Bi<0 в устройстве управления определяется значение управляющего оператора ξi для второго шага

На втором шаге выполняется коррекция множителя В в зависимости от значения ξ1 {0,1}. Из блока управления на вход 7 поступает сигнал запрета, устанавливающий второй сумматор-вычитатель 13 на вычитание, а на входы 6 и 8 поступает управляющий оператор ξ1.

При ξ=0 (В<0) второй элемент 21 И закрыт, множимое А на второй вход второго сумматора-вычитателя 13 не поступает, и второй сдвиговый регистр 16 продолжает сохранять нулевое состояние. При ξ=1 (В≥0) второй элемент 21 И открыт, множимое без сдвига поступает на второй вход второго сумматора-вычитателя 13 и вычитается из нуля, содержащегося до этого во втором сдвиговом регистре 16.

Полученный дополнительный код множимого Адоп вновь поступает во второй сдвиговый регистр 16, определяя содержимое второго сдвигового регистра 16 после выполнения 2-го шага как 0-ξ1⋅А=ξ1⋅Aдоп.

Управляющее воздействие ξ1, поданное на вход 6, выполняет соответствующую установку сумматора-вычитателя 20

На вход 7 из блока памяти поступает число 2-1 и на выходе 11 третьего сумматора-вычитателя 20 образуется число В2=В1-signB1⋅2-1, которое вновь поступает в третий сдвиговый регистр 17. Знак этого числа при появлении его на выходе 11 анализируется в блоке управления и определяет управляющий оператор ξ2 для третьего шага.

Начиная с третьего шага в первом коммутирующем блоке 12 происходят сдвиги множимого вправо на каждом шаге на один разряд, во втором сдвиговом регистре 16 накапливается произведение, а на вход 7 из блока управления подается сигнал разрешения.

В результате выполнения 3-го шага в третьем сдвиговом регистре 17 имеет место сумма ξ1⋅Aдоп+ξ2⋅А⋅2-1.

Для определения управляющего воздействия следующего (четвертого) шага из блока памяти на вход 7 поступает число 2-2, на выходе третьего сумматора-вычитателя 20 образуется число В3=В2-signB2⋅2-2, которое снова записывается в третий сдвиговый регистр 17.

В каждом такте (итерации) на вход 1 поступают управляющие сигналы. Они поступают через элемент 26 временной задержки на вход логического элемента И 25, на второй вход которого приходит значение младшего разряда первого сдвигового регистра 15 (множимое А).

Далее происходят действия по оптимальному округлению множимого перед его сдвигом вправо: если его младший разряд равен 1, то посылается сигнал "1" на самый младший разряд комбинационного сумматора 24, на остальные разряды - "0". В то же время на второй вход комбинационного сумматора 24 подается множимое от первого сдвигового регистра 15. В результате этого его содержимое скорректируется перед сдвигом вправо на один разряд вправо, с учетом минимальной ошибки от потери младшего разряда. Округленное по правилам меньшей ошибки значение множимого используется при умножении двух чисел. Роль элемента временной задержки 26 заключается в устранении "гонок" в электронных цепях.

После выполнения (n+1) шагов, где n равно числу разрядов в сдвиговых регистрах арифметического устройства, во втором сдвиговом регистре 16 содержится произведение Z=А⋅В при изменении сомножителей и результата в пределах -1≤A<1; -1≤B<1; -1

В конце операции результат Zn может быть выведен по линии 11.

Эффективность изобретения заключается в повышении точности умножения двух двоичных чисел за одну операцию.

Реферат

Изобретение относится к цифровой вычислительной технике и может применяться в составе арифметических устройств цифровых вычислительных машин. Техническим результатом является повышение точности умножения. Устройство содержит три сдвиговых регистра, два коммутационных блока, три сумматора-вычитателя, три элемента И, комбинационный сумматор, логический элемент И, элемент временной задержки. 1 ил.

Комментарии