Накапливающий сумматор - RU2642366C1

Код документа: RU2642366C1

Чертежи

Описание

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах, а также в цифровых синтезаторах частот широкополосных систем связи.

Известен накапливающий сумматор, содержащий 2 сумматора и регистр (Пухальский Г.И., Новосельцева Т.Я. Проектирование дискретных устройств на интегральных микросхемах: Справочник. -M.: Радио и связь, 1990, рис. 4.80, с. 263).

Недостатком данного устройства является низкое быстродействие.

Наиболее близким по технической сущности и достигаемому результату к изобретению является накапливающий сумматор (Патент RU 2544748 по заявке 2014111953/08, 27.03.2014. Опубл. 20.03.2015. Бюл. №8). Устройство содержит три n-разрядных сумматора, 2n-разрядный регистр и (n+1)-разрядный двухвходовый мультиплексор.

Недостатком данного накапливающего сумматора является большой объем оборудования.

Техническим результатом изобретения является сокращение объема оборудования и, как следствие, уменьшение энергопотребления за счет исключения (n+1)-разрядного мультиплексора, одного n-разрядного сумматора и введения одного (n+1)-разрядного полусумматора.

Для достижения технического результата в накапливающий сумматор, содержащий первый и второй n-разрядные сумматоры и 2n-разрядный регистр, причем первые информационные входы первого n-разрядного сумматора соединены с k/2 младшими разрядами информационного входа устройства, где k=2n - разрядность входных чисел, информационные выходы первого n-разрядного сумматора соединены с младшими n информационными входами 2n-разрядного регистра, младшие n информационных выходов которого являются k/2 младшими разрядами выхода суммы устройства и соединены со вторыми информационными входами первого n-разрядного сумматора, вход переноса которого является первым входом переноса устройства, первые информационные входы второго n-разрядного сумматора соединены с k/2 старшими разрядами информационного входа устройства, тактовый вход 2n-разрядного регистра является тактовым входом устройства, вход обнуления 2n-разрядного регистра является входом обнуления устройства, старшие n информационных выходов являются k/2 старшими разрядами выхода суммы устройства и соединены со вторыми информационными входами второго n-разрядного сумматора, на вход переноса которого со второго входа переноса устройства подается сигнал логического нуля, введен (n+1)-разрядный полусумматор, второй информационный вход которого соединен с выходом переноса первого n-разрядного сумматора, младшие n первых информационных входов соединены с информационными выходами второго n-разрядного сумматора, (n+1)-й первый информационный вход соединен с выходом переноса второго n-разрядного сумматора, младшие n информационных выходов соединены со старшими n информационными входами 2n-разрядного регистра, (n+1)-й разряд является выходом переноса устройства.

Сущность изобретения заключается в реализации следующего способа накопительного суммирования чисел Ai, поступающих последовательно в параллельном коде с разрядностью k=2n на вход накапливающего сумматора. Младшие k/2 разрядов входного числа поступают на первый сумматор, одновременно старшие k/2 разрядов входного числа поступают на второй сумматор, который осуществляет суммирование с учетом входного сигнала переноса равного логическому нулю. В итоге результат суммирования для младших k/2 разрядов и для старших k/2 разрядов вычисляется одновременно, т.е. исключается необходимость начала процесса суммирования старших k/2 разрядов по окончании суммирования младших k/2 разрядов. Сигнал переноса по результатам суммирования младших k/2 разрядов суммируется с использованием (n+1)-разрядного полусумматора, с результатом суммирования старших k/2 разрядов во втором сумматоре. В итоге получают окончательное значение старших разрядов суммы, которое вместе с младшими разрядами записывается в 2n-разрядный регистр. Вторым слагаемым для первого сумматора являются младшие n разрядов числа, записанного в регистре, а для второго сумматора - старшие n разрядов.

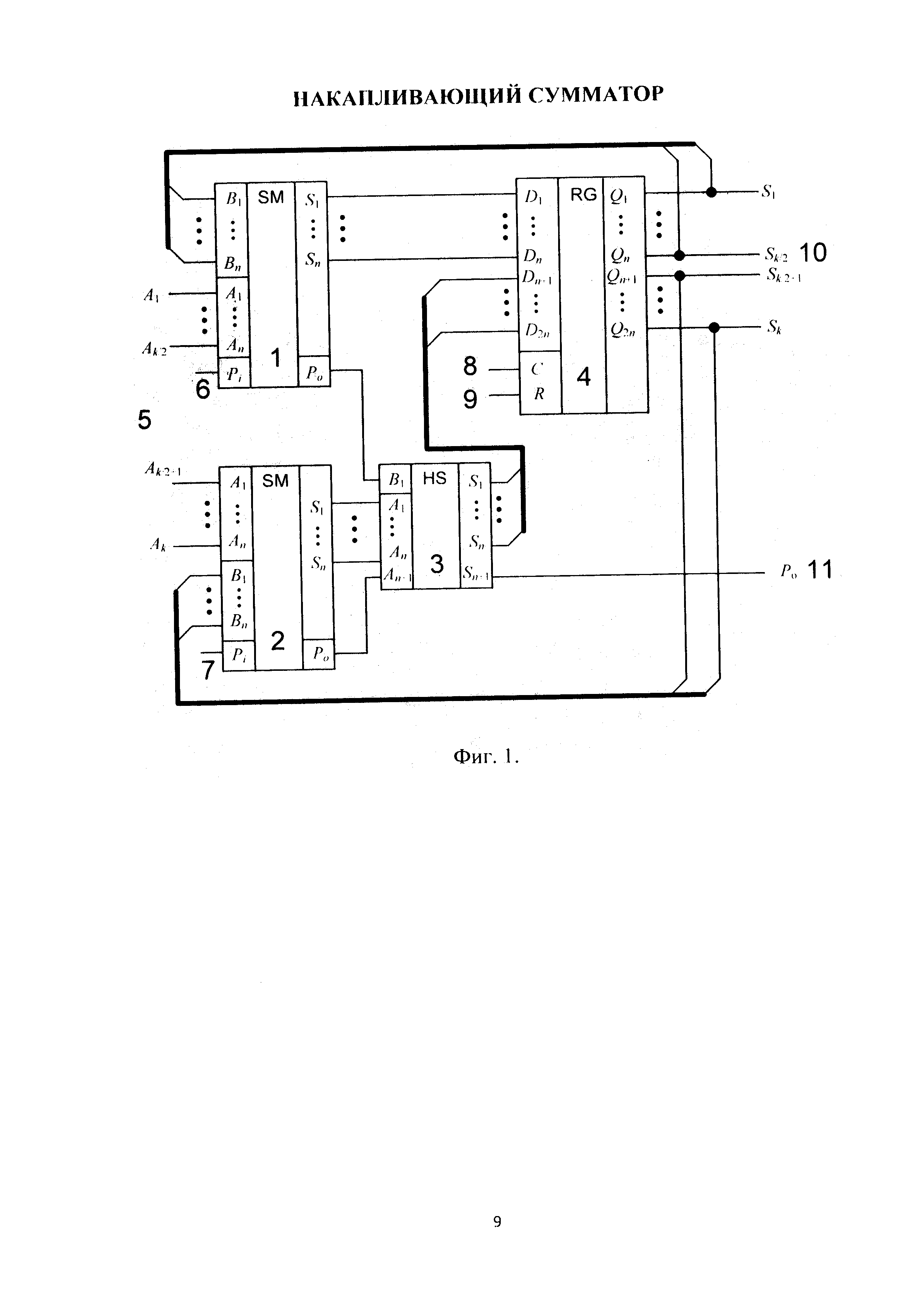

На фиг. 1 представлена схема накапливающего сумматора.

Накапливающий сумматор содержит первый и второй n-разрядные сумматоры 1 и 2, (n+1)-разрядный полусумматор 3 и 2n-разрядный регистр 4, информационный вход 5 устройства чисел Аi,разделенных на k/2 младших (А1…Аk/2) разрядов и k/2 старших (Аk/2+1…Аk) разрядов, где k=2n-разрядность входных чисел Ai, первый 6 и второй 7 входы переноса устройства, тактовый вход 8 устройства, вход 9 обнуления устройства, выход 10 суммы S устройства, разделенный на k/2 младших (S1…Sk/2) разрядов и k/2 старших (Sk/2+1…Sk) разрядов, выход 11 переноса устройства. Первые информационные входы первого n-разрядного сумматора 1 соединены с k/2 младшими разрядами информационного входа 5 устройства, информационные выходы первого n-разрядного сумматора 1 соединены с младшими n информационными входами 2n-разрядного регистра 4, младшие n информационных выходов которого являются k/2 младшими разрядами выхода 10 суммы устройства и соединены со вторыми информационными входами первого n-разрядного сумматора 1, вход переноса которого является первым входом 6 переноса устройства, первые информационные входы второго n-разрядного сумматора 2 соединены с k/2 старшими разрядами информационного входа 5 устройства, тактовый вход 2n-разрядного регистра является тактовым входом 8 устройства, вход обнуления 2n-разрядного регистра является входом 9 обнуления устройства, старшие n информационных выходов являются k/2 старшими разрядами выхода 10 суммы устройства и соединены со вторыми информационными входами второго n-разрядного сумматора 2, на вход переноса которого со второго входа 7 переноса устройства подается сигнал логического нуля. Второй информационный вход (n+1)-разрядного полусумматора 3 соединен с выходом переноса первого n-разрядного сумматора 1, младшие n первых информационных входов соединены с информационными выходами второго n-разрядного сумматора 2, (n+1)-й информационный вход соединен с выходом переноса второго n-разрядного сумматора 2, младшие n информационных выходов соединены со старшими n информационными входами 2n-разрядного регистра 4, (n+1)-й разряд является выходом 11 переноса устройства.

Накапливающий сумматор работает следующим образом.

Перед началом процедуры накапливающего суммирования на вход 9 обнуления устройства поступает сигнал, который обнуляет 2n-разрядный регистр 4. На информационный вход 5 устройства подаются последовательно в параллельном коде суммируемые k-разрядные числа Аi.

С информационного входа 5 устройства с младших k/2 разрядов (А1…Аk/2) код входного числа поступает на первые информационные входы (А1…Аn) первого n-разрядного сумматора 1, а со старших k/2 разрядов (Аk/2+1…Аk) - код входного числа поступает на первые информационные входы (А1…Аn) второго n-разрядного сумматора 2. На вход переноса второго n-разрядного сумматора 2 со второго входа 7 переноса устройства поступает сигнал логического нуля. На вторые информационные входы (В1…Вn) первого n-разрядного сумматора 1 поступает код числа с младших k/2=n разрядов (Q1…Qn) 2n-разрядного регистра 4. На вторые информационные входы (В1…Вn) второго n-разрядного сумматора 2 поступает код числа со старших k/2=n разрядов (Qn+1…Q2n) 2n-разрядного регистра 4. В итоге результат суммирования для младших k/2 разрядов и для старших k/2 разрядов, без учета сигнала переноса, вычисляется одновременно. Сигнал переноса по результатам суммирования младших k/2 разрядов с выхода переноса первого n-разрядного сумматора 1 поступает на второй информационный вход (n+1)-разрядного полусумматора 3, на младшие n первых информационных входов которого поступает результат суммирования старших k/2 разрядов с информационных выходов второго n-разрядного сумматора 2 и на (n+1)-й информационный вход поступает сигнал с выхода переноса второго n-разрядного сумматора 2. В результате чего на выходах (n+1)-разрядного полусумматора 3 формируется окончательное значение суммы старших k/2 разрядов и сигнал переноса. Тактовые импульсы, следующие синхронно с входными числами записывают результат суммирования в 2n-разрядный регистр 4. Результат накапливающего суммирования (S1…Sk) с выхода 2n-разрядного регистра 4 поступает на выход 10 суммы устройства, а на выход 11 переноса устройства поступает сигнал переноса Рo с (n+1)-го разряда (n+1)-разрядного полусумматора 3.

Рассмотрим работу накапливающего сумматора на конкретном примере. Пусть разрядность k входных чисел составляет 4 бита. В исходном состоянии 2n-разрядный регистр 4 обнулен. Пусть первое входное число А1=510=01012. Тогда младшие разряды Aмл=01, а старшие разряды Аст=01. Младшая часть входного числа Aмл=01 подается на первые информационные входы А1…Аn первого n-разрядного сумматора 1, а старшая часть входного числа Аст=01 подается на первые информационные входы А1…Аn второго n-разрядного сумматора 2. На вторые информационные входы В1…Вn первого n-разрядного сумматора 1 и на вторые информационные входы В1…Вn второго n-разрядного сумматора 2 на первом такте подаются нули с информационных выходов 2n-разрядного регистра 4. На информационных выходах первого n-разрядного сумматора 1 появится число 01, а на информационных выходах второго n-разрядного сумматора 2 появится число 01. На информационных выходах (n+1)-разрядного полусумматора 3 появится число 010. В результате на первом такте в 2n-разрядный регистр 4 будет записано число 0101.

Пусть второе входное число входное число А2=710=01112. Тогда на втором такте на информационном выходе первого n-разрядного сумматора 1 появится число 01+11=00, а на его выходе переноса образуется сигнал логической «1». На информационном выходе второго n-разрядного сумматора 2 появится число 01+01=10, а на его выходе переноса образуется сигнал логического «0». На информационном выходе (n+1)-разрядного полусумматора 3 появится число 1+010=011. В результате на втором такте в 2n-разрядный регистр 4 будет записано число 1100. На выход 11 переноса поступит сигнал логического «0». В результате в 2n-разрядном регистре 4 будет записано число 11002=1210, что является корректным, поскольку 5+7=12.

Оценим эффективность предлагаемого устройства по сравнению с прототипом.

Одноразрядный полусумматор содержит 4 элементарных логических элемента, одноразрядный полный сумматор состоит из двух полусумматоров и дополнительного логического элемента, т.е. содержит 9 элементарных логических элементов (рис. 3.52, с. 274 и рис. 3.53, с. 276, Безуглов Д.А. Цифровые устройства и микропроцессоры / Д.А. Безуглов, И.В. Калиенко. - Изд. 2-е. Ростов н/Д: Феникс, 2008. - 468 с.). Один мультиплексор содержит 3 элементарных логических элемента на один разряд и один логический элемент на всю схему (рис. 3.8 б, с. 104, Пухальский Г.И., Новосельцева Т.Я. Проектирование дискретных устройств на интегральных микросхемах: Справочник. - М.: Радио и связь. 1990. - 334 с.).

При построении предлагаемого накапливающего сумматора из устройства прототипа был исключен один n-разрядный сумматор, содержащий 9n элементарных логических элементов и один n+1-разрядный мультиплексор, содержащий 3(n+1)+1=3n+4 элементарных логических элементов. В тоже время, в предлагаемое устройство введен n+1-разрядный полусумматор, содержащий 4(n+1) элементарных логических элементов. Итого число элементарных логических элементов в предлагаемом устройстве по сравнению с устройством прототипом уменьшилось на 9n+(3n+4)-4(n+1)=8n элементарных логических элементов.

Реферат

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах, а также в цифровых синтезаторах частот широкополосных систем связи. Техническим результатом является сокращение объема оборудования и уменьшение энергопотребления. Устройство содержит два n-разрядных сумматора, (n+1)-разрядный полусумматор, 2n-разрядный регистр. 1 ил.

Комментарии