Процессоры, способы, системы и команды для сложения трех операндов-источников с плавающей запятой - RU2656730C2

Код документа: RU2656730C2

Чертежи

Описание

Область техники, к которой относится изобретение

Описанные в настоящем документе варианты осуществления изобретения, в общем, касаются процессоров. В частности, описанные в настоящем документе варианты осуществления изобретения, в общем, касаются процессоров для сложения чисел с плавающей запятой в ответ на команды.

Уровень техники

Числа с, плавающей запятой обычно используются в процессорах, вычислительных системах и других электронных устройствах. Преимущество чисел с плавающей запятой состоит в том, что они позволяют широкий диапазон числовых значений представлять в сравнительно компактном числовом формате и/или сравнительно компактным количеством битов. Биты чисел с плавающей запятой могут быть распределены на несколько составляющих полей, известных как знак, мантисса и показатель степени числа с плавающей запятой. Знак, мантисса, основание и показатель степени могут быть связаны следующим образом:

Выражение «(-1)знак» представляет минус единицу в степени, равной знаку. Это выражение вычисляет, является ли число с плавающей запятой положительным (+) или отрицательным (-). Например, когда знак является целым нулем, число с плавающей запятой является положительным, или, в качестве альтернативы, когда знак равен целой единице, число с плавающей запятой является отрицательным. Мантисса содержит строку цифр, длина которой во многом определяет точность числа с плавающей запятой. Мантиссу также иногда называют значащими цифрами, коэффициентом или дробной частью. Запятая (например, десятичная запятая для десятичного формата или двоичная запятая для двоичного формата) обычно неявно расположена в фиксированной позиции (например, непосредственно справа от самой левой или самой старшей цифры мантиссы, что в некоторых случаях может подразумеваться). Примером мантиссы в двоичном случае является «1.10010010000111111011011». Цифры мантиссы, расположенные слева от запятой (например, «10010010000111111011011»), могут представлять биты дробной части. Выражение «основаниепоказательстепени» представляет основание, возведенное в степень, равную показателю степени. Основание обычно является основанием, равным 2 (для двоичного случая), равным 10 (для десятичного случая) или равным 16 (для шестнадцатеричного случая). Основание иногда называют основанием степени. Показатель степени также иногда называют характеристикой или масштабом. Возведение основания в степень, равную показателю степени, фактически сдвигает запятую (например, от неявной или подразумеваемой начальной позиции) на количество позиций, равное показателю степени. Запятую сдвигают вправо, если показатель степени положителен, или влево, если показатель степени отрицателен.

Институт (IEEE) инженеров по электротехнике и электронике стандартизовал несколько различных форматов с плавающей запятой в стандарте IEEE 754. Типично, формат с плавающей запятой одинарной точности содержит 32 бита и содержит 23 бита мантиссы в битах [22:0], 8 битов показателя степени в битах [30:23] и один бит знака в бите [31]. Формат с плавающей запятой двойной точности содержит 64 бита и содержит 52 бита мантиссы в битах [51:0], 11 битов показателя степени в битах [62:52] и один бит знака в бите [63]. В технике также известны другие форматы с плавающей запятой, такие как, например, формат с плавающей запятой половинной точности, формат с плавающей запятой расширенной двойной точности и формат с плавающей запятой четверной точности. Дополнительные подробности о числах и форматах с плавающей запятой, при желании, доступны в IEEE 754.

Краткое описание чертежей

Изобретение будет лучше понятно из последующего описания и приложенных чертежей, используемых для иллюстрации вариантов осуществления изобретения. На чертежах:

Фиг. 1 - вид, показывающий структурную схему одного варианта осуществления процессора, выполненного для реализации варианта осуществления команды сложения трех источников с плавающей запятой;

фиг. 2 - вид, показывающий блок-схему одного варианта осуществления способа осуществления варианта осуществления команды сложения трех источников с плавающей запятой;

фиг. 3 - вид, показывающий схему одного варианта осуществления операции сложения трех упакованных, возможно маскированных, источников с плавающей запятой;

фиг. 4 - вид, показывающий схему одного варианта осуществления операции сложения трех скалярных, возможно маскированных, источников с плавающей запятой;

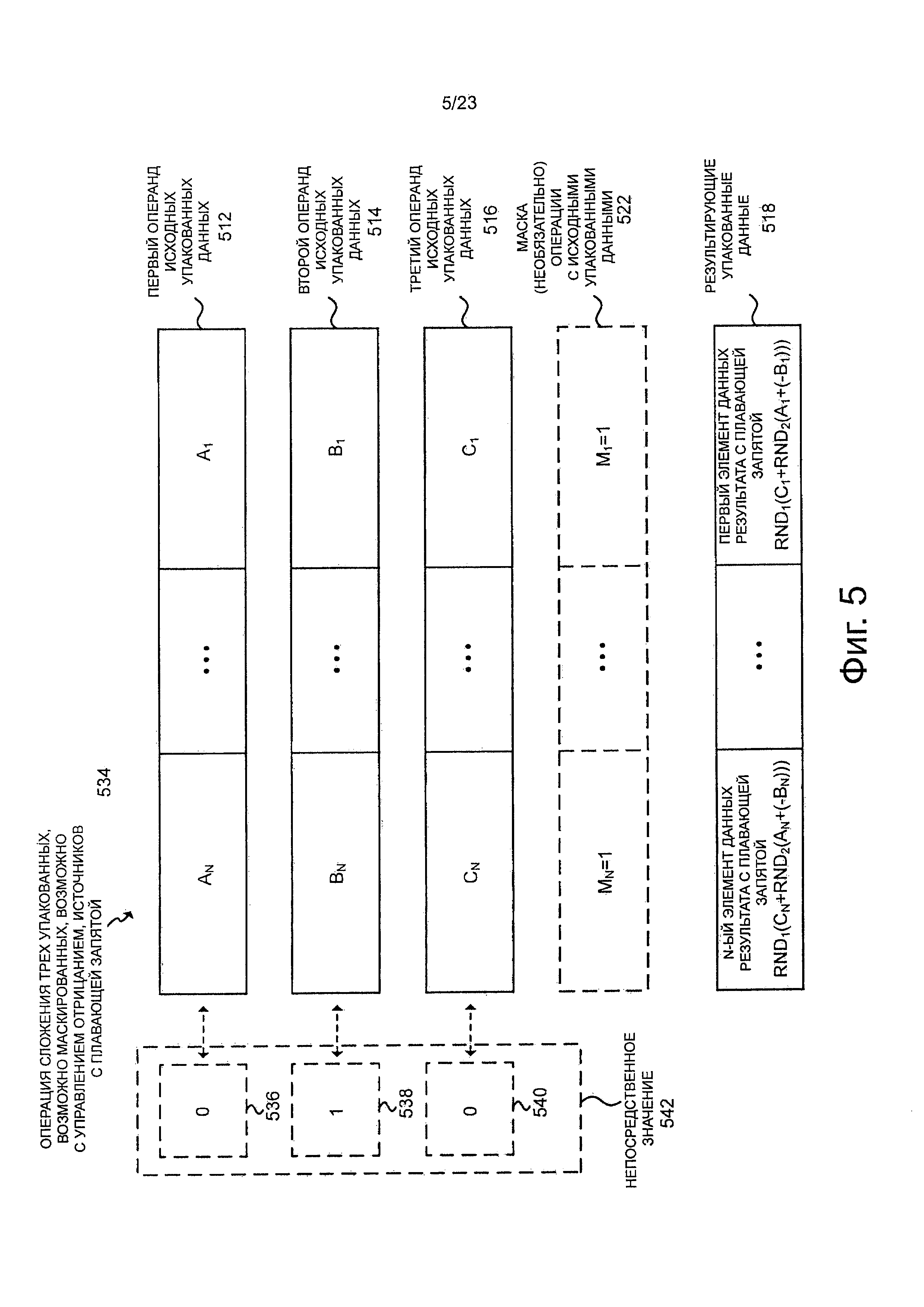

фиг. 5 - вид, показывающий схему одного варианта осуществления операции сложения трех упакованных, возможно маскированных, возможно с управлением отрицанием, источников с плавающей запятой;

фиг. 6 - вид, показывающий схему одного варианта осуществления операции сложения трех скалярных, возможно маскированных, возможно с управлением отрицанием, источников с плавающей запятой;

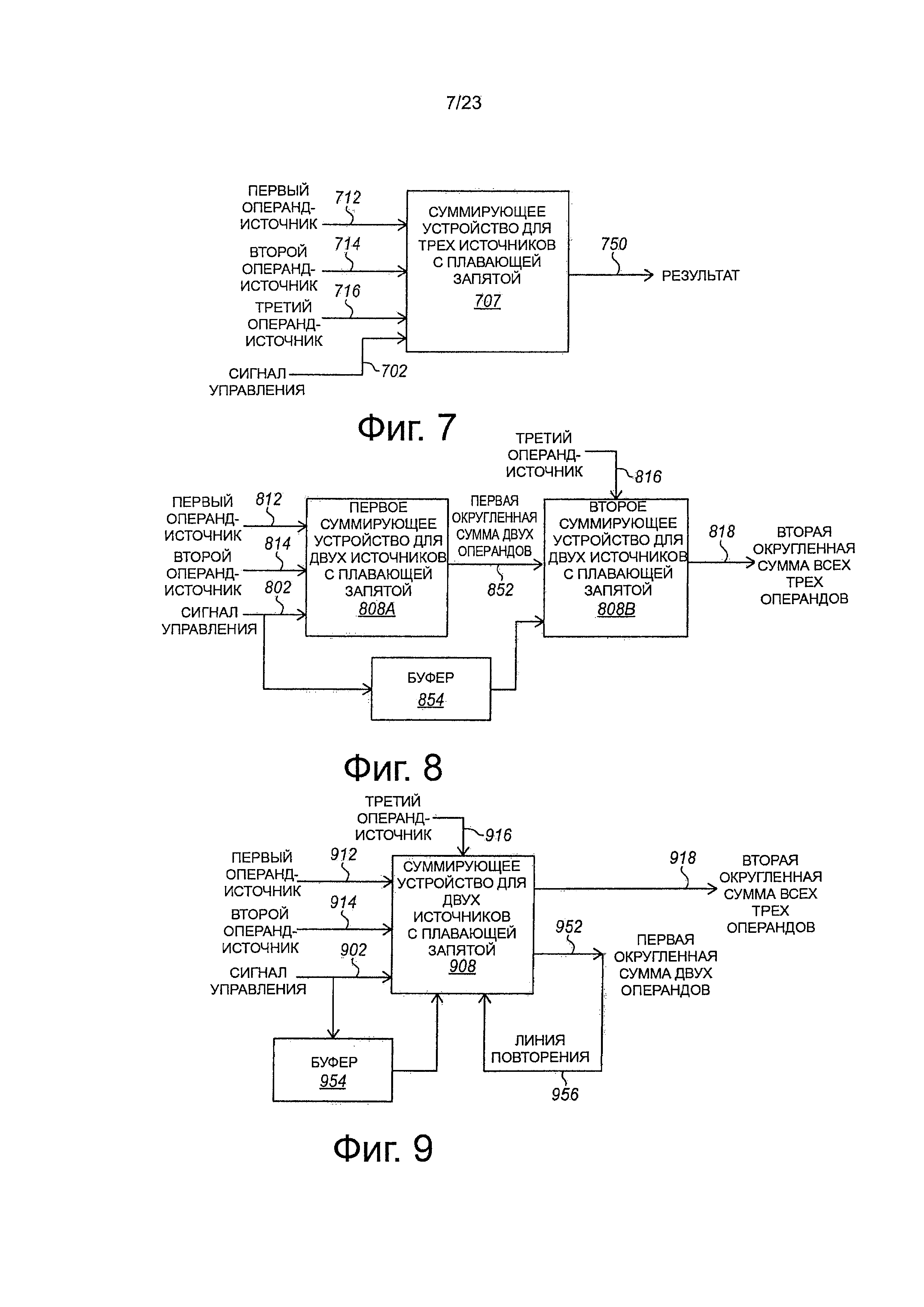

фиг. 7 - вид, показывающий схему одного варианта осуществления суммирующего устройства для трех источников с плавающей запятой;

фиг. 8 - вид, показывающий схему одного варианта осуществления двух последовательно связанных суммирующих устройств для двух источников с плавающей запятой;

фиг. 9 - вид, показывающий схему одного варианта осуществления суммирующего устройства для двух источников с плавающей запятой с линией повторения, которая связывает выход с входом;

фиг. 10 - вид, показывающий схему одного варианта осуществления подходящего формата команды для команды сложения трех источников с плавающей запятой;

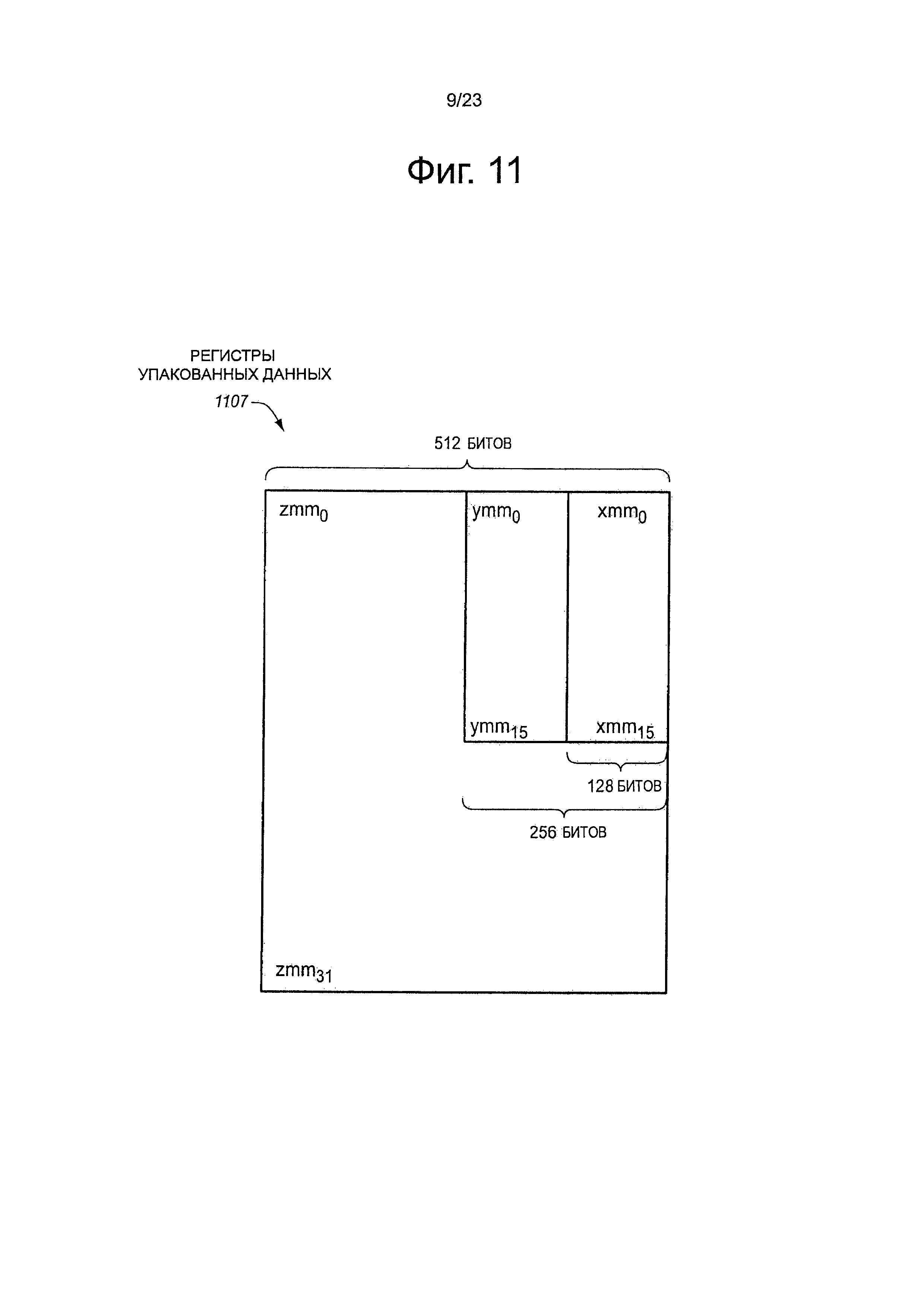

фиг. 11 - вид, показывающий схему одного варианта осуществления подходящего набора регистров упакованных данных;

фиг. 12 - вид, показывающий таблицу, иллюстрирующую то, что количество битов маски зависит от ширины упакованных данных и ширины элемента данных;

фиг. 13 - вид, показывающий схему одного варианта осуществления подходящего набора регистров масок операций;

фиг. 14А-14В - виды, показывающие схемы, иллюстрирующие общий формат векторно-ориентированных команд и его шаблоны команд, в соответствии с вариантами осуществления изобретения;

фиг. 15А - вид, показывающий схему одного примера конкретного формата векторно-ориентированных команд, в соответствии с вариантами осуществления изобретения;

фиг. 15В - вид, показывающий схему, иллюстрирующую поля одного конкретного формата векторно-ориентированных команд, которые составляют поле полного кода операции, в соответствии с одним вариантом осуществления изобретения;

фиг. 15С - вид, показывающий схему, иллюстрирующую поля одного конкретного формата векторно-ориентированных команд, которые составляют поле индекса регистра, в соответствии с одним вариантом осуществления изобретения;

фиг. 15D - вид, показывающий схему, иллюстрирующую поля одного конкретного формата векторно-ориентированных команд, который составляют поле операции приращения, в соответствии с одним вариантом осуществления изобретения;

фиг.16 - вид, показывающий схему одного варианта осуществления архитектуры регистров;

фиг. 17А - вид, показывающий структурную схему, иллюстрирующую вариант осуществления конвейера с исполнением команд по очереди и вариант осуществления конвейера с внеочередным исполнением/направлением команд, с переименованием регистров;

фиг. 17В - вид, показывающий структурную схему варианта осуществления ядра процессора, содержащего входной блок, связанный с блоком механизма исполнения, при этом входной блок и блок механизма исполнения связаны с блоком памяти;

фиг. 18А - вид, показывающий структурную схему варианта осуществления одного ядра процессора вместе с соединением с внутренней сетью на кристалле и с локальным подмножеством кэш-памяти уровня 2 (L2);

фиг. 18В - вид, показывающий увеличенную структурную схему варианта осуществления части ядра процессора с фиг. 18А;

фиг. 19 - вид, показывающий структурную схему варианта осуществления процессора, который может содержать более одного ядра, может содержать контроллер интегрированной памяти и может содержать интегрированную графику;

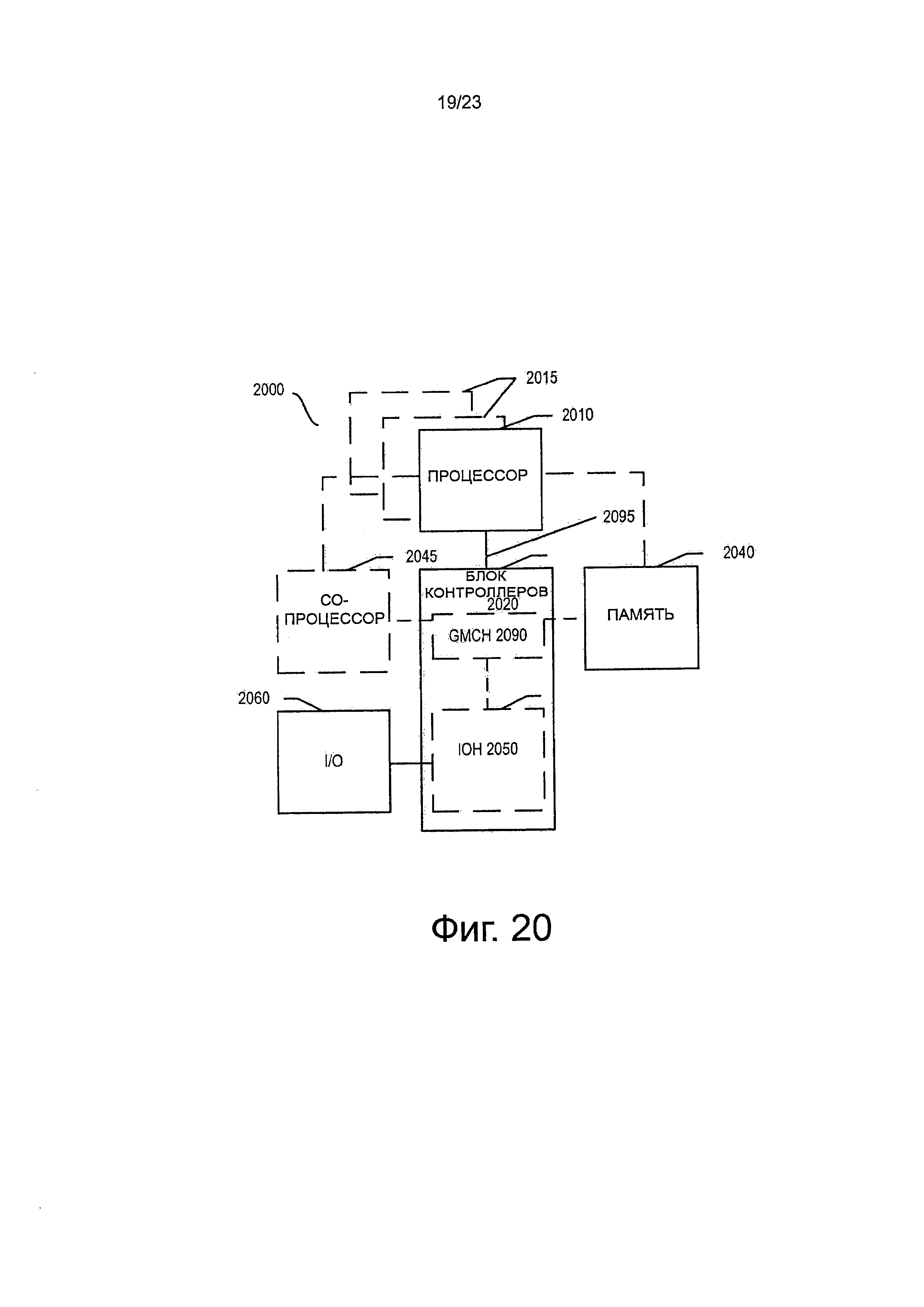

фиг. 20 вид, показывающий структурную схему первого варианта осуществления архитектуры компьютера;

фиг. 21 - вид, показывающий структурную схему второго варианта осуществления архитектуры компьютера;

фиг. 22 - вид, показывающий структурную схему третьего варианта осуществления архитектуры компьютера;

фиг. 23 - вид, показывающий структурную схему четвертого варианта осуществления архитектуры компьютера;

фиг. 24 вид, показывающий структурную схему использования программного устройства преобразования команд для преобразования двоичных команд исходного набора команд в двоичные команды целевого набора команд, в соответствии с вариантами осуществления изобретения.

Осуществление изобретения

В настоящем документе описаны команды сложения трех операндов-источников с плавающей запятой, процессоры для исполнения этих команд, способы, реализуемые процессорами при обработке или исполнении этих команд, и системы, содержащие один или несколько процессоров для обработки или исполнения этих команд. В последующем описании изложено большое количество конкретных подробностей (например, конкретные операции команд, форматы данных, конфигурации процессоров, подробности микроархитектуры, последовательности операций и так далее). Тем не менее, варианты осуществления изобретения могут быть реализованы без этих конкретных подробностей. В других примерах хорошо известные схемы, структуры и технологии не показаны подробно, чтобы не мешать пониманию описания.

На фиг. 1 показана структурная схема одного варианта осуществления процессора 100, выполненного для реализации варианта осуществления команды 102 сложения трех источников с плавающей запятой. В некоторых вариантах осуществления изобретения процессор может быть процессором общего назначения (например, такой тип процессора часто используют в настольных компьютерах, ноутбуках или других компьютерах). В. качестве альтернативы, процессор может быть процессором специального назначения. Примеры подходящих процессоров специального назначения содержат, помимо прочего, графические процессоры, сетевые процессоры, процессоры связи, криптографические процессоры, сопроцессоры, встроенные процессоры, цифровые сигнальные процессоры (DSP) и контроллеры (например, микроконтроллеры). Процессор может быть любым из различных процессоров (CISC) со сложным набором команд, различных процессоров (RISC) с сокращенным набором команд, различных процессоров (VLIW) с очень длинным командным словом, их различных гибридов или процессоров других типов.

Во время работы процессор 100 может принимать вариант осуществления команды 102 сложения трех источников с плавающей запятой. Например, команда сложения трех источников с плавающей запятой может быть принята от блока вызова команд, очереди команд или подобного. Команда сложения трех источников с плавающей запятой может представлять макрокоманду, команду языка ассемблера, команду машинного кода или команду или сигнал управления набора команд процессора. В некоторых вариантах осуществления изобретения команда сложения трех источников с плавающей запятой может прямо определять (например, с помощью одного или нескольких полей или наборов битов) или другим образом указывать (например, неявно указывать, благодаря соотнесению регистра с помощью карты эмуляции регистров и так далее) первый операнд-источник 112, который должен содержать, по меньшей мере, первый элемент данных с плавающей запятой, может определять или другим образом указывать второй операнд-источник 114, который должен содержать, по меньшей мере, второй элемент данных с плавающей запятой, может определять или другим образом указывать третий операнд-источник 116, который должен содержать, по меньшей мере, третий элемент данных с плавающей запятой, и может определять или другим образом указывать операнд-назначение (например, место хранения назначения), где должен храниться результат 118.

Обращаясь снова к фиг. 1, процессор содержит блок декодирования или декодер 104. Блок декодирования может принять и декодировать команду 102 сложения трех источников с плавающей запятой. Блок декодирования может подать на выход одну или несколько микрокоманд, микроопераций, точек входа микрокода, декодированных команд или сигналов управления, или другие сравнительно низкоуровневые команды или сигналы управления, которые отражают, представляют и/или получаются из команды сложения трех источников с плавающей запятой. Одна или несколько низкоуровневых команд или сигналов управления могут реализовывать высокоуровневую команду сложения трех источников с плавающей запятой с помощью одной или нескольких низкоуровневых (например, уровня схемы или уровня аппаратного обеспечения) операций. В некоторых вариантах осуществления изобретения блок декодирования содержит одну или несколько входных структур (например, порт (порты), соединение (соединения), интерфейс и так далее) для приема команды, логическую схему распознавания и декодирования команд, связанную с входными структурами для приема, распознавания и декодирования команды в одну или несколько соответствующих низкоуровневых команд или сигналов управления, и одну или несколько выходных структур (например, порт (порты), соединение (соединения), интерфейс и так далее), связанных с логической схемой распознавания и декодирования команд, для подачи на выход одной или нескольких соответствующих низкоуровневых команд или сигналов управления. Блок декодирования может быть реализован с использованием различных механизмов, в том числе, помимо прочего, постоянных запоминающих устройств (ROM) микрокода, таблиц соответствия, аппаратных реализаций, программируемых логических массивов (PLA) и других известных в технике механизмов.

В некоторых вариантах осуществления изобретения вместо прямого предоставления команды сложения трех источников с плавающей запятой в блок декодирования, при желании, может быть использован эмулятор, транслятор, устройство трансформирования, интерпретатор команд или другой модуль преобразования команд. В технике известны различные типы модулей преобразования команд, и они могут быть реализованы в форме аппаратного обеспечения, программного обеспечения, аппаратнореализованного программного обеспечения или их комбинации. В некоторых вариантах осуществления изобретения модуль преобразования команд может быть расположен снаружи процессора обработки команд, например, на отдельном кристалле и/или в памяти (например, статичный, динамичный модуль или модуль эмуляции команд времени выполнения). В качестве примера модуль преобразования команд может принимать команду сложения трех источников с плавающей запятой, которая может быть из первого набора команд, и может эмулировать, транслировать, трансформировать, интерпретировать или другим образом преобразовывать команду сложения трех источников с плавающей запятой в одну или несколько соответствующих, или полученных промежуточных команд или сигналов управления, которые могут быть из второго другого набора команд. Одна или несколько промежуточных команд или сигналов управления второго набора команд могут быть предоставлены на блок декодирования, который может декодировать принятые одну или несколько команд или сигналов управления второго набора команд в одну или несколько низкоуровневых команд или сигналов управления, которые могут быть исполнены естественным аппаратным обеспечением процессора (например, одним или несколькими блоками исполнения).

Процессор также содержит набор 110 регистров. Каждый из регистров может представлять собой место хранения на кристалле, которое выполнено для хранения данных с плавающей запятой. В качестве примера, регистры могут быть регистрами с плавающей запятой, выполненными с возможностью хранения элементов данных с плавающей запятой, регистрами упакованных данных, выполненными с возможностью хранения упакованных или скалярных элементов данных с плавающей запятой, или подобными. Регистры могут представлять архитектурные или архитектурно видимые регистры (например, файл архитектурных регистров), которые видимы программному обеспечению и/или программисту и/или могут являться регистрами, указанными командами набора команд процессора для идентификации операндов. Эти архитектурные регистры отличаются от других не архитектурных регистров или не архитектурно видимых регистров в заданной микроархитектуре (например, временные регистры, буферы переупорядочивания, регистров выгрузки и так далее). Регистры могут быть реализованы различным образом в различных микроархитектурах с использованием хорошо известных технологий, и они не ограничены каким-либо конкретным типом схемы. Примеры подходящих типов регистров содержат, помимо прочего, специальные физические регистры, динамически выделяемые физические регистры с использованием переименования регистров и комбинации перечисленного.

В некоторых вариантах осуществления изобретения первый операнд-источник 112 может, при желании, храниться в первом регистре набора, второй операнд-источник 114 может, при желании, храниться во втором регистре набора, третий операнд-источник 116 может, при желании, храниться в третьем регистре набора и операнд-назначение может, при желании, храниться в четвертом регистре набора. В некоторых случаях, регистр, используемый для операнда-назначения, может отличаться от регистров, используемых для первого, второго и третьего операндов-источников. В других случаях, регистр, используемый для одного из операндов-источников, может быть повторно использован для операнда-назначения (например, результат может быть записан поверх одного из операндов-источников). В качестве альтернативы, ячейки памяти или другие ячейки запоминающего устройства могут быть, при желании, использованы для одного или нескольких из указанных операндов.

Обращаясь снова к фиг. 1, блок 106 исполнения связан с блоком 104 декодирования и набором 110 регистров. В некоторых вариантах осуществления изобретения блок исполнения также может быть связан с необязательным регистром 120 маски операции с упакованными данными и/или необязательной маской 122 операции с упакованными данными, как будет дополнительно описано ниже, хотя этого не требуется. Блок исполнения может принимать одну или несколько декодированных, или другим образом преобразованных команд или сигналов управления, которые представляют команду сложения трех источников с плавающей запятой и/или которые получены из указанной команды. Блок исполнения также может принимать первый операнд-источник 112, содержащий, по меньшей мере, первый элемент данных с плавающей запятой, второй операнд-источник 114, содержащий, по меньшей мере, второй элемент данных с плавающей запятой, и третий операнд-источник 116, содержащий, по меньшей мере, третий элемент данных с плавающей запятой. Блок исполнения выполнен с возможностью, в ответ на команду сложения трех источников с плавающей запятой или в результате этой команды (например, в ответ на одну или несколько команд или сигналов управления, декодированных прямо или косвенно (например, с помощью эмуляции) из этой команды), сохранения результата 118 в операнде-назначении, указанном командой. В некоторых вариантах осуществления изобретения результат может содержать, по меньшей мере, результирующий элемент данных с плавающей запятой, который соответствует первому, второму и третьему элементам данных с плавающей запятой. В некоторых вариантах осуществления изобретения результирующий элемент данных с плавающей запятой может содержать, по меньшей мере, первую округленную сумму с плавающей запятой. Первая округленная сумма с плавающей запятой является числом с плавающей запятой, при этом осуществлено надлежащее округление с плавающей запятой. В некоторых вариантах осуществления изобретения первая округленная сумма с плавающей запятой может представлять собой алгебраическую сумму второй округленной суммы с плавающей запятой и третьего элемента данных с плавающей запятой. В некоторых вариантах осуществления изобретения вторая округленная сумма с плавающей запятой может представлять собой алгебраическую сумму первого элемента данных с плавающей запятой и второго элемента данных с плавающей запятой. В некоторых вариантах осуществления изобретения результат может быть любым из показанных и описанных результатов для фиг. 3-6, хотя объем изобретения этим не ограничен.

Для ясности, в настоящем документе термин «алгебраическая сумма» первого значения и второго значения используют для обозначения суммы, которая позволяет брать любое значение из первого и второго значений с обратным знаком. Например, алгебраическая сумма второй округленной суммы с плавающей запятой и третьего элемента данных с плавающей запятой может содержать сумму третьего элемента данных с плавающей запятой и второй округленной суммы с плавающей запятой или сумму второй округленной суммы с плавающей запятой и третьего элемента данных с плавающей запятой с обратным знаком (отрицание). Аналогично, алгебраическая сумма первого и второго элементов данных с плавающей запятой может содержать сумму первого элемента данных с плавающей запятой и второго элемента данных с плавающей запятой, сумму первого элемента данных с плавающей запятой и второго элемента данных с плавающей запятой с обратным знаком, сумму первого элемента данных с плавающей запятой с обратным знаком и второго элемента данных с плавающей запятой с обратным знаком и сумму первого элемента данных с плавающей запятой с обратным знаком и второго элемента данных с плавающей запятой. Как будет подробнее описано ниже, некоторые, но не все, варианты осуществления изобретения могут, при желании, позволять брать любой один, два или все элементы данных с обратным знаком до сложения, хотя этого не требуется (например, другой вариант осуществления изобретения не позволяет брать такое отрицание).

Предпочтительно, что команда сложения трех источников с плавающей запятой может осуществлять два сложения в рамках исполнения одной команды (например, макрокоманды, команды из набора команд и так далее). Обычно требуется две различные команды. Способность осуществлять оба сложения в одной команде может позволить получить определенные преимущества с точки зрения в производительности и/или энергопотребления. Во-первых, оба сложения могут быть осуществления при декодировании одной команды, вместо декодирования двух отдельных команд. Это может помочь увеличить производительность декодирования команды благодаря освобождению области декодирования для другой команды. Это также может помочь уменьшить величину потребления электроэнергии, так как для осуществления двух сложений декодируют на одну команду меньше. Улучшения производительности также могут быть достигнуты путем отказа от записи промежуточной суммы одного из двух сложений в архитектурный регистр и последующего считывания промежуточной суммы из архитектурного регистра с целью осуществления второго сложения. Такие записи и считывания из архитектурного регистра обычно подразумевают дополнительное время или ожидание (например, порядка нескольких тактовых циклов). Это также может помочь избежать связывания архитектурного регистра и помочь уменьшить количество операций переименования регистров. Исключение считываний, записей и операций переименования регистров также может помочь уменьшить потребление электроэнергии. Для определенных процессоров, уменьшение потребления электроэнергии может привести к увеличению производительности, так как определенные процессоры (например, это особенно относится к процессорам, используемым для высокопроизводительных вычислений) могут обладать производительностью, которая имеет тенденцию быть ограниченной доступными границами потребления электроэнергии. Соответственно, уменьшение потребления электроэнергии также может вести к увеличению производительности.

Округление с плавающей запятой может быть использовано тогда, когда точный результат операции с плавающей запятой (например, сложения с плавающей запятой) требует больше цифр, чем присутствует цифр в мантиссе. В некоторых вариантах осуществления изобретения результат может отражать две различные операции округления с плавающей запятой, вместо одной операции округления с плавающей запятой. Более конкретно, первая начальная операция округления с плавающей запятой может быть осуществлена для суммы, подразумевающей первый и второй элементы данных с плавающей запятой с целью выработки первой округленной суммы и далее вторая операция округления с плавающей запятой может быть осуществлена для суммы третьего элемента данных с плавающей запятой и первой округленной суммы. Как будет подробно объяснено ниже, эти две операции округления с плавающей запятой могут отражать микроархитектурную реализацию команды. Например, в некоторых вариантах осуществления изобретения микроархитектура, используемая для реализации команды, может использовать логическую схему, которая не способна одновременно сложить три значения с плавающей запятой. В качестве одного примера, как будет подробно описано ниже, два суммирующих устройства для чисел с плавающей запятой могут быть использованы последовательно и каждое может быть использовано для осуществления одновременного сложения только двух значений с плавающей запятой. Например, в первом суммирующем устройстве может быть получена сумма двух значений с плавающей запятой и далее для суммы может быть осуществлена первая операция округления с плавающей запятой, и далее во втором суммирующем устройстве может быть получена сумма третьего значения с плавающей запятой и округленной суммы, и далее для суммы, поданной на выход второго суммирующего устройства, может быть осуществлена вторая операция округления.

В качестве другого примера, как будет подробно описано ниже, может быть повторно использовано одно суммирующие устройство для чисел с плавающей запятой и во время каждого цикла или прохода суммирующего устройства может быть осуществлено одновременное сложение только двух значений с плавающей запятой. Например, в один проход может быть получена сумму двух значений с плавающей запятой, и далее для этой суммы может быть осуществлена первая операция округления с плавающей запятой, и далее во второй проход может быть получена сумма третьего значения с плавающей запятой и округленной суммы с первого прохода, и далее для суммы, поданной на выход суммирующего устройства во втором проходе, может быть осуществлена вторая операция округления. Как будет подробно описано ниже, преимущества такой микроархитектурной реализации состоят в том, что, например, исключается необходимость в специальной и/или, в общем, большой и сложной логической схеме для осуществления одновременного сложения трех значений с плавающей запятой. Результаты, включающиеся в себя две операции округления с плавающей запятой, могут немного отличаться от случая осуществления одной операции округления с плавающей запятой и это отражает такие микроархитектурные реализации.

В некоторых вариантах осуществления изобретения для обоих округлений может использоваться операция округления или режим округления одного типа. Различные типы операций округления или режимов округления подходят для различных вариантов осуществления изобретения. Примерами подходящих режимов округления являются, помимо прочего, следующие: (1) округление до ближайшего четного; (2) округление в меньшую сторону к отрицательной бесконечности; (3) округление в большую сторону к положительной бесконечности; и (4) округление в сторону нуля с отбрасыванием.

В некоторых вариантах осуществления изобретения команда сложения трех источников с плавающей запятой может поддерживать встроенное управление режимом округления, хотя этого не требуется. Обычно, управление режимом округления, в целом, определено в регистре состояния и управления плавающей запятой (например, MXCSR). Некоторые команды способны обеспечить переопределение округления для каждой команды с помощью полей кодирования в операнде с непосредственным значением. В некоторых вариантах осуществления изобретения управление переопределением режима округления для каждой команды может быть обеспечено с помощью кодирования команды и за рамками непосредственного значения. В качестве примера, в некоторых вариантах осуществления изобретения, управление режимом округления может быть встроено в префикс (например, EVEX префикс) как статичное управление или управление переопределением режима округления для каждой команды. Это может позволить программисту статично применять конкретный режим округления, который может переопределить режим округления в регистре состояния и управления плавающей запятой (например, MXCSR). В некоторых вариантах осуществления изобретения, при желании, может подразумеваться запрещение сообщения обо всех исключениях с плавающей запятой, когда такое управление режимом округления обеспечивают с помощью кодирования команды. Запрещение сообщения об всех исключениях с плавающей запятой может иметь место независимо от любых конкретных битов маски для запрещения или разрешения сообщения о соответствующих исключениях с плавающей запятой в регистре состояния и управления плавающей запятой (например, MXCSR). Запрещение сообщения об этих исключениях с плавающей запятой может означать, что биты или флаги в регистре состояния и управления плавающей запятой (например, MXCSR) могут не обновляться при появлении таких исключений с плавающей запятой (то есть, о них не сообщают).

Возвращаясь снова к фиг. 1, блок 106 исполнения и/или процессор 100 могут содержать конкретную или специфичную логическую схему (например, транзисторы, интегральные схемы или другое аппаратное обеспечение, потенциально объединенное с встроенными программами (например, команды, сохраненные в энергонезависимой памяти) и/или программным обеспечением), которые выполнены с возможностью реализации команды сложения трех источников с плавающей запятой и хранения результата в ответ на команду сложения трех источников с плавающей запятой и/или в результате команды сложения трех источников с плавающей запятой (например, в ответ на одну или несколько команд или сигналов управления, декодированных или другим образом полученных из команды сложения трех источников с плавающей запятой). Блок исполнения может содержать логическую схему 108 сложения с плавающей запятой. В качестве примера блок исполнения и/или логическая схема сложения с плавающей запятой содержат суммирующее устройство для чисел с плавающей запятой, объединенное устройство (FMA) сложения-умножения с плавающей запятой, блок арифметики с плавающей запятой, логический блок арифметики с плавающей запятой или подобные. В некоторых вариантах осуществления изобретения блок исполнения может содержать одну или несколько входных структур (например, порт (порты), соединение (соединения), интерфейс и так далее) для приема операндов-источников, логическую схему или схему сложения с плавающей запятой, связанную с входной структурой (структурами) для приема и обработки операндов-источников и выработки результата, и одну или несколько выходных структур (например, порт (порты), соединение (соединения), интерфейс и так далее), связанных с логической схемой или схемой сложения с плавающей запятой с целью подачи результата на выход. В некоторых вариантах осуществления изобретения блок исполнения может содержать схему или логическую схему, показанную и описанную на каких-либо фиг. из фиг. 7-9, на которых приведены. примеры подходящих микроархитектурных конструкций, хотя объем изобретения этим не ограничен.

Для ясности описания будет показан и описан сравнительно простой процессор 100. В других вариантах осуществления изобретения, при желании, процессор может содержать другие хорошо известные компоненты процессора. Возможные примеры таких компонентов включают в себя, помимо прочего, блок вызова команд, кэш-памяти данных и команд, кэш-памяти второго или более высоких уровней, логическую схему с внеочередным исполнением команд, блок планирования исполнения команд, блок переименования регистров, блок выгрузки, блок интерфейса шины, буферы предыстории преобразования данных и команд, буферы предварительного вызова, очереди микрокоманд, устройства, задающие последовательность микрокоманд, другие компоненты, содержащиеся в процессорах и их различные комбинации. Подходят большое количество разных комбинаций и конфигураций таких компонентов. Варианты осуществления изобретения не ограничены какой-либо известной комбинацией или конфигурацией. Более того, варианты осуществления изобретения могут содержаться в процессорах с несколькими ядрами, логических процессорах или устройствах исполнения, по меньшей мере, один из которых содержит блок декодирования и блок исполнения для реализации варианта осуществления команды сложения трех источников с плавающей запятой.

На фиг. 2 показана схема одного варианта способа 225 реализации варианта осуществления команды сложения трех источников с плавающей запятой. В различных вариантах осуществления изобретения способ может быть выполнен процессором, устройством обработки команд или другим цифровым логическим устройством. В некоторых вариантах осуществления изобретения операции и/или способ с фиг. 2 могут быть выполнены процессором и/или в процессоре с фиг. 1. Компоненты, признаки и конкретные необязательные подробности, описанные в настоящем документе для процессора с фиг. 1, также, при желании, применимы к операциям и/или способу с фиг. 2. В качестве альтернативы операции и/или способ с фиг. 2 могут быть выполнены аналогичным или другим процессором или устройством. Более того, процессор с фиг. 1 может выполнить операции и/или способ, аналогичные, похожие или отличные от операций и/или способа с фиг. 2.

Способ включает в себя в блоке 226 прием команды сложения трех источников с плавающей запятой. В различных аспектах изобретения, команда может быть принята в процессоре, устройстве обработки команд или его участке (например, блоке вызова команд, блоке декодирования, блоке интерфейса шины и так далее). В различных аспектах команда может быть принята от источника, расположенного не на кристалле (например, из памяти, соединения и так далее) или от источника на кристалле (например, из кэш-памяти команд, очереди команд и так далее). Команда сложения трех источников с плавающей запятой может определять или другим образом указывать первый операнд-источник, содержащий, по меньшей мере, первый элемент данных с плавающей запятой, определять или другим образом указывать второй операнд-источник, содержащий, по меньшей мере, второй элемент данных с плавающей запятой, и может определять или другим образом указывать третий операнд-источник, содержащий, по меньшей мере, третий элемент данных с плавающей запятой.

В блоке 227 результат сохраняют в операнде-назначении в ответ на команду сложения трех источников с плавающей запятой и/или в результате команды сложения трех источников с плавающей запятой. Операнд-назначение может быть определен или другим образом указан в команде сложения трех источников с плавающей запятой. Обычно, блок исполнения, устройство обработки команд или процессор могут выполнять команду и сохранять результат. Результат может содержать, по меньшей мере, результирующий элемент данных с плавающей запятой, который должен соответствовать первому, второму и третьему элементам данных с плавающей запятой. Результирующий элемент данных с плавающей запятой может содержать первую округленную сумму с плавающей запятой. В некоторых вариантах осуществления изобретения первая округленная сумма с плавающей запятой может представлять собой алгебраическую сумму второй округленной суммы с плавающей запятой и третьего элемента данных с плавающей запятой. В некоторых вариантах осуществления изобретения вторая округленная сумма с плавающей запятой может представлять собой алгебраическую сумму первого элемента данных с плавающей запятой и второго элемента данных с плавающей запятой. В некоторых вариантах осуществления изобретения результат может быть любым из показанных и описанных результатов для фиг. 3-6, хотя объем изобретения этим не ограничен.

Показанный способ включает в себя архитектурные операции (например, операции, видимые в программном обеспечении). В других вариантах осуществления изобретения, при желании, способ может включать в себя одну или несколько микроархитектурных операций. В качестве примера, команда может быть вызвана, декодирована, возможно может быть получен доступ к операндам-источникам, блок исполнения может выполнить микроархитектурные операции с целью реализации команды и так далее. В некоторых вариантах осуществления изобретения микроархитектурные операции для реализации команды могут, при желании, содержать любую операцию из показанных и описанных со ссылками на фиг. 3-6 или 7-9. Например, в некоторых вариантах осуществления изобретения вторая округленная сумма с плавающей запятой, при желании, может быть предоставлена из первого суммирующего устройства для чисел с плавающей запятой во второе суммирующее устройство для чисел с плавающей запятой. В качестве другого примера, в некоторых вариантах осуществления изобретения вторая округленная сумма с плавающей запятой, при желании, может быть повторно подана из выхода суммирующего устройства для чисел с плавающей запятой на вход суммирующего устройства для чисел с плавающей запятой.

На фиг. 3 показана схема одного варианта осуществления операции 330 сложения трех упакованных, возможно маскированных, источников с плавающей запятой, которая может быть выполнена в ответ на вариант осуществления команды сложения трех упакованных, возможно маскированных, источников с плавающей запятой. Команда может определять (например, явно определять) или другим образом указывать (например, неявно указывать) первый операнд 312 исходных упакованных данных, второй операнд 314 исходных упакованных данных, и третий операнд 316 исходных упакованных данных. Первый операнд исходных упакованных данных может содержать первое множество упакованных элементов данных с плавающей запятой A1-AN. Второй операнд исходных упакованных данных может содержать второе множество упакованных элементов данных с плавающей запятой B1-BN. Третий операнд исходных упакованных данных может содержать третье множество упакованных элементов данных с плавающей запятой C1-CN. Каждый элемент данных в первом операнде исходных упакованных данных может соответствовать другому элементу данных во втором операнде исходных упакованных данных и другому элементу данных в третьем операнде исходных упакованных данных, в соответствующей относительной позиции в операндах. Например, A1, B1 и C1 могут соответствовать друг другу, AN, BN и CN могут соответствовать друг другу и так далее.

Обычно количество элементов данных с плавающей запятой в каждом операнде исходных упакованных данных может быть равно размеру в битах операнда исходных упакованных данных, деленному на размер в битах каждого элемента данных с плавающей запятой. В различных вариантах осуществления изобретения ширина каждого операнда исходных упакованных данных может быть равна 64 битам, 128 битам, 256 битам, 512 битам или 1024 битам, хотя объем изобретения этим не ограничен. В различных вариантах осуществления изобретения каждый элемент данных с плавающей запятой может быть 16-битовым элементом данных с плавающей запятой половинной точности, 32-битовым элементом данных с плавающей запятой одинарной точности, 64-битовым элементом данных с плавающей запятой двойной точности, 80-битовым элементом данных двойного расширенного формата точности или 128 битовым элементом данных с плавающей запятой формата четверной точности. В некоторых вариантах осуществления изобретения 32 битовый формат одинарной точности или 64 битовый формат двойной точности могут поддерживаться благодаря их текущему широкому использованию. Также подходящими являются другие размеры операндов упакованных данных и варианты ширины элементов данных. В различных вариантах осуществления изобретения в каждом операнде исходных упакованных данных может присутствовать, по меньшей мере, два, по меньшей мере, четыре, по меньшей мере, восемь или более восьми элементов данных с плавающей запятой.

Обращаясь снова к фиг. 3, в некоторых вариантах осуществления изобретения команда, при желании, также может определять или другим образом указывать маску 322 операции с исходными упакованными данными, хотя этого не требуется. В настоящем документе маска операции с упакованными данными также называют просто маской операции, маской наложения логического условия или маской. Маска операции с исходными упакованными данными может содержать множество элементов маски M1-MN. Каждый элемент маски может соответствовать элементу исходных данных и/или элементу данных результата в соответствующей относительной позиции в операндах. Например, M1 может соответствовать A1, В1 и С1.

. Маска операции с исходными упакованными данными может представлять собой операнд маски, операнд наложения логического условия или операнд условного управления, который может быть использован для наложения логического условия, условного управления или маскирования того, должны ли выполняться соответствующие операции с упакованными данными и/или сохраняться соответствующие результаты. В некоторых вариантах осуществления изобретения маскирование или наложение логического условия может находиться на уровне элементов данных, так что операциями над различными множествами соответствующих троек элементов данных можно условно управлять или накладывать логические условия отдельно и/или независимо от других. Маска может содержать множество элементов маски, элементов наложения логического условия или элементов условного управления. В одном аспекте, элементы маски могут состоять во взаимно однозначном соответствии с соответствующими наборами троек элементов исходных данных и/или соответствующих элементов данных результата. Как показано, в некоторых вариантах осуществления изобретения каждый элемент маски может быть одним битом маски. В таких случаях маска может содержать бит для каждого элемента данных в первом операнде исходных упакованных данных и/или каждого элемента данных результата в результирующих упакованных данных 318. Значение каждого бита маски может управлять, выполняют ли соответствующую операцию с упакованными данными и сохраняют ли соответствующий элемент данных результата. Каждый бит маски может обладать первым значением для предоставления возможности выполнять операцию для соответствующего набора из трех элементов исходных данных и предоставления возможности сохранять соответствующий элемент данных результата в результирующих упакованных данных или может обладать вторым, другим, значением, чтобы не позволять выполнять эту операцию для соответствующего набора из трех элементов исходных данных и/или не позволять сохранять соответствующий элемент данных результата в результирующих упакованных данных. В соответствии с одной возможной договоренностью, как показано на иллюстрации, бит маски, установленный равным двоичному нулю (то есть, 0) может представлять операцию замаскирования, когда в соответствующем элементе данных результата сохраняют замаскированное значение вместо результата операции. В отличие от этого, бит маски, установленный равным двоичной единице (то есть, 1) может представлять операцию без маскирования, когда в соответствующем элементе данных результата сохраняют результат операции. В других вариантах осуществления изобретения могут быть использованы противоположные договоренности, или два или несколько битов могут быть, при желании, использованы для каждого элемента маски (например, каждый элемент маски может обладать количеством битов, одинаковым с соответствующим элементом исходных данных, и для наложения логического условия могут быть использованы один или несколько самых старших или самых младших битов).

Вариант осуществления операции 330 может быть выполнен в ответ на один вариант осуществления команды и/или в результате одного варианта осуществления команды. В вариантах осуществления изобретения, когда, при желании, использована маска 322 операции с упакованными данными, операция может быть выполнена в зависимости от маскирования, наложения логического условия или условного управления со стороны необязательной маски операции с исходными упакованными данными. Результирующие упакованные данные 318 могут быть выработаны (например, в блоке исполнения) и сохранены в целевую ячейку памяти в ответ на команду. Целевая ячейка памяти может быть определена, или другим образом указана, в команде. В различных вариантах осуществления изобретения целевая ячейка памяти может быть регистром упакованных данных, ячейкой запоминающего устройства или другой ячейкой памяти. Результирующие упакованные данные могут содержать множество элементов данных, каждый из которых соответствует другому набору из трех элементов исходных данных и другому соответствующему элементу маски.

В вариантах осуществления изобретения, где используют необязательную маску операции с упакованными данными, элементы данных результата, соответствующие немаскирующим элементам маски, могут обладать значениями, которые зависят от операции, выполненной с соответствующим набором трех исходных элементов данных с плавающей запятой. В показанном примере, самый правый элемент данных результата соответствует операции без маскирования и сохраняет значение, которое зависит от соответствующей операции с упакованными данными, выполняемой с соответствующими тремя исходными элементами данных с плавающей запятой из первого, второго и третьего операндов исходных упакованных данных. Более конкретно, в некоторых вариантах осуществления изобретения, самый правый элемент результата с плавающей запятой может сохранять первую округленную сумму с плавающей запятой (например, RND1(C1+RND2(A1+В1)). Первая округленная сумма с плавающей запятой может представлять собой алгебраическую сумму второй округленной суммы с плавающей запятой (например, RND2(A1+B1)) и третьего элемента данных с плавающей запятой (например, C1). Вторая округленная сумма с плавающей запятой (например, RND2(A1+B1)) может представлять собой алгебраическую сумму первого элемента данных с плавающей запятой (например, A1) и второго элемента данных с плавающей запятой (например, B1). Алгебраические суммы позволяют потенциально или, при желании, брать элементы исходных данных (например, один или несколько из А1, В1, и/или C1) с обратным знаком. В этом примере, RND1 и RND2 используют для обозначения двух отдельных, используемых последовательно операций округления с плавающей запятой (например, RND2 выполняют до RND1).

В отличие от этого, в вариантах осуществления изобретения, где используют необязательную маску 322 операции с упакованными данными, элементы данных результата, соответствующие замаскированным элементам маски, могут обладать значениями, которые не зависят от операции, выполненной с соответствующей парой элементов исходных данных. Предпочтительнее, эти элементы данных результата могут обладать замаскированными значениями (например, фиксированными или заранее заданными значениями). Например, или не нужно выполнять соответствующую операцию, или если соответствующая операция выполнена, то соответствующий результат не нужно сохранять в результирующих упакованных данных. Предпочтительнее, замаскированные значения (например, фиксированные или заранее заданные значения) могут быть сохранены в соответствующем элементе данных результата.

В показанном примере N-ый элемент маски MN обладает замаскированным значением (например, в этом случае двоичный ноль). В результате, соответствующий самый левый элемент данных результата обладает замаскированным значением. Конкретное замаскированное значение может зависеть от типа маскирования, используемого для конкретной реализации. В некоторых вариантах осуществления изобретения может быть использовано маскирование нулями. При маскировании нулями замаскированные элементы данных результата могут быть приравнены нулю (например, вынуждены обладать значением, равным нулю). В других вариантах осуществления изобретения может быть использовано маскирование поглощением. При маскировании поглощением, замаскированные элементы данных результата могут обладать значением одного из соответствующих элементов исходных данных (например, соответствующий элемент исходных данных может перейти в замаскированный элемент данных результата). Например, самый левый элемент данных результата может обладать одним из следующих значений: AN, BN, или CN. В других вариантах осуществления изобретения другие элементы данных результата могут подвергаться или не подвергаться маскированию.

На фиг. 4 показана схема одного варианта осуществления операции 432 сложения трех скалярных, возможно маскированных, источников с плавающей запятой, которая может быть выполнена в ответ на один вариант осуществления команды сложения трех скалярных, возможно маскированных, источников с плавающей запятой. Скалярная операция с фиг. 4 обладает определенным сходством с упакованной операцией с фиг. 3. Чтобы избежать неясности в описании, в основном, будут описаны разные и/или дополнительные характеристики скалярной операции с фиг. 4, без повторения аналогичных или общих характеристик и подробностей относительно упакованной операции с фиг. 3. Тем не менее, следует понимать, что ранее описанные характеристики и подробности упакованной операции с фиг. 3, за исключением аспектов, касающихся множества элементов данных в каждом операнде, также могут быть, при желании, применены к скалярной операции с фиг. 4, если не указано или не ясно обратное.

Команда может определять (например, явно определять) или другим образом указывать (например, неявно указывать) первый операнд-источник 412, второй операнд-источник 414, и третий операнд-источник 416. Первый операнд-источник может содержать первый элемент А данных с плавающей запятой. Второй операнд-источник может содержать второй элемент В данных с плавающей запятой. Третий операнд-источник может содержать третий элемент С данных с плавающей запятой. Элементы А, В и С данных могут соответствовать друг другу. Подходят типы элементов данных с плавающей запятой, ранее упомянутые при рассмотрении фиг. 3.

В некоторых вариантах осуществления изобретения элементы А, В и С данных могут быть сохранены в скалярных форматах в соответствующих регистрах упакованных данных. Регистры упакованных данных могут обладать шириной в битах, превосходящей элементы А, В и С данных с плавающей запятой. Например, в различных вариантах осуществления изобретения ширина каждого регистра упакованных данных может быть равна 64 битам, 128 битам, 256 битам, 512 битам или 1024 битам, хотя объем изобретения этим не ограничен. В одном конкретном примере, могут быть использованы 128 битовые регистры упакованных данных, хотя этого не требуется. Регистры упакованных данных могут быть способны сохранять упакованные данные помимо скалярных элементов А, В и С данных с плавающей запятой.

Обращаясь снова к фиг. 4, в некоторых вариантах осуществления изобретения команда, при желании, также может определять или другим образом указывать маску 422 операции с исходными данными, хотя этого не требуется. Маска операции с исходными данными может содержать элемент М маски. Элемент М маски может соответствовать элементам А, В и С исходных данных. Элемент М маски также может соответствовать элементу данных результата, расположенному в результате 418 в той же относительной позиции. Маска операции с исходными данными может обладать аналогичными атрибутами и вариантами, что и описанная ранее маска операции с исходными упакованными данными с фиг. 3, с одним исключением, заключающимся в том, что присутствует единственный элемент маски вместо множества. В этом типовом варианте осуществления изобретения элемент маски не предполагает маскирования (например, М=1). В некоторых вариантах осуществления изобретения маска операции с исходными данными может быть использована даже в случае только одного набора соответствующих скалярных элементов.

Вариант осуществления операции 432 может быть выполнен в ответ на один вариант осуществления команды и/или в результате одного варианта осуществления команды. В вариантах осуществления изобретения, когда, при желании, использована маска 422 операции, операция может быть выполнена в зависимости от маскирования, наложения логического условия или условного управления необязательной маски операции с исходными данными. Результат 418 может быть выработан (например, в блоке исполнения) и сохранен в целевую ячейку памяти в ответ на команду. Целевая ячейка памяти может быть определена, или другим образом указана, в команде. В различных вариантах осуществления изобретения целевая ячейка памяти может быть регистром, ячейкой запоминающего устройства или другой ячейкой памяти. Результат может содержать результирующий элемент данных с плавающей запятой, который соответствует элементам А, В и С исходных данных с плавающей запятой и элементу М маски.

В показанном примере, так как элемент маски не предполагает маскирования (например, М=1), элемент данных результата сохраняет значение, которое зависит от операции, выполненной с соответствующим набором элементов А, В и С исходных данных с плавающей запятой. Более конкретно, в некоторых вариантах осуществления изобретения, результирующий элемент данных с плавающей запятой может сохранять первую округленную сумму с плавающей запятой (например, RND1(C+RND2(A+В)). Первая округленная сумма с плавающей запятой может представлять собой алгебраическую сумму второй округленной суммы с плавающей запятой (например, RND2(A+В)) и третьего элемента данных с плавающей запятой (например, С). Вторая округленная сумма с плавающей запятой (например, RND2(A+В)) может представлять собой алгебраическую сумму первого элемента данных с плавающей запятой (например, А) и второго элемента данных с плавающей запятой (например, В). Алгебраические суммы позволяют потенциально или, при желании, брать один или несколько элементов из А, В и С с обратным знаком. RND1 и RND2 используют для обозначения двух отдельных, последовательно выполняемых операций округления с плавающей запятой.

В альтернативном примере, если элемент маски содержит маскирование (например, если М=0), элемент данных результата может сохранять замаскированное значение (например, фиксированное или заранее заданное значение). Подходят ранее описанные замаскированные значения, упомянутые при рассмотрении фиг. 3 (например, 0 в случае маскирования нулями или любой из А, В или С в случае маскирования поглощением).

На фиг. 5 показана схема одного варианта осуществления операции 534 сложения трех упакованных, возможно маскированных, возможно с управлением отрицанием, источников с плавающей запятой, которая может быть выполнена в ответ на вариант осуществления команды сложения трех упакованных, возможно маскированных, возможно с управлением отрицанием, источников с плавающей запятой. Операция, возможно с управлением отрицанием, с фиг. 5 обладает определенным сходством с операцией с фиг. 3. Чтобы избежать неясности в описании, в основном, будут описаны разные и/или дополнительные характеристики операции, возможно с управлением отрицанием, с фиг. 5, без повторения аналогичных или общих характеристик и подробностей относительно операции с фиг. 3. Тем не менее, следует понимать, что ранее описанные характеристики и подробности операции с фиг. 3, также могут, при желании, применены к операции, возможно с управлением отрицанием, с фиг. 5, если не указано или не ясно обратное.

Команда может определить или другим образом указать первый операнд 512 исходных упакованных данных, содержащий элементы A1-AN данных с плавающей запятой, второй операнд 514 исходных упакованных данных, содержащий элементы B1-BN данных с плавающей запятой, и третий операнд 516 исходных упакованных данных, содержащий элементы C1-CN данных с плавающей запятой. Операнды исходных упакованных данных и элементы данных могут обладать описанными выше признаками и вариантами (например, для фиг. 3).

В некоторых вариантах осуществления изобретения команда, при желании, также может определять или другим образом указывать маску 522 операции с исходными упакованными данными, хотя этого не требуется. Маска операции с исходными упакованными данными может содержать элементы M1-MN маски. Маска операции с исходными упакованными данными и элементы маски могут обладать описанными выше признаками и вариантами (например, для фиг. 3). В показанном примере, элементы M1 и MN маски не предполагают маскирования (например, M1=1 и MN=1).

В некоторых вариантах осуществления изобретения команда, при желании, может содержать один или несколько битов управления отрицанием, хотя этого не требуется. Один или несколько битов управления отрицанием могут позволить программному обеспечению и/или программисту управлять отрицанием любого одного или нескольких или всех операндов-источников. В некоторых вариантах осуществления изобретения команда может содержать первый набор из одного или нескольких битов 536, которые соответствуют первому операнду-источнику 512, для определения, должно ли применяться отрицание ко всем элементам упакованных данных с плавающей запятой (например, A1-AN) первого операнда-источника. В некоторых вариантах осуществления изобретения команда также, или в качестве альтернативы, может содержать второй набор из одного или нескольких битов 538, которые соответствуют второму операнду 514-источнику, для определения, должно ли применяться отрицание ко всем элементам упакованных данных с плавающей запятой (например, B1-BN) второго операнда-источника. В некоторых вариантах осуществления изобретения команда также, или в качестве альтернативы, может содержать третий набор из одного или нескольких битов 540, которые соответствуют третьему операнду-источнику 516, для определения, должно ли применяться отрицание ко всем элементам упакованных данных с плавающей запятой (например, C1-CN) третьего операнда-источника.

В некоторых вариантах осуществления изобретения единственный бит может соответствовать каждому соответствующему операнду исходных упакованных данных и может быть использован для обеспечения управления отрицанием для этого операнда исходных упакованных данных. В соответствии с одной возможной договоренностью, каждый единственный бит управления отрицанием может быть установлен равным двоичной единице (то есть, 1) для определения того, что все элементы данных соответствующих исходных упакованных данных должны быть взяты с обратным знаком, или вместо этого может быть очищен до двоичного нуля (то есть, 0) для определения того, что все элементы данных соответствующего операнда исходных упакованных данных не должны быть взяты с обратным знаком. Например, первый бит 536 может быть установлен для определения того, что все элементы данных первого операнда-источника (например, A1-AN) должны быть взяты с обратным знаком, или очищен для указания того, что они не должны быть взяты с обратным знаком. Аналогично, второй бит 538 может быть установлен для определения того, что все элементы данных второго операнда-источника (например, B1-BN) должны быть взяты с обратным знаком, или очищен для указания того, что они не должны быть взяты с обратным знаком. Аналогично, третий бит 540 может быть установлен для определения того, что все элементы данных третьего операнда-источника (например, C1-CN) должны быть взяты с обратным знаком, или очищен для указания того, что они не должны быть взяты с обратным знаком.

В некоторых вариантах осуществления изобретения может присутствовать один набор из одного или нескольких битов управления отрицанием, который может соответствовать и обеспечивать управление отрицанием для любых из первых, вторых и третьих исходных упакованных данных. В других вариантах осуществления изобретения может присутствовать два набора из одного или нескольких битов управления отрицанием каждый, которые могут соответствовать и обеспечивать управление отрицанием для любых двух данных из первых, вторых и третьих исходных упакованных данных. В качестве альтернативы, может присутствовать три набора из одного или нескольких битов каждый для управления отрицанием, которые могут соответствовать и обеспечивать управление отрицанием для всех трех данных из первых, вторых и третьих исходных упакованных данных.

В некоторых вариантах осуществления изобретения бит (биты) управления отрицанием могут, при желании, быть предоставлены непосредственным значением 542 для команды. Например, в одном конкретном примере варианта осуществления изобретения, при желании, может быть использован 8-битовое непосредственное значение, и один бит 536, который соответствует первым исходным упакованным данным, может быть предоставлен битом imm8[0], один бит 538, который соответствует вторым исходным упакованным данным, может быть предоставлен битом imm8[1], и один бит 540, который соответствует третьим исходным упакованным данным, может быть предоставлен битом imm8[2], В других вариантах осуществления изобретения могут быть использованы непосредственные значения другого размера, такие как, например, 2-битовые непосредственные значения, 4-битовые непосредственные значения, 6-битовые непосредственные значения, и так далее. В других вариантах осуществления изобретения, при желании, могут быть использованы другие биты таких непосредственных значений и/или их могут сопоставлять другим образом с исходными упакованными данными. В другом варианте, вместо использования непосредственного значения, бит (биты) управления отрицанием могут быть другим образом предоставлены командой (например, как часть кода операции, как другое поле команды и так далее).

Снова обращаясь к фиг. 5, в показанном примере, один бит управления отрицанием используют как соответствующий каждым исходным упакованным данным. Более того, бит установлен для определения отрицания или бит сброшен для определения отсутствия отрицания. В показанном примере, сброшен бит, соответствующий первым исходным упакованным данным, и сброшен бит, соответствующий третьим исходным упакованным данным. Соответственно, элементы данных первых (например, A1-AN) и третьих исходных упакованных данных (например, C1-CN) не будут браться с обратным знаком. В отличие от этого, установлен бит, соответствующий вторым исходным упакованным данным, и, таким образом, элементы данных вторых исходных упакованных данных (например, В1-BN) будут взяты с обратным знаком.

Вариант осуществления операции 534 может быть выполнен в ответ на один вариант осуществления команды и/или в результате одного варианта осуществления команды. Результирующие упакованные данные 518 могут быть выработаны (например, в блоке исполнения) и сохранены в целевую ячейку памяти в ответ на команду. Результирующие упакованные данные могут содержать множество элементов данных результата. В показанном примере варианта осуществления изобретения самый правый элемент данных результата с плавающей запятой может хранить первую округленную сумму с плавающей запятой (например, RND1(C1+RND2(A1+(-B1))), а самый левый элемент данных результата с плавающей запятой может хранить N-ую округленную сумму с плавающей запятой (например, RND1(CN+RND2(AN+(-BN))). Заметим, что элементы B1-BN данных взяты с обратным знаком на основе управления отрицанием, предоставленного вторым битом 538. Первая и N-ая округленные суммы с плавающей запятой могут представлять собой алгебраическую сумму другой соответствующей округленной суммы с плавающей запятой (например, RND2(A1+(-B1)) или RND2(AN+(-BN))) и соответствующего элемента данных с плавающей запятой из третьих исходных упакованных данных (например, С1 или CN). Алгебраические суммы позволяют потенциально или, при желании, брать исходные элементы данных, в этом случае B1-BN, с обратным знаком.

Предпочтительно, чтобы способность команды определять управление отрицанием, при желании, могла быть использована для увеличения гибкости команды (например, позволяя вычитать одни или несколько источников). В качестве альтернативы, отрицание, при желании, может быть выполнено вне границ исполнения команды сложения трех упакованных источников с плавающей запятой (например, с помощью одной или нескольких других команд).

В таблице 1 предоставлено описание конкретного примера варианта осуществления команды, которая называется VADD3PD, сложения трех упакованных источников с плавающей запятой двойной точности, с маскированием и управлением отрицанием. В некоторых вариантах осуществления изобретения команда может обладать следующим форматом: VADD3PD zmml {k1}{z}, zmm2, zmm3/m512, imm8{er}. В некоторых вариантах осуществления изобретения команда может быть закодирована в EVEX как EVEX.U1.NDS.512. F3.0F3A.W1 68 /r/is4.

Ниже показан псевдокод для команды VADD3PD. DEST является первым операндом-источником и операндом-назначением. SRC2 является вторым операндом-источником. SRC3 является третьим операндом-источником. VL является вектором с длиной в битах, в этом случае 512-битовым вектором. KL является маской с длиной в битах, в этом случае 8-битовой маской. EVEX.b бит используют для встроенного управления округлением и запрещения исключений, k1 является маской операции с исходными данными. IMM8 является 8 битовым непосредственным значением. «i» и «j» являются счетчиками. В других вариантах осуществления изобретения регистры могут быть заменены памятью или другими ячейками запоминающего устройства.

В таблице 2 предоставлено описание конкретного примера варианта осуществления команды, которая называется VADD3PS, сложения трех упакованных источников с плавающей запятой одинарной точности с маскированием и управлением отрицанием.

Псевдокод для команды VADD3PS аналогичен приведенному выше псевдокоду для команды VADD3PD за исключением того, что вместо 64-битовых элементов данных используют 32-битовые элементы данных и используют в два раза более широкие маски операций. В других вариантах осуществления изобретения регистры могут быть заменены памятью или другими ячейками запоминающего устройства.

Эти примеры являются просто приведенными для иллюстрации примерами подходящих вариантов осуществления команд. Другие варианты осуществления изобретения могут использовать или более узкие, или более широкие операнды исходных упакованных данных и/или могут использовать другие размеры элементов данных с плавающей запятой. Другие варианты осуществления изобретения могут не использовать маскирования/наложения логического условия. Другие варианты осуществления изобретения могут не использовать управление отрицанием. Другие варианты осуществления изобретения могут по-другому определять или указывать операнд-источник и/или операнд-назначение.

На фиг. 6 показана схема одного варианта осуществления операции 644 сложения трех скалярных, возможно маскированных, возможно с управлением отрицанием, источников с плавающей запятой, которая может быть выполнена в ответ на вариант осуществления команды сложения трех скалярных, возможно маскированных, возможно с управлением отрицанием, источников с плавающей запятой. Скалярная операция, возможно с управлением отрицанием, с фиг. 6 обладает определенным сходством со скалярной операцией с фиг. 4, но содержит необязательное управление отрицанием, аналогичное упакованной операции с фиг. 5. Чтобы избежать неясности в описании, кратко будут описана фиг. 6, без повторения всех необязательных аналогичных или общих характеристик и подробностей, касающихся операции с фиг. 4-5. Тем не менее, следует понимать, что ранее описанные характеристики и подробности скалярной операции с фиг. 4 и аспекты необязательного управления отрицанием операции с фиг. 5 также могут быть, при желании, применены к операции с фиг. 6, если не указано или не ясно обратное.

Как со скалярной операцией с фиг. 4, команда может определить или другим образом указать первый операнд-источник 612, содержащий элемент А данных, второй операнд-источник 614, содержащий элемент В данных, и третий операнд-источник 616, содержащий элемент С данных. Операнды-источники и элементы данных могут обладать описанными выше признаками и вариантами (например, для фиг. 4).

В некоторых вариантах осуществления изобретения команда, при желании, также может определять или другим образом указывать маску 622 операции с исходными данными, хотя этого не требуется. Маска операции с исходными данными и элемент маски могут обладать описанными выше признаками и вариантами (например, для фиг. 4). В показанном примере элемент М маски не предполагает маскирования (например, М=1).

В некоторых вариантах осуществления изобретения команда, при желании, может содержать один или несколько битов управления отрицанием, хотя этого не требуется. Например, в показанном варианте осуществления изобретения, команда содержит первый бит 636, второй бит 638 и третий бит 640, хотя объем изобретения этим не ограничен. Эти биты, при желании, могут быть непосредственным значением 642, хотя объем изобретения этим не ограничен. В других вариантах осуществления изобретения, команда может содержать управление отрицанием с любыми описанными выше признаками, характеристиками и вариантами операции с фиг. 5, за исключением того, что управление отрицанием применяют к одиночным скалярным элементам данных в исходных операциях в этом скалярном варианте осуществления изобретения. В показанном примере варианта осуществления изобретения первый бит 636 установлен для управления отрицанием элемента А данных, второй бит 638 сброшен для отсутствия управления отрицанием элемента В данных, и третий бит 640 установлен для управления отрицанием элемента С данных. В результате, в этом примере результат можно сохранять как один элемент данных результата первой округленной суммы с плавающей запятой (например, RND1((-C)+RND2((-A)+В))). Следует понимать, что то, какие операнды-источники взяты с обратным знаком, является только примером для иллюстрации и в других вариантах осуществления изобретения операнды-источники могут быть взяты по-другому или вообще не взяты с обратным знаком.

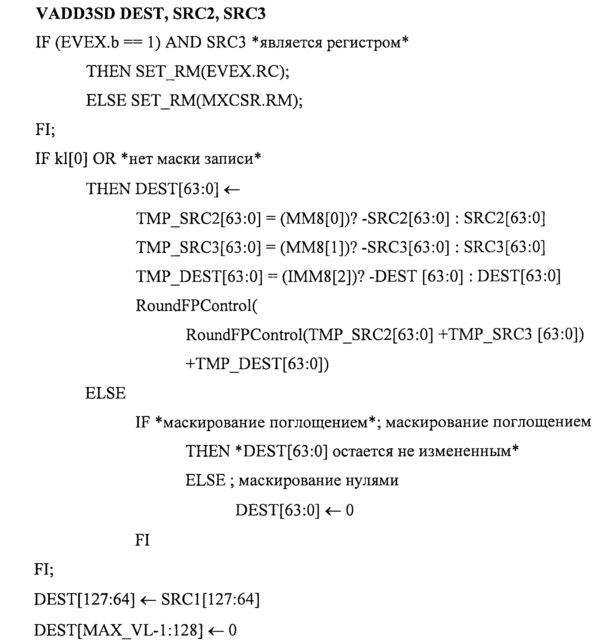

В таблице 3 предоставлено описание конкретного примера варианта осуществления команды, которая называется VADD3SD, сложения трех скалярных источников с плавающей запятой двойной точности, с маскированием и управлением отрицанием. В некоторых вариантах осуществления изобретения команда может обладать следующим форматом

VADD3SD xmm1 {k1}{z}, xmm2, xmm3/m64, imm8{er}. В некоторых вариантах осуществления изобретения команда может быть закодирована в EVEX как EVEX.UENDS.128.F3.0F3A.W1 69 /r/is4.

Ниже показан псевдокод для команды VADD3SD. DEST является первым операндом-источником и операндом-назначением. SRC2 является вторым операндом-источником. SRC3 является третьим операндом-источником. EVEX.b бит используют для встроенного управления округлением и запрещения исключений, k1 является маской операции с исходными данными. IMM8 является 8 битовым непосредственным значением. В других вариантах осуществления изобретения регистры могут быть заменены памятью или другими ячейками запоминающего устройства.

В таблице 4 предоставлено описание конкретного примера варианта осуществления команды, которая называется VADD3SS, сложения трех скалярных источников с плавающей запятой одинарной точности, с маскированием и управлением отрицанием.

Псевдокод для команды VADD3SS аналогичен приведенному выше псевдокоду для команды VADD3SD за исключением того, что вместе 64-битовых элементов данных используют 32-битовые элементы данных. В других вариантах осуществления изобретения регистры могут быть заменены памятью или другими ячейками запоминающего устройства.

Эти примеры являются просто приведенными для иллюстрации примерами подходящих вариантов осуществления команд. Другие варианты осуществления изобретения могут использовать другие размеры элементов данных с плавающей запятой. Другие варианты осуществления изобретения могут не использовать маскирования/наложения логического условия. Другие варианты осуществления изобретения могут не использовать управление отрицанием. Другие варианты осуществления изобретения могут по-другому определять или указывать операнд-источник и/или операнд-назначение.

На фиг. 7 показана схема одного варианта осуществления суммирующего устройства 707 для трех источников с плавающей запятой, выполненного для сложения трех операндов-источников с плавающей запятой. В этом варианте осуществления изобретения суммирующее устройство для трех источников с плавающей запятой выполнено для одновременного приема и сложения первого операнда-источника 712 с плавающей запятой, второго операнда-источника 714 с плавающей запятой и третьего операнда-источника 716 с плавающей запятой и выработки потенциально округленного результата 750. Суммирующее устройство содержит входы для одновременного приема трех операндов-источников и способно складывать их, в общем, в ходе операции одновременного сложения. В таких вариантах осуществления изобретения, в целом, не нужна и не выполняется операция промежуточного округления и нормализации. Тем не менее, один потенциальный недостаток таких суммирующих устройств для трех источников с плавающей запятой заключается в том, что часто они имеют склонность обладать сравнительно более сложной конструкцией, часто обладают большими размерами, часто потребляют сравнительно большее количество электроэнергии и часто являются более специализированными устройствами.

Многие процессоры уже обладают или легко могут обладать одним или несколькими суммирующими устройствами для двух источников с плавающей запятой, каждое из которых способно одновременно складывать два операнда-источника с плавающей запятой, но которые не способны одновременно складывать три операнда-источника с плавающей запятой. Примерами таких суммирующих устройств являются обычные суммирующие устройства с плавающей запятой, объединенные устройства умножения-сложения и подобные. В некоторых вариантах осуществления изобретения такие существующие суммирующие устройства для источников с плавающей запятой могут быть использованы для реализации описанных в настоящем документе команд/операций сложения трех источников с плавающей запятой с целью исключения необходимости содержать специальное суммирующее устройство для трех источников с плавающей запятой, такое как показано на фиг.7.

На фиг. 8 показана схема одного варианта осуществления двух последовательно связанных суммирующих устройств 808А, 808В для двух источников с плавающей запятой с целью сложения трех операндов-источников с плавающей запятой. В качестве примера, суммирующие устройства могут содержать суммирующие устройства с плавающей запятой, объединенные устройства умножения-сложения с плавающей запятой или подобные. Первое суммирующее устройство 808А для двух операндов-источников с плавающей запятой содержит входы, связанные с целью приема первого операнда 812 с плавающей запятой и второго операнда 814 с плавающей запятой. Первое суммирующее устройство для двух операндов-источников с плавающей запятой также содержит вход, связанный с целью приема сигнала 802 управления, соответствующего команде сложения трех источников с плавающей запятой и/или полученного из этой команды. Например, сигнал управления может быть принят из резервирующей станции (не показана). В некоторых вариантах осуществления изобретения сигнал управления или, при желании, его упрощенная версия, также могут быть, при желании, предоставлены на необязательный буфер 854. Первое суммирующее устройство для двух операндов-источников с плавающей запятой способно складывать первый и второй операнды с плавающей запятой для получения первой округленной суммы 852, содержащей первый и второй операнды. Первую округленную сумму округляют в подходящий момент в соответствии с режимом округления с плавающей запятой. Первое суммирующее устройство для двух операндов-источников с плавающей запятой содержит выход для предоставления первой округленной суммы. Второе суммирующее устройство 808В для двух источников с плавающей запятой содержит вход, связанный с выходом первого суммирующего устройства для приема первой округленной суммы. Второе суммирующее устройство для двух источников с плавающей запятой также содержит вход, связанный с целью приема третьего операнда 816 с плавающей запятой. Второе суммирующее устройство для двух источников с плавающей запятой также содержит вход, связанный с выходом буфера 854 для приема сигнала 802 управления или его упрощенной версии. Сигнал управления может храниться в буфере в течение некоторого периода времени, когда первую округленную сумму вырабатывают в первом суммирующем устройстве, и далее сигнал управления может быть предоставлен на второе суммирующее устройство вместе с первой округленной суммой. Второе суммирующее устройство для двух операндов-источников с плавающей запятой способно складывать третий операнд с плавающей запятой и первую округленную сумму для получения второй округленной суммы 818, содержащей все три операнда с плавающей запятой. Второе суммирующее устройство для двух операндов-источников с плавающей запятой содержит выход для предоставления второй округленной суммы. Предпочтительно, что в этом варианте осуществления изобретения три операнда-источника с плавающей запятой могут быть сложены без необходимости использования суммирующего устройства для трех источников с плавающей запятой, что может помочь уменьшить сложность конструкции, размер и/или потребление электроэнергии.