Вероятностный вычитатель - RU181260U1

Код документа: RU181260U1

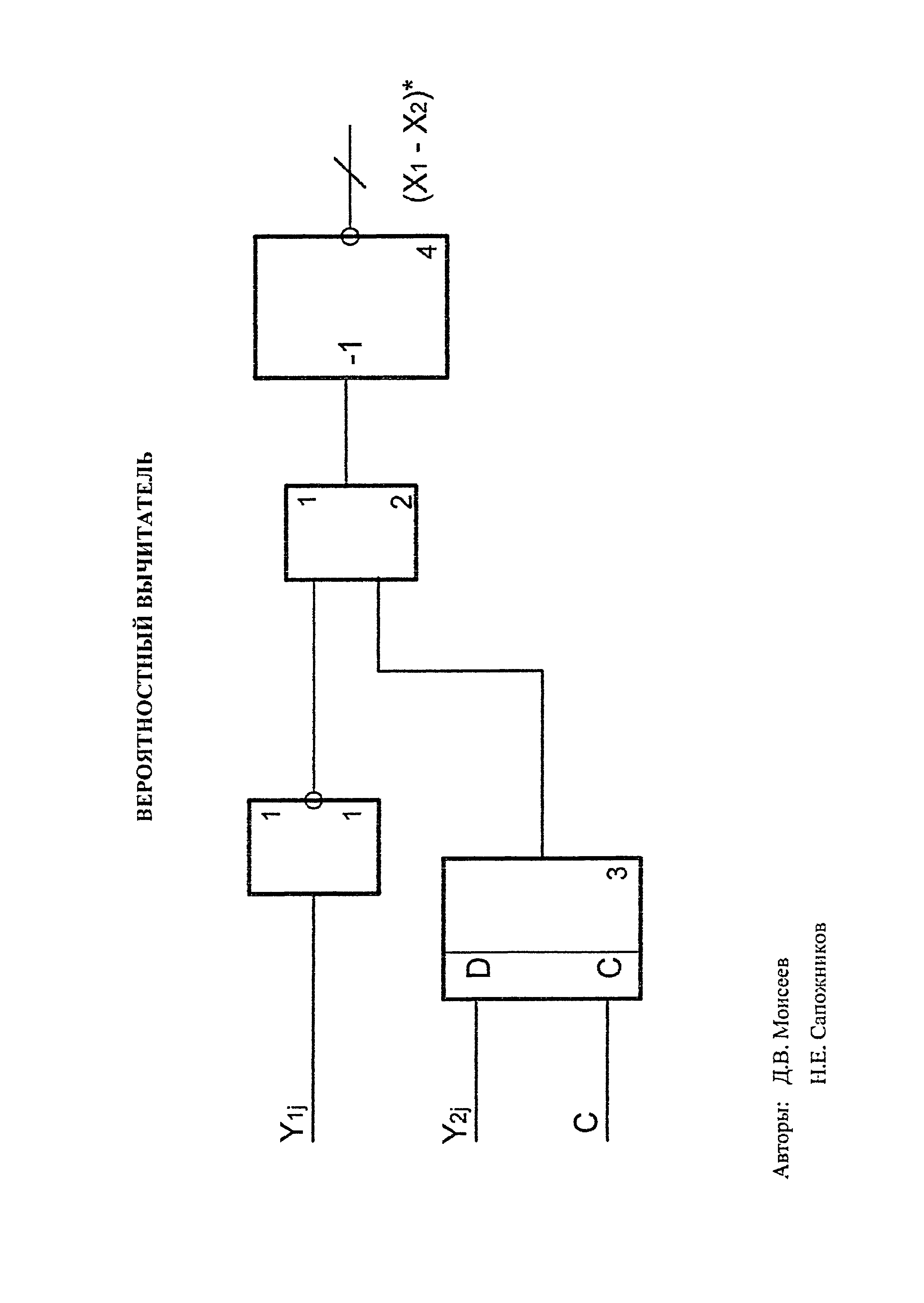

Чертежи

Описание

Полезная модель относится к области автоматики и измерительной техники и может быть использовано в арифметических устройствах, специализированных и универсальных ЭВМ.

Из существующего уровня техники известны вероятностные вычитатели аналогичного назначения, в состав которых входят: первый и второй блоки сравнения, генератор случайных чисел, первый и второй элемент ЗАПРЕТ, стохастический интегратор, элемент ИЛИ, триггер знака. (Стохастический вычитатель, АС №970364, СССР, опубл. 30.10.1982, бюл. №40). Основным недостатком данного прототипа является большой аппаратный объем.

Задачей, на решение которой направлена заявляемая полезная модель - сокращение оборудования при выполнении операции вычитания над операндами представленными в виде вероятностного отображения.

Данная задача решается за счет того, что схема вероятностного вычитателя содержит инвертор, на вход которого подается уменьшаемое, выход инвертора нагружен на первый вход дизъюнктора, на второй вход которого нагружен прямой выход однотактного D-триггера, на синхровход которого поступает синхроимпульсы, а на информационный вход которого подается вычитаемое, выход дизъюнктора нагружен на декрементирующий вход вычитающего счетчика, инверсный выход которого является выходом всей схемы.

Техническим результатом, обеспечиваемым приведенной совокупностью признаков, является значительное снижение аппаратного объема устройства в целом, сравнительно с прототипом.

Сущность полезной модели поясняется чертежом Фиг., на котором изображена схема вероятностного вычитателя, в состав которой входит:

1 - инвертер;

2 - дизъюнктор;

3 - однотактный D-триггер;

4 - двоичный вычитающий счетчик.

Для получения разности при представлении уменьшаемого и вычитаемого в виде вероятностных отображений, можно, операцию вычитания реализовать на основе операции сложения используя инверсию вероятностного отображения.

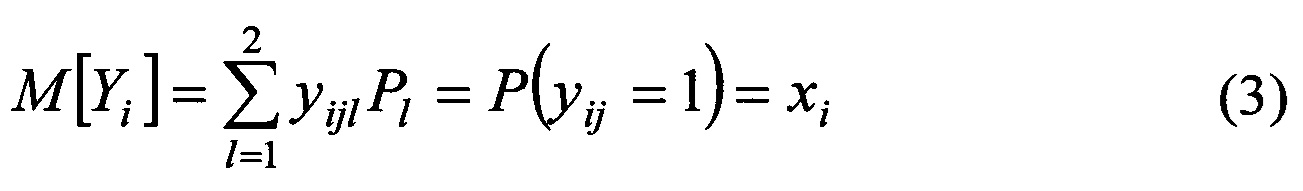

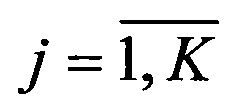

Представление информации в вероятностное отображение поясняется правилом:

где хi - i-e значение параметра преобразуемого сигнала X(t);

R(tij) - j-е значение параметра вспомогательного случайного сигнала R(t), изменяющегося в интервале изменениях X(t);

уij - значение вероятностного отображения параметра сигнала xi из ряда Yt(t)={yi1; yi2; … yij; … yiK).

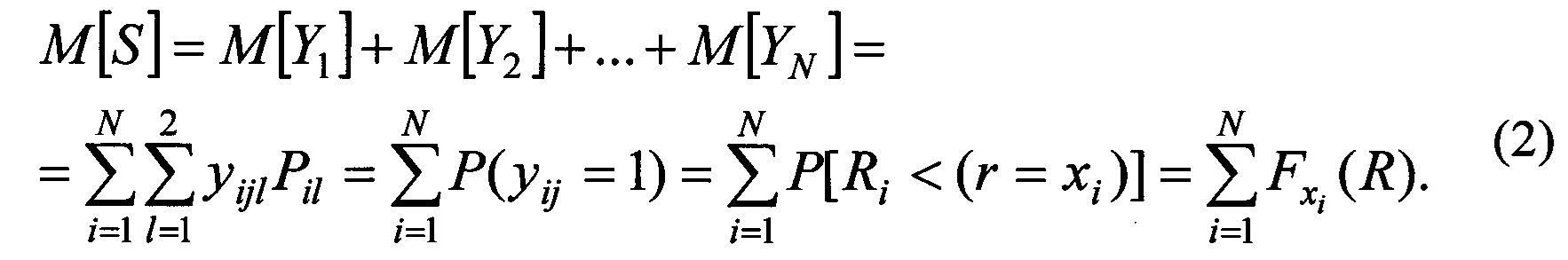

Математическое ожидание случайной последовательности S можно рассматривать как сумму математических ожиданий вероятностных отображений ее членов, то есть

Для вспомогательной случайной величины R, распределенной равномерно, имеем:

и далее получим

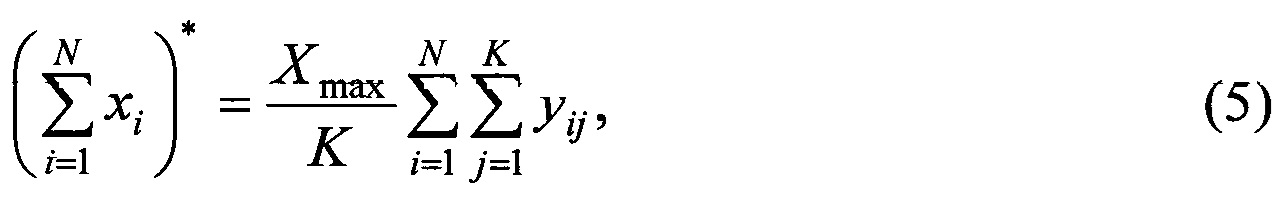

В качестве оценки для суммы входных слагаемых получим:

Таким образом, сумма вероятностно представленных значений будет равна сумме единиц, входящих в вероятное отображение каждого из операндов, отнесенной к количеству статистических испытаний К и умноженной на значение верхней границы диапазона Хmax.

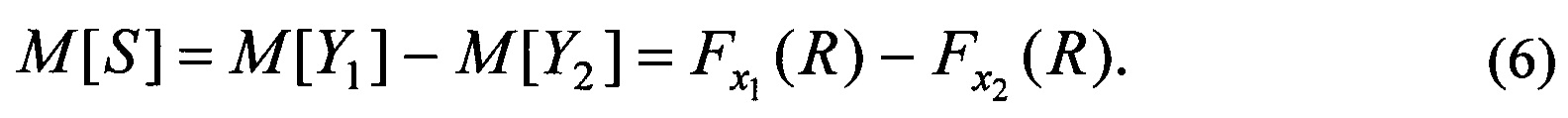

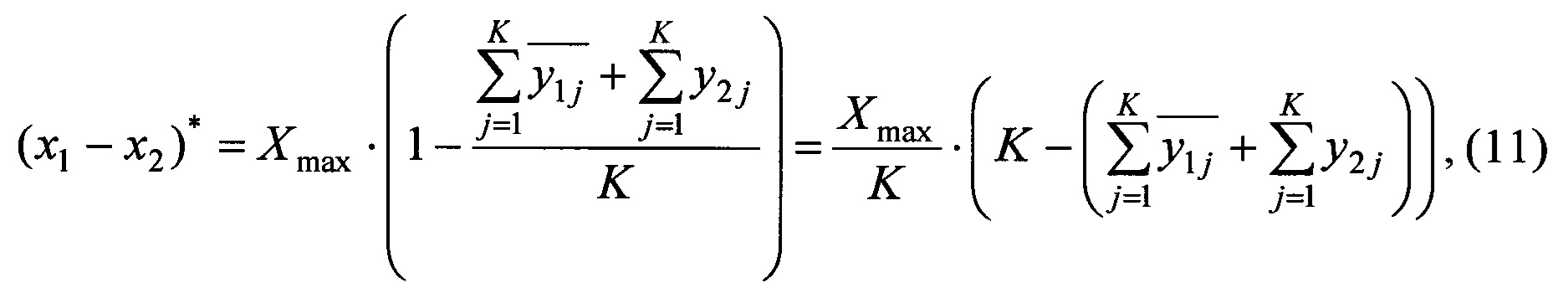

Для выполнения операции вычитания, выполнив те же действия, что и для сложения двух слагаемых, второе из которых взято с противоположным знаком, из выражения (2) получим:

При равномерном распределении вспомогательной случайной последовательности R имеем выражение для вероятностного вычитания

Имеем вероятностное отображение уменьшаемого Y1 и вычитаемого Y2:

Y1={y11; y12, … , y1j, … , y1k} и Y2={y21, y22, …, y2j, …, y2k}

где yij - j-ое значение вероятностного отображения величины Х1 и Х2;

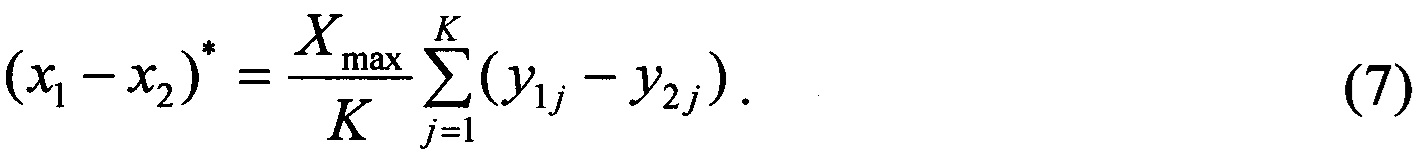

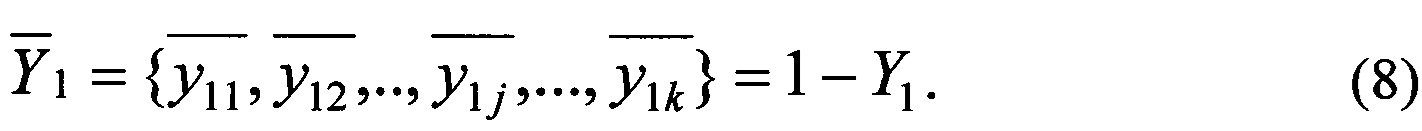

Инвертируя все разряды вероятностного отображения уменьшаемого Y1 получим:

Применив это свойство к первому операнду при сложении двух чисел, получим

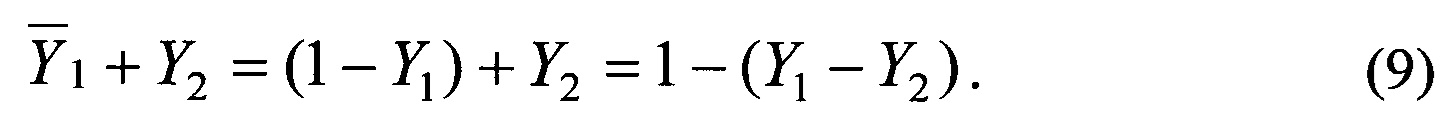

Проинвертируем выражение (9):

Из выражения (10) видно, что разность двух вероятностно представленных чисел можно найти через сумму, проинвертировав первый операнд и результат операции.

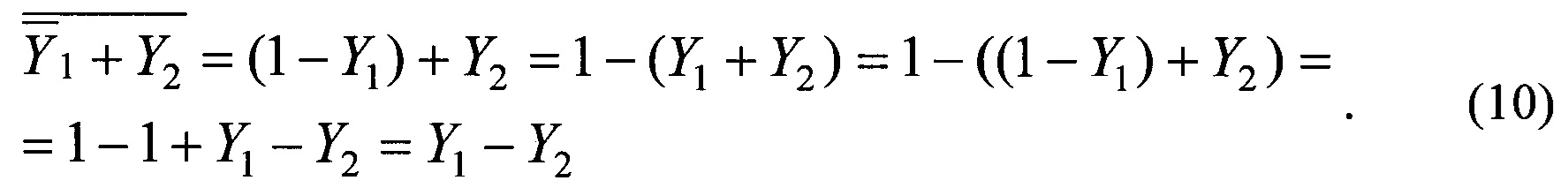

При этом необходимо применять нормирование:

Процессы в схеме вероятностного вычитателя протекают в следующей последовательности. После подачи на схему электропитания, в двоичный вычитающий счетчик заносится значение К - количество статистических испытаний, вероятностное отображение уменьшаемого поступает на вход инвертора (1), на выходе которого в результате инвертировании всех разрядов вероятностной последовательности получаем значение 1-Y1, которое поступает на первый вход дизъюнктора (2), вычитаемое Y2 поступает на вход однотактного D-триггера (3) в котором производится задержка передачи вероятностного отображения вычитаемого Y2 на пол такта, после чего, с прямого выхода однотактного D-триггера (3), вероятностного отображения вычитаемого Y2 поступает на второй вход дизъюнктора (2), на выходе которого формируется значение суммы вероятностных отображений

Преимущество усовершенствованного вероятностного вычитателя состоит в том, схема прототипа заменена на схему, содержащую инвертор (1), дизъюнктор (2), однотактный D-триггер (3), двоичный вычитающий счетчик (4), аппаратная реализация которой значительно проще.

Реферат

Полезная модель относится к области автоматики и измерительной техники и может быть использована в арифметических устройствах, специализированных и универсальных ЭВМ.Технический результат полезной модели заключается в значительном снижении аппаратного объема устройства в целом, сравнительно с прототипом, достигаемое путем замены схемы Прототипа на схему, содержащую: инвертор, дизъюнктор, однотактный D-триггер, двоичный вычитающий счетчик, аппаратная реализация которой значительно проще.Решение технической задачи достигается изменениями схемы вероятностного вычитателя выполняющего операцию разности между уменьшаемым и вычитаемым, представленными в виде вероятностных отображений.

Комментарии