Многовходовой цифровой сумматор импульсных потоков - RU181022U1

Код документа: RU181022U1

Чертежи

Описание

Полезная модель относится к области вычислительной техники и может быть использована в различных областях науки и промышленности при создании устройств управления и цифровой обработки сигналов.

Из существующего уровня техники известен цифровой двухвходовой сумматор импульсных потоков [Ng С.W. et al. Bit-stream adders and multipliers for tri-level sigma-delta modulators / IEEE Transactions on Circuits and Systems II: Express Briefs, 2007, V. 54, N. 12, pp. 1082-1086]. Такое устройство содержит три трехвходовых однобитных сумматора и однобитный элемент памяти.

Недостатками данного устройства является низкая точность при сложении трех и более импульсных потоков при помощи каскада из нескольких сумматоров. Этот недостаток связан с малым объемом памяти в сумматоре, не позволяющим хранить перенос, если он возникает на двух последовательных тактах сложения импульсных потоков.

Предлагаемая полезная модель направлена на решение технической задачи по устранению указанного недостатка.

Достигаемый при этом технический результат заключается в повышении точности формирования результирующего сигнала на выходе сумматора при сложении трех и более импульсных потоков.

Технический результат достигается тем, что многовходовой цифровой сумматор импульсных потоков включает в себя цифровой сумматор входных потоков, выход которого преобразуется в импульсный поток при помощи цифрового сигма-дельта модулятора первого порядка, включающего в себя цифровой отрицательный сумматор, соединенный с цифровым сумматором интегратора, который соединен с элементом памяти, вход разрешения которого подключен к таблице истинности, подключенной к двум старшим битам результата цифрового сумматора интегратора и старшему биту результата цифрового отрицательного сумматора, а выход элемента памяти подключен к цифровому квантователю, выход которого является выходом многовходового цифрового сумматора импульсных потоков, а также подключен к цифровому отрицательному сумматору.

Указанные признаки полезной модели являются существенными и совокупность этих признаков достаточна для получения требуемого технического результата.

Полезная модель поясняется чертежами.

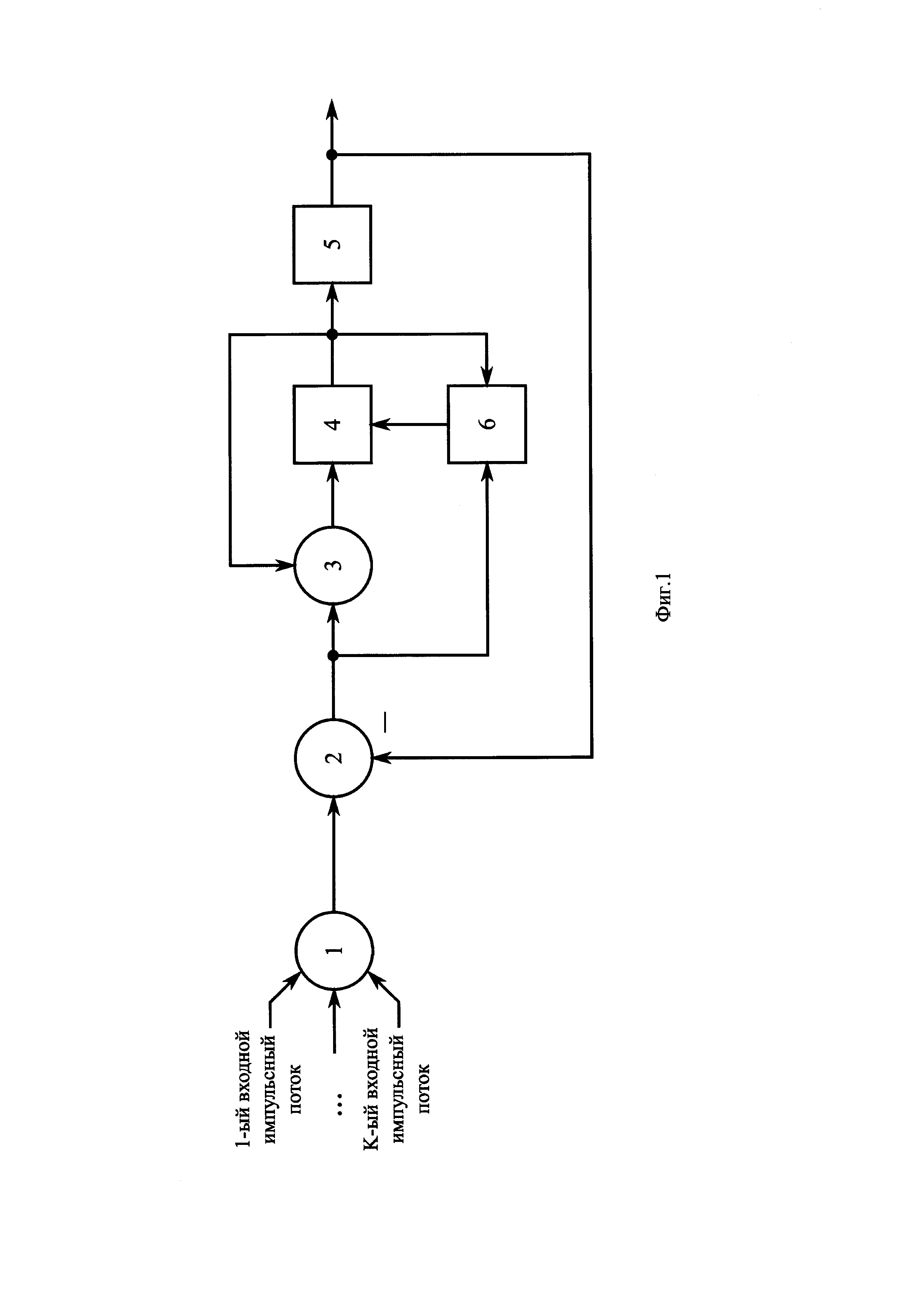

На фиг. 1 показана блок-схема заявляемой полезной модели. Она содержит цифровой сумматор входных потоков 1, цифровой отрицательный сумматор 2, цифровой сумматор интегратора 3, элемент памяти с входом разрешения записи 4, цифровой квантователь 5 и таблицу истинности 6.

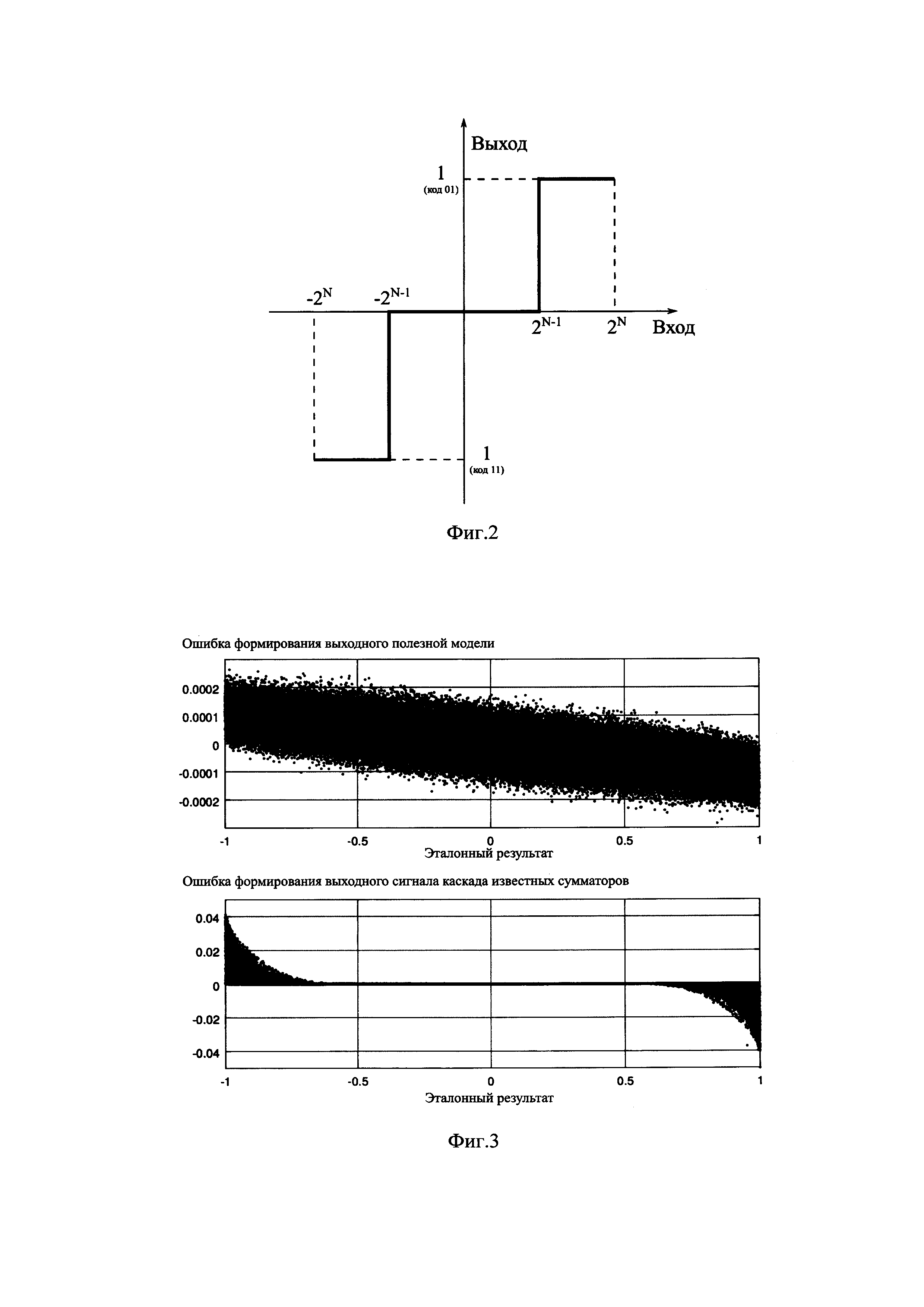

Работает устройство следующим образом. На его вход поступают K импульсных потоков, закодированных таким образом, что импульсу амплитудой -1 соответствует двухбитный код 11, импульсу с амплитудой 1 соответствует двухбитный код 01, а отсутствию импульса соответствует код 00. Коды входных импульсных потоков поступают на цифровой сумматор входных потоков 1, где складываются без потери точности, формируя выходной N-битный импульсно-кодовомодулированный сигнал, где N≥(log2 K+1). Результат цифрового сумматора входных потоков 1 поступает на вход N-битного цифрового отрицательного сумматора 2, где из него вычитается выход многовходового цифрового сумматора импульсных потоков, полученный на предыдущем шаге расчета и дополненный N-2 знаковыми битами до размера N-бит. Младшие N-бит выхода цифрового отрицательного сумматора 2 поступают на первый вход цифрового сумматора интегратора 3, к второму входу которого подключен выход элемента памяти 4. Выход цифрового сумматора интегратора 3 записывается в элемент памяти 4 при наличии сигнала разрешения записи. Сигнал разрешения записи формируется при помощи таблицы истинности 6, на вход которой поступают два старших бита выхода элемента памяти 4 и старший бит выхода цифрового отрицательного сумматора 2. Формирование выхода таблицы истинности 6 осуществляется согласно таблице 1. Выход элемента памяти 4 поступает на симметричный цифровой квантователь 5, который на его основе формирует двухбитный код, соответствующий значению амплитуды следующего импульса выходного потока. Зависимость выхода квантователя 5 от его входа показана на фиг. 2. Элементы 1-5 изменяют свои выходы синхронно по фронту общего тактового сигнала.

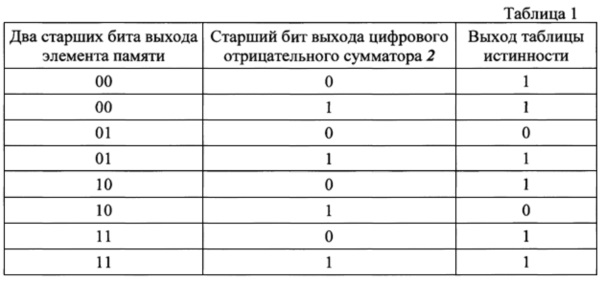

Работоспособность была проверена на макете, который наглядно продемонстрировал получение требуемого технического результата. Предложенное устройство было реализовано в виде трехвходового сумматора импульсных потоков с N=4. Также для сравнения был отмакетирован аналог на базе каскада из двух известных двухвходовых сумматоров импульсных потоков [Ng C.W. et al. Bit-stream adders and multipliers for tri-level sigma-delta modulators / IEEE Transactions on Circuits and Systems II: Express Briefs, 2007, V. 54, N. 12, pp. 1082-1086]. Формирование входных импульсных потоков осуществлялось при помощи цифровых сигма-дельта модуляторов первого порядка, работающих на частоте 100 МГц. Демодуляция входных импульсных потоков и результирующего импульсного потока сумматора осуществлялась при помощи усредняющего фильтра с окном 65535 измерений с периодом 10 не. Все элементы макета были реализованы на базе микросхемы ПЛИС Xilinx XC7A100T-1CSG324C, которая тактировалась генератором с частотой 100 МГц.

На фиг. 3 показана зависимость ошибки выходного результата полезной модели и каскада известных сумматоров, приведенной к максимальной амплитуде импульсов в импульсных потоках от эталонного значения результата, полученная в ходе 100000 экспериментов. Как видно из фиг. 3, максимальная ошибка сложения трех импульсных потоков у предложенной полезной модели на 2 порядка ниже, чем у каскада известных двухвходовых сумматоров импульсных потоков, что говорит о ее работоспособности и достижении заявленного технического результата.

Реферат

Полезная модель относится к области вычислительной техники, а именно к многовходовому цифровому сумматору импульсных потоков, включающему в себя цифровой сумматор входных потоков, выход которого преобразуется в импульсный поток при помощи цифрового сигма-дельта модулятора первого порядка, включающего в себя цифровой отрицательный сумматор, соединенный с цифровым сумматором интегратора, который соединен с элементом памяти, вход разрешения которого подключен к таблице истинности, подключенной к двум старшим битам выхода элемента памяти и старшему биту результата цифрового отрицательного сумматора, а выход элемента памяти подключен к цифровому квантователю, выход которого является выходом многовходового цифрового сумматора импульсных потоков, а также подключен к цифровому отрицательному сумматору. Полезная модель обеспечивает повышение точности формирования результирующего сигнала на выходе сумматора при сложении трех и более импульсных потоков.

Комментарии