Запоминающее устройство прямого доступа (dasd) емкостью больше 528 мегабайт и способ его воплощения для персональных компьютеров - RU2155369C2

Код документа: RU2155369C2

Чертежи

Описание

Персональные компьютерные системы в целом и, в частности, персональные компьютеры фирмы IBM получили широкое распространение, обеспечивая вычислительными услугами многие слои современного общества. Под персональными компьютерными системами обычно понимают настольные, напольные или портативные микрокомпьютеры, которые состоят из системного блока, имеющего один системный процессор и связанную с ним энергозависимую или энергонезависимую память, монитор, клавиатуру, один или более накопителей на гибких дисках, накопитель на фиксированных (несъемных) магнитных дисках и, на выбор, принтер или плоттер. Одним из отличительных признаков этих систем является использование материнской платы, или системного планара (planar), для электрического соединения многих из перечисленных компонентов вместе. Эти системы предназначены главным образом для предоставления вычислительных возможностей одиночному пользователю, не требуя значительных затрат при их покупке отдельными людьми или небольшими организациями. Примерами таких персональных компьютерных систем являются системы IBM: персональный компьютер AT, персональная система PS/1, персональная система PS/2 и THINKPAD.

Эти системы можно разбить на два основных семейства. В первом семействе, обычно называемом "модели I семейства", используется системная и шинная архитектура, такая как, например, в персональных компьютерах AT IBM и других IBM-совместимых системах. Во втором семействе, обычно называемом "модели II семейства", используется микроканальная шинная архитектура, такая, например, как в моделях с 50 по 95 персональных систем IBM PS/2. Первоначально в моделях I семейства в качестве системного процессора использовался микропроцессор INTEL 8088 или 8086. Эти процессоры имеют возможность адресации одного мегабайта оперативного запоминающего устройства прямого доступа (известного также, как PAM - энергонезависимой памяти, используемой в качестве оперативной памяти в персональных компьютерных системах). В моделях II семейства использовались высокоскоростные микропроцессоры INTEL 80286, 80386, 80486 и Pеntium, которые могут работать в реальном режиме для эмуляции низкоскоростного микропроцессора INTEL 8086, или в защищенном режиме, который расширяет диапазон адресации памяти с 1 мегабайта до 4 гигабайт для некоторых моделей. В сущности, наличие реального режима процессоров 80286, 80386 и 80486 обеспечивает аппаратную совместимость с программным обеспечением, записанном для микропроцессоров 8086 и 8088.

Персональные компьютерные системы I семейства известны также как системы с "промышленным стандартом архитектуры", или ISA системы, в виду того, что конструкция таких систем воплощена в стандартах, которым следуют крупные подотрасли индустрии персональных компьютеров. Эти стандарты содержат конкретные рабочие обращения, которые используют управляющие программы, разрешающие функционирование систем. Такие управляющие программы часто называются "базовыми системами ввода/вывода", или BIOS, и ISA системы придерживаются программной разработки BIOS, изложенной в Техническом справочнике IBM BIOS. С точки зрения целей настоящего изобретения важной частью этого Справочника является раздел, относящийся к операции "Прерывание 13", изложенный на страницах 2-58 в указанной справочной публикации. Прерывание 13 устанавливает способ адресации фиксированного диска или запоминающих устройств прямого доступа (известных также, как DASD), например, памяти большой емкости, накопителей с фиксированными поворачивающимися магнитными (или другими) носителями, или "жесткими файлами", или жесткими дисками. Такие DASD отличаются от накопителей для "гибких" дисков, у которых магнитный (либо другой носитель) снимается, а не зафиксирован на месте.

DASD, используемые с персональными компьютерными системами ISA, известны также, как "AT-подключаемые" или "AT" дисководы. В системах, разработанных ранее, такие DASD обычно используются вместе с контроллером, который находится отдельно от самого дисковода. Обмен цифровыми данными между DASD и остальной частью компьютерной системы происходит под управлением контроллера, который в более ранних разработках представляет собой карту или плату, вмонтированную в разъеме, или гнезде, предназначенном для шины ввод/вывода, или 1/0 шины. (Смотри The Winn Rosch Hardware Bible, Simon (Schuster, New Yоrk, 1989; p.p. 475 f.f.). Контроллер управляется таким образом, чтобы адресовать местоположение цифровых данных, записываемых на или считываемых с поворачивающихся дисков DASD, указывая дорожку (известную также, как цилиндр) и сектор. Кроме того, поскольку DASD имеет обычно множество дисков или пластин, сложенных вместе и обслуживаемых множеством головок, указывается адрес головки, которая будет осуществлять доступ к требуемой части цилиндра, или сектору. Такая адресация известна под названием адресация "цилиндр-головка-сектор", или CHS адресация.

Благодаря некоторым ограничениям схемы прерывания 13 персональная компьютерная система предполагает адресацию одной тысячи двадцати четырех цилиндров и до двухсот пятидесяти шести головок. Однако конструкция DASD не всегда соответствует этим ожидаемым характеристикам. Взамен этого разработчики и производители DASD могут обеспечить большее число цилиндров и число головок, меньшее чем максимальное количество головок, предполагаемое схемой Прерывания 13. Обычно ATA DASD имеет 16 головок. Однако ограничение на адресацию цилиндров до одной тысячи двадцати восьми и аналогичные внутренние ограничения на размеры сектора до шестидесяти трех для каждой дорожки и количества байт на сектор до пятисот двенадцати ограничивает адресуемое пространство такого ATA/DASD с шестнадцатью головками до пятисот двадцати восьми миллионов четырех восьмидесяти двух тысяч трехсот четырех байт (1024х16х63х512).

Прогресс в разработке персональных компьютерных систем ISA привел к появлению альтернативных путей реализации управления DASD. Эти разработки содержали устройства типа дисковода с встроенным контроллером (известные также, как IDE), в которых электронные схемы, в противном случае располагаемые на плате контроллера, интегрированы в структуру DASD. Это позволяет инсталлировать IDE DASD отдельно от специально предусмотренной платы контроллера, сохраняя таким образом гнездо, или разъем, для 1/0 шины. Другой альтернативный вариант, используемый в некоторых системах, заключается в монтаже контроллера для DASD непосредственно на системной материнской плате, или планаре, также давая возможность инсталляции DASD отдельно от специально предусмотренной платы управления, сохраняя таким образом гнездо или разъем для 1/0 шины. Ни одно из этих решений не снимает проблему использования ранее упомянутых CHS данных при адресации больше, чем 1024 цилиндров в таких дисководах.

Как и в вышеупомянутых направлениях разработок, аналогичный прогресс был достигнут и в разработке и производстве DASD. В результате появились дисководы, имеющие емкости, превышающие верхнюю границу порядка 528 мегабайт. Таким образом весьма важно иметь возможность адресации дисководов с такими емкостями.

Область техники, к которой относится изобретение

Это изобретение

относится к трансляции адресации "цилиндр-головка-сектор" (CHS) цифровых данных, записанных в или считываемых из DASD, так чтобы приспособить для использования DASD с емкостью памяти, превышающей

ограничение на емкость порядка пятисот двадцати восьми мегабайт, накладываемое схемой Прерывания 13.

Сущность изобретения

Раскрытое здесь изобретение дает возможность CHS

адресации, для того чтобы должным образом адресовать DASD, имеющие емкости памяти, превышающие предел порядка пятисот двадцати восьми мегабайт, накладываемый схемой Прерывания 13, путем использования

управляющей программы, функционирующей с помощью микропроцессора и DASD: для опроса DASD относительно количества имеющихся цилиндров; определения того, превышает ли это число тысячу двадцать четыре, и

в случае, если это так, многократного деления существующего числа цилиндров на два, пока частное от деления не станет меньше чем тысяча двадцать четыре, регистрируя в то же время число таких

повторившихся делений; создания затем первого справочного кадра (записи) для данных "цилиндр-головка-сектор", которые имеют предел числа цилиндров до одной тысячи двадцати четырех цилиндров и предел

числа головок до двухсот пятидесяти шести; создание второго справочного кадра для данных "цилиндр-головка-сектор", которые имеют предел числа цилиндров больше чем тысяча двадцать четыре, и предел

числа головок, не превышающий число головок, имеющихся в данной DASD; и трансляции цифровых адресных данных памяти, которыми обмениваются первый и второй справочные кадры, для разрешения обмена данных

с использованием всей емкости памяти указанной DASD. Трансляция выполняется посредством использования количества повторившихся делений на два числа имеющихся цилиндров.

Краткое

описание чертежей

В дальнейшем изобретение поясняется описанием конкретных вариантов его воплощения со ссылками на сопровождающие чертежи, на которых:

фиг. 1 - перспективное

изображение персонального компьютера, в котором воплощается настоящее изобретение;

фиг. 2 - поэлементное перспективное изображение некоторых элементов персонального компьютера на фиг. 1,

содержащее корпус, крышку, запоминающее устройство прямого доступа (DASD) и планарную плату и иллюстрирующее некоторые связи между этими элементами;

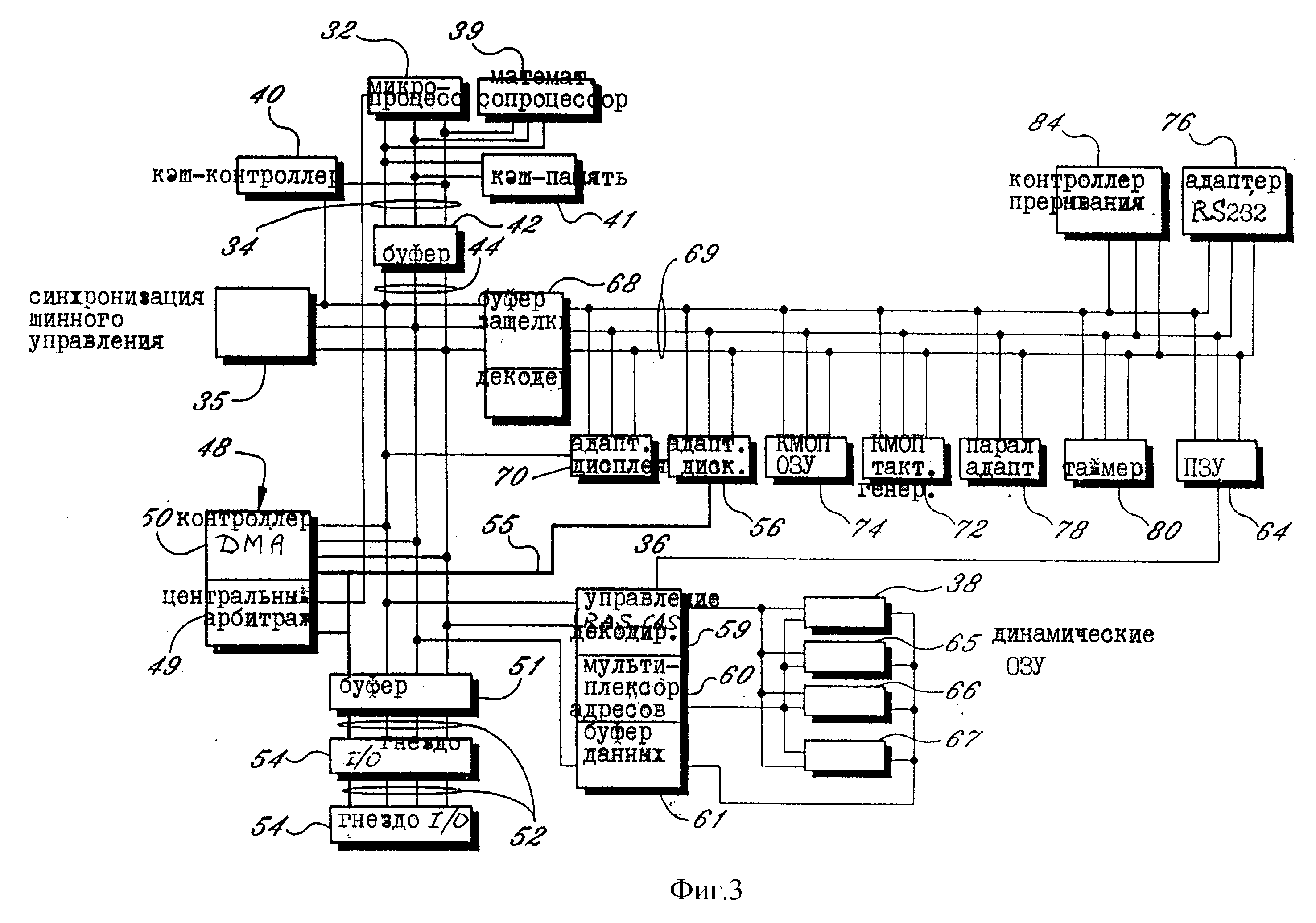

фиг. 3 - схематическое изображение

некоторых элементов персонального, компьютера, изображенных на фигурах 1 и 2;

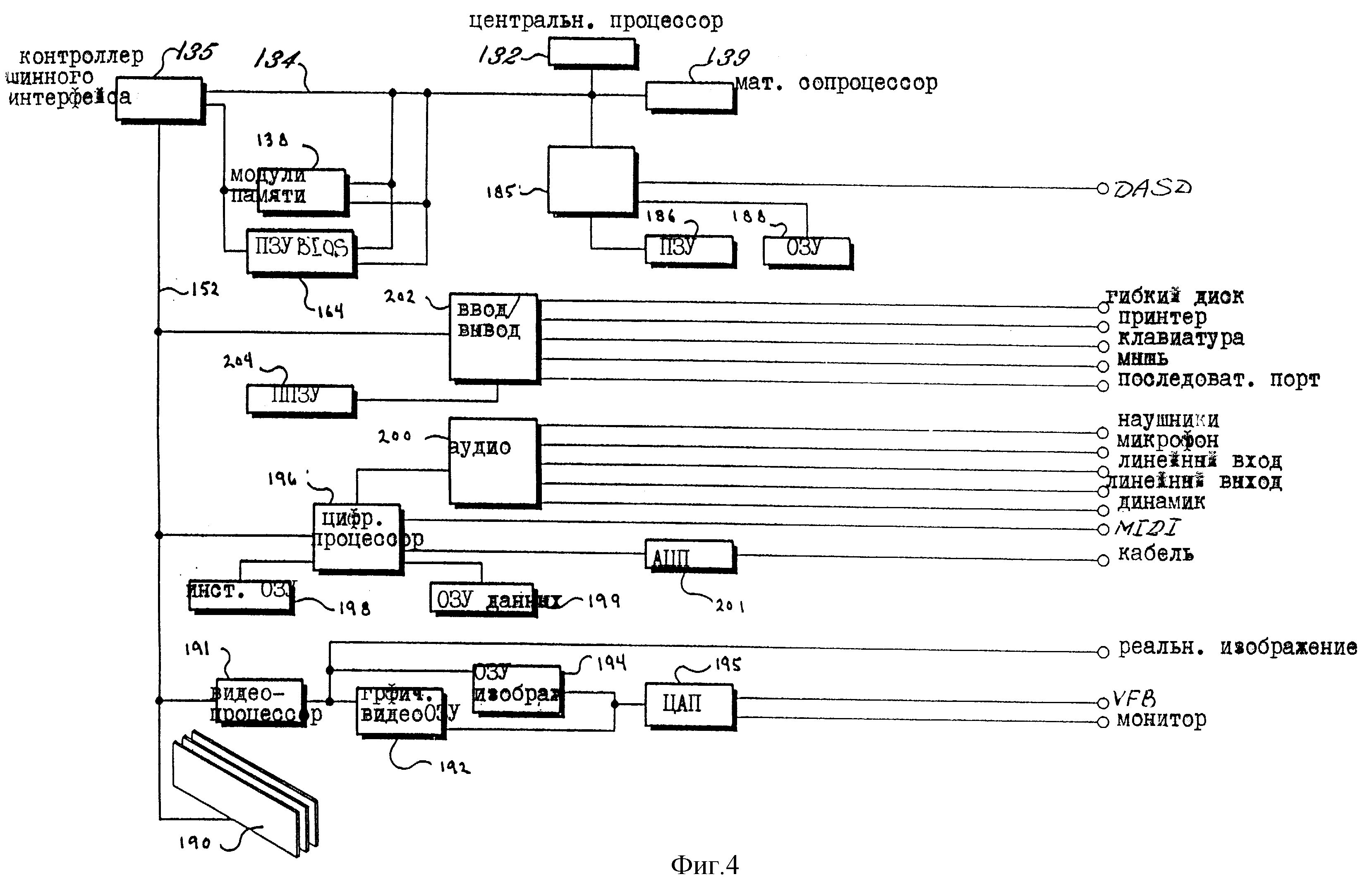

фиг. 4 - схематическое изображение альтернативного расположения элементов персонального компьютера на фигурах 1 и

2, иллюстрирующее другую конфигурацию этих элементов;

фиг. 5 - блок-схема некоторых рабочих операций, выполняемых при реализации настоящего изобретения с использованием персональных

компьютеров на фигурах с 1 по 4;

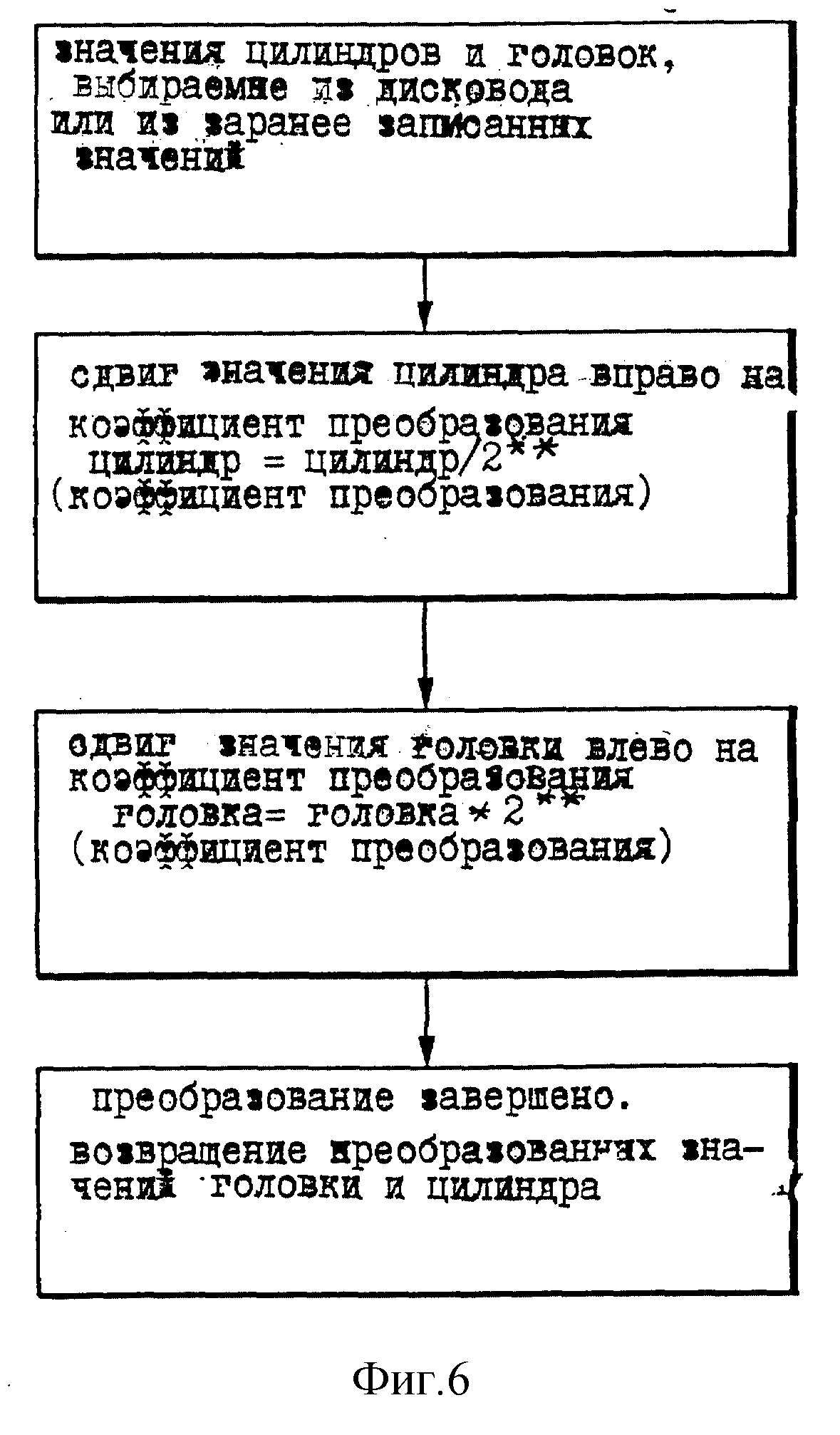

фиг. 6 - блок-схема ряда других рабочих операций, выполняемых при реализации настоящего изобретения с использованием персональных компьютеров на фигурах с 1

по 4; и

фиг. 7 - блок-схема ряда еще одних рабочих операций, выполняемых при реализации настоящего изобретения с использованием персональных компьютеров на фигурах с 1 по 4.

Описание примерных вариантов реализации

Хотя настоящее изобретение будет описано здесь более подробно со ссылками на сопроводительные чертежи, на которых показан предпочтительный вариант

реализации настоящего изобретения, с самого начала описания должно быть понятно, что специалисты могут модифицировать описанное здесь изобретение, достигая, используя это изобретение, еще более

хороших результатов. Соответственно, должно быть ясно, что последующее описание представляет собой подробное разъяснение, предназначенное для специалистов в соответствующих областях, и не должно

рассматриваться как ограничение настоящего изобретения.

Теперь обратимся более конкретно к сопроводительным чертежам, где показана персональная компьютерная система, обозначенная в целом под номером 10 (фиг. 1), в которой воплощено настоящее изобретение. Как было упомянуто выше, компьютер 10 может иметь монитор 11, клавиатуру 12 и принтер или плоттер 14. Компьютер 10 имеет крышку 15, выполненную из декоративной внешней части 16 (фиг. 2) и внутреннего экрана 18, который связан с корпусом 19, образуя замкнутый экранированный объем для размещения в нем электрических элементов обработки данных и памяти для обработки и хранения цифровых данных. По меньшей мере, некоторые из этих элементов смонтированы на многослойном планаре (planar), или материнской плате 20, которая смонтирована в корпусе 19 и обеспечивает электрическое соединение элементов компьютера 10, содержащего указанные выше, а также другие элементы, такие как дисководы для гибких дисков, различные типы запоминающих устройств прямого доступа, вспомогательные карты, или платы и т.п.

Корпус 19 имеет основание 22, переднюю панель 24 и заднюю панель 25 (фиг. 2). Передняя панель 24 определяет место для, по меньшей мере, одной открытой секции (в показанном варианте для четырех секций) для размещения запоминающего устройства, например дисковода для магнитных или оптических дисков, резервного накопителя на магнитной ленте или т.п. В показанном варианте имеются пара верхних секций 26, 28 и пара нижних секций 29, 30. Одна из верхних секций 26 приспособлена для размещения периферийных дисководов первого размера (например, известные дисководы на 3,5 дюйма), в то время как другая секция 28 приспособлена для размещения дисководов одного из двух размеров на выбор (например, 3,5 и 5,25 дюйма), а нижние секции приспособлены для размещения устройств только одного размера (3,5 дюйма). Одно DASD с фиксированными дисками показано под номером 90 на фиг. 1 и, как известно, в общем случае предназначено для приема, хранения и выдачи данных.

Прежде чем обратиться к вышеуказанной структуре настоящего изобретения, рассмотрим качественно общий принцип действия персональной компьютерной системы 10. Обратимся к фиг. 3, где показана блок-схема первого варианта персональной компьютерной системы, иллюстрирующая различные элементы компьютерной системы, например системы 10 согласно настоящему изобретению, содержащей элементы, смонтированные на плате 20 и связи платы с гнездами ввода/вывода (1/0) и другим аппаратным обеспечением персональной компьютерной системы. Соединенный с платой системный процессор 32 содержит микропроцессор, который соединен высокоскоростной локальной шиной центрального процессора (CPU) 34 через блок шинной синхронизации 35 с блоком управления памятью 36, который, кроме того, подсоединен к энергозависимому оперативному запоминающему устройству (RAM) 38. Хотя можно использовать любой соответствующий процессор, одним из подходящих является процессор 80386, который поставляется фирмой INTEL.

Хотя настоящее изобретение описывается здесь с конкретными ссылками на блок-схемы системы, показанные на фигурах 3 и 4, с самого начала последующего описания должно быть ясно, что рассматриваемое устройство и способы согласно настоящему изобретению могут быть использованы и с другой аппаратной конфигурацией планарной платы. Например, в качестве системного процессора можно использовать микропроцессор 80286 или 80486.

Обратимся теперь к фиг. 3, где локальная магистраль CPU 34 (содержащая шины данных, адресов и управления) предназначена для соединения микропроцессора 32, математического сопроцессора 39, кэш-контроллера 40 и кэш-памяти 41. С локальной магистралью CPU 34 связан также буфер 42. Буфер 42 в свою очередь подсоединен к низкоскоростной (по сравнению с локальной магистралью CPU) системной магистрали 44, также содержащей шины адресов, данных и управления. Системная магистраль 44 проходит между буфером 42 и другими буферами 51, 68. Системная магистраль 44, кроме того, подсоединена к блоку шинного управления и синхронизации 35 и блоку прямого доступа к памяти (DMA) 48. Блок DMA 48 содержит центральный арбитражный блок 49 и контроллер DMA 50. Один буфер 51 обеспечивает интерфейс между системной магистралью 44 и магистралью с произвольными характеристиками, например магистралью ISA 52. К магистрали 52 подсоединено множество 1/0 гнезд 54 для размещения адаптерных плат ISA, которые, кроме того, могут быть соединены с устройством 1/0 или памятью. Шина арбитражного управления 55 соединяет контроллер DMA 50 и центральный арбитражный блок 49 с гнездами 1/0 54 и адаптером дискет 56. К системной магистрали 44 подсоединен также блок управления памятью 36, который содержит контроллер памяти 59, мультиплексор адресов 60 и буфер данных 61. Блок управления памятью 36 подсоединен, кроме того, к оперативному запоминающему устройству, представленному блоком RAM 38. Контроллер памяти 36 содержит логические схемы для преобразования адресов в или из микропроцессора 32 в конкретные области RAM 38. Контроллер памяти 36 генерирует также сигнал выбора ROM (ROMSEL), который используется для включения или отключения ROM 64. Хотя микрокомпьютерная система показана с базовым модулем RAM на 1 мегабайт, понятно, что можно подсоединить дополнительную память, как показано на фиг. 3, с помощью необязательных модулей памяти с 65 по 67.

Буфер защелки 68 подключен между системной магистралью 44 и планарной магистралью 1/0 69. Планарная магистраль 1/0 содержит соответственно шины адресов, данных и управления. Вдоль планарной магистрали 1/0 69 подсоединено множество адаптеров 1/0 и других элементов, таких как адаптер дисплея 70 (который используется для управления монитором 11), тактовый генератор с комплементарной структурой "металл-оксид-полупроводник" (КМОП) 72, энергонезависимая RAM с КМОП-структурой 74, здесь и далее обозначенная как NVRAM, адаптер RS232 76, параллельный адаптер 78, множество таймеров 80, адаптер дискет 56, контроллер прерываний 84 и постоянное запоминающее устройство (только для считывания) 64. Постоянное запоминающее устройство 64 хранит программу управления BIOS, которая используется для интерфейса между устройствами ввода/вывода (1/0) и операционной системой микропроцессора 32. BIOS, хранящаяся в ROM 64, может быть скопирована в RAM 38 для уменьшения времени выполнения BIOS. Кроме того, ROM 64 доступна (с помощью сигнала ROMSEL) контроллеру памяти 36. Если ROM 64 приведено в действие контроллером памяти 36, BIOS выполняется из ROM. Если ROM 64 не задействовано контроллером памяти 36, ROM не реагирует на адресные запросы от микропроцессора 32, (то есть BIOS выполняется из RAM).

Тактовый генератор 72 используется для расчетов текущего времени, a NVRAM используется для хранения данных о конфигурации системы. То есть, NVRAM будет содержать значения параметров, которые описывают существующую конфигурацию системы. Например, NVRAM содержит информацию, описывающую емкость фиксированного диска или дискеты, тип дисплея, объем памяти, время, дату и т.п. Особенно важно, что NVRAM будет содержать данные (может быть один бит), которые используются контроллером памяти 36 для определения того, выполняется ли BIOS из ROM или из RAM, и того, возвращаться ли к RAM, предназначенную для использования BIOS RAM. Кроме того, эти данные хранятся в NVRAM всякий раз, когда выполняется специальная программа конфигурации, например, SET Configuration. Назначение программы SET Configuration - записывать в NVRAM значения, характеризующие конфигурацию системы.

Как было замечено выше, компьютер имеет крышку, обозначенную в целом под номером 15, которая вместе с корпусом 19 образует замкнутый экранированный объем для размещения вышеуказанных элементов микрокомпьютера. Крышка предпочтительно выполняется с внешним декоративным верхом 16, который представляет собой прессованное изделие, выполненное из прессуемого синтетического материала, и тонкой металлической прокладки 18, форма которой соответствует конфигурации декоративного верха крышки. Однако крышка может быть выполнена и другими известными способами, и полезность этого изобретения не сводится к корпусам описанного типа.

Альтернативная структура персонального компьютера ISA представлена на фиг. 4, где показана блок-схема персональной компьютерной системы, иллюстрирующая различные элементы альтернативной структуры компьютерной системы, например системы 10, согласно настоящему изобретению. При идентификации элементов, показанных на фиг. 4, которые функционально подобны элементам, описанным выше со ссылками на фиг. 3, можно использовать аналогичные цифровые ссылки, начинающиеся со 100. Например, микропроцессор 132, показанный на фиг. 4, в общем случае функционально подобен микропроцессору 32 на фиг. 3. CPU 132 подсоединен с помощью высокоскоростной локальной магистрали CPU 134 к блоку управления шинным интерфейсом 135, к энергозависимому оперативному запоминающему устройству (RAM) 138, представленному здесь в виде модулей с однорядным расположением микросхем памяти (SIMM), и к BIOS ROM 164, в котором хранятся команды для базовых операций ввода/вывода в CPU 132. BIOS ROM 164 содержит BIOS, которая используется для интерфейса между устройствами ввода/вывода и операционной системой микропроцессора 132. Команды, хранящиеся в ROM 164, могут быть скопированы в RAM 138 для уменьшения времени выполнения BIOS.

Локальная магистраль CPU 134 (содержащая шины данных, адресную и управления) предназначена также для соединения микропроцессора 132 с математическим сопроцессором 139 и контроллером DASD 185. Контроллер DASD 185, как известно специалистам в области разработки и эксплуатации компьютеров, может быть соединен (или пригоден к подсоединению) с постоянным запоминающим устройством (ROM) 186, RAM 188 и соответствующими внешними устройствами различных типов, для которых предусмотрены соединения 1/0, указанные на фигуре справа.

Контроллер шинного интерфейса (BIC) 135 соединяет локальную магистраль CPU 134 с магистралью 1/0 152. Посредством магистрали 152 BIC 135 соединяется с магистралью с произвольными характеристиками, например магистралью ISA, имеющей множество гнезд 1/0 для размещения адаптерных плат 190, которые могут быть, кроме того, подсоединены к устройству 1/0 или памяти (не показано). Магистраль 1/0 152 содержит адресную шину, шины данных и управления.

Вдоль шины 1/0 152 подсоединено множество устройств ввода/вывода, таких как видеопроцессор 191, который связан с видеоRAM (VRAM) для хранения графической информации (смотри ссылку 192) и для хранения информации об изображениях (смотри ссылку 194). Видеосигналы, обмен которыми осуществляется с помощью процессора 191, могут проходить через цифро-аналоговый преобразователь (DAC) 195 на монитор или другое устройство отображения. Также предусмотрена возможность соединения VSP 191 непосредственно с так называемыми устройствами ввода/вывода натуральных изображений, к которым относятся видеомагнитофон/плейер, камера и т.п. Магистраль 1/0 152 подключена также к цифровому процессору (DSP) 196, который связывает RAM команд 198 и RAM данных 199, предусмотренных для хранения программных команд для обработки сигналов с помощью DSP 196 и данных, подлежащих такой обработке. DSP 196 предназначен для обработки входных и выходных аудиосигналов, подаваемых от аудиоконтроллера 200, и для обработки других сигналов, подаваемых от контроллера аналогового интерфейса 201. И, наконец, магистраль 1/0 152 связана с контроллером ввода/вывода 202 (с электрически стираемым программируемым постоянным запоминающим устройством (EEPPOM) 204), посредством которого производится обмен входными и выходными сигналами с известными периферийными устройствами, такими как накопители на гибких дисках, принтер или плоттер 14, клавиатура 12, мышь или координатно-указательное устройство, а также через последовательный порт.

В любом из описанных к данному моменту альтернативных вариантов конфигурации персонального компьютера используемое DASD может иметь количество цилиндров и головок, не выходящее за пределы, предполагаемые схемой Прерывания 13. То есть количество цилиндров может быть 1024 или менее, а количество головок - 256 или менее. В этом случае имеет место обычная работа персональной компьютерной системы, заключающейся в опросе DASD относительно его характеристик, запоминании этой информации как части системной конфигурации и работе системы в нормальном режиме, хорошо известном специалистам. Такое функционирование с DASD, которое, в действительности, имеет шестнадцать головок (как обычно имеет место для DASD) приводит к ограничению емкости памяти DASD, имеющейся в наличии для CHS адресации, до пятисот двадцати восьми миллионов четырехсот восьмидесяти двух тысяч трехсот четырех байт цифровых данных.

Важным отличительным признаком настоящего изобретения является то, что CHS адресация, которая находится в пределах, предполагаемых схемой Прерывания 13, используется для адресации ATA DASD, которое имеет количество цилиндров, превышающее 1024, шестнадцать головок и емкость памяти для цифровых данных, которая превышает пятьсот двадцать восемь миллионов четыреста восемьдесят две тысячи триста четыре байта цифровых данных. Это выполняется согласно настоящему изобретению посредством проведения трансляции между справочными кадрами для CHS адресации.

Согласно настоящему изобретению создается первый справочный кадр для CHS адресации, имеющий количество цилиндров, которое превышает одну тысячу двадцать четыре и количество головок, соответствующее действительному количеству головок, находящихся в дисководе, подлежащем подключению и адресации. Как было отмечено, это количество обычно составляет шестнадцать головок для дисководов того типа, которые встречались в то время, когда это изобретение было воплощено в реально эксплуатируемых персональных компьютерных системах. Однако количество головок может быть любым заданным числом, отличным от шестнадцати, которое может выбрать и использовать разработчик DASD. Первый справочный кадр соответствует машинным характеристикам используемого DASD.

Также создается второй справочный кадр для CHS адресации, причем второй кадр имеет количество цилиндров и головок, которые соответствуют предполагаемым параметрам схемы Прерывания 13. То есть второй справочный кадр имеет не более 1024 цилиндров и не более 256 головок.

Настоящее изобретение предполагает, что данные CHS адресации, которыми обмениваются два кадра, транслируются для разрешения обмена данных с использованием всей емкости памяти подключенного DASD. Эта трансляция выполняется посредством установления конкретного соотношения между адресацией в первом справочном кадре и адресацией во втором справочном кадре.

Последующие рассуждения относятся к способу создания двух справочных кадров и выполнения трансляции между ними. Однако в качестве преамбулы необходимо отметить, что, как здесь полагается, такое создание кадров и трансляция между ними будет полезной для различных вариантов управления DASD, с которыми можно столкнуться на практике. В частности, настоящее изобретение можно использовать с DASD, которое управляется с помощью платы контроллера, смонтированной в шинном разъеме 1/0; c DASD типа IDE и с DASD, которое непосредственно адресуется под управлением системного CPU 32, 132. Необходимо отметить, что в каждом варианте имеется микропроцессор, который функционирует с использованием CHS адресации. В варианте комбинации DASD /плата контроллера микропроцессор адресации обычно расположен на плате. В варианте IDE DASD микропроцессор адресации обычно интегрирован в DASD. В варианте, когда DASD управляется непосредственно системным CPU, микропроцессор и есть системный CPU. Кроме того, в каждом варианте имеется записанная управляющая программа, которая доступна микропроцессору, загружается в микропроцессор и которая с помощью микропроцессора выполняет адресацию. Эту управляющую программу, как и здесь, часто называют базовой системой ввода/вывода, или она может быть частью такой системы, известной как BIOS. BIOS для персональной компьютерной системы может содержать главную BIOS, на которую ссылались при описании конфигурации системы, показанной на фигурах 3 или 4; или часть BIOS, которая может, например, храниться на некоторой дополнительной плате, например, контроллера DASD; или BIOS устройства, которая может, например, храниться как часть IDE DASD; или часть главной BIO, описанной ранее. Настоящее изобретение предполагает, что упомянутая здесь управляющая программа может быть любой из этих различных типов.

В любом случае, как предполагается согласно настоящему изобретению, система имеет запоминающее устройство прямого доступа (DASD)) с поворачивающимися носителями 90 для приема, хранения и выдачи цифровых данных. DASD имеет первое заданное число цилиндров и второе заданное число головок, причем каждый цилиндр разделен на третье заданное число секторов. Как будет понятно, дорожки обмениваются цифровыми данными с секторами цилиндров, записывая их на или считывая их с секторов под управлением сигналов CHS адресации. Согласно настоящему изобретению цилиндры, головки и сектора образуют вместе емкость памяти для DASD, превышающую пятьсот двадцать восемь миллионов четыреста восемьдесят две тысячи триста четыре байта цифровых данных.

Как было указано выше, система имеет микропроцессор для обработки цифровых сигналов, причем микропроцессор управляет обменом цифровых данных с DASD, используя данные адресации памяти "цилиндр-головка-сектор". Система также имеет управляющую программу, доступную микропроцессору, для управления потоком цифровых данных в и из DASD. В процессе работы микропроцессор осуществляет доступ к управляющей программе, загружает управляющую программу и, работая под управлением управляющей программы, выполняет последовательность операций, которые разрешают обмен данными со всей емкостью памяти DASD.

Выполняемые

операции включают создание первого и второго справочных кадров, упомянутых выше, и затем трансляцию между ними. Перед созданием справочных кадров система определяет коэффициент преобразования, который

будет использоваться, выполняя шаги, показанные на фиг. 5. Эти шаги содержат запрос относительно количества цилиндров, имеющихся в DASD, затем определение того, больше ли количество цилиндров, чем

шестнадцать тысяч триста восемьдесят четыре. Последнее число - это тот максимум, который может быть адресован в конкретном, описанном здесь варианте реализации, и это число может быть другим, если

вариант реализации отличается от здесь описанного. Если количество цилиндров больше, тогда число шестнадцать тысяч триста восемьдесят четыре используется для последующих шагов. Если нет, то тогда

используется сообщенное число. На следующем шаге устанавливается в нулевое значение регистр, используемый для хранения коэффициента преобразования. Затем определяется, больше ли количество цилиндров,

чем одна тысяча двадцать четыре, то есть верхнего предела, устанавливаемого схемой прерывания 13, как было описано выше. Если число равно или меньше одной тысячи двадцати четырех, то тогда регистр

коэффициента преобразования оставляется в нулевом состоянии и в преобразовании нет необходимости. Если это число больше, чем тысяча двадцать четыре, тогда число цилиндров делится на два.

Предпочтительный способ выполнения деления состоит в использовании команды "Shift Right" ("сдвиг вправо"). Вслед за делением следует приращение на единицу состояния регистра коэффициента

преобразования. Затем процесс возвращается к запросу относительно числа цилиндров, определенного как частное от предшествующего деления; деления на два этого частного, если оно больше, чем тысяча

двадцать четыре; приращения на единицу содержимого регистра коэффициента преобразования; и повторения деления/приращения, пока частное от деления числа цилиндров не станет меньше одной тысячи двадцати

четырех. В тот момент, когда частное от деления становится меньше, чем одна тысяча двадцать четыре, содержимое регистра представляет собой коэффициент преобразования (обозначаемый здесь и далее как

"N"), который и используется в дальнейшем. Там, где это подходит, коэффициент преобразования может храниться как часть данных о конфигурации системы, содержащихся в NVRAM. Определив коэффициент

преобразования, можно создать вышеупомянутые справочные кадры. Один такой кадр устанавливается процедурой получения параметров дисковода DASD, как показано на фиг. 6. Как видно из фигуры, значения для

цилиндров и головок выбираются из DASD или из предварительно записанных значений путем запроса. Затем номер цилиндра преобразуется с использованием коэффициента преобразования путем деления номера

цилиндра на два (делитель в ранее описанном процессе определения коэффициента преобразования) в степени "коэффициент преобразования". Или, если объяснить это преобразование по-другому, номер цилиндра

сдвигается вправо на коэффициент преобразования. Алгоритмически это выражается как

Converted Cylinder (преобразованный цилиндр) = Cylinder (цилиндр)/2 N

Затем осуществляется

преобразование номера головки с использованием коэффициента преобразования путем умножения номера головки на два в степени "коэффициент преобразования" (или сдвиг номера головки влево на коэффициент

преобразования). Алгоритмически это выражается как

Converted Head (преобразованная головка) = Head (головка)•2N

В этот момент преобразование заканчивается и преобразованные

номера цилиндров и головок возвращаются для использования при CHS адресации DASD.

Следует отметить, что DASD имеет целое число цилиндров и не может иметь дробного числа цилиндров. Любой дробный цилиндр, который, в противном случае, мог бы появиться при преобразовании, отбрасывается. То есть, дисковод с двумя тысячами одним цилиндром и шестнадцатью головками будет записан как имеющий тысячу цилиндров и тридцать две головки. Половина цилиндра BIOS "теряется". Если такое DASD адресуется через BIOS с использованием ограничений схемы Прерывания 13 к головке 20 цилиндра O, в машинном DASD будет обращение к головке 4 цилиндра 1.

Для примера предположим, что система снабжена DASD, которое имеет две тысячи цилиндров и шестнадцать головок с общей возможной емкостью памяти десять миллиардов сто четыре миллиона сто девяносто две тысячи байт цифровых данных (2000х16х63х512). Коэффициент преобразования будет равен единице (одно деление 2000 на 2 дает частное 1000, что меньше, чем 1024).

Второй справочный кадр устанавливается самим DASD, как имеющим предел числа цилиндров больше тысячи двадцати четырех и предел числа головок, не превышающий заданное, а именно, имеющееся число головок в машинном дисководе. В рассмотренном выше примере (как и для большинства ATA DASD) это число равно шестнадцати.

Трансляция

между двумя справочными кадрами происходит, как показано на фиг. 7, посредством функционирования управляющей программы с помощью микропроцессора, как было описано выше. В частности, трансляция

цифровых данных об адресах памяти, которыми обмениваются первый и второй справочные кадры для разрешения обмена данных с использованием всей емкости памяти указанного DASD, выполняется с

использованием числа (N) повторившихся делений на два количества цилиндров. Согласно такой трансляции, сначала запрашиваются хранящиеся данные, чтобы определить, отличается ли от нуля записанный

коэффициент преобразования. Если он равен нулю, то тогда преобразование не требуется и CHS адресация происходит так, как это предусмотрено исходной схемой Прерывания 13. Если он больше нуля, то тогда

номер цилиндра в команде дисковода умножается на два в степени "коэффициент преобразования (N)". Алгоритмически это выражается как

Translated Cylinder (транслированный цилиндр) = Converted

Cylinder (преобразованный цилиндр)•2N

Затем преобразованный номер головки делится на число головок, реально существующих в DASD, а остаток от этого деления определяется как

транслированный номер головки. Затем частное от этого деления подвергается логической операции "ИЛИ" вместе с транслированным номером цилиндра и определяется как адресуемый номер цилиндра.

Как было отмечено выше, такое определение коэффициента преобразования, само преобразование и трансляция могут выполняться либо как функция системной BIOS во взаимодействии с системным CPU; как функция BIOS платы контроллера во взаимодействии с микропроцессором контроллера; или как функция IDE BIOS во взаимодействии с микропроцессором IDE. Во всех случаях эффект трансляции тот же самый: CHS адрес в первом справочном кадре, который наталкивается на ограничение схемы Прерывания 13 в ISA BIOS, транслируется в CHS адрес во втором справочном кадре, который имеет дело с физическими характеристиками DASD, который, в противном случае, вышел бы за пределы ограничений схемы Прерывания 13 в ISA BIOS.

В чертежах и описании был изложен предпочтительный вариант реализации изобретения, и, хотя использовались конкретные термины, данное описание использует терминологию только в обобщенном и описательном смысле, а не с целью ограничения.

Реферат

Изобретение относится к трансляции адресации "цилиндр-головка-сектор" (ЦГС) цифровых данных, записываемых в или считываемых из ЗУПД. Техническим результатом является приспособление использования емкостей ЗУПД, превышающих ограничение на емкость примерно пятьсот двадцать восемь мегабайт, накладываемое схемой "Прерывания 13" в персональной компьютерной системе промышленного стандарта архитектуры (ПСА) ЗУПД, который достигается тем, что цилиндр-головка-сектор (ЦГС) адрес в первом справочном кадре, подвергающийся ограничениям схемы "Прерывания 13" в ПСА базовой системы ввода (вывода), транслируется в ЦГС адрес во втором справочном кадре, подвергающийся ограничениям физических характеристик ЗУПД. 2 с. и 19 з.п.ф-лы, 7 ил.