Процессор с плавающей запятой с пониженной потребляемой мощностью для выбираемой субточности - RU2412462C2

Код документа: RU2412462C2

Чертежи

Описание

Уровень техники

Процессоры с плавающей запятой представляют собой специализированные вычислительные блоки, которые выполняют некоторые математические операции, например умножение, деление, тригонометрические функции и экспоненциальные функции, с высокой скоростью. Следовательно, мощные вычислительные системы часто включают в себя процессоры с плавающей запятой или как часть основного процессора, или как сопроцессор. Представление числа в виде числа с плавающей запятой обычно включает в себя составляющую знака, экспоненту и мантиссу. Чтобы найти значение числа с плавающей запятой, мантисса умножается на основание (обычно 2 в компьютерах), возведенное в степень экспоненты. К результирующему значению применяется знак.

Точность процессора с плавающей запятой определяется количеством разрядов, используемых для представления мантиссы. Чем больше разрядов в мантиссе, тем больше точность. Точность процессора с плавающей запятой, как правило, зависит от конкретного применения. Например, стандарт ANSI/IEEE-754 (Американского национального института стандартов и Института инженеров по электротехнике и радиоэлектронике) (которому обычно следуют современные компьютеры) задает 32-разрядный одинарный формат, имеющий 1-разрядный знак, 8-разрядную экспоненту и 23-разрядную мантиссу. Только 23 разряда дробной части мантиссы сохраняются при 32-разрядном кодировании, разряд целого числа, непосредственно слева от двоичной запятой, подразумевается. Стандарт IEEE-754 также задает 64-разрядный двойной формат, имеющий 1-разрядный знак, 11-разрядную экспоненту и 53-разрядную мантиссу. Аналогично одинарному кодированию только 52 разряда дробной части мантиссы сохраняются при 64-разрядном кодировании, разряд целого числа, непосредственно слева от двоичной запятой, подразумевается. Более высокая точность приводит к более высокой правильности, но обычно приводит к повышенной потребляемой мощности.

Выполнение арифметических операций с плавающей запятой может вызывать неэффективность вычислений, так как процессоры с плавающей запятой обычно ограничиваются точностью, обеспечиваемой или одинарным форматом, или как одинарным, так и двойным форматом. Хотя некоторые применения могут требовать эти типы точности, другие применения могут их не требовать. Например, некоторые графические применения могут требовать только 16-разрядную мантиссу. Для этих графических применений любая точность свыше 16 разрядов точности имеет тенденцию приводить к необязательному расходу мощности. Это имеет особое значение в устройствах с батарейным питанием, где мощность имеет первостепенное значение, таких как беспроводные телефоны, персональные цифровые помощники (PDA), портативные компьютеры, игровые консоли, пейджеры и камеры (в качестве примера приводятся только некоторые). Известно, что применение всегда требует некоторую пониженную точность, процессор с плавающей запятой может быть спроектирован и построен с этой пониженной точностью. Для процессоров общего назначения, однако, обычной ситуацией является то, что для некоторых применений, например генерирования трехмерной графики, может быть приемлемой пониженная точность, и для других применений, например реализации функций глобальной системы определения местоположения (GPS), может требоваться более высокая точность. Следовательно, в технике существует потребность в процессоре с плавающей запятой, в котором выбирается пониженная точность, или субточность, формата с плавающей запятой. Также могут применяться методы управления мощностью, чтобы гарантировать, что процессор с плавающей запятой не потребляет больше мощности, чем необходимо для поддержки выбранной субточности.

Сущность изобретения

Описывается аспект способа выполнения операции с плавающей запятой при помощи процессора с плавающей запятой, имеющего формат точности. Способ включает в себя выбор субточности для операции с плавающей запятой над одним или несколькими числами с плавающей запятой, причем выбор субточности приводит к одному или нескольким избыточным разрядам для каждого из одного или нескольких чисел с плавающей запятой. Способ дополнительно включает в себя снятие питания с одного или нескольких компонентов в процессоре с плавающей запятой, которые иначе использовались бы для хранения или обработки одного или нескольких избыточных разрядов, и выполнение операции с плавающей запятой со снятым питанием с одного или нескольких компонентов.

Описывается один аспект процессора с плавающей запятой, имеющего формат точности. Процессор с плавающей запятой включает в себя контроллер с плавающей запятой, выполненный с возможностью выбора субточности для операции с плавающей запятой над одним или несколькими числами с плавающей запятой, причем выбор субточности приводит к одному или нескольким избыточным разрядам для каждого из одного или нескольких чисел с плавающей запятой, при этом контроллер с плавающей запятой дополнительно выполнен с возможностью снятия питания с одного или нескольких компонентов в процессоре с плавающей запятой, которые иначе бы использовались для хранения или обработки одного или нескольких избыточных разрядов. Процессор с плавающей запятой дополнительно включает в себя оператор с плавающей запятой, выполненный с возможностью выполнения операции с плавающей запятой.

Описывается другой аспект процессора с плавающей запятой, имеющего формат точности. Процессор с плавающей запятой включает в себя регистр с плавающей запятой, имеющий множество запоминающих элементов, выполненных с возможностью хранения множества чисел с плавающей запятой, и оператор с плавающей запятой, выполненный с возможностью выполнения операции с плавающей запятой над одним или несколькими числами с плавающей запятой, хранимыми в регистре с плавающей запятой. Процессор с плавающей запятой дополнительно включает в себя контроллер с плавающей запятой, выполненный с возможностью выбора субточности для операции с плавающей запятой над упомянутым одним или несколькими числами с плавающей запятой, причем выбор субточности приводит к одному или нескольким избыточным разрядам для каждого из упомянутого одного или нескольких чисел с плавающей запятой, один или несколько избыточных разрядов сохраняются в одном или нескольких запоминающих элементах регистра с плавающей запятой, и в котором контроллер с плавающей запятой дополнительно выполнен с возможностью снятия питания с запоминающих элементов для одного или нескольких избыточных разрядов.

Описывается другой аспект процессора с плавающей запятой, имеющего формат точности. Процессор с плавающей запятой включает в себя регистр с плавающей запятой, выполненный с возможностью хранения множества чисел с плавающей запятой, и оператор с плавающей запятой, имеющий логику, выполненную с возможностью выполнения операции с плавающей запятой над одним или несколькими числами с плавающей запятой, хранимыми в регистре с плавающей запятой. Процессор с плавающей запятой дополнительно включает в себя контроллер с плавающей запятой, выполненный с возможностью выбора субточности для операции с плавающей запятой над упомянутым одним или несколькими числами с плавающей запятой, причем выбор субточности приводит к одному или нескольким избыточным разрядам для каждого из упомянутого одного или нескольких чисел с плавающей запятой, и в котором контроллер с плавающей запятой дополнительно выполнен с возможностью снятия питания с части логики, которая иначе бы использовалась для обработки одного или нескольких избыточных разрядов.

Необходимо понять, что другие варианты осуществления процессора с плавающей запятой и способ выполнения операций с плавающей запятой станут легко очевидными для специалиста в данной области техники из последующего подробного описания, в котором различные варианты осуществления процессора с плавающей запятой и способа выполнения операций с плавающей запятой показаны и описаны посредством иллюстрации. Как станет понятно, возможны другие и различные варианты осуществления процессора с плавающей запятой и способа выполнения операций с плавающей запятой, и подробности, используемые для описания этих вариантов осуществления, могут модифицироваться во многих отношениях. Следовательно, чертежи и подробное описание должны рассматриваться как иллюстративные по своей сущности, а не как ограничительные.

Краткое описание чертежей

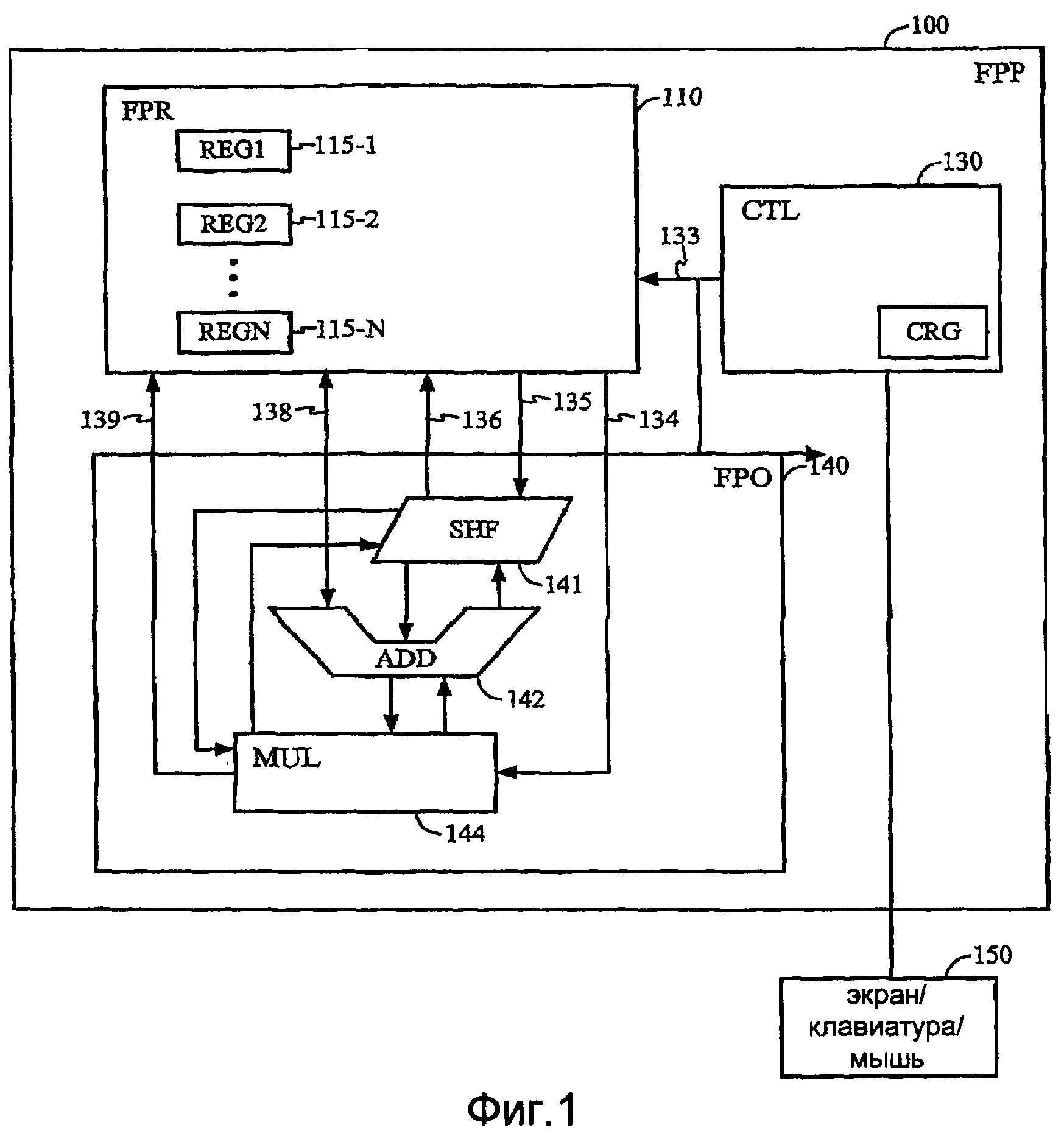

Фиг.1 представляет собой функциональную блок-схему, иллюстрирующую пример процессора с плавающей запятой с выбираемой субточностью;

фиг.2 представляет собой графическую иллюстрацию примера регистрового файла с плавающей запятой, используемого в процессоре с плавающей запятой с выбираемой субточностью;

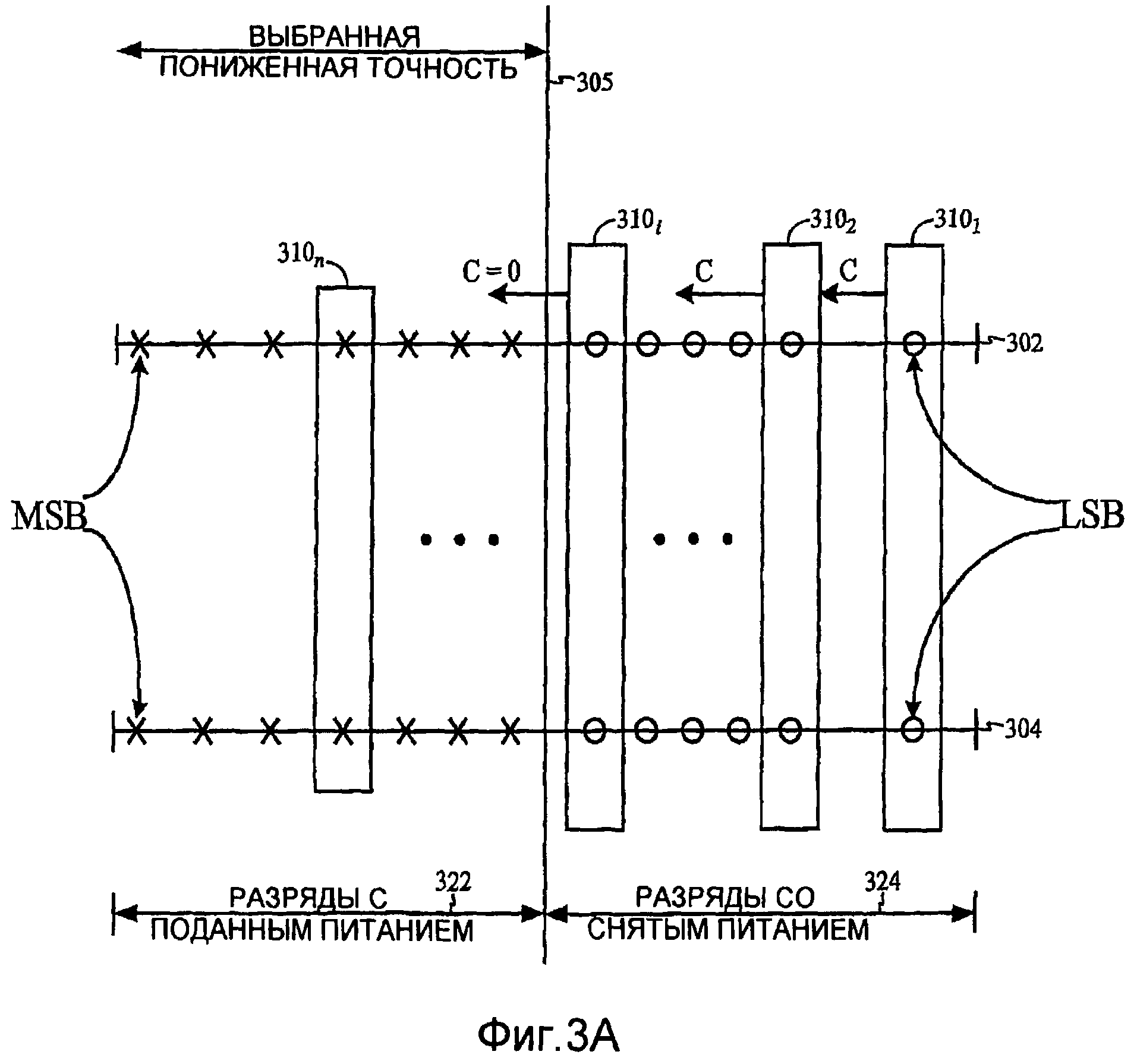

фиг.3А представляет собой концептуальную схему, иллюстрирующую пример сложения с плавающей запятой, выполняемого с использованием процессора с плавающей запятой с выбираемой субточностью; и

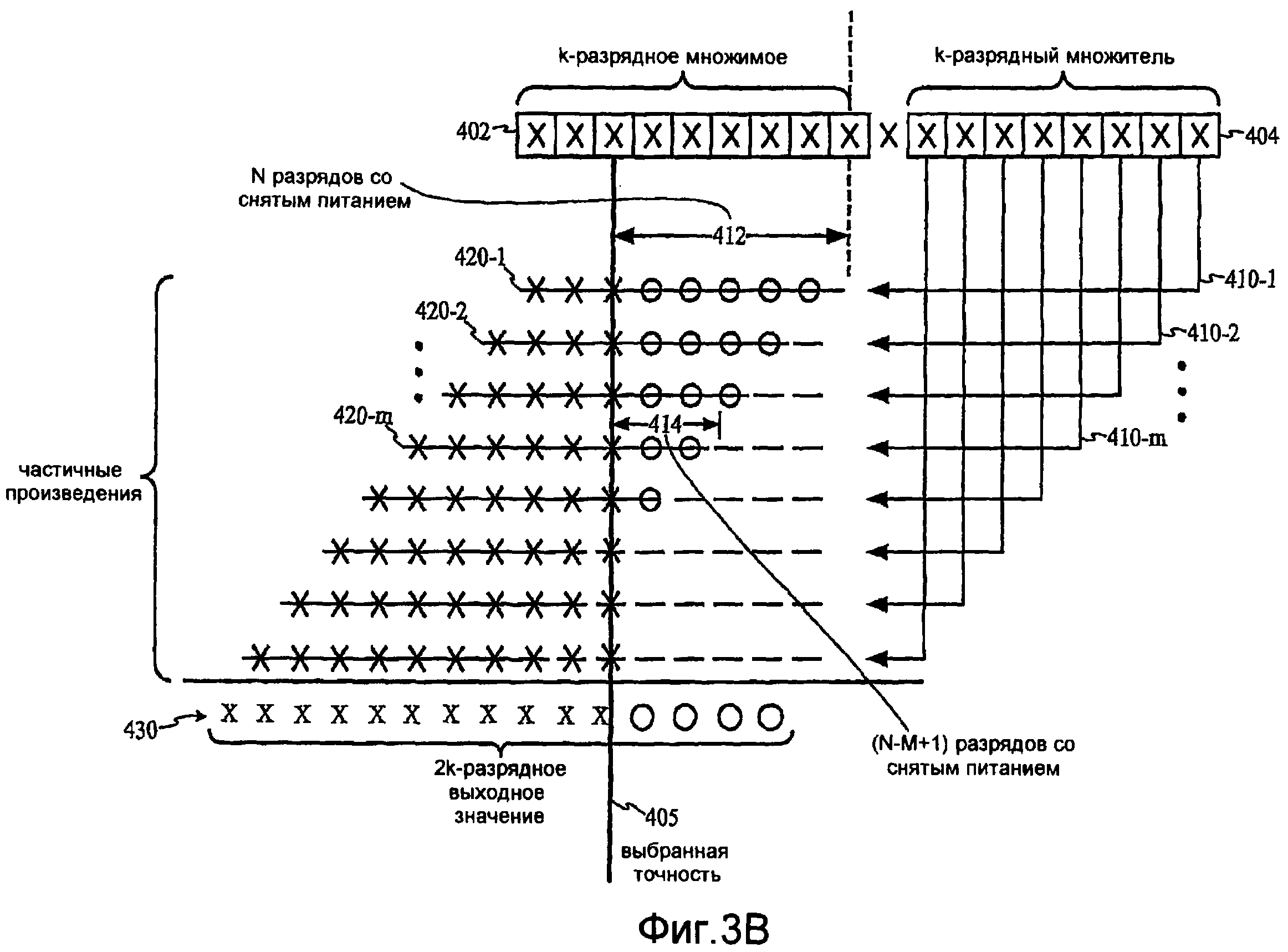

фиг.3В представляет собой концептуальную схему, иллюстрирующую пример умножения с плавающей запятой, которое выполняется с использованием процессора с плавающей запятой с выбираемой субточностью.

Подробное описание

Подробное описание, изложенное ниже в связи с прилагаемыми чертежами, предназначено для описания различных вариантов осуществления настоящего раскрытия, но не предназначено для представления единственных вариантов осуществления, в которых настоящее раскрытие может быть осуществлено на практике. Подробное описание включает в себя конкретные подробности, чтобы обеспечить полное понимание настоящего раскрытия. Специалист в данной области техники примет во внимание, однако, что настоящее раскрытие может быть осуществлено на практике без этих конкретных подробностей. В некоторых случаях общеизвестные конструкции и компоненты показаны в виде блок-схемы, чтобы более ясно иллюстрировать принципы настоящего раскрытия.

По меньшей мере в одном варианте осуществления процессора с плавающей запятой точность для одной или нескольких операций с плавающей запятой может понижаться по сравнению с точностью заданного формата. Кроме того, методы управления мощностью могут применяться для гарантирования того, что процессор с плавающей запятой не потребляет больше мощности, чем необходимо для поддержки выбранной субточности. Инструкции, предусмотренные для процессора с плавающей запятой для выполнения математических операций, могут включать в себя программируемое управляющее поле. Управляющее поле может использоваться для выбора субточности формата с плавающей запятой и управления потребляемой мощностью. Посредством выбора субточности формата с плавающей запятой такой, которая необходима для конкретной операции, таким образом снижая потребление мощности процессора с плавающей запятой для поддержки выбранной субточности, может достигаться большая эффективность, а также существенная экономия мощности.

Фиг.1 представляет функциональную блок-схему, иллюстрирующую пример процессора 100 с плавающей запятой (FPP) с выбираемой субточностью. Процессор 100 с плавающей запятой включает в себя регистровый файл 110 с плавающей запятой (FPR); контроллер 130 с плавающей запятой (CTL) и математический оператор 140 с плавающей запятой (FPO). Процессор 100 с плавающей запятой может быть реализован как часть основного процессора, как сопроцессор или как отдельный объект, подсоединенный к основному процессору при помощи шины или другого канала.

Регистровый файл 110 с плавающей запятой может представлять собой любую подходящую запоминающую среду. В варианте осуществления, показанном на фиг.1, регистровый файл 110 с плавающей запятой включает в себя несколько адресуемых регистровых ячеек 115-1 (REG1), 115-2 (REG2), … 115-N (REGN), причем каждая выполнена с возможностью хранения операнда для операции с плавающей запятой. Операнды могут включать в себя, например, данные из памяти и/или результаты предыдущих операций с плавающей запятой. Инструкции, предоставляемые процессору с плавающей запятой, могут использоваться для перемещения операндов в основную память и из нее.

Фиг.2 схематически иллюстрирует пример структуры данных для регистрового файла 110 с плавающей запятой, используемого в процессоре 100 с плавающей запятой с выбираемой субточностью, как описано в связи с фиг.1. В варианте осуществления, изображенном на фиг.2, регистровый файл 110 с плавающей запятой включает в себя шестнадцать адресуемых регистровых ячеек, причем на каждую регистровую ячейку ссылка выполняется посредством позиции 200 на фиг.2 для удобства. Каждая регистровая ячейка 200 выполнена с возможностью хранения 32-разрядного двоичного числа с плавающей запятой в 32-разрядном единичном формате стандарта IEEE-754. В частности, каждая ячейка 200 регистра содержит 1-разрядный знак 202, 8-разрядный порядок 204 и 24-разрядную дробную часть 206. Конечно, необходимо понять, однако, что другие варианты осуществления процессора 100 с плавающей запятой могут включать в себя регистровый файл 110 с плавающей запятой, который форматируется отлично от 32-разрядного одиночного формата стандарта IEEE (включая, но не ограничиваясь 64-разрядным двойным форматом стандарта IEEE), и/или может содержать другое количество ячеек регистра.

Обращаясь обратно к фиг.1, контроллер 130 с плавающей запятой может использоваться для выбора субточности операций с плавающей запятой, используя управляющий сигнал 133. Регистр 137 управления (CRG) может загружаться разрядами выбора субточности, например, передаваемыми управляющим полем одной или несколькими инструкциями. Так, как описано более подробно ниже, разряды выбора субточности могут использоваться контроллером 130 с плавающей запятой для снижения точности операндов. Разряды выбора субточности также могут использоваться для отключения частей процессора 100 с плавающей запятой. В качестве примера разряды выбора субточности могут использоваться для снятия питания с элементов регистра с плавающей запятой для разрядов, которые не требуются для выбранной субточности. Разряды выбора субточности также могут использоваться для снятия питания с логики в операторе 140 с плавающей запятой FPO, которая не используется, когда понижается выбранная субточность. Может использоваться ряд выключателей для снятия и приложения питания к элементам регистра с плавающей запятой и логики в операторе 140 с плавающей запятой. Выключатели, которые могут быть внутренними или внешними по отношению к регистру 110 с плавающей запятой и оператору 140 с плавающей запятой, могут представлять собой полевые транзисторы или любой другой тип переключателей.

Оператор 140 с плавающей запятой может включать в себя один или несколько компонентов, выполненных с возможностью выполнения операций с плавающей запятой. Эти компоненты могут включать в себя, но не ограничиваются ими, вычислительные блоки, такие как сумматор 142 с плавающей запятой (ADD), выполненный с возможностью исполнения инструкций сложения и вычитания с плавающей запятой, и умножитель 144 с плавающей запятой (MUL), выполненный с возможностью исполнения инструкций умножения с плавающей запятой. Как показано на фиг.1, каждый из вычислительных блоков ADD 142 и MUL 144 в операторе 140 с плавающей запятой соединен друг с другом и с регистровым файлом 110 с плавающей запятой таким образом, что позволяет выполнять пересылку операндов между вычислительными блоками, а также между каждым вычислительным блоком и регистровым файлом 110 с плавающей запятой. Оператор с плавающей запятой может быть соединен с регистром с плавающей запятой при помощи индивидуальных соединений 134, 135, 136, 137, 138 и 139, как изображено, или может быть соединен при помощи шины или любого другого подходящего соединения. По меньшей мере в одном варианте осуществления процессора 100 с плавающей запятой выход любого одного из вычислительных блоков (ADD 142 и MUL 144) может быть входом любого другого вычислительного блока. Регистровый файл 110 с плавающей запятой может использоваться для хранения промежуточных результатов, а также результатов, которые выводятся из оператора 140 с плавающей запятой.

Сумматор 142 может быть обычным сумматором с плавающей запятой, выполненным с возможностью выполнения стандартных арифметических операций в формате с плавающей запятой. Умножитель 144 может быть обычным умножителем с плавающей запятой, выполненным с возможностью выполнения умножения с плавающей запятой. Умножитель 144 может осуществлять в качестве примера алгоритм Бута или модифицированный алгоритм Бута и может включать в себя логику генерирования частичного произведения, которая генерирует частичные произведения, и ряд сумматоров с запоминанием переноса, которые суммируют частичные произведения.

Хотя для простоты на фиг.1 показаны только сумматор 142 и умножитель 144, оператор 140 с плавающей запятой также может включать в себя другие вычислительные блоки (не показаны), которые известны в технике и которые выполняются с возможностью исполнения других типов математических операций с плавающей запятой. Эти вычислительные блоки могут включать в себя, но не ограничиваться ими: делитель с плавающей запятой, выполненный с возможностью выполнения инструкций деления с плавающей запятой; блок извлечения квадратного корня с плавающей запятой, выполненный с возможностью выполнения инструкций извлечения квадратного корня с плавающей запятой; экспоненциальный оператор с плавающей запятой, выполненный с возможностью исполнения экспоненциальных инструкций с плавающей запятой; логарифмический оператор с плавающей запятой, выполненный с возможностью выполнения инструкций для вычисления логарифмических функций; и тригонометрический оператор с плавающей запятой, выполненный с возможностью выполнения инструкций для вычисления тригонометрических функций.

Различные варианты осуществления процессора 100 с плавающей запятой могут включать в себя только один, или некоторые, или все из вычислительных блоков, перечисленных выше. Например, каждый из сумматора 142 и умножителя 144 может включать в себя один или несколько общеизвестных обычных субблоков, таких как выравниватели, которые выравнивают входные операнды, нормализаторы, которые сдвигают результат в стандартный формат, и блоки округления, которые округляют результат, основываясь на заданном режиме округления. Общеизвестные схемные элементы, такие как инверторы разрядов, мультиплексоры, счетчики и схемы комбинаторной логики также включены в сумматор 142 и умножитель 144.

Как показано на фиг.1, оператор 140 с плавающей запятой соединен с регистровым файлом 110 с плавающей запятой, так что для каждой инструкции запрашиваемой операции с плавающей запятой соответствующий вычислительный блок, т.е. сумматор 142 или умножитель 144, может принимать из регистрового файла 110 с плавающей запятой один или несколько операндов, хранимых в одной или нескольких ячейках REG1, … REGN регистра.

При приеме операндов из регистрового файла 110 с плавающей запятой один или несколько вычислительных блоков в операторе 140 с плавающей запятой могут исполнять инструкции запрашиваемой операции с плавающей запятой над принятыми операндами с субточностью, выбранной контроллером 130 с плавающей запятой. Выход может посылаться обратно на регистр 110 с плавающей запятой для хранения, как показано на фиг.1.

В варианте осуществления процессора 100 с плавающей запятой выбираемый программным образом режим может использоваться для снижения точности операций с плавающей запятой под программным управлением или, как объяснено выше, инструкции, подаваемые на процессор 100 с плавающей запятой, могут включать в себя программируемое управляющее поле, содержащее разряды выбора субточности. Разряды выбора субточности записываются в регистр 137 управления, который, в свою очередь, управляет длиной в разрядах мантиссы для каждого операнда во время операции с плавающей запятой. Альтернативно разряды выбора субточности могут записываться в регистр 137 управления непосредственно из любого подходящего пользовательского интерфейса, включающего в себя, например, но не ограничиваясь ими, экран монитора / клавиатура или мышь 150, показанные на фиг.1. В другом варианте осуществления процессора 100 с плавающей запятой разряды выбора субточности могут записываться в регистр 137 управления непосредственно из основного процессора или его операционной системы. Регистр 137 управления, который показан в контроллере 130 с плавающей запятой, может постоянно находиться где-то еще в качестве отдельного объекта, интегрированного в другой объект или распределенного по многочисленным объектам.

Разряды выбора субточности могут использоваться для снижения точности операции с плавающей запятой. Это может достигаться различными путями. В одном варианте осуществления контроллер 130 с плавающей запятой может вызывать снятие питания с элементов регистра с плавающей запятой для избыточных разрядов дробной части, которые не требуются для осуществления точности, задаваемой разрядами выбора субточности. В качестве примера, если каждая ячейка в регистровом файле с плавающей запятой содержит 23-разрядную дробную часть, и субточность, необходимая для операции с плавающей запятой, составляет 10 разрядов, причем необходимы только 9 обычно значащих разрядов (MSB) дробной части; скрытый разряд или разряд целого числа составляет десятый. Питание может сниматься с элементов регистра с плавающей запятой для оставшихся 14 разрядов дробной части. Если субточность для одной или нескольких инструкций повышается до 16 разрядов, тогда будут необходимы 15 MSB мантиссы. В последнем случае питание может сниматься с элементов регистра с плавающей запятой для 8 младших значащих разрядов (LSB) дробной части.

Кроме того, не требует питания логика в операторе 140 с плавающей запятой, соответствующая избыточным разрядам мантиссы. Таким образом, может достигаться экономия мощности посредством снятия питания с логики в операторе 140 с плавающей запятой, которая остается неиспользуемой в результате выбранной субточности.

Фиг.3А представляет собой концептуальную схему, иллюстрирующую пример операции сложения с плавающей запятой, причем питание селективно подается на логику в операторе с плавающей запятой. В частности, фиг.3А концептуально иллюстрирует операцию сложения с плавающей запятой с двумя введенными числами 302 и 304 с плавающей запятой, причем каждый характеризуется выбранной субточностью, суммированной вместе. Для простоты предполагается, что два числа 302 и 304 уже были выровнены, так что нет необходимости делать сдвиг. Операция сложения с плавающей запятой в режиме полной точности выполняется посредством последовательности ступеней, ссылка на которые на фиг.3А выполняется позициями 3101, 3102, … 310i … 310n. Согласно стандартному соглашению регистр с плавающей запятой хранит по порядку разряды, которые составляют каждое число, начиная от самого правого LSB до самого левого MSB. Каждая последовательная ступень из ступеней, двигаясь справа налево по фиг.3А, включает в себя разряды, которые имеют увеличенную значимость по сравнению с разрядами, включенными в предыдущие ступени.

В примере, изображенном на фиг.3А, выбранная субточность представлена линией 305. Питание может сниматься с логики, используемой для осуществления каждой ступени справа от линии 305. Выходной сигнал переноса С с последней ступени 310i со снятым питанием обнуляется. Питание подается только на логику, используемую для осуществления каждой ступени слева от линии 305. На фиг.3А разряды, на которые подается питание, представленные активным ступеням оператора с плавающей запятой, показаны как Хs с использованием позиции 322, тогда как разряды, на которые не подано питание, представленные ступеням со снятым питанием, показаны как кружочки с использованием позиции 324.

Фиг.3В представляет собой концептуальную схему, иллюстрирующую пример операции умножения с плавающей запятой, причем питание селективно подается на логику в операторе с плавающей запятой. Операция умножения с плавающей запятой выполняется в умножителе MUL с плавающей запятой, показанном на фиг.1 позицией 144. Именно в умножителе может быть снято питание со значительной части логики, обеспечивая существенную экономию мощности. Двоичное умножение, как изображено на фиг.3В, представляет собой в основном последовательность сложений сдвинутых чисел с плавающей запятой. В изображенном варианте осуществления двоичное умножение выполняется между k-разрядным множимым 402 и k-разрядным множителем 404 с использованием метода сдвига и сложения. Метод сдвига и сложения может быть заменен алгоритмом Бута, или множителем модифицированного алгоритма Бута.

Как и в случае сложения с плавающей запятой, умножение с плавающей запятой выполняется в виде последовательности ступеней, изображенных на фиг.3В как 410-1, … 410-m. Предполагая для простоты, что используется алгоритм Бута, одно частичное произведение генерируется для каждого разряда в множителе 404, причем частичное произведение 420-i генерируется во время соответствующей ступени 410-i. Если значение множителя равно 0, его соответствующее частичное произведение состоит только из 0; если значение разряда равно 1, его соответствующее частичное произведение является копией множимого. Каждое частичное произведение 420-i сдвигается влево как функция разряда множителя, с которым он связан, после чего операция переходит на следующую ступень. Каждое частичное произведение, таким образом, может рассматриваться как сдвинутое число. Частичное произведение, связанное с разрядом 0 в множителе, сдвигается влево на нуль разрядов, и частичное произведение, связанное с разрядом 1, сдвигается влево на один разряд. Частичные произведения или сдвинутые числа 420-i с плавающей запятой суммируются вместе и генерируют выходное значение 430 для умножения.

В варианте осуществления, изображенном на фиг.3В, выбор требуемой пониженной точности контроллером 130 указывается линией 405. Как и в случае со сложением с плавающей запятой, описанным в связи с фиг.3А, питание может быть снято с логики, используемой для осуществления ступеней справа от линии 405. Питание подается только на ступени, которые действительно необходимы для поддержки выбранной субточности, т.е. ступени слева от линии 405. На фиг.3В разряды, представленные логике с поданным питанием, показаны как Xs, тогда как разряды, представленные ступеням с отключенным питанием, показаны в виде кружочков.

Как показано на фиг.3В, для первого частичного произведения 420-1, снимается питание с логики для числа с разрядами N, показанными с использованием позиции 402. Для второго частичного произведения снимается питание с логики для N-1 разрядов и т.д. Для m-го частичного произведения или сдвинутого числа 420-m с плавающей запятой снимается питание с логики для числа (N-m+1) разрядов, показанных с использованием позиции 414. Число разрядов N выбирается так, что это не оказывает неблагоприятного влияния на точность оставшихся ступеней.

Выходное значение, которое является результатом умножения с плавающей запятой, описанного выше, имеет длину (т.е. количество разрядов), которая равна сумме длин двух входных значений 402 и 404, которые перемножаются. Выходное значение 430 может быть усечено до выбранной субточности, т.е. любые разряды выходного значения 430, которые по минимуму, до которого может быть усечена выбранная точность, генерируют усеченное выходное число, характеризуемое выбранной точностью. Альтернативно выходное значение 430 может быть округлено до выбранной точности. В обоих случаях также может сниматься питание с выходных разрядов, которые являются менее значащими, чем выбранная точность.

Различные иллюстративные логические узлы, блоки, модули, схемы, элементы и/или компоненты, описанные в связи с вариантами осуществления, раскрытыми в данном документе, могут быть реализованы или выполнены в процессоре с плавающей запятой, который является частью процессора общего назначения, процессора цифровых сигналов (DSP), специализированной интегральной схемы (ASIC), программируемой вентильной матрицы (FPGA) или другого программируемого логического компонента, дискретного вентиля или транзисторной логики, дискретных аппаратных компонентов или любой их комбинации, предназначенной для выполнения функций, описанных в данном документе. Процессором общего назначения может быть микропроцессор, но в альтернативе, процессор может быть любым обычным процессором, контроллером, микроконтроллером или конечным автоматом. Процессор также может быть реализован в виде комбинации вычислительных компонентов, например комбинации DSP и микропроцессора, множества микропроцессоров, одного или нескольких микропроцессоров совместно с ядром DSP или любой другой такой конфигурации.

Способы или алгоритмы, описанные в связи с вариантами осуществления, раскрытыми в данном документе, могут быть реализованы непосредственно аппаратными средствами, программным модулем, исполняемым процессором, или их комбинацией. Программный модуль может постоянно находиться в памяти RAM, флэш-памяти, памяти ROM, памяти EPROM, памяти EEPROM, регистрах, на жестком диске, съемном диске, компакт-диске или в запоминающей среде любого другого вида, известного в технике. Запоминающая среда может быть связана с процессором, так что процессор может считывать информацию с запоминающей среды и записывать информацию в нее. В альтернативном варианте запоминающая среда может быть интегрирована в процессор.

Предшествующее описание раскрытых вариантов осуществления предусмотрено для того, чтобы предоставить возможность любому специалисту в данной области техники выполнить или использовать настоящее раскрытие. Различные модификации этих вариантов осуществления очевидны для специалиста в данной области техники, и обобщенные принципы, определенные в данном документе, могут быть применены к другим вариантам осуществления без отступления от сущности или объема раскрытия. Таким образом, настоящее раскрытие не предназначено для ограничения вариантами осуществления, показанными в данном документе, но оно должно соответствовать полному объему, совместимому с формулой изобретения, причем предполагается, что ссылка на элемент в единственном числе не означает «один и только один», если не указано специально так, но скорее «один или несколько». Все конструктивные и функциональные эквиваленты элементам различных вариантов осуществления, описанных во всем этом раскрытии, которые известны или станут известными для специалиста в данной области техники, точно включены в данный документ по ссылке и, как предполагается, охватываются формулой изобретения. Кроме того, предполагается, что ничто, описанное в данном документе, не делает его всеобщим достоянием, безотносительно к тому, указано ли в явной форме такое раскрытие в формуле изобретения. Элемент формулы изобретения не должен толковаться по положению Раздела 35 Кодекса законов США, §112, шестой абзац, если только элемент не указывается в явной форме с использованием фразы «средство для» или, в случае формулы изобретения на способ, элемент не указывается с использованием фразы «этап для».

Реферат

Группа изобретений относится к способу и устройствам для выполнения операции с плавающей запятой при помощи процессора с плавающей запятой, имеющего заданную точность. Техническим результатом является снижение потребляемой мощности процессора. Способ выполнения операции с плавающей запятой процессором с плавающей запятой, выполненным с возможностью выполнять операции с плавающей запятой, имеющие первую точность, включает этапы: выбора субточности, которая меньше, чем первая точность, для операции с плавающей запятой над одним или несколькими числами с плавающей запятой, причем выбор субточности приводит к одному или нескольким избыточным разрядам для каждого из одного или нескольких чисел с плавающей запятой; снятия питания с логических схем, которые бы использовались для обработки одного или нескольких избыточных разрядов; и выполнения операции с плавающей запятой при питании, снятом с логических схем. 4 н. и 20 з.п. ф-лы, 4 ил.

Формула

выбор субточности, которая меньше, чем первая точность, для операции с плавающей запятой над одним или несколькими числами с плавающей запятой, причем выбор субточности приводит к одному или нескольким избыточным разрядам для каждого из одного или нескольких чисел с плавающей запятой;

снятие питания с логических схем, которые бы использовались для обработки одного или нескольких избыточных разрядов; и

выполнение операции с плавающей запятой при питании, снятом с логических схем.

контроллер с плавающей запятой, выполненный с возможностью выбора субточности, которая меньше, чем первая точность для операции с плавающей запятой над одним или несколькими числами с плавающей запятой, причем выбор субточности приводит к одному или нескольким избыточным разрядам для каждого из одного или нескольких чисел с плавающей запятой, при этом контроллер с плавающей запятой дополнительно выполнен с возможностью снятия питания с элементов регистра с плавающей запятой в процессоре с плавающей запятой, которые иначе бы использовались для хранения одного или нескольких избыточных разрядов и снятия питания с логических схем, которые бы использовались для обработки одного или нескольких избыточных разрядов; и

оператор с плавающей запятой, выполненный с возможностью выполнения операции с плавающей запятой, при питании, снятом с регистровых элементов с плавающей запятой и логических схем.

регистр с плавающей запятой, имеющий множество запоминающих элементов, выполненный с возможностью хранения одного или нескольких чисел с плавающей запятой;

оператор с плавающей запятой, выполненный с возможностью выполнения операции с плавающей запятой над одним или несколькими числами с плавающей запятой, хранимыми в регистре с плавающей запятой; и

контроллер с плавающей запятой, выполненный с возможностью выбора субточности, которая меньше, чем первая точность, для операции с плавающей запятой над одним или несколькими числами с плавающей запятой, причем выбор субточности приводит к одному или нескольким избыточным разрядам для каждого из одного или нескольких чисел с плавающей запятой, при этом один или несколько избыточных разрядов хранятся в одном или нескольких запоминающих элементах регистра с плавающей запятой, и при этом контроллер с плавающей запятой дополнительно выполнен с возможностью снятия питания с запоминающих элементов, хранящих один или несколько избыточных разрядов, и снятия питания с логических схем, которые бы использовались для обработки одного или нескольких избыточных разрядов.

регистр с плавающей запятой, выполненный с возможностью хранения одного или нескольких чисел с плавающей запятой;

оператор с плавающей запятой, имеющий логику, выполненный с возможностью выполнения операции с плавающей запятой над одним или несколькими числами с плавающей запятой, хранимыми в регистре с плавающей запятой; и

контроллер с плавающей запятой, выполненный с возможностью выбора субточности, которая меньше, чем первая точность, для операции с плавающей запятой над одним или несколькими числами с плавающей запятой, причем выбор субточности приводит к одному или нескольким избыточным разрядам для каждого из одного или нескольких чисел с плавающей запятой, и в котором контроллер с плавающей запятой дополнительно выполнен с возможностью снятия питания с части логических схем, которые иначе бы использовались для обработки одного или нескольких избыточных разрядов, и снятия питания с элементов регистра с плавающей запятой, которые иначе бы использовались для хранения одного или нескольких избыточных разрядов.

Комментарии