Устройство для деления - SU1361545A1

Код документа: SU1361545A1

Описание

Изобретение относится к вычислительной технике и может быть использовано в качестве блока приближенного деления.

Цель изобретения - сокращение количества оборудования.

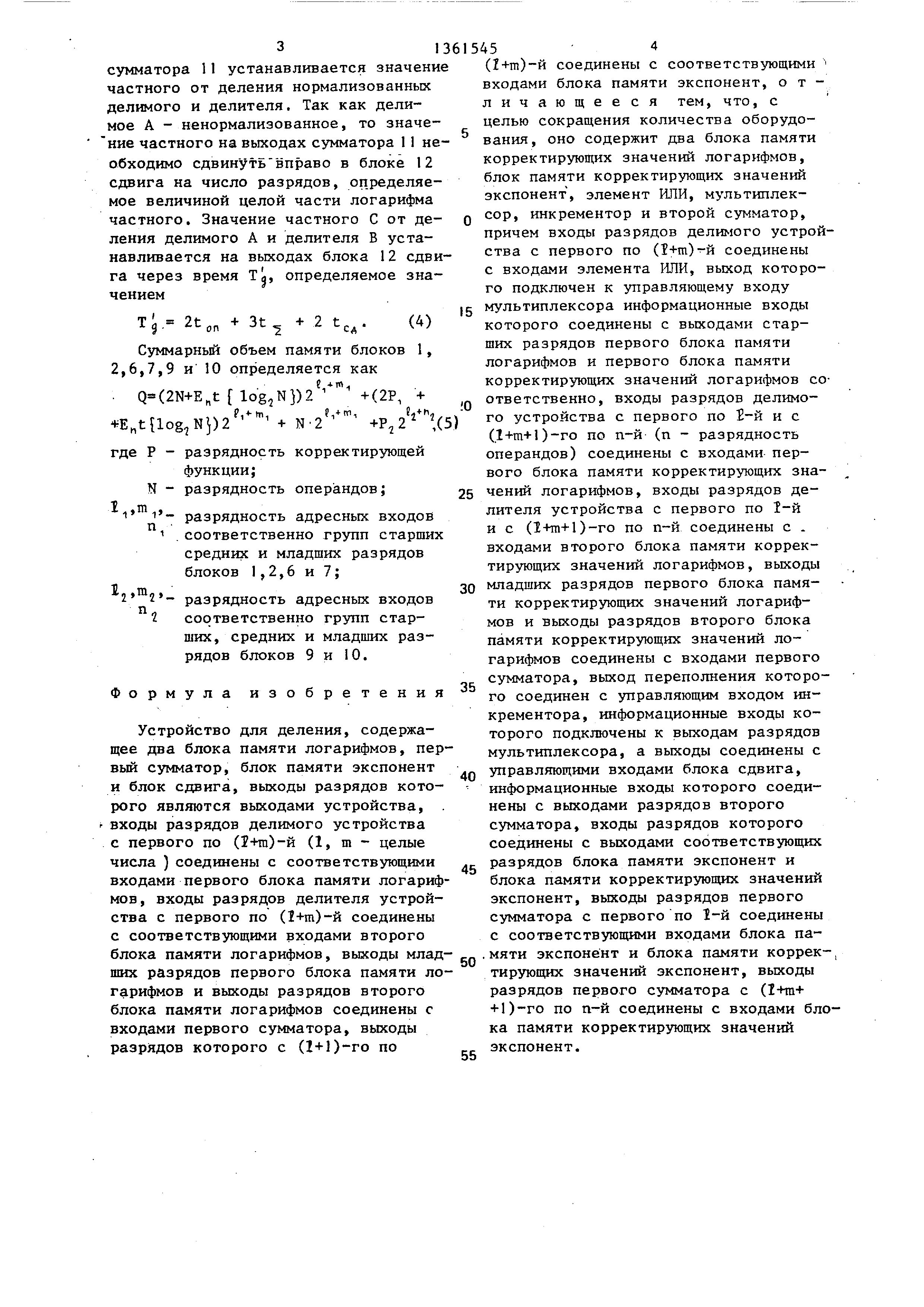

На чертеже приведена схема устройства .

Устройство содержит блок 1 памяти логарифмов, блок 2 памяти корректирующих значений логарифмов, инкремен- тор 3, .мультиплексор А, элемент ИЛИ. 5, блок 6 памяти логарифмов, блок 7 памяти корректирующих значений логарифмов , сумматор 8, блок 9 памяти экспонент, блок 10 памяти .корректирующих значений экспонент, сумматор 11 и блок I 2 сдвига,

Входы 13 делимого и входы 14 делителя являются информационными входами устройства. Входы 15 t старших разрядов делимого подключены к входам старших разрядов элемента ШШ 5 и . блоков 1 и 2 памяти, входы 16 разрядов делимого с (1+1)-го по (1+т)-й соединены с входами младших разрядов элемента ИЛИ 5 и блока 1 памяти, входы 17 младших разрядов делимого ,с (1+га+1)-го по п-й подключены к входам младших разрядов блока 2 памяти. Выходы старших разрядов блоков 1 и 2 памяти соединены соответственно с первой и второй группами информационных входов мультиплексора 4, управляющий вход которого соединен с выходом элемента ИЛИ 5. Входы 18 старших разрядов делителя подключены к входам старших разрядов блоков 6 и 7 памяти, входы 19 разрядов делителя с (1+1)-го по (1+т)-й соединены с входами младших разрядов блока 6 памяти , а входы 20 младших разрядов делителя с (5-Нп+1)-го по п-й подключены к входам младших разрядов блока 7 памяти. Входы первого, второго,, третьего и четвертого слагаемых сум- матора 8 соединены соответственно с выходами младших разрядов блоков 1 и 2 памяти и с выходами блоков 6 и 7 памяти. Выход переноса сумматора 8 подключен к управляющему входу инкре- ментора 3, информационные входы которого соединены с вькодами мультиплексора 4. Выходы 1 старших разрядов сумматора 8 подключены к входам старших разрядов блоков 9 и 10 памяти, выходы разрядов сумматора 8 с (1+1)- го по (1+т)-й - к входам младших

разрядов блока 9 памяти и выходы младших разрядов с (1н-т+1 )-го по п-й- к входам младших разрядов блока 10 памяти. Выходы блоков 9 и 10 памяти соединены соответственно с входами первого и Второго слагаемых сумматора 11, выходы которого подключены к информационным входам блока 12 сдвига, управляющие входы которого соединены с выходами инкрементора 3. Выходы 21 блока сдвига 12 являются информационными выходами устройства.

Устройство работает следующим образом .

Деление реализуется по формуле

С А/В 2

eo(j;j,4-feg-2a;

(1)

Делимое А поступает на входы блоков 1 и 2, которые содержат характеристику и мантиссу соответствующих значений логарифма. В зависимости от значений групп старших, средних и младших разрядов делимого А на инкре- ментор 3 через мультиплексор 4 поступает значение характеристики логарифма из блока 1 (в случае наличия хотя бы одного единичного разряда в группе старших и средних разрядов делимого А, что определяет формирование управляющего сигнала элементом РШИ 5 для мультиплексора 4 (или из: блока 2) при нулевом значении старших и средних разрядов делимого А). Значения мантис сы логарифмов и корректирующих функций с выходов блоков 1, 2, 6 и 7 поступают на входы сумматора 8, где реализуется функция

40

F(x) F,(x) - F2(x); (2) Fi(x) f(xe,) + 1,(хе.„), (3)

где f.(Xj) - значение функции-в узловых точках; значение корректирующей функции.

.(«,т)

F., (х) F(x).

Если при выполнении (2) в сумматоре 8 возникает перенос, то формируется управляющий сигнал для инкрементора 3, которьш увеличивает на единицу младшего разряда значение характеристики делимого А. Полученное значение разности мантисс логарифмов (2) поступает на входы блоков 9 и 10, которые совместно с сумматором 11 реализуют вычисление экспоненты согласно (1) и (3). На выходах.

сумматора 11 устанавливается значение частного от деления нормализованных делимого и делителя. Так как делимое А - ненормализованное, то значе- ние частного на выходах сумматора 11 необходимо сдвинуть вправо в блоке 12 сдвига на число разрядов, определяемое величиной целой части логарифма частного. Значение частного С от де- ления делимого А и делителя В устанавливается на выходах блока 12 сдвига через время Та, определяемое знаа

чением

Тд. 2t, + 3t + 2 t,.

(4)

Суммарньй объем памяти блоков 1, 2,6,7,9 и 10 определяется как

. Q(2N+E,t log,N}) +(2Р, + E,tUog,.N.2 .P,

где Р - разрядность корректирующей

функции; N - разрядность операндов;

1 1- разрядность адресных входов 1 .соответственно групп старших средних и младших разрядов блоков 1,2,6 и 7;

1,,т„,

2- разрядность адресных входов

1 соответственно групп старших , средних и младших разрядов блоков 9 и IО.

Формула изобретения

Устройство для деления, содержащее два блока памяти логарифмов, первый сумматор, блок памяти экспонент и блок сдвига, выходы разрядов которого являются выходами устройства, входы разрядов делимого устройства с первого по (Т+га)-й (1, m - целые числа ) соединены с соответствующими входами первого блока памяти логарифмов , входы разрядов делителя устройства с первого по (1+т)-й соединены с соответствующими входами второго блока памяти логарифмов, выходы млад-

ших разрядов первого блока памяти логарифмов и выходы разрядов второго блока памяти логарифмов соединены с входами первого сумматора, выходы разрядов которого с (1+1)-го по

5

5

0

5

0

..

v

5

(1+т)-й соединены с соответствующими входами блока памяти экспонент, отличающееся тем, что, с целью сокращения количества оборудования , оно содержит два блока памяти корректирующих значений логарифмов, блок памяти корректирующих значений экспонент , элемент ИЛИ, мультиплексор , инкрементор и второй сумматор, причем входы разрядов делимого устройства с первого по (1+т) соединены с входами элемента 1-ШИ, выход которого подключен к управляющему входу мультиплексора информационные входы которого соединены с выходами старших разрядов первого блока памяти логарифмов и первого блока памяти корректирующих значений логарифмов соответственно , входы разрядов делимого устройства с первого по Б-й и с (1+т-И)-го по п-й (п - разрядность операндов) соединены с входами первого блока памяти корректирующих значений логарифмов, входы разрядов делителя устройства с первого по 1-й и с (1+т+1)-го по п-й соединены с . входами второго блока памяти корректирующих значений логарифмов, выходы младших разрядов первого блока памяти корректирующих значений логарифмов и выходы разрядов второго блока памяти корректирующих значений логарифмов соединены с входами первого сумматора, выход переполнения которого соединен с управляющим входом ин- крементора, информационные входы которого подключены к выходам разрядов мультиплексора, а выходы соединены с управляющими входами блока сдвига, информационные входы которого соединены с выходами разрядов второго сумматора, входы разрядов которого соединены с выходами соответствующих разрядов блока памяти экспонент и блока памяти корректирующих значений экспонент, выходы разрядов первого сумматора с первого по 1-й соединены с соответствующими входами блока па- .мяти экспонент и блока памяти коррек-, тирующих значений экспонент, выходы разрядов первого сумматора с (1+т+ +1)-го по п-й соединены с входами блока памяти корректирующих значений экспонент.

Реферат

Изобретение относится к вычис-. лительной технике и может быть ис;пользовано в качестве блока приближенного деления..Цель изобретения J5 16 /7 5 сокращение количества оборудования. Устройство содержит два блока 1, 6 памяти логарифмов, два блока 2, 7 памяти корректирующих значений логарифмов , инкрементор 3, мультиплексор 4, элемент ИЛИ 5, два сумматора 8, II блок 9 памяти экспонент, блок 10 памяти корректирующих значений экспонент и блок 12 сдвига. Сокращение аппаратных затрат достигнуто за счет введения двух блоков памяти корректирующих значений логарифмов, инкре- ментора, мультиплексора, элемента ИЛИ, сумматора, блока памяти коррек-i тирующих значений экспоненты и оригинальных связей между узлами и блоками . 1 ил. 5 73 1 20 . Г1 11 .«А. i 21

Формула

Комментарии