Множительное устройство - SU824206A1

Код документа: SU824206A1

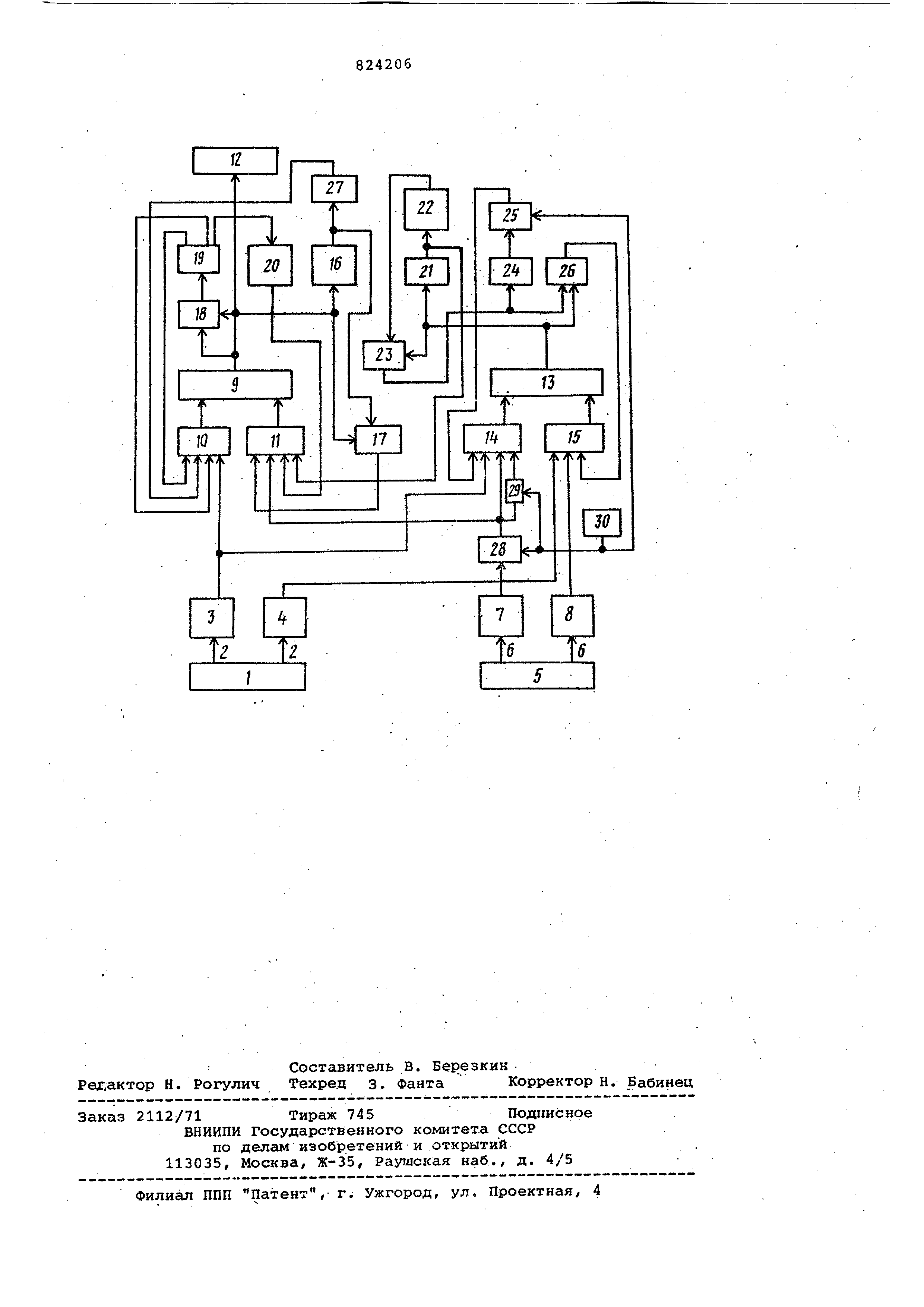

Чертежи

Описание

1

Изобретение относится к вычисли- тельной технике и может быть использовано для ускоренного выделения операций умножения и деления в быстродействующих специализированных и универсальных цифровых вычислительны машин.

Известно табличное суммирующеемножительное устройство, содержащее запоминающее устройство, схему фор .мирования адресов таблиц, регистры первого и второго onepaHjjOB и уст- . ройство управления, кроме того, со держит блок выдачи результата и блок анёшиза, входы которого подключены к выходам регистров первого и второго операндов, выходы блока анализа операндов подсоединены через схемы И ко входам первой и второй схемы ИЛИ б.1юка - выдачи результата , выход первой схемы ИЛИ блока выдачи результата соединен со входами опроса регистра второго операнда, выход которого подк.пючен к триггерам регистра второго операнда , выход второй схемы ИЛИ блока выдачи результата соединён со входом схемы опроса регистра первого операнда , выход которой подключен к триггерзм регистра первого операнда 1.

Недостатком такого устройства является сравнительно большая емкость используемого запоминающего устройства , а также невоэможность выполнения этим устройством операции деления .

Известно множительное устройство, содержащее два регистра первого one- . ранда, соединенные выходами своей

0 старшей и младшей частей соответственно с первым и вторым блоками памяти, регистр второго операнда соединенный выходами своей старшей и младшей частей соответственно с треть5 им и четвертым блокс1ми памяти, первый су1.Ф4атор, входы которого соединены с первыми вторым коммутаторами, вы .ход первого сумматора соединен с регистром результата, и второй сумматор, входьт

0 которого соединены с третьими четвертым коммутаторами, выход первого блока памяти через первый коммутатор подключен к первому сумматору и через третий коммутатор ко второму сумматору, выход

5 второго блока памяти, и выход четвертого блока памяти через четвертый ког.1мутатор подключены ко второму cyMMciTOpy 2,.

Недостатком такого ус1ройства яв-ляется необходимость использования

блоков памяти большой емкости, что связано со значительными техническими трудностями изготовления. Так при длине п двоичных разрядов операндов требуемый суммарный объем блоков памяти составляет (4ц+3)2 Кроме того, это устройство не приспособлено для выполнения операции деления. ,

Цель изобретения - уменьшение сум1ларной емкости используемых блоков памяти и расширение функциональных возможностей устройства за счет возможности выполнения операции деления .

Поставленная цель достигается тем, что множительное устройство, содержащее регистры первого и второго операндов , регистр результата, блоки памяти , сумматоры и коммутаторы, причем выходы старшей и младшей частей регистра первого операнда соединень со входом соотве тственно первого и второго блоков памяти, выходы старшей и младшей частей регистра второго операнда соединены со входами соответственно третьего и четвертого блоков памяти, входы первого сумматора соединены с выходами первого и второго коммутаторов , а выход - со входом регистра результата, входы второго сумматора подключены к выходам третьего и четвертого коммутаторов, выход первого блока памяти соединен с первыми входами первого и третьего коммутаторов , выход второго блока памяти соединен с первым входом четвертого комглутатора , выход четвертого блока памяти соединен со вторым входом четвертого коммутатора, содержит дополнительно три блока памяти, буферные регистры , сдвлгатели, преобразователи кода в дополни тельный, многоразрядный ключ и блок переключения режимов, причем выход первого сумматора соединен со входом пятого блока памяти, выход- которого подключен ко входу первого сдвигателя, выход которого соединен с первым входом второго коммутатора, выход первого сумматора соедине-н со входом второго сдвигат-еля , выход которого подключен ко входу первого буферного регистра, выход младшей части которого соединен со входом шестого блока памяти, выход которого подключен ко второму входу второго коммутатора, выход второго сумматора соединен со входом второго буферного регистра, выход которого соединен со входом седьмого блока памяти, выходл которого подключен ко входу третьего сдвигателя, вь1ход которого подключен ко входу третьего буферного регистра, выход которого соединен со входом первого пре-. образователя прямого кода в дополнительнЫй , выход которого подключен ко второму входу третьего коммутатора, выход второго сумматора соединен со

входом четвертого буферного регистра выход, которого соединен с третьим входов четвертого коммутатора, выход третьего сдвигателя соединен со входом четвертого буферного регистра, выход пятого блока памяти соединен со входом пятого буферного регистра выход которого подключен ко второму входу первого коммутатора, выход третьего блока памяти соединен со вхдом второго преобразователя прямого кода в дополнительный, выход которого подключен к третьему входу второго коммутатора, третьему входу третьего коммутатора и с информационным входом многоразрядного ключа, выход которого соединен с четвертым входом третьего коммутатора, выходы старшей и младшей частей, первого буферного регистра соединены с третьим и четверты входами первого коммутатора , выход второго буферного регистра соединен с четвертым входом второго коммутатора, управляющие входы преобразователей прямого кода в дополнительный и многоразрядного ключа подключены к выходу блока переключения Е)ежимов.

Умножение XY и деление X/Y операндов X и Y производится в устройстве на основе следующих соотношений .

Пусть ,1, Хг,

Y l,

Vl

2. V Y |0,1 . Фиксируем некоторые значения параметров. К и L 1 К, , и разбиваем операнды X и Y в суммы двух слагаемых - опорные значения XpYo и приращения операндов дх, UY;

.oi)

i+i--X XO- AX , .

(y,)X-y и FgCK. ,

Разлагают функции

в ряд Тейлора по приращениямДX, &Y,

ограничившись первыми производными

Х- i(X,)

X/V--F,IX,V)--XO/ O - х/ о-А ХоПо- «2,

где R и R - остаточные члены формулы Тейлора и для данных FI

и Fg имеем

/R,/ лхь. /Ra/ /AX-2.f/

При l/2iSX l,, , 0« И для оценки остаточных членов имеем неравенства.

1, /R. (

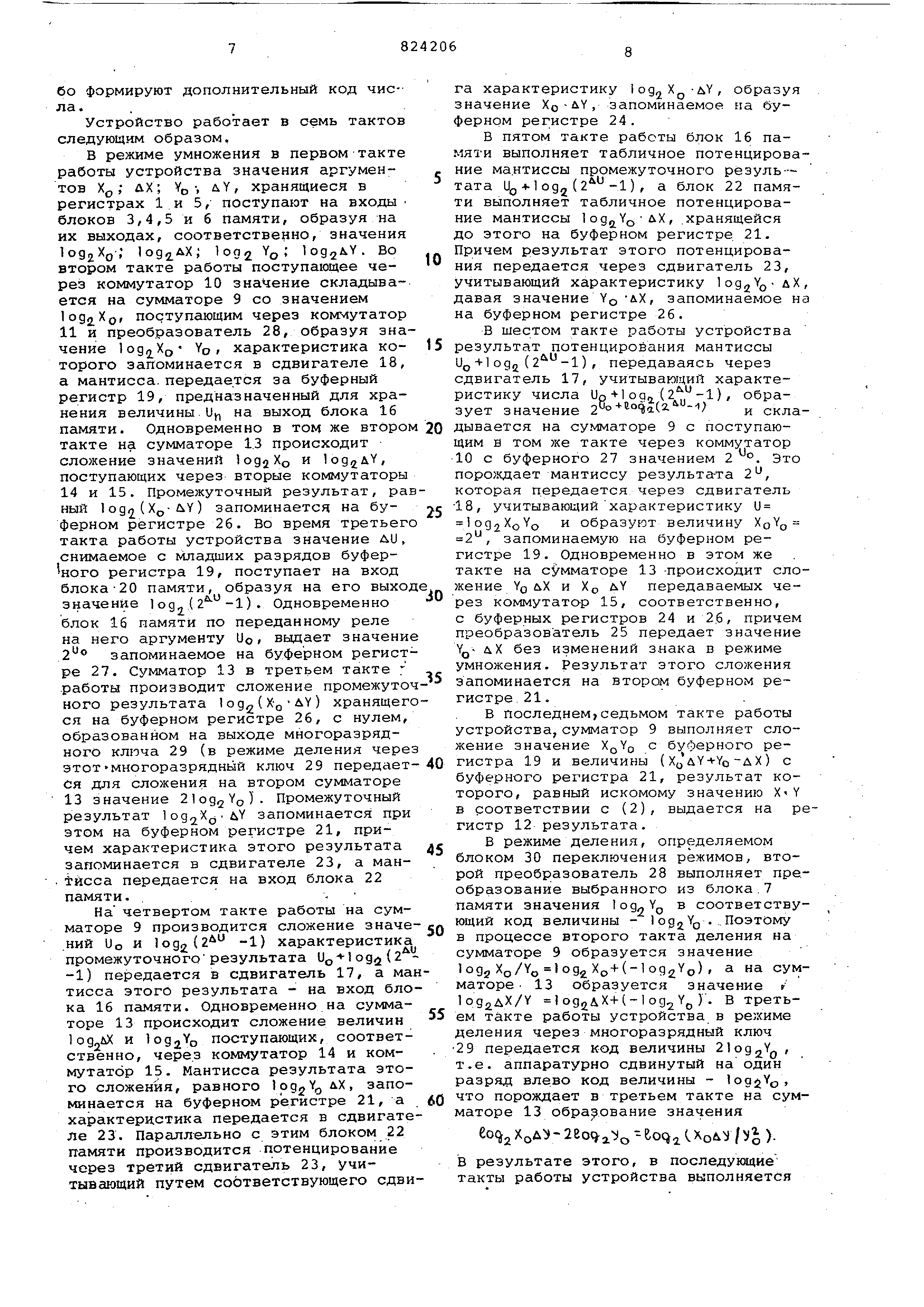

2-.2b.j Выбирают значения параметров К и 1 так, чтобы выполнялось условие (K,bH)4h + 2, (1) вычисляют значения результатов операций X-Y и X/Y с п+1 верной знача1дей двоичной цифрой после запятой по формулам Х-У Хо о-«-Д) . (2) 1 .X/Vo- o/Vo (3) Заменяя в этих формулах операции умножения .на последовательные операции логарифмирования, сложения и потенцирования имеем ) .ч, -. ц... 42 гос яА - -eocjaXo, Х/: -. . + 2 2Д - ос 2Хо-2Со( Значения Log2Xo. оЭз. 1ог,дУ, в связи с существенно меньшей чем п разрядностью промежуточных аргументов Хд; Уд;дХ, дУ, находят табличным преобразованием соответствующих аргументов. Операцию потенци (рования по основанию 2, также находят табличным преобразованием, но в связи со значительно ольщей ра рядностью первых слагаег-их в первой части формул (2) и (3) по сравнению с остальными слагаемыми целесообр зно с точки зрения сокращения объема блоков памяти, используемых для хранения таблиц преобразований, поступают следующим образом. Требуется найти значение 2 (условие U Uof&U), тогда (2 ограничиваемся ПЗУ, хранящим таблицы от промежуточных аргументов U и &U вдвое меньшей разрядности. На чертеже представлена блок-схем . множительного устройства. Устройство содержит регистр 1 пер вого операнда, выходы 2 которого сое динены со входами блоков 3 и 4 памяти , причем выход старшей час.ти регис ра 1 соединен со входом блока 3 памя ти, а выход младшей части - со входом блока 4 памяти, регистр 5 второго операнда, выходы 6 которого соединены со входами блоком 7 и 8 памяти причем выход старшей части регист ра 5 соединен со входом блока 7 памяти , а выход младшей части регистра 5 - со входом блока 8 памяти, сум ма.тор 9, входы которого соединены с выходами первого и второго коммутаторов 10 и 11, выход первого суммато ра 9 соединен с регистром 12 результ та, сумматор 13, входы которого .соединены с третьим и четвертым коммута торами 14 и 15. Устройство содержит, кроме того, последовательно соединей ные с выходом сумматора 9 блок 16 памяти и сдвигатель 17, выход которо го подключен ко входу коммутатора 11 а также последовательно соединенные с выходом сумматора сдвигатель 18, буферный регистр 19 и блок 20 памяти, выход которого подключен ко входу коммутатора 11. В состав устройства входят последовательно соединенные с выходом сумматора 13 буферные регистр 21, блок 22 памяти, сдвигатель 23, буферный регистр 24 и преобразователь 25 прямого кода в дополнительный, выход которого подключен ко входу коммутатора 14, буферный регистр 26, соединенный по входу с выходом сумматора 13 и выходом сдвигателя 23, а по выходу - со входом коммутатора 15. Устройство содержит также буферный регистр 27, соединенный по входу с выходом блока16 памяти, а по выходу - со входом коммутатора 10, преобразователь прямого кода в дополнительный 28, соединенный по входу с выходом блока 7 памяти, а по выходусо входом коммутатора 11, со входом коммутатора 14 и с информационным входом многоразрядного ключа 29, соединенного по выходу со входом коммутатора 14. Выход блока 3 памяти через коммутатор 10 подключен, к сумматору .9 и через коммутатор 14 к сумматору 13, выход блока 3 памяти и выход блока 8 памяти через к.оммутатор 15 подключены к сумматору 13. Выходы старшейИ младшей части буферного регистра 19 соединены со входами коммутатора 10, выход буферного регистра 21 соединен со входом коммутатора 11, а управляющие входы преобразователей 25 и 26 прямого кода в дополнительный и многоразрядного ключа 29 подключены к выходу блока 30 переключения режимов. Управляющий вход сдвигателя 17 соединен с выходом сумматора 9, а управляющий вход сдвигателя 23 подключен к выходу сумматора 13. В предлагаемом устройстве в старшей части регистра 1 первого операнда хранится значение Хр старших .разрядов аргумента X, в младшей части регистра 1 первого операнда содержится значение лХ млащших разрядов аргумента X. В старшей и младшей частях регистра второго операнда хранятся , соответственно, значения Y и л,У. Для хранения таблиц значений logj logg ДХ; logjY, используются , соответственно, блоки 3,4, 7 и 8 памяти, блоки 16 и 18 памяти и используются для табличных преобразований потенцирования , блок 20 памяти содержит таблицы значений 1092() . Сдвигатели 18, 17 и 23 используются wui получения верного промежуточного результата по мантиссе аргумента потенцирования с учетом характеристики этого аргумента. Преобразователи 25 и 28 в зависимости от состояния управляющего входа либо передают код числа без изменений, либо формируют дополнительный код чис-ла . .

Устройство работает в семь тактов следующим образом,

В режиме умножения в первом такте работы устройства значения аргументов Хд; ДХ; УС,-, ДУ, хранящиеся в регистрах 1 и 5, поступают на входы блоков 3,4,5 и б памяти, образуя на их выходах, соответственно, значения logjXo, )од2.ДХ; 1од2 YQ ; . Во втором такте работы поступающее через коммутатор 10 значение складывается на сумматоре 9 со значением , поступающим через коммутатор 11 и преобразователь 28, образуя значение УО , характеристика которого запоминается в сдвигателе 18, а мантисса, передается за буферный регистр 19, предназначенный для хранения величины.и на выход блока 16 памяти. Одновременно в том же втором такте на сумматоре 1.3 происходит сложение значений logjXo и поступающих через вторые коммутаторы 14 и 15. Промежуточный результат, равный 1 од (Xj,-ukY) запоминается на буферном регистре 26. Во время третьего такта работы устройства значение ли, снимаемое с младших разрядов буфер ного регистра 19, поступает на вход блока-20 памяти, образуя на его выход значение од„(). Одновременно блок 16 памяти по переданному реле на него аргументу Uo, выдает значение 2 запоминаемое на буферном регистре 27. Сумматор 13 в третьем такте : .работы производит сложение промежуточ ного результата 1од2(Х-о-ДУ) хранящегося на буферном регистре 26, с нулем, образованном на выходе многоразрядного ключа 29 (в режиме деления через этотМногоразрядный ключ 29 передается для сложения на втором сумматоре 13 значение 21од2Уо)- Промежуточный результат .iy запоминается при этом на буферном регистре 21, причем характеристика этого результата запоминается в сдвигателе 23, а ман . йсса передается на вход блока 22 памяти. ..

На четвертом такте работы на сумматоре 9 производится сложение значе .НИИ Uo и og2{2 -1) характеристика промежуточногорезультата ,j(2 -1 ) передается в сдвигатель 17, а мантисса этого результата - на вход блока 16 памяти. Одновременно на сумматоре 13 происходит сложение величин и поступающих, соответственно , чере.з коммутатор 14 и коммутатор 15. Мантисса результата этого сложения, равного ДХ, запоминается на буферном регистре 21, а характеристика передается в сдвигателе 23. Параллельно с этим блоком 22 памяти производится потенцирование через третий сдвигатель 23, учитывающий путем соответствующего сдвига характеристику 1од Хр-дУ, образуя значение XQ - лУ , запоминаемое Eia буферном регистре 24.

В пятом такте работы блок 16 памяти выполняет табличное потенцирование ма,нтиссы промежуточного резуль-тата UQ -log2() , а блок 22 памяти выполняет табличное потенцирование мантиссы , .хранящейся до этого на буферном регистре. 21. Причем результат этого потенцирования передается через сдвигатель 23, учитывающий характеристику logjyQ-AX давая значение УО ЛХ, запоминаемое н на буферном регистре 26.

В шестом такте работы устройства результат потенциройания мантиссы о °9г передаваясь через сдвигатель 17, учитывающий характеристику числа Up-t-1 од,, (), образует значение 2°°- °SJa(2. складывается на сумматоре 9 с поступающим а том же такте через коммутатор 10 с буферного 27 значением 2 °. Это поро кдает мантиссу результата 2, которая передается через сдвигатель 18, учитывающийхарактеристику и и образуют величину ХоУд 2, запоминаемую на буферном регистре 19. Одновременно в этом же такте на сумматоре 13 -происходит сложение Уц лХ и XQ дУ передаваемых через коммутатор 15, соответственно, с буферных регистров 24 и 2.6, причем преобразователь 25 передает значение Уд- дХ без изменений з.нака в режиме умножения. Результат этого сложения запоминается на втором буферном регистре 21.

В последнем,седьмом такте работы устройства, сумматор 9 выполняет сложение значение с буферного регистра 19 и величины ( ХОДУ- -УО-д Х) с буферного регистра 21, результат которого , равный искомому значению XУ в соответствии с (2), выдается на ргистр 12 результата.

В режиме деления, определяемом блоком 30 переключения режимов, второй преобразователь 28 выполняет преобразование выбранного из блока.7 памяти значения в соответствующий код величины - 1 Поэтому в процессе второго такта деления на сумматоре 9 образуется значение logg Хо/Уо 1од2Хо+(-1од2Уо) а на сумматоре . 13 образуется значение / 1 og2&X+(-1 од.Ур ). В третьем такте работы устройства в режиме деления через многоразрядный ключ 29 передается код величины 21од2Уд, т.е. аппаратурно сдвинутый на один разряд влево код величины - , что порождает в третьем такте на сумматоре 13 образование значения

-boq,, Uo /V ).

В результате этого, в последугацие такты работы устройства выполняется потенцирование логарифмов logj X j/YplogguX/Yo и (Xo ) вместо оЗаЛХУо и од„ХоЛУ, образуя значения XO/YJJ , AX/YO и ХолУ/У В шестом такте деления преобразователь 22 изменяет знак передаваемого с буферного регистра 21 значения ХрйУ/ygf , поэтому при сложении содержимого буферных регистров 24 и 26 в этом такте образуется значение дХ/Уо-дУ ХО/У(. Функционирование остальных узлов устройства в режиме де ления происходит таким же образом, как и в рассмотренном подробно режиме умноясения. СумМ(арный объем блоков памяти, используемом в предлагаемом устройстве , составляет величину Q (.i-v3)(«-K-I-3) (у, + Ъ)2 + -v() (и+г ) 2, где .Ь1,сГ Л 2-ГУИУ1(К,1И), а функция W(X) x есть наименьгаее целое число, не меньшее X, причем для получения требуемой точности необходимо выполнение условия (1). Для разрядной сетки получаем , что требуется суммарный объем блоков памяти величиной в ,875 Кби для предлагаемого устройства, в то время как для известного необходимы блоки памяти cyjvwapHofl емкостью Q 8576 Кбит, т.е. получаем выигрыш в объеме блоков памяти более чем в 350 раз. Для п-24 получаем, соответственно , ( Кбит, Q 992 Кбит, что дает выигрьни более, чем в 4000 раз Формула изобретения Множительное устройство, содержащее регистры -первого и второго операндов , регистр результата, блоки па мяти, сумматоры и кoм yтaтopы, приче выходы старшей и младшей частей ре .гистра первого операнда соединены со входом соответственно первого и второго блоков памяти, вьисоды старшей и частей регистра второго операнда соединены со входами соотве ственн9 третьего и четвертого блоков памяти j звходы первого сумматора сое динены с выходами первого и второго коммутатос, а выход - со входом регистра результата; входы второго сум матора подклпочены к выходам третьего и четвертого коммутаторов, выход первого блока памяти соединен с первыми входами первого и третьего коммутаторов , выход второго блока памяти соединен со вторым входом четверт го коммутатора, выход четвертого бло ка памяти соединен со вторам входом четвертого коммутатора, отлича ющееся Тем,что,с целью расширен функциональных возможностей устройства за счет выполнения операции деленияи сокращения суммарной емкости используемых блоков памяти устройство содержит дополнительно три блока памяти, буферные регистры, сдвигатели, преобразователи прямото кода в дополнительный, многоразрядный ключ и блок переключения.режимов , причем выход первого сумматора соединен, со входом пятого блока памяти , выход которого подключен ко входу первого сдвигателя, выход которого соединен с первым входом второго коммутатора, выход первого суммато- ра соединен со входом второго сдвигателя , выход, которого подключен ко входу первого буферного регистра, выход младшей части которого соединен со входом шестого блока памяти, выход которого подключен ко второму входу второго коммутатора, выход второго сумматора соединен со входом второго буферного регистра, выход которого соединен со входом седьмого блока памяти , выход которого подключен ко входу третьего сдвигателя, выход которого подключен ко входу.третьего буферного регистра, выход которого соединен со входом первого преобразователя прямого кода в дополнительный, выход которого подключен ко второму входу третьего коммутатора, выход второго, сумматора соединен со входом четвертого буферного регистра, выход которого соединен с третьим . входом четвертого коммутатора, выход .третьего сдвигателя .соединен со входом четвертого б.уферного регистра, выход пятого блока памяти соединен со входом пятого буферного регистра, выход которого подключен ко второ .му входу первого коммутатора, выход третьего блока памяти-соединен со входом Е..ТОРОГО преобразователя прямого кода в дополнительный, выход которого подключая к третьему входу второго коммутатора, третьему входу третьего коммутатора и с информационным входом многоразрядного ключа, выход которого соединен с четвертым входом третьего коммутатора, выходы старшей и младшей частей первого буферного регистра соединены с третьим и четвертым входами первого коммутатора , выход второго буферного регистра соединен с четвертым входом вто- рого коммутатора, управляющие входы преобразователей прямого кода в дополнительный и многоразрядного ключа подключены- к выходу блока переключения режимов. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 253442, кл. G 06 F 3/39, . G Об Г, 7/385, 1968. 2.Патент США № 3749898, кл. 235-164, 1973 -(прототип

Реферат

Формула

Комментарии